Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

| Product Status             | Obsolete                                                               |  |

| Core Processor             | ST7                                                                    |  |

| Core Size                  | 8-Bit                                                                  |  |

| Speed                      | 16MHz                                                                  |  |

| Connectivity               | LINbusSCI, SPI                                                         |  |

| Peripherals                | LVD, POR, PWM, WDT                                                     |  |

| Number of I/O              | 15                                                                     |  |

| Program Memory Size        | 8KB (8K x 8)                                                           |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | -                                                                      |  |

| RAM Size                   | 384 x 8                                                                |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |  |

| Data Converters            | A/D 7x10b                                                              |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |

| Mounting Type              | Surface Mount                                                          |  |

| Package / Case             | 20-VQFN Exposed Pad                                                    |  |

| Supplier Device Package    | 20-QFN (6x5)                                                           |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite35u6tr |  |

## **Table of Contents**

| 16.2    | LINSCI LIMITATION | <br> | <br> | <br> | <br> | 169 |

|---------|-------------------|------|------|------|------|-----|

| 17 REVI | SION HISTORY      | <br> | <br> | <br> | <br> | 171 |

To obtain the most recent version of this datasheet, please check at www.st.com

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 169.

## PIN DESCRIPTION (Cont'd)

## Legend / Abbreviations for Table 2:

Type: I = input, O = output, S = supply

In/Output level:  $C_T = CMOS \ 0.3V_{DD}/0.7V_{DD}$  with input trigger Output level:  $HS = 20mA \ high \ sink \ (on \ N-buffer \ only)$

Port and control configuration:

Input: float = floating, wpu = weak pull-up, int = interrupt, ana = analog

Output: OD = open drain, PP = push-pull

The RESET configuration of each pin is shown in bold which is valid as long as the device is in reset state.

**Table 2. Device Pin Description**

|       |            |                      |      | Le      | vel            |       | Ро    | rt / C | Cont | rol |     |               |                                                                                                                                                                   |  |  |  |

|-------|------------|----------------------|------|---------|----------------|-------|-------|--------|------|-----|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | P20        | Pin Name             | Type | _       | ¥              |       | Inp   | out    |      | Out | put | Main Function | Alternate Function                                                                                                                                                |  |  |  |

| QFN20 | SO20/DIP20 | i iii Naiile         | Τ    | Input   | Output         | float | ndw   | int    | ana  | ОО  | РР  | (after reset) | Alternate Function                                                                                                                                                |  |  |  |

| 19    | 1          | V <sub>SS</sub> 1)   | S    |         |                |       |       |        |      |     |     | Ground        |                                                                                                                                                                   |  |  |  |

| 20    | 2          | V <sub>DD</sub> 1)   | S    |         |                |       |       |        |      |     |     | Main pow      | er supply                                                                                                                                                         |  |  |  |

| 1     | 3          | RESET                | I/O  | $C_T$   |                |       | Х     |        |      | Х   |     | Top priori    | rity non maskable interrupt (active low)                                                                                                                          |  |  |  |

| 2     | 4          | PB0/AIN0/SS          | I/O  | C       | Ç <sub>T</sub> | x     | x ei3 |        | х    | x   | x   | Port B0       | ADC Analog Input 0 or SPI Slave Select (active low)  Caution: No negative current injection allowed on this pin. For details, refer to section 13.2.2 on page 132 |  |  |  |

| 3     | 5          | PB1/AIN1/SCK         | I/O  | C       | C <sub>T</sub> | x     |       |        | Х    | х   | х   | Port B1       | ADC Analog Input 1 or SPI Serial Clock <b>Caution:</b> No negative current injection allowed on this pin. For details, refer to section 13.2.2 on page 132        |  |  |  |

| 4     | 6          | PB2/AIN2/<br>MISO    | I/O  | C       | C <sub>T</sub> | х     |       |        | Х    | Х   | Х   | Port B2       | ADC Analog Input 2 or SPI Master In/<br>Slave Out Data                                                                                                            |  |  |  |

| 5     | 7          | PB3/AIN3/<br>MOSI    | I/O  | C       | Ст             | х     | е     | i2     | х    | Х   | Х   | Port B3       | ADC Analog Input 3 or SPI Master Out / Slave In Data                                                                                                              |  |  |  |

| 6     | 8          | PB4/AIN4/<br>CLKIN** | I/O  | C       | C <sub>T</sub> | X     | Х     |        | х    | х   | Х   | Port B4       | ADC Analog Input 4 or External clock input                                                                                                                        |  |  |  |

| 7     | 9          | PB5/AIN5             | I/O  | C       | C <sub>T</sub> | X     | 0     | i2     | Х    | Х   | Χ   | Port B5       | ADC Analog Input 5                                                                                                                                                |  |  |  |

| 8     | 10         | PB6/AIN6/RDI         | I/O  | (       | C <sub>T</sub> | X     | е     | 14     | Х    | Х   | Χ   | Port B6       | ADC Analog Input 6 or LINSCI Input                                                                                                                                |  |  |  |

| 9     | 11         | PA7/TDO              | I/O  | $C_{T}$ | HS             | X     | Χ     |        |      | Х   | Х   | Port A7       | LINSCI Output                                                                                                                                                     |  |  |  |

CR9 CR8 CR7 CR6 CR5 CR4 CR3 CR2 **RCCR** CR0 SICSR CR1 CLKIN/2 (Ext Clock) Tunable 1% RC Oscillator RC OSC 1MHz PLL Clock 8MHz PLL 1MHz -> 8MHz fosc 4MHz PLL 1MHz -> 4MHz OSCRANGE[2:0] Option bits OSC Option bit PLLx4x8 CLKIN H **CLKIN** /2 OSC,PLLOFF, **DIVIDER** OSCRANGE[2:0] Option bits CLKIN/ OSC1 OSC Crystal OSC /2 OSC2 1-16 MHZ **DIVIDER** or 32kHz f<sub>LTIMER</sub> 8-BIT (1ms timebase @ 8 MHz f<sub>OSC</sub>) LITE TIMER 2 COUNTER fosc fosc/32 /32 DIVIDER  $f_{CPU}$ TO CPU AND f<sub>OSC</sub> 0 PERIPHERALS MCO SMS **MCCSR**  $f_{CPU}$

Figure 13. Clock Management Block Diagram

#### 9 POWER SAVING MODES

#### 9.1 INTRODUCTION

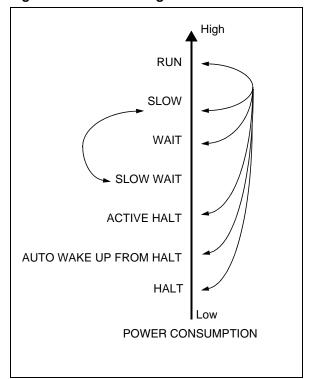

To give a large measure of flexibility to the application in terms of power consumption, five main power saving modes are implemented in the ST7 (see Figure 21):

- Slow

- Wait (and Slow-Wait)

- Active Halt

- Auto Wake up From Halt (AWUFH)

- Halt

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 (f<sub>OSC2</sub>).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

Figure 21. Power Saving Mode Transitions

#### 9.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

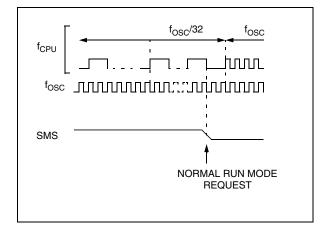

SLOW mode is controlled by the SMS bit in the MCCSR register which enables or disables Slow mode.

In this mode, the oscillator frequency is divided by 32. The CPU and peripherals are clocked at this-lower frequency.

**Note**: SLOW-WAIT mode is activated when entering WAIT mode while the device is already in SLOW mode.

Figure 22. SLOW Mode Clock Transition

#### POWER SAVING MODES (Cont'd)

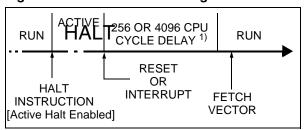

Figure 26. ACTIVE-HALT Timing Overview

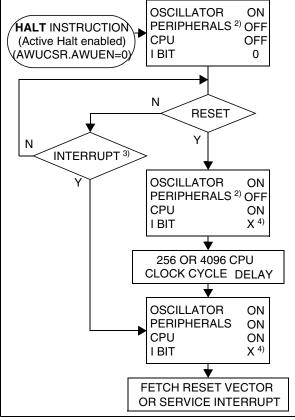

Figure 27. ACTIVE-HALT Mode Flow-chart

#### Notes:

- 1. This delay occurs only if the MCU exits ACTIVE-HALT mode by means of a RESET.

- 2. Peripherals clocked with an external clock source can still be active.

- **3.** Only the RTC1 interrupt and some specific interrupts can exit the MCU from ACTIVE-HALT mode. Refer to Table 6, "Interrupt Mapping," on page 36 for more details.

- **4.** Before servicing an interrupt, the CC register is pushed on the stack. The I bit of the CC register is set during the interrupt routine and cleared when the CC register is popped.

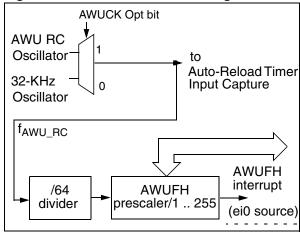

#### 9.6 AUTO WAKE UP FROM HALT MODE

Auto Wake Up From Halt (AWUFH) mode is similar to Halt mode with the additional of an internal RC oscillator for wake-up. Compared to ACTIVE-HALT mode, AWUFH has lower power consumption (the main clock is not kept running), but there is no accurate realtime clock available.

It is entered by executing the HALT instruction when the AWUEN bit in the AWUCSR register has been set.

Figure 28. AWUFH Mode Block Diagram

As soon as HALT mode is entered, and if the AWUEN bit has been set in the AWUCSR register, the AWU RC oscillator provides a clock signal (f<sub>AWU RC</sub>). Its frequency is divided by a fixed divider and a programmable prescaler controlled by the AWUPR register. The output of this prescaler provides the delay time. When the delay has elapsed the AWUF flag is set by hardware and an interrupt wakes-up the MCU from Halt mode. At the same time the main oscillator is immediately turned on and a 256 cycle delay is used to stabilize it. After this start-up delay, the CPU resumes operation by servicing the AWUFH interrupt. The AWU flag and its associated interrupt are cleared by software reading the AWUCSR register.

To compensate for any frequency dispersion of the AWU RC oscillator, it can be calibrated by measuring the clock frequency  $f_{AWU}$  RC and then calculating the right prescaler value. Measurement mode is enabled by setting the AWUM bit in the AWUCSR register in Run mode. This connects  $f_{AWU}$  RC to the input capture of the 12-bit Auto-Relad timer, allowing the  $f_{AWU}$  RC to be measured using the main oscillator clock as a reference time-base.

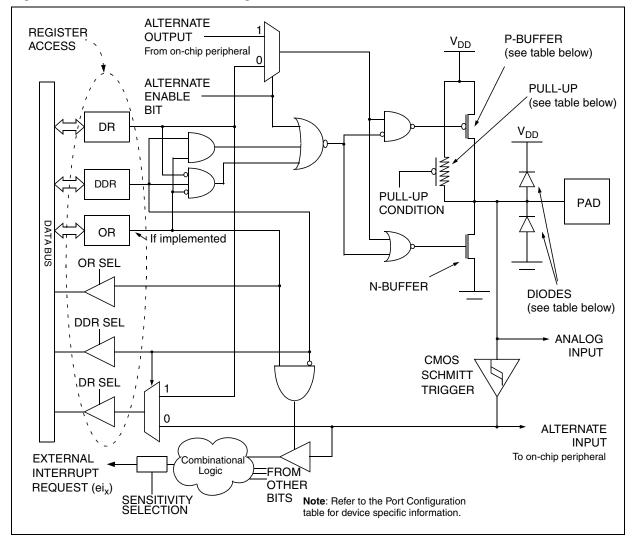

## I/O PORTS (Cont'd)

Figure 31. I/O Port General Block Diagram

Table 9. I/O Port Mode Options

|        | Configuration Made              | Pull-Up | P-Buffer | Dio                | Diodes             |  |  |

|--------|---------------------------------|---------|----------|--------------------|--------------------|--|--|

|        | Configuration Mode              | Pull-Op | P-Buller | to V <sub>DD</sub> | to V <sub>SS</sub> |  |  |

| Innut  | Floating with/without Interrupt | Off     | Off      | Off                |                    |  |  |

| Input  | Pull-up with/without Interrupt  | On      | 7 011    | On                 |                    |  |  |

|        | Push-pull                       | Off     | On       | - On               | On                 |  |  |

| Output | Open Drain (logic level)        |         | Off      |                    | I                  |  |  |

|        | True Open Drain                 | NI      | NI       | NI (see note 1)    |                    |  |  |

Legend: NI - not implemented

Off - implemented not activated

On - implemented and activated

**Note 1:** The diode to  $V_{DD}$  is not implemented in the true open drain pads. A local protection between

the pad and  $\ensuremath{V_{OL}}$  is implemented to protect the device against positive stress.

Note 2: For further details on port configuration, please refer to Table 11 and Table 12 on page 51.

## WATCHDOG TIMER (Cont'd)

## 11.1.5 Interrupts

None.

# 11.1.6 Register Description CONTROL REGISTER (CR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | ТО |

Bit 7 = **WDGA** Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bit 6:0 = **T[6:0]** *7-bit timer (MSB to LSB)*. These bits contain the decremented value. A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

## **DUAL 12-BIT AUTORELOAD TIMER 3** (Cont'd)

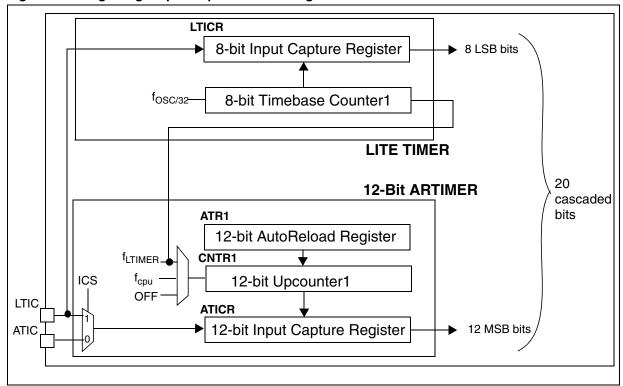

#### Long input capture

Pulses that last between 8 $\mu$ s and 2s can be measured with an accuracy of 4 $\mu$ s if f<sub>OSC</sub> = 8MHz in the following conditions:

- The 12-bit AT3 Timer is clocked by the Lite Timer (RTC pulse: CK[1:0] = 01 in the ATCSR register)

- The ICS bit in the ATCSR2 register is set so that the LTIC pin is used to trigger the AT3 Timer capture.

- The signal to be captured is connected to LTIC pin

- Input Capture registers LTICR, ATICRH and ATICRL are read

This configuration allows to cascade the Lite Timer and the 12-bit AT3 Timer to get a 20-bit input capture value. Refer to Figure 44.

Figure 44. Long Range Input Capture Block Diagram

#### Notes:

- 1. Since the input capture flags (ICF) for both timers (AT3 Timer and LT Timer) are set when signal transition occurs, software must mask one interrupt by clearing the corresponding ICIE bit before setting the ICS bit.

- 2. If the ICS bit changes (from 0 to 1 or from 1 to 0), a spurious transition might occur on the input capture signal because of different values on LTIC and ATIC. To avoid this situation, it is recommended to do as follows:

- First, reset both ICIE bits.

- Then set the ICS bit.

- Reset both ICF bits.

- And then set the ICIE bit of desired interrupt.

- 3. How to compute a pulse length with long input capture feature.

As both timers are used, computing a pulse length is not straight-forward. The procedure is as follows:

At the first input capture on the rising edge of the pulse, we assume that values in the registers are as follows:

LTICR = LT1

ATICRH = ATH1

ATICRL = ATL1

Hence ATICR1 [11:0] = ATH1 & ATL1

Refer to Figure 45 on page 65.

#### **DUAL 12-BIT AUTORELOAD TIMER 3** (Cont'd)

#### 11.2.6 Register Description

## TIMER CONTROL STATUS REGISTER (ATCSR)

Read / Write

Reset Value: 0x00 0000 (x0h)

| 7 | 6   |      |     |     |      |        | 0     |

|---|-----|------|-----|-----|------|--------|-------|

| 0 | ICF | ICIE | CK1 | СКО | OVF1 | OVFIE1 | CMPIE |

Bit 7 = Reserved.

## Bit 6 = ICF Input Capture Flag.

This bit is set by hardware and cleared by software by reading the ATICR register (a read access to ATICRH or ATICRL will clear this flag). Writing to this bit does not change the bit value.

0: No input capture

1: An input capture has occurred

#### Bit 5 = ICIE IC Interrupt Enable.

This bit is set and cleared by software.

0: Input capture interrupt disabled

1: Input capture interrupt enabled

#### Bits 4:3 = **CK[1:0]** Counter Clock Selection.

These bits are set and cleared by software and cleared by hardware after a reset. They select the clock frequency of the counter.

| Counter Clock Selection                     | CK1 | СКО |

|---------------------------------------------|-----|-----|

| OFF                                         | 0   | 0   |

| OFF                                         | 1   | 1   |

| f <sub>LTIMER</sub> (1 ms timebase @ 8 MHz) | 0   | 1   |

| f <sub>CPU</sub>                            | 1   | 0   |

#### Bit 2 = **OVF1** Overflow Flag.

This bit is set by hardware and cleared by software by reading the TCSR register. It indicates the transition of the counter1 CNTR1 from FFh to ATR1 value.

0: No counter overflow occurred

1: Counter overflow occurred

#### Bit 1 = **OVFIE1** Overflow Interrupt Enable.

This bit is read/write by software and cleared by hardware after a reset.

0: Overflow interrupt disabled.

1: Overflow interrupt enabled.

#### Bit 0 = **CMPIE** Compare Interrupt Enable.

This bit is read/write by software and cleared by hardware after a reset. It can be used to mask the interrupt generated when any of the CMPFx bit is set

0: Output compare interrupt disabled.

1: Output Compare interrupt enabled.

## **COUNTER REGISTER 1 HIGH (CNTR1H)**

Read only

Reset Value: 0000 0000 (000h)

| 15 |   |   |   |              |              |             | 8           |

|----|---|---|---|--------------|--------------|-------------|-------------|

| 0  | 0 | 0 | 0 | CNTR1_<br>11 | CNTR1_<br>10 | CNTR1_<br>9 | CNTR1_<br>8 |

## **COUNTER REGISTER 1 LOW (CNTR1L)**

Read only

Reset Value: 0000 0000 (000h)

| CNTR1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

Bits 15:12 = Reserved.

#### Bits 11:0 = **CNTR1[11:0]** *Counter Value*.

This 12-bit register is read by software and cleared by hardware after a reset. The counter CNTR1 is incremented continuously as soon as a counter clock is selected. To obtain the 12-bit value, software should read the counter value in two consecutive read operations. The CNTR1H register can be incremented between the two reads, and in order to be accurate when f<sub>TIMER</sub>=f<sub>CPU</sub>, the software should take this into account when CNTR1L and CNTR1H are read. If CNTR1L is close to its highest value, CNTR1H could be incremented before it is read.

When a counter overflow occurs, the counter restarts from the value specified in the ATR1 register.

0

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

## 11.5.5 SCI Mode - Functional Description

#### **Conventional Baud Rate Generator Mode**

The block diagram of the Serial Control Interface in conventional baud rate generator mode is shown in Figure 55.

It uses four registers:

- 2 control registers (SCICR1 and SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

#### **Extended Prescaler Mode**

Two additional prescalers are available in extended prescaler mode. They are shown in Figure 57.

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

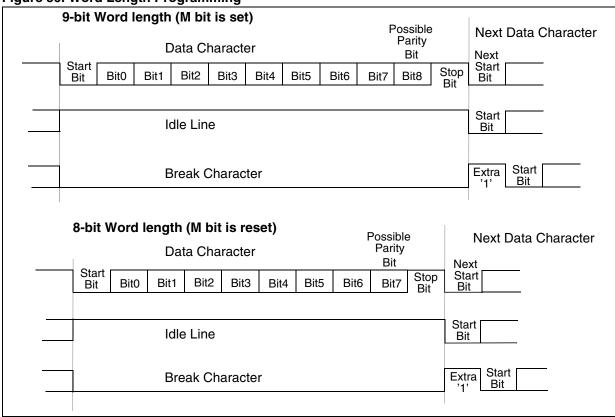

#### 11.5.5.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 56).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as a continuous logic high level for 10 (or 11) full bit times.

A Break character is a character with a sufficient number of low level bits to break the normal data format followed by an extra "1" bit to acknowledge the start bit.

Figure 56. Word Length Programming

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### 11.5.5.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 55).

#### **Procedure**

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to send a preamble of 10 (M = 0) or 11 (M = 1) consecutive ones (Idle Line) as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I[11:0] bits are cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set.

When a character transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I[1:0] bits are cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break character length depends on the M bit (see Figure 56).

As long as the SBK bit is set, the SCI sends break characters to the TDO pin. After clearing this bit by software, the SCI inserts a logic 1 bit at the end of the last break character to guarantee the recognition of the start bit of the next character.

#### Idle Line

Setting the TE bit drives the SCI to send a preamble of 10 (M = 0) or 11 (M = 1) consecutive '1's (idle line) before the first character.

In this case, clearing and then setting the TE bit during a transmission sends a preamble (idle line) after the current word. Note that the preamble duration (10 or 11 consecutive '1's depending on the M bit) does not take into account the stop bit of the previous character.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

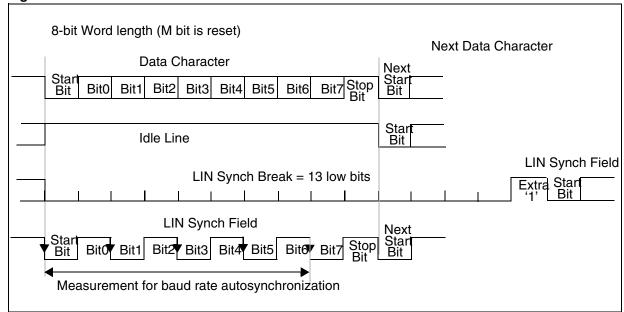

## LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

## Figure 58. LIN Characters

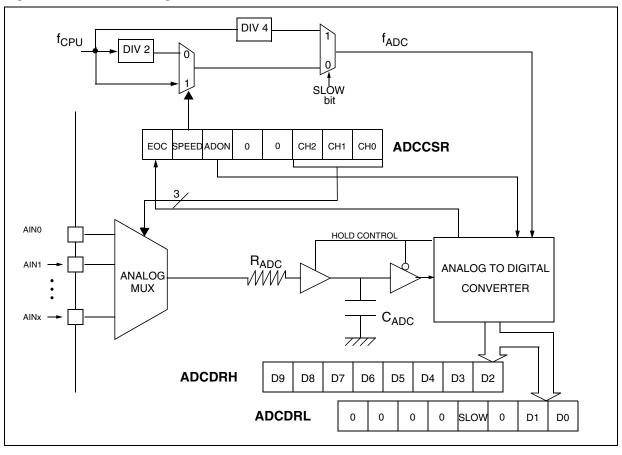

#### 11.6 10-BIT A/D CONVERTER (ADC)

#### 11.6.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 7 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 7 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 11.6.2 Main Features

- 10-bit conversion

- Up to 7 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 66.

## 11.6.3 Functional Description

## 11.6.3.1 Analog Power Supply

$V_{DDA}$  and  $V_{SSA}$  are the high and low level reference voltage pins. In some devices (refer to device pin out description) they are internally connected to the  $V_{DD}$  and  $V_{SS}$  pins.

Conversion accuracy may therefore be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines.

Figure 66. ADC Block Diagram

## 12 INSTRUCTION SET

#### 12.1 ST7 ADDRESSING MODES

The ST7 Core features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The ST7 Instruction set is designed to minimize the number of bytes required per instruction: To do so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

**Table 23. ST7 Addressing Mode Overview**

|           | Mode     |          | Syntax              | Destination/<br>Source      | Pointer<br>Address<br>(Hex.) | Pointer<br>Size<br>(Hex.) | Length<br>(Bytes)                              |

|-----------|----------|----------|---------------------|-----------------------------|------------------------------|---------------------------|------------------------------------------------|

| Inherent  |          |          | nop                 |                             |                              |                           | + 0                                            |

| Immediate |          |          | ld A,#\$55          |                             |                              |                           | + 1                                            |

| Short     | Direct   |          | ld A,\$10           | 00FF                        |                              |                           | + 1                                            |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF                    |                              |                           | + 2                                            |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF                        |                              |                           | + 0 (with X register)<br>+ 1 (with Y register) |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE                       |                              |                           | + 1                                            |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF                    |                              |                           | + 2                                            |

| Short     | Indirect |          | ld A,[\$10]         | 00FF                        | 00FF                         | byte                      | + 2                                            |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF                    | 00FF                         | word                      | + 2                                            |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE                       | 00FF                         | byte                      | + 2                                            |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF                    | 00FF                         | word                      | + 2                                            |

| Relative  | Direct   |          | jrne loop           | PC-128/PC+127 <sup>1)</sup> |                              |                           | + 1                                            |

| Relative  | Indirect |          | jrne [\$10]         | PC-128/PC+127 <sup>1)</sup> | 00FF                         | byte                      | + 2                                            |

| Bit       | Direct   |          | bset \$10,#7        | 00FF                        |                              |                           | + 1                                            |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF                        | 00FF                         | byte                      | + 2                                            |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF                        |                              |                           | + 2                                            |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF                        | 00FF                         | byte                      | + 3                                            |

#### Note:

1. At the time the instruction is executed, the Program Counter (PC) points to the instruction following JRxx.

#### 12.2 INSTRUCTION GROUPS

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | CP   | TNZ  | ВСР  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a prebyte

The instructions are described with 1 to 4 bytes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

PC-2 End of previous instruction

PC-1 Prebyte

PC Opcode

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit or direct relative addressing mode to an instruction using the corresponding indirect addressing mode. It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

#### 12.2.1 Illegal Opcode Reset

In order to provide enhanced robustness to the device against unexpected behavior, a system of illegal opcode detection is implemented. If a code to be executed does not correspond to any opcode or prebyte value, a reset is generated. This, combined with the Watchdog, allows the detection and recovery from an unexpected fault or interference.

**Note:** A valid prebyte associated with a valid opcode forming an unauthorized combination does not generate a reset.

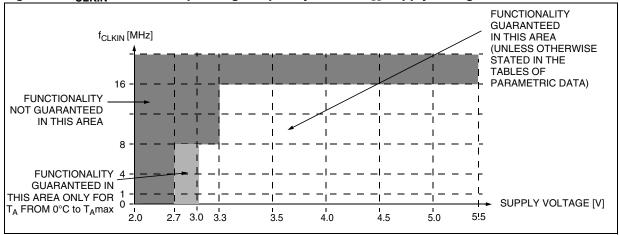

#### 13.3 OPERATING CONDITIONS

## 13.3.1 General Operating Conditions: Suffix 6 Devices

$T_A = -40 \text{ to } +125^{\circ}\text{C}$  unless otherwise specified.

| Symbol             | Parameter                             | Conditions                                                                  | Min      | Max | Unit   |

|--------------------|---------------------------------------|-----------------------------------------------------------------------------|----------|-----|--------|

|                    |                                       | f <sub>OSC</sub> = 8 MHz. max., T <sub>A</sub> = 0 to 125°C 2.7             |          | 5.5 |        |

| $V_{DD}$           | Supply voltage                        | $f_{OSC} = 8 \text{ MHz. max., } T_A = -40 \text{ to } 125^{\circ}\text{C}$ | 3.0      | 5.5 | V      |

|                    |                                       | f <sub>OSC</sub> = 16 MHz. max.                                             | 3.3      | 5.5 |        |

| f <sub>CLKIN</sub> | External clock frequency on CLKIN pin | V <sub>DD</sub> ≥3.3V                                                       | up to 16 |     | MHz    |

|                    |                                       | V <sub>DD</sub> ≥3.0V                                                       | up to 8  |     | IVIIIZ |

Figure 69. f<sub>CLKIN</sub> Maximum Operating Frequency Versus V<sub>DD</sub> Supply Voltage

#### 13.5 CLOCK AND TIMING CHARACTERISTICS

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub>.

## 13.5.1 General Timings

| Symbol               | Parameter 1)                                                             | Conditions             | Min  | <b>Typ</b> <sup>2)</sup> | Max  | Unit             |

|----------------------|--------------------------------------------------------------------------|------------------------|------|--------------------------|------|------------------|

| +                    | Instruction cycle time                                                   | f <sub>CPU</sub> =8MHz | 2    | 3                        | 12   | t <sub>CPU</sub> |

| <sup>t</sup> c(INST) |                                                                          |                        | 250  | 375                      | 1500 | ns               |

| +                    | Interrupt reaction time $^{3)}$<br>$t_{v(IT)} = \Delta t_{c(INST)} + 10$ | f <sub>CPU</sub> =8MHz | 10   |                          | 22   | t <sub>CPU</sub> |

| τ <sub>ν(IT)</sub>   |                                                                          |                        | 1.25 |                          | 2.75 | μS               |

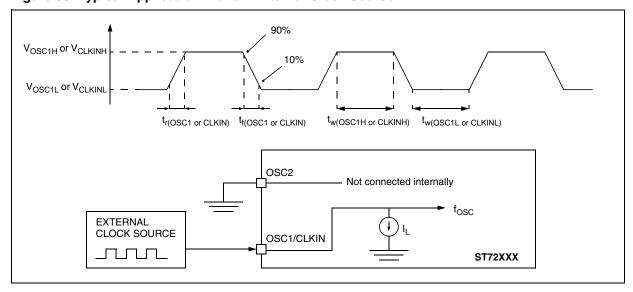

#### 13.5.2 External Clock Source

| Symbol                                                                                                                                        | Parameter                                  | Conditions                       | Min                 | Тур | Max             | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------|---------------------|-----|-----------------|------|

| V <sub>OSC1H</sub> or V <sub>CLKIN_H</sub>                                                                                                    | OSC1/CLKIN input pin high level voltage    |                                  | 0.7xV <sub>DD</sub> |     | $V_{DD}$        | V    |

| V <sub>OSC1L</sub> or V <sub>CLKIN_L</sub>                                                                                                    | OSC1/CLKIN input pin low level voltage     |                                  | $V_{SS}$            |     | $0.3xV_{ m DD}$ | V    |

| $ \begin{array}{c} t_{w(\text{OSC1H})} \text{ or } t_{w(\text{CLKINH})} \\ t_{w(\text{OSC1L})} \text{ or } t_{w(\text{CLKINL})} \end{array} $ | OSC1/CLKIN high or low time 4)             | see Figure 83                    | 15                  |     |                 | ns   |

| $t_{r(OSC1)}$ or $t_{r(CLKIN)}$<br>$t_{f(OSC1)}$ or $t_{f(CLKIN)}$                                                                            | OSC1/CLKIN rise or fall time <sup>4)</sup> |                                  |                     |     | 15              | 115  |

| IL                                                                                                                                            | OSCx/CLKIN Input leakage current           | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                     |     | ±1              | μΑ   |

#### Notes:

- 1. Guaranteed by Design. Not tested in production.

- 2. Data based on typical application software.

- 3. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

- 4. Data based on design simulation and/or technology characteristics, not tested in production.

Figure 83. Typical Application with an External Clock Source

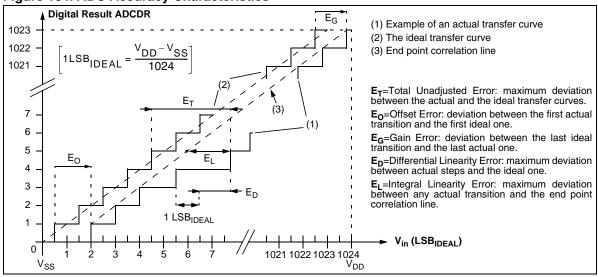

## **ADC CHARACTERISTICS (Cont'd)**

## ADC Accuracy with 3V<sub>2</sub>V<sub>DD</sub> <3.6V

| Symbol            | Parameter                    | Conditions                                                      | Тур | Max <sup>3)</sup> | Unit |

|-------------------|------------------------------|-----------------------------------------------------------------|-----|-------------------|------|

| IE <sub>T</sub> I | Total unadjusted error       |                                                                 | 2.5 | 6                 |      |

| IE <sub>O</sub> I | Offset error                 |                                                                 | 0.9 | 4                 |      |

| IE <sub>G</sub> I | Gain Error                   | f <sub>CPU</sub> =4MHz, f <sub>ADC</sub> =2MHz <sup>1) 2)</sup> | 1.3 | 4.5               | LSB  |

| IE <sub>D</sub> I | Differential linearity error |                                                                 | 1.8 | 3                 |      |

| IE <sub>L</sub> I | Integral linearity error     |                                                                 | 1.0 | 3                 |      |

## ADC Accuracy with 4.5V<sub>S</sub>V<sub>DD</sub> 5.5V

| Symbol            | Parameter                    | Conditions                                                      | Тур | Max <sup>3)</sup> | Unit |

|-------------------|------------------------------|-----------------------------------------------------------------|-----|-------------------|------|

| IE <sub>T</sub> I | Total unadjusted error       |                                                                 | 2.0 | 4                 |      |

| IE <sub>O</sub> I | Offset error                 |                                                                 | 0.6 | 1.5               | LSB  |

| IE <sub>G</sub> I | Gain Error                   | f <sub>CPU</sub> =8MHz, f <sub>ADC</sub> =4MHz <sup>1) 2)</sup> | 1.2 |                   |      |

| IE <sub>D</sub> I | Differential linearity error |                                                                 | 1.6 | 2.5               |      |

| IE <sub>L</sub> I | Integral linearity error     |                                                                 | 1.8 | 2.5               |      |

#### Notes:

- 1. Data based on characterization results over the whole temperature range, monitored in production.

- 2. ADC accuracy vs negative injection current: Injecting negative current on any of the analog input pins may reduce the accuracy of the conversion being performed on another analog input.

The effect of negative injection current on robust pins is specified in section 13.11 on page 157

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 13.2.2 does not affect the ADC accuracy.

3. Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to +125°C ( $\pm$  3 $\sigma$  distribution limits).

Figure 104. ADC Accuracy Characteristics

| ST7LITE                                                                                       | E3xF2 FASTROM MIC<br>(Last update:          | ROCONTRO<br>November 20                 |                                                                                                                   | -                                             |

|-----------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Customer                                                                                      |                                             |                                         |                                                                                                                   |                                               |

| Contact Phone No Reference FASTROM Code*: *FASTROM code name is ass FASTROM code must be sent | igned by STMicroelec<br>in .S19 formatHex e | tronics.                                |                                                                                                                   |                                               |

| Device type: [] S                                                                             | T7PLITE30F2                                 | ST7PLITE35                              | F2 []ST7PLIT                                                                                                      | E39F2                                         |

|                                                                                               |                                             |                                         |                                                                                                                   |                                               |

| Special Marking: [] N<br>Authorized characters are lette<br>Maximum character count: 8 c      | ers, digits, '.', '-', '/' and              |                                         | "                                                                                                                 |                                               |

| Temperature range                                                                             | [] - 40°C to + 85                           | 5°C                                     | [] - 40°C to + 125°                                                                                               | С                                             |

| AWUCK Selection                                                                               | [] 32-kHz Oscill                            | ator                                    | [] AWU RC Oscilla                                                                                                 | tor                                           |

| Clock Source Selection:                                                                       | [] Resonator:                               | [ ] LP: Low<br>[ ] MP: Me<br>[ ] MS: Me | ry Low power resona<br>power resonator (1 t<br>dium power resonato<br>dium speed resonato<br>n speed resonator (8 | to 2 MHz)<br>r (2 to 4 MHz)<br>r (4 to 8 MHz) |

|                                                                                               | [] External Clod                            | [] on PB4<br>[] on OSC                  | 1                                                                                                                 | ·                                             |

|                                                                                               | [] Internal RC C                            | Oscillator                              |                                                                                                                   |                                               |

| Sector 0 size:                                                                                | [] 0.5K                                     | []1K                                    | [] 2K                                                                                                             | []4K                                          |

| Readout Protection:                                                                           | [] Disabled                                 | [] Enabled                              |                                                                                                                   |                                               |

| FLASH Write Protection                                                                        | [] Disabled                                 | [] Enabled                              |                                                                                                                   |                                               |

| PLL                                                                                           | [] Disabled                                 | [] PLLx4                                | [] PLLx8                                                                                                          |                                               |

| LVD Reset                                                                                     | [] Disabled                                 | [] Highest<br>[] Medium<br>[] Lowest    | threshold                                                                                                         |                                               |

| Watchdog Selection:                                                                           | [] Software Act                             | tivation                                | [] Hardware                                                                                                       | Activation                                    |

| Watchdog Reset on Halt:                                                                       | [] Disabled                                 |                                         | [] Enabled                                                                                                        |                                               |

| Date:                                                                                         | application:                                |                                         |                                                                                                                   |                                               |

| Important note: Not all config<br>Refer to Figu                                               |                                             | nation schem                            | e.                                                                                                                |                                               |

| rlease download the latest versio                                                             | n of this option list fron                  | n:                                      |                                                                                                                   |                                               |

## **15.4 ST7 APPLICATION NOTES**

## **Table 27. ST7 Application Notes**

| IDENTIFICATION        | DESCRIPTION                                                                                 |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

|                       | APPLICATION EXAMPLES                                                                        |  |  |  |  |  |

| AN1658                | SERIAL NUMBERING IMPLEMENTATION                                                             |  |  |  |  |  |

| AN1720                | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                                  |  |  |  |  |  |

| AN1755                | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                                 |  |  |  |  |  |

| AN1756                | CHOOSING A DALI IMPLEMENTATION STRATEGY WITH ST7DALI                                        |  |  |  |  |  |

| AN1812                | A HIGH PRECISION, LOW COST, SINGLE SUPPLY ADC FOR POSITIVE AND NEGATIVE IN-<br>PUT VOLTAGES |  |  |  |  |  |

| <b>EXAMPLE DRIVER</b> | RS                                                                                          |  |  |  |  |  |

| AN 969                | SCI COMMUNICATION BETWEEN ST7 AND PC                                                        |  |  |  |  |  |

| AN 970                | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                                    |  |  |  |  |  |

| AN 971                | I <sup>2</sup> C COMMUNICATION BETWEEN ST7 AND M24CXX EEPROM                                |  |  |  |  |  |

| AN 972                | ST7 SOFTWARE SPI MASTER COMMUNICATION                                                       |  |  |  |  |  |

| AN 973                | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                             |  |  |  |  |  |

| AN 974                | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                               |  |  |  |  |  |

| AN 976                | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                             |  |  |  |  |  |

| AN 979                | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                                 |  |  |  |  |  |

| AN 980                | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                           |  |  |  |  |  |

| AN1017                | USING THE ST7 UNIVERSAL SERIAL BUS MICROCONTROLLER                                          |  |  |  |  |  |

| AN1041                | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                                   |  |  |  |  |  |

| AN1042                | ST7 ROUTINE FOR I <sup>2</sup> C SLAVE MODE MANAGEMENT                                      |  |  |  |  |  |

| AN1044                | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                                          |  |  |  |  |  |

| AN1045                | ST7 S/W IMPLEMENTATION OF I <sup>2</sup> C BUS MASTER                                       |  |  |  |  |  |

| AN1046                | UART EMULATION SOFTWARE                                                                     |  |  |  |  |  |

| AN1047                | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                                      |  |  |  |  |  |

| AN1048                | ST7 SOFTWARE LCD DRIVER                                                                     |  |  |  |  |  |

| AN1078                | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                                |  |  |  |  |  |

| AN1082                | DESCRIPTION OF THE ST72141 MOTOR CONTROL PERIPHERALS REGISTERS                              |  |  |  |  |  |

| AN1083                | ST72141 BLDC MOTOR CONTROL SOFTWARE AND FLOWCHART EXAMPLE                                   |  |  |  |  |  |

| AN1105                | ST7 PCAN PERIPHERAL DRIVER                                                                  |  |  |  |  |  |

| AN1129                | PWM MANAGEMENT FOR BLDC MOTOR DRIVES USING THE ST72141                                      |  |  |  |  |  |

| AN1130                | AN INTRODUCTION TO SENSORLESS BRUSHLESS DC MOTOR DRIVE APPLICATIONS WITH THE ST72141        |  |  |  |  |  |

| AN1148                | USING THE ST7263 FOR DESIGNING A USB MOUSE                                                  |  |  |  |  |  |

| AN1149                | HANDLING SUSPEND MODE ON A USB MOUSE                                                        |  |  |  |  |  |

| AN1180                | USING THE ST7263 KIT TO IMPLEMENT A USB GAME PAD                                            |  |  |  |  |  |

| AN1276                | BLDC MOTOR START ROUTINE FOR THE ST72141 MICROCONTROLLER                                    |  |  |  |  |  |

| AN1321                | USING THE ST72141 MOTOR CONTROL MCU IN SENSOR MODE                                          |  |  |  |  |  |

| AN1325                | USING THE ST7 USB LOW-SPEED FIRMWARE V4.X                                                   |  |  |  |  |  |

| AN1445                | EMULATED 16-BIT SLAVE SPI                                                                   |  |  |  |  |  |

| AN1475                | DEVELOPING AN ST7265X MASS STORAGE APPLICATION                                              |  |  |  |  |  |

| AN1504                | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER                     |  |  |  |  |  |

| AN1602                | 16-BIT TIMING OPERATIONS USING ST7262 OR ST7263B ST7 USB MCUS                               |  |  |  |  |  |

| AN1633                | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION IN ST7 NON-USB APPLICATIONS                    |  |  |  |  |  |

| AN1712                | GENERATING A HIGH RESOLUTION SINEWAVE USING ST7 PWMART                                      |  |  |  |  |  |

| AN1713                | SMBUS SLAVE DRIVER FOR ST7 I2C PERIPHERALS                                                  |  |  |  |  |  |

| AN1753                | SOFTWARE UART USING 12-BIT ART                                                              |  |  |  |  |  |

|                       |                                                                                             |  |  |  |  |  |