Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | LINbusSCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 256 x 8                                                                |

| RAM Size                   | 384 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite39m3tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents

\_

|    | 9.5    | ACTIVE-HALT MODE                                          | 42  |

|----|--------|-----------------------------------------------------------|-----|

|    | 9.6    | AUTO WAKE UP FROM HALT MODE                               | 43  |

| 10 | I/O P0 | ORTS                                                      | 47  |

|    | 10.1   | INTRODUCTION                                              | 47  |

|    | 10.2   | FUNCTIONAL DESCRIPTION                                    | 47  |

|    | 10.3   | I/O PORT IMPLEMENTATION                                   | 50  |

|    |        | UNUSED I/O PINS                                           |     |

|    | 10.5   | LOW POWER MODES                                           | 50  |

|    |        | INTERRUPTS                                                |     |

| 11 |        | HIP PERIPHERALS                                           |     |

|    |        | WATCHDOG TIMER (WDG)                                      |     |

|    |        | DUAL 12-BIT AUTORELOAD TIMER 3 (AT3)                      |     |

|    |        | LITE TIMER 2 (LT2)                                        |     |

|    |        | SERIAL PERIPHERAL INTERFACE (SPI)                         |     |

|    |        | LINSCI SERIAL COMMUNICATION INTERFACE (LIN MASTER/SLAVE)  |     |

|    |        | 10-BIT A/D CONVERTER (ADC)                                |     |

| 12 |        |                                                           |     |

|    |        | ST7 ADDRESSING MODES                                      |     |

|    |        | INSTRUCTION GROUPS                                        |     |

| 13 |        |                                                           |     |

|    |        | PARAMETER CONDITIONS                                      |     |

|    |        | ABSOLUTE MAXIMUM RATINGS                                  |     |

|    | 13.3   | OPERATING CONDITIONS                                      |     |

|    | 13.4   | SUPPLY CURRENT CHARACTERISTICS                            |     |

|    | 13.5   | CLOCK AND TIMING CHARACTERISTICS                          |     |

|    | 13.6   | MEMORY CHARACTERISTICS                                    |     |

|    |        | EMC (ELECTROMAGNETIC COMPATIBILITY) CHARACTERISTICS       |     |

|    | 13.8   | I/O PORT PIN CHARACTERISTICS                              | 148 |

|    |        | CONTROL PIN CHARACTERISTICS                               |     |

|    | 13.10  | COMMUNICATION INTERFACE CHARACTERISTICS                   | 155 |

|    | 13.11  | 10-BIT ADC CHARACTERISTICS                                | 157 |

| 14 | PACK   |                                                           | 159 |

|    |        | PACKAGE MECHANICAL DATA                                   | 159 |

|    | 14.2   | THERMAL CHARACTERISTICS<br>160                            |     |

| 15 | DEVIC  | CE CONFIGURATION                                          | 161 |

|    | 15.1   | FLASH OPTION BYTES                                        | 161 |

|    | 15.2   | DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 163 |

|    | 15.3   | DEVELOPMENT TOOLS                                         | 165 |

|    | 15.4   | ST7 APPLICATION NOTES                                     | 166 |

| 16 |        | WN LIMITATIONS                                            |     |

|    | 16.1   | CLEARING ACTIVE INTERRUPTS OUTSIDE INTERRUPT ROUTINE      | 169 |

## Table of Contents

| 16.2    | LINSCI LIMITATION | <br> | <br> |    | 9 |

|---------|-------------------|------|------|----|---|

| 17 REVI | SION HISTORY      | <br> | <br> | 17 | 1 |

To obtain the most recent version of this datasheet, please check at www.st.com

57

Please also pay special attention to the Section "KNOWN LIMITATIONS" on page 169.

| Table 3. | Hardware | Register | Мар |

|----------|----------|----------|-----|

|----------|----------|----------|-----|

| Address Block -   |                 | Block Register Register Name |                                                               |                   | Remarks           |  |

|-------------------|-----------------|------------------------------|---------------------------------------------------------------|-------------------|-------------------|--|

| 0000h             |                 | PADR                         | Port A Data Register                                          | FFh <sup>1)</sup> | R/W               |  |

| 0001h             | Port A          | PADDR                        | Port A Data Direction Register                                | 00h               | R/W               |  |

| 0002h             |                 | PAOR                         | Port A Option Register                                        | 40h               | R/W               |  |

| 0003h             |                 | PBDR                         | Port B Data Register                                          | FFh <sup>1)</sup> | R/W               |  |

| 0004h             | Port B          | PBDDR                        | Port B Data Direction Register                                | 00h               | R/W               |  |

| 0005h             |                 | PBOR                         | Port B Option Register                                        | 00h               | R/W <sup>2)</sup> |  |

| 0006h<br>0007h    |                 |                              | Reserved area (2 bytes)                                       |                   |                   |  |

| 0008h             |                 | LTCSR2                       | Lite Timer Control/Status Register 2                          | 0Fh               | R/W               |  |

| 0009h             |                 | LTARR                        | Lite Timer Auto-reload Register                               | 00h               | R/W               |  |

| 000Ah             | LITE<br>TIMER 2 | LTCNTR                       | Lite Timer Counter Register                                   | 00h               | Read Only         |  |

| 000Bh             | HIVIER 2        | LTCSR1                       | Lite Timer Control/Status Register 1                          | 0x00 00x0b        | R/W               |  |

| 000Ch             |                 | LTICR                        | Lite Timer Input Capture Register                             | xxh               | Read Only         |  |

| 000Dh             |                 | ATCSR                        | Timer Control/Status Register                                 | 0x00 0000b        | R/W               |  |

| 000Eh             |                 | CNTR1H                       | Counter Register 1 High                                       | 00h               | Read Only         |  |

| 000Fh             |                 | CNTR1L                       | Counter Register 1 Low                                        | 00h               | Read Only         |  |

| 0010h             |                 | ATR1H                        | Auto-Reload Register 1 High                                   | 00h               | R/W               |  |

| 0011h             |                 | ATR1L                        | Auto-Reload Register 1 Low                                    | 00h               | R/W               |  |

| 0012h             |                 | PWMCR                        | PWM Output Control Register                                   | 00h               | R/W               |  |

| 0013h             |                 | PWM0CSR                      | PWM 0 Control/Status Register                                 | 00h               | R/W               |  |

| 0014h             |                 | PWM1CSR                      | PWM 1 Control/Status Register                                 | 00h               | R/W               |  |

| 0015h             |                 | PWM2CSR                      | PWM 2 Control/Status Register                                 | 00h               | R/W               |  |

| 0016h             |                 | PWM3CSR                      | PWM 3 Control/Status Register                                 | 00h               | R/W               |  |

| 0017h             | AUTO-           | DCR0H                        | PWM 0 Duty Cycle Register High                                | 00h               | R/W               |  |

| 0018h             | RELOAD          | DCR0L                        | PWM 0 Duty Cycle Register Low                                 | 00h               | R/W               |  |

| 0019h             | TIMER 3         | DCR1H                        | PWM 1 Duty Cycle Register High                                | 00h               | R/W               |  |

| 001Ah             |                 | DCR1L                        | PWM 1 Duty Cycle Register Low                                 | 00h               | R/W               |  |

| 001Bh             |                 | DCR2H                        | PWM 2 Duty Cycle Register High                                | 00h               | R/W               |  |

| 001Ch             |                 | DCR2L                        | PWM 2 Duty Cycle Register Low                                 | 00h               | R/W               |  |

| 001Dh             |                 | DCR3H                        | PWM 3 Duty Cycle Register High                                | 00h               | R/W               |  |

| 001Eh             |                 |                              | PWM 3 Duty Cycle Register Low                                 | 00h               | R/W<br>Bood Only  |  |

| 001Fh<br>0020h    |                 | ATICRH<br>ATICRL             | Input Capture Register High                                   | 00h               | Read Only         |  |

| 0020n<br>0021h    |                 | ATCSR2                       | Input Capture Register Low<br>Timer Control/Status Register 2 | 00h<br>03h        | Read Only<br>R/W  |  |

| 0021h<br>0022h    |                 | BREAKCR                      | Break Control Register                                        | 03h<br>00h        | R/W               |  |

| 0022n<br>0023h    |                 | ATR2H                        | Auto-Reload Register 2 High                                   | 00h               | R/W<br>R/W        |  |

| 0023n<br>0024h    |                 | ATR2H<br>ATR2L               | Auto-Reload Register 2 High                                   | 00h               | R/W<br>R/W        |  |

| 002411<br>0025h   |                 | DTGR                         | Dead Time Generator Register                                  | 00h               | R/W               |  |

| 0026h to<br>002Dh |                 |                              | Reserved area (8 bytes)                                       |                   | 1                 |  |

| 002Eh             | WDG             | WDGCR                        | Watchdog Control Register                                     | 7Fh               | R/W               |  |

| 0002Fh            | FLASH           | FCSR                         | Flash Control/Status Register                                 | 00h               | R/W               |  |

| 00030h            | EEPROM          | EECSR                        | Data EEPROM Control/Status Register                           | 00h               | R/W               |  |

## DATA EEPROM (Cont'd)

57/

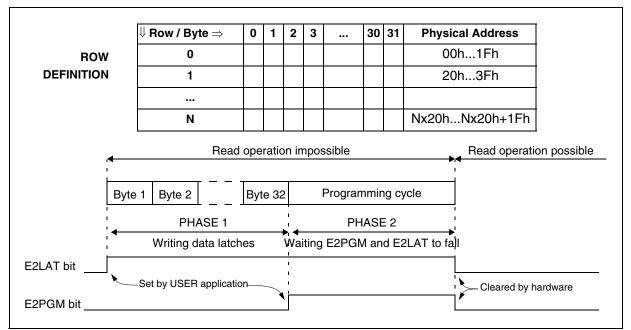

Figure 8. Data E<sup>2</sup>PROM Write Operation

**Note:** If a programming cycle is interrupted (by a reset action), the integrity of the data in memory is not guaranteed.

## DATA EEPROM (Cont'd)

### **5.7 REGISTER DESCRIPTION**

# EEPROM CONTROL/STATUS REGISTER (EEC-SR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   | 0           |

|---|---|---|---|---|---|-------------|

| 0 | 0 | 0 | 0 | 0 | 0 | E2LAT E2PGM |

Bits 7:2 = Reserved, forced by hardware to 0.

#### Bit 1 = E2LAT Latch Access Transfer

This bit is set by software. It is cleared by hardware at the end of the programming cycle. It can only be cleared by software if the E2PGM bit is cleared.

0: Read mode

1: Write mode

<u>ارک</u>

### Bit 0 = **E2PGM** *Programming control and status*

This bit is set by software to begin the programming cycle. At the end of the programming cycle, this bit is cleared by hardware.

0: Programming finished or not yet started

1: Programming cycle is in progress

**Note**: if the E2PGM bit is cleared during the programming cycle, the memory data is not guaranteed

#### Table 4. DATA EEPROM Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label    | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0          |

|-------------------|----------------------|---|---|---|---|---|---|------------|------------|

| 0030h             | EECSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | E2LAT<br>0 | E2PGM<br>0 |

## 7 SUPPLY, RESET AND CLOCK MANAGEMENT

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components.

#### Main features

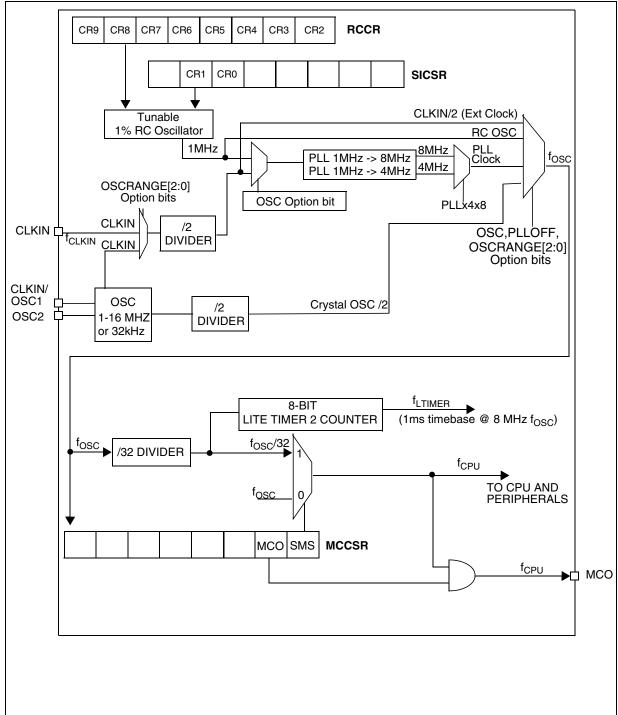

- Clock Management

- 1 MHz internal RC oscillator (enabled by option byte, available on ST7LITE35 and ST7LITE39 devices only)

- 1 to 16 MHz or 32kHz External crystal/ceramic resonator (selected by option byte)

- External Clock Input (enabled by option byte)

- PLL for multiplying the frequency by 8 or 4 (enabled by option byte)

- Reset Sequence Manager (RSM)

- System Integrity Management (SI)

- Main supply Low voltage detection (LVD) with reset generation (enabled by option byte)

- Auxiliary Voltage detector (AVD) with interrupt capability for monitoring the main supply (enabled by option byte)

## 7.1 INTERNAL RC OSCILLATOR ADJUSTMENT

The device contains an internal RC oscillator with an accuracy of 1% for a given device, temperature and voltage range (4.5V-5.5V). It must be calibrated to obtain the frequency required in the application. This is done by software writing a 8-bit calibration value in the RCCR (RC Control Register) and in the bits [6:5] in the SICSR (SI Control Status Register).

Whenever the microcontroller is reset, the RCCR returns to its default value (FFh), i.e. each time the device is reset, the calibration value must be loaded in the RCCR. Predefined calibration values are stored in EEPROM for 3V and 5V V<sub>DD</sub> supply voltages at 25°C, as shown in the following table.

| RCCR   | Conditions                                    | ST7LITE3                           |  |  |

|--------|-----------------------------------------------|------------------------------------|--|--|

| ncon   | Conditions                                    | Addresses                          |  |  |

| RCCRH0 | V <sub>DD</sub> =5V                           | DEE0h <sup>1)</sup> (CR[9:2] bits) |  |  |

| RCCRL0 | T <sub>A</sub> =25°C<br>f <sub>RC</sub> =1MHz | DEE1h <sup>1)</sup> (CR[1:0] bits) |  |  |

| RCCRH1 | V <sub>DD</sub> =3.3V                         | DEE2h <sup>1)</sup> (CR[9:2] bits) |  |  |

| RCCRL1 | T <sub>A</sub> =25°C<br>f <sub>RC</sub> =1MHz | DEE3h <sup>1)</sup> (CR[1:0] bits) |  |  |

1. DEE0h, DEE1h, DEE2h and DEE3h addresses are located in a reserved area of non-volatile memory. They are read-only bytes for the application code. This area cannot be erased or programmed by any ICC operation.

For compatibility reasons with the SICSR register, CR[1:0] bits are stored in the 5th and 6th position of DEE1 and DEE3 addresses.

#### Note:

- In 38-pulse ICC mode, the internal RC oscillator is forced as a clock source, regardless of the selection in the option byte. For ST7LITE30 devices which do not support the internal RC oscillator, the "option byte disabled" mode must be used (35-pulse ICC mode entry, clock provided by the tool).

- See "ELECTRICAL CHARACTERISTICS" on page 131. for more information on the frequency and accuracy of the RC oscillator.

- To improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the V<sub>DD</sub> and V<sub>SS</sub> pins as close as possible to the ST7 device

- These bytes are systematically programmed by ST, including on FASTROM devices. Consequently, customers intending to use FASTROM service must not use these bytes.

- RCCR0 and RCCR1 calibration values will not be erased if the read-out protection bit is reset after it has been set. See "Read out Protection" on page 14.

**Caution:** If the voltage or temperature conditions change in the application, the frequency may need to be recalibrated.

Refer to application note AN1324 for information on how to calibrate the RC frequency using an external reference signal.

## 7.2 PHASE LOCKED LOOP

The PLL can be used to multiply a 1MHz frequency from the RC oscillator or the external clock by 4 or 8 to obtain  $f_{OSC}$  of 4 or 8 MHz. The PLL is enabled and the multiplication factor of 4 or 8 is selected by 2 option bits.

- The x4 PLL is intended for operation with  $V_{DD}$  in the 2.7V to 3.3V range

- The x8 PLL is intended for operation with  $V_{DD}$  in the 3.3V to 5.5V range

Refer to Section 15.1 for the option byte description.

If the PLL is disabled and the RC oscillator is enabled, then  $f_{OSC}$  = 1MHz.

Figure 13. Clock Management Block Diagram

**\$7**

## RESET SEQUENCE MANAGER (Cont'd)

The RESET pin is an asynchronous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in the electrical characteristics section.

#### 7.5.3 External Power-On RESET

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until  $V_{DD}$  is over the minimum level specified for the selected  $f_{OSC}$  frequency.

A proper reset signal for a slow rising  $V_{DD}$  supply can generally be provided by an external RC network connected to the RESET pin.

# 7.5.4 Internal Low Voltage Detector (LVD) RESET

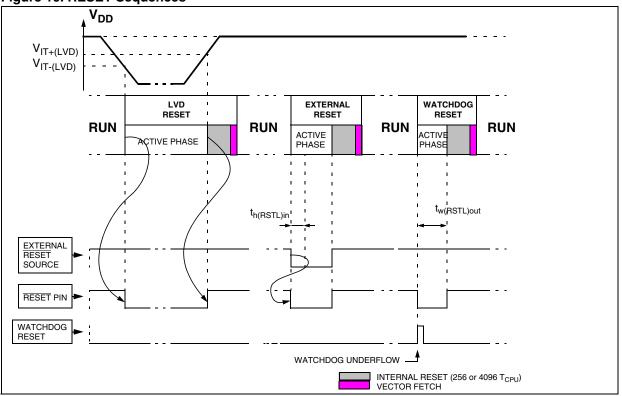

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

The device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low when  $V_{DD}{<}V_{IT{+}}$  (rising edge) or  $V_{DD}{<}V_{IT{-}}$  (falling edge) as shown in Figure 16.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{g(VDD)}$  to avoid parasitic resets.

#### 7.5.5 Internal Watchdog RESET

The RESET sequence generated by a internal Watchdog counter overflow is shown in Figure 16.

Starting from the Watchdog counter underflow, the device RESET pin acts as an output that is pulled low during at least  $t_{w(RSTL)out}$ .

## Figure 16. RESET Sequences

57/

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 7.6.4 Register Description

### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

Read/Write

Reset Value: 0110 0xx0 (6xh)

| 7 |     |     |           |        |       |      | 0     |

|---|-----|-----|-----------|--------|-------|------|-------|

| 0 | CR1 | CR0 | WDG<br>RF | LOCKED | LVDRF | AVDF | AVDIE |

Bit 7 = Reserved, must be kept cleared.

# Bits 6:5 = **CR[1:0]** *RC* Oscillator Frequency Adjustment bits

These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. Refer to section 7.3 on page 24

#### Bit 4 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (by reading SICSR register) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

#### Bit 3 = LOCKED PLL Locked Flag

This bit is set by hardware. It is cleared only by a power-on reset. It is set automatically when the PLL reaches its operating frequency.

0: PLL not locked

1: PLL locked

#### Bit 2 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (by reading). When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

#### Bit 1 = AVDF Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit is set. Refer to Figure 19 and to Section 7.6.2.1 for additional details. 0:  $V_{DD}$  over AVD threshold

1: V<sub>DD</sub> under AVD threshold

### Bit 0 = **AVDIE** Voltage Detector interrupt enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag is set. The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.

0: AVD interrupt disabled 1: AVD interrupt enabled

### **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

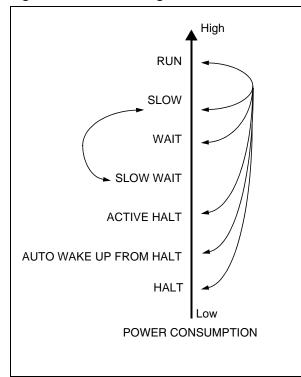

## 9 POWER SAVING MODES

## 9.1 INTRODUCTION

To give a large measure of flexibility to the application in terms of power consumption, five main power saving modes are implemented in the ST7 (see Figure 21):

- Slow

- Wait (and Slow-Wait)

- Active Halt

- Auto Wake up From Halt (AWUFH)

- Halt

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

#### Figure 21. Power Saving Mode Transitions

### 9.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

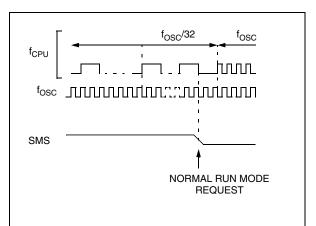

SLOW mode is controlled by the SMS bit in the MCCSR register which enables or disables Slow mode.

In this mode, the oscillator frequency is divided by 32. The CPU and peripherals are clocked at thislower frequency.

**Note**: SLOW-WAIT mode is activated when entering WAIT mode while the device is already in SLOW mode.

Figure 22. SLOW Mode Clock Transition

## 10 I/O PORTS

### **10.1 INTRODUCTION**

The I/O ports allow data transfer. An I/O port can contain up to 8 pins. Each pin can be programmed independently either as a digital input or digital output. In addition, specific pins may have several other functions. These functions can include external interrupt, alternate signal input/output for onchip peripherals or analog input.

#### **10.2 FUNCTIONAL DESCRIPTION**

A Data Register (DR) and a Data Direction Register (DDR) are always associated with each port. The Option Register (OR), which allows input/output options, may or may not be implemented. The following description takes into account the OR register. Refer to the Port Configuration table for device specific information.

An I/O pin is programmed using the corresponding bits in the DDR, DR and OR registers: bit x corresponding to pin x of the port.

Figure 31 shows the generic I/O block diagram.

#### 10.2.1 Input Modes

Clearing the DDRx bit selects input mode. In this mode, reading its DR bit returns the digital value from that I/O pin.

If an OR bit is available, different input modes can be configured by software: floating or pull-up. Refer to I/O Port Implementation section for configuration.

#### Notes:

1. Writing to the DR modifies the latch value but does not change the state of the input pin.

2. Do not use read/modify/write instructions (BSET/BRES) to modify the DR register.

#### **External Interrupt Function**

Depending on the device, setting the ORx bit while in input mode can configure an I/O as an input with interrupt. In this configuration, a signal edge or level input on the I/O generates an interrupt request via the corresponding interrupt vector (eix).

Falling or rising edge sensitivity is programmed independently for each interrupt vector. The External Interrupt Control Register (EICR) or the Miscellaneous Register controls this sensitivity, depending on the device.

A device may have up to 7 external interrupts. Several pins may be tied to one external interrupt vector. Refer to Pin Description to see which ports have external interrupts. If several I/O interrupt pins on the same interrupt vector are selected simultaneously, they are logically combined. For this reason if one of the interrupt pins is tied low, it may mask the others.

External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Modifying the sensitivity bits will clear any pending interrupts.

#### 10.2.2 Output Modes

Setting the DDRx bit selects output mode. Writing to the DR bits applies a digital value to the I/O through the latch. Reading the DR bits returns the previously stored value.

If an OR bit is available, different output modes can be selected by software: push-pull or opendrain. Refer to I/O Port Implementation section for configuration.

#### DR Value and Output Pin Status

| DR | Push-Pull       | Open-Drain      |

|----|-----------------|-----------------|

| 0  | V <sub>OL</sub> | V <sub>OL</sub> |

| 1  | V <sub>OH</sub> | Floating        |

#### 10.2.3 Alternate Functions

Many ST7s I/Os have one or more alternate functions. These may include output signals from, or input signals to, on-chip peripherals. The Device Pin Description table describes which peripheral signals can be input/output to which ports.

A signal coming from an on-chip peripheral can be output on an I/O. To do this, enable the on-chip peripheral as an output (enable bit in the peripheral's control register). The peripheral configures the I/O as an output and takes priority over standard I/ O programming. The I/O's state is readable by addressing the corresponding I/O data register.

Configuring an I/O as floating enables alternate function input. It is not recommended to configure an I/O as pull-up as this will increase current consumption. Before using an I/O as an alternate input, configure it without interrupt. Otherwise spurious interrupts can occur.

Configure an I/O as input floating for an on-chip peripheral signal which can be input and output.

#### Caution:

I/Os which can be configured as both an analog and digital alternate function need special attention. The user must control the peripherals so that the signals do not arrive at the same time on the same pin. If an external clock is used, only the clock alternate function should be employed on that I/O pin and not the other alternate function.

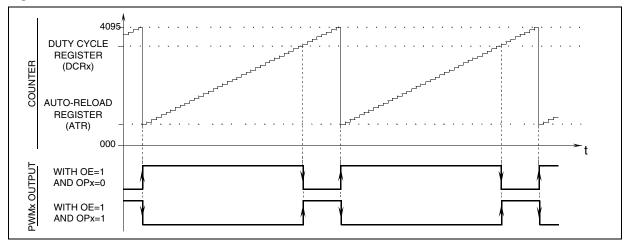

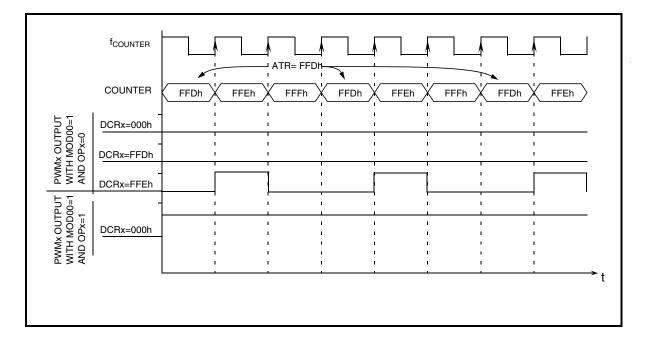

## DUAL 12-BIT AUTORELOAD TIMER 3 (Cont'd)

#### Figure 37. PWM Function

<u>(</u>ح)

## SERIAL PERIPHERAL INTERFACE (cont'd)

SPI CONTROL/STATUS REGISTER (SPICSR)

Read/Write (some bits Read Only) Reset Value: 0000 0000 (00h)

| 7    |      |     |      |   |     |     | 0   |

|------|------|-----|------|---|-----|-----|-----|

| SPIF | WCOL | OVR | MODF | - | SOD | SSM | SSI |

Bit 7 = **SPIF** Serial Peripheral Data Transfer Flag (Read only)

This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).

- 0: Data transfer is in progress or the flag has been cleared.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

Bit 6 = **WCOL** Write Collision status (Read only)

This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 53).

0: No write collision occurred

1: A write collision has been detected

Bit 5 = **OVR** SPI Overrun error (Read only)

This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (See Section 11.4.5.2). An interrupt is generated if SPIE = 1 in the SPICR register. The OVR bit is cleared by software reading the SPICSR register. 0: No overrun error

1: Overrun error detected

#### Bit 4 = **MODF** Mode Fault flag (Read only)

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 11.4.5.1 Master Mode Fault (MODF)). An SPI interrupt can be generated if SPIE = 1 in the SPICR register. This bit is cleared by a software sequence (An access to the SPICSR register while MODF = 1 followed by a write to the SPICR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bit 3 = Reserved, must be kept cleared.

#### Bit 2 = SOD SPI Output Disable

This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode) 0: SPI output enabled (if SPE = 1) 1: SPI output disabled

### Bit 1 = **SSM** *SS Management*

This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See Section 11.4.3.2 Slave Select Management.

- 0: Hardware management (SS managed by external pin)

- 1: Software management (internal SS signal controlled by SSI bit. External SS pin free for general-purpose I/O)

### Bit 0 = **SSI** *SS* Internal Mode

This bit is set and cleared by software. It <u>acts</u> as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.

0: Slave selected

1: Slave deselected

## SPI DATA I/O REGISTER (SPIDR)

Read/Write

Reset Value: Undefined

| /  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

**Warning:** A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see Figure 48).

Δ

## LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

## 11.5.5 SCI Mode - Functional Description

#### **Conventional Baud Rate Generator Mode**

The block diagram of the Serial Control Interface in conventional baud rate generator mode is shown in Figure 55.

It uses four registers:

57/

- 2 control registers (SCICR1 and SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

#### **Extended Prescaler Mode**

Two additional prescalers are available in extended prescaler mode. They are shown in Figure 57.

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

#### Figure 56. Word Length Programming

#### 11.5.5.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 56).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as a continuous logic high level for 10 (or 11) full bit times.

A Break character is a character with a sufficient number of low level bits to break the normal data format followed by an extra "1" bit to acknowledge the start bit.

| 9-bit Word length (M bit is set) Data Character |      |        |                           |        |       |       |       |                    | Possible<br>Parity<br>Bit | )           | Next Data Character<br>Next |

|-------------------------------------------------|------|--------|---------------------------|--------|-------|-------|-------|--------------------|---------------------------|-------------|-----------------------------|

| <br>Start<br>Bit                                | Bit0 | Bit1   | Bit2                      | Bit3   | Bit4  | Bit5  | Bit6  | Bit7               | Bit8                      | Stop<br>Bit | Start<br>Bit                |

|                                                 |      | l      | dle Lin                   | e      |       |       |       |                    |                           | Dit         | Start<br>Bit                |

| <br>1                                           |      | E      | Break C                   | Charac | ter   |       |       |                    |                           |             | Extra Start<br>'1' Bit      |

| <br>8-bi                                        |      | d leng | <b>th (M t</b><br>Data Cl |        | -     |       |       | Possi<br>Par<br>Bi | ity<br>t                  | Ne          | Next Data Character         |

| Bit                                             |      | t0 Bit | 1 Bit                     | 2 Bit  | 3 Bit | 4 Bit | 5 Bit | 6 Bit              | t7 Sto<br>Bit             |             | t                           |

|                                                 |      | le     | dle Lin                   | e      |       |       |       |                    |                           | Sta<br>Bi   |                             |

|                                                 |      | E      | Break C                   | Charac | ter   |       |       |                    |                           | Ext<br>1    | ra Start<br>Bit             |

## LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

SCICR2 register is set, the LHDM bit selects the Wake-Up method (replacing the WAKE bit). 0: LIN Synch Break Detection Method 1: LIN Identifier Field Detection Method

#### Bit 2 = LHIE LIN Header Interrupt Enable

This bit is set and cleared by software. It is only usable in LIN Slave mode.

0: LIN Header Interrupt is inhibited.

1: An SCI interrupt is generated whenever LHDF = 1.

#### Bit 1 = LHDF LIN Header Detection Flag

This bit is set by hardware when a LIN Header is detected and cleared by a software sequence (an access to the SCISR register followed by a read of the SCICR3 register). It is only usable in LIN Slave mode.

0: No LIN Header detected.

1: LIN Header detected.

**Notes:** The header detection method depends on the LHDM bit:

- If LHDM = 0, a header is detected as a LIN Synch Break.

- If LHDM = 1, a header is detected as a LIN Identifier, meaning that a LIN Synch Break Field + a LIN Synch Field + a LIN Identifier Field have been consecutively received.

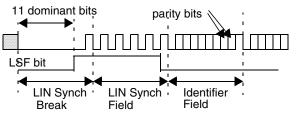

#### Bit 0 = LSF LIN Synch Field State

5/

This bit indicates that the LIN Synch Field is being analyzed. It is only used in LIN Slave mode. In Auto Synchronization Mode (LASE bit = 1), when the SCI is in the LIN Synch Field State it waits or counts the falling edges on the RDI line.

It is set by hardware as soon as a LIN Synch Break is detected and cleared by hardware when the LIN Synch Field analysis is finished (see Figure 65). This bit can also be cleared by software to exit LIN Synch State and return to idle mode.

0: The current character is not the LIN Synch Field

1: LIN Synch Field State (LIN Synch Field undergoing analysis)

#### Figure 65. LSF Bit Set and Clear

#### LIN DIVIDER REGISTERS

LDIV is coded using the two registers LPR and LP-FR. In LIN Slave mode, the LPR register is accessible at the address of the SCIBRR register and the LPFR register is accessible at the address of the SCIETPR register.

#### LIN PRESCALER REGISTER (LPR)

#### **Read/Write**

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| LPR7 | LPR6 | LPR5 | LPR4 | LPR3 | LPR2 | LPR1 | LPR0 |

#### **LPR[7:0]** *LIN Prescaler (mantissa of LDIV)*

These 8 bits define the value of the mantissa of the LIN Divider (LDIV):

| LPR[7:0] | Rounded Mantissa (LDIV) |

|----------|-------------------------|

| 00h      | SCI clock disabled      |

| 01h      | 1                       |

|          |                         |

| FEh      | 254                     |

| FFh      | 255                     |

**Caution:** LPR and LPFR registers have different meanings when reading or writing to them. Consequently bit manipulation instructions (BRES or BSET) should never be used to modify the LPR[7:0] bits, or the LPFR[3:0] bits.

## INSTRUCTION GROUPS (cont'd)

| Mnemo | Description                | Function/Example    | Dst    | Src | Н | I | Ν | Ζ | С |

|-------|----------------------------|---------------------|--------|-----|---|---|---|---|---|

| ADC   | Add with Carry             | A = A + M + C       | А      | М   | Н |   | Ν | Z | С |

| ADD   | Addition                   | A=A+M               | А      | М   | Н |   | Ν | Z | С |

| AND   | Logical And                | A = A . M           | А      | М   |   |   | Ν | Z |   |

| BCP   | Bit compare A, Memory      | tst (A . M)         | А      | М   |   |   | Ν | Z |   |

| BRES  | Bit Reset                  | bres Byte, #3       | М      |     |   |   |   |   |   |

| BSET  | Bit Set                    | bset Byte, #3       | М      |     |   |   |   |   |   |

| BTJF  | Jump if bit is false (0)   | btjf Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| BTJT  | Jump if bit is true (1)    | btjt Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| CALL  | Call subroutine            |                     |        |     |   |   |   |   |   |

| CALLR | Call subroutine relative   |                     |        |     |   |   |   |   |   |

| CLR   | Clear                      |                     | reg, M |     |   |   | 0 | 1 |   |

| СР    | Arithmetic Compare         | tst(Reg - M)        | reg    | М   |   |   | Ν | Z | С |

| CPL   | One Complement             | A = FFH-A           | reg, M |     |   |   | Ν | Z | 1 |

| DEC   | Decrement                  | dec Y               | reg, M |     |   |   | Ν | Z |   |

| HALT  | Halt                       |                     |        |     |   | 0 |   |   |   |

| IRET  | Interrupt routine return   | Pop CC, A, X, PC    |        |     | Н | Ι | Ν | Z | С |

| INC   | Increment                  | inc X               | reg, M |     |   |   | Ν | Z |   |

| JP    | Absolute Jump              | jp [TBL.w]          |        |     |   |   |   |   |   |

| JRA   | Jump relative always       |                     |        |     |   |   |   |   |   |

| JRT   | Jump relative              |                     |        |     |   |   |   |   |   |

| JRF   | Never jump                 | jrf *               |        |     |   |   |   |   |   |

| JRIH  | Jump if ext. interrupt = 1 |                     |        |     |   |   |   |   |   |

| JRIL  | Jump if ext. interrupt = 0 |                     |        |     |   |   |   |   |   |

| JRH   | Jump if H = 1              | H = 1 ?             |        |     |   |   |   |   |   |

| JRNH  | Jump if H = 0              | H = 0 ?             |        |     |   |   |   |   |   |

| JRM   | Jump if I = 1              | I = 1 ?             |        |     |   |   |   |   |   |

| JRNM  | Jump if I = 0              | I = 0 ?             |        |     |   |   |   |   |   |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?             |        |     |   |   |   |   |   |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?             |        |     |   |   |   |   |   |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?             |        |     |   |   |   |   |   |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?             |        |     |   |   |   |   |   |

| JRC   | Jump if C = 1              | C = 1 ?             |        |     |   |   |   |   |   |

| JRNC  | Jump if C = 0              | C = 0 ?             |        |     |   |   |   |   |   |

| JRULT | Jump if C = 1              | Unsigned <          |        |     |   |   |   |   |   |

| JRUGE | Jump if C = 0              | Jmp if unsigned >=  |        |     |   |   |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >          |        |     |   |   |   |   |   |

## **OPERATING CONDITIONS** (Cont'd)

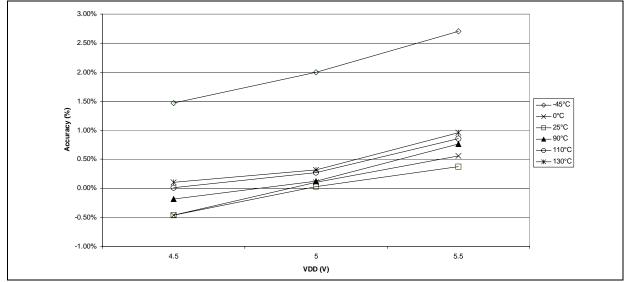

Figure 70. Typical accuracy with RCCR=RCCR0 vs  $V_{DD}$ = 4.5 to 5.5V and Temperature

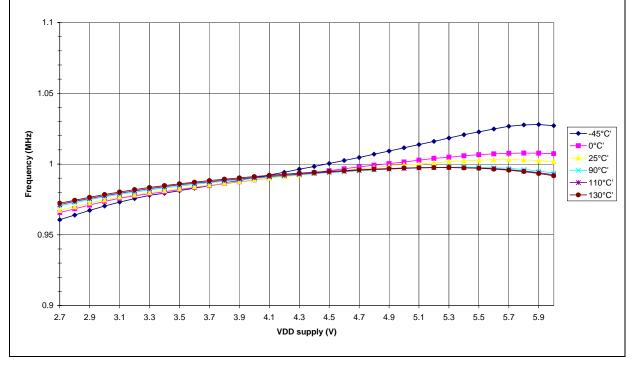

Figure 71. Typical RCCR0 vs  $V_{DD}$  and Temperature

57

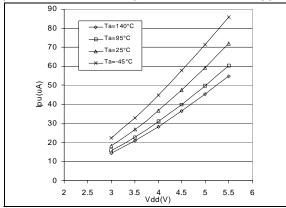

## Figure 85. Typical $I_{PU}$ vs. $V_{DD}$ with $V_{IN}=V_{SS}$

## I/O PORT PIN CHARACTERISTICS (Cont'd)

## 13.8.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                          | Parameter                                                                                                |                     | Conditions                                   | Min                  | Тур  | Мах  | Unit |

|---------------------------------|----------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------|----------------------|------|------|------|

|                                 | Output low level voltage for a standard I/O                                                              |                     | I <sub>IO</sub> =+5mA T <sub>A</sub> ≤125°C  |                      | 0.65 | 1.0  |      |

| V <sub>OL</sub> <sup>1)</sup>   | pin when 8 pins are sunk at same time (see Figure 88)                                                    |                     | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.25 | 0.4  |      |

| VOL /                           | Output low level voltage for a high sink I/O                                                             | =5V                 | I <sub>IO</sub> =+20mA,T <sub>A</sub> ≤125°C |                      | 1.05 | 1.3  |      |

|                                 | pin when 4 pins are sunk at same time (see Figure 91)                                                    | V <sub>DD</sub> =5V | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.4  | 0.75 |      |

| V 2)                            | Output high level voltage for an I/O pin                                                                 |                     | I <sub>IO</sub> = -5mA,T <sub>A</sub> ≤125°C | V <sub>DD</sub> -1.5 | 4.30 |      |      |

| V <sub>OH</sub> <sup>2)</sup>   | when 4 pins are sourced at same time (see Figure 94)                                                     |                     | I <sub>IO</sub> = -2mA T <sub>A</sub> ≤125°C | V <sub>DD</sub> -0.8 | 4.70 |      |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O<br>pin when 8 pins are sunk at same time<br>(see Figure 87)  |                     | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.25 |      |      |

| VOL                             | Output low level voltage for a high sink I/O<br>pin when 4 pins are sunk at same time (see<br>Figure 90) | V <sub>DD</sub> =4V | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.35 |      | v    |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see Figure 93)      |                     | I <sub>IO</sub> = -2mA T <sub>A</sub> ≤125°C |                      | 3.70 |      |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O<br>pin when 8 pins are sunk at same time<br>(see Figure 86)  | V <sub>DD</sub> =3V | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.30 |      |      |

| VOL / /                         | Output low level voltage for a high sink I/O<br>pin when 4 pins are sunk at same time (see<br>Figure 89) |                     | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.40 |      |      |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see Figure 92)      |                     | I <sub>IO</sub> = -2mA T <sub>A</sub> ≤125°C |                      | 2.60 |      |      |

#### Notes:

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

**2.** The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

3. Not tested in production, based on characterization results.

## **OPTION BYTES** (Cont'd)

|                  |           |    |             | OPTIC | N BYT | E 0  |      | OPTION BYTE 1 |             |            |      |     |         |          |           |             |

|------------------|-----------|----|-------------|-------|-------|------|------|---------------|-------------|------------|------|-----|---------|----------|-----------|-------------|

|                  | 7         |    |             |       |       |      |      | 0             | 7           |            |      |     |         |          |           | 0           |

|                  | AWU<br>CK | OS | CRAN<br>2:0 | GE    | SEC1  | SEC0 | FMPR | FMPW          | PLL<br>x4x8 | PLL<br>OFF | Res. | OSC | L\<br>1 | /D<br>:0 | WDG<br>SW | WDG<br>HALT |

| Default<br>Value | 1         | 1  | 1           | 1     | 1     | 1    | 0    | 0             | 1           | 1          | 1    | 0   | 1       | 1        | 1         | 1           |

#### **OPTION BYTE 1**

OPT 7 = **PLLx4x8** *PLL Factor Selection.* 0: PLLx4 1: PLLx8

OPT 6 = **PLLOFF** *PLL Disable* This option bit enables or disables the PLL.

0: PLL enabled

1: PLL disabled (bypassed)

OPT 5 = Reserved. Must always be set to 1.

OPT 4 = **OSC** RC Oscillator Selection

This option bit enables to select the internal RC Oscillator.

0: RC Oscillator on

1: RC Oscillator off

#### Notes:

- RC oscillator available on ST7LITE35 and ST7LITE39 devices only

- If the RC oscillator is selected, then to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the V<sub>DD</sub> and V<sub>SS</sub> pins as close as possible to the ST7 device.

OPT 3:2 = **LVD[1:0]** Low Voltage Selection These option bits enable the voltage detection block (LVD and AVD) with a selected threshold to the LVD and AVD.

| Configuration             | VD1 | VD0 |

|---------------------------|-----|-----|

| LVD Off                   | 1   | 1   |

| Highest Voltage Threshold | 1   | 0   |

| Medium Voltage Threshold  | 0   | 1   |

| Lowest Voltage Threshold  | 0   | 0   |

OPT 1 = **WDGSW** Hardware or Software Watchdog

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT 0 = WDG HALT Watchdog Reset on Halt

0: No reset generation when entering HALT mode

1: Reset generation when entering HALT mode