#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

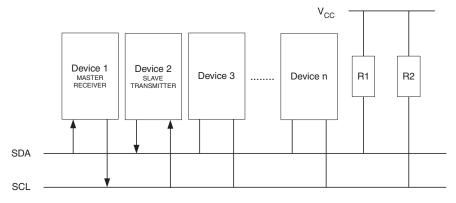

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-TQFP                                                                  |

| Supplier Device Package    | 32-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168-20au |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.2 SRAM Data Memory

Figure 5-3 shows how the ATmega48/88/168 SRAM Memory is organized.

The ATmega48/88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

The lower 768/1280/1280 data memory locations address both the Register File, the I/O memory, Extended I/O memory, and the internal data SRAM. The first 32 locations address the Register File, the next 64 location the standard I/O memory, then 160 locations of Extended I/O memory, and the next 512/1024/1024 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, 160 Extended I/O Registers, and the 512/1024/1024 bytes of internal data SRAM in the ATmega48/88/168 are all accessible through all these addressing modes. The Register File is described in "General Purpose Register File" on page 10.

#### Figure 5-3. Data Memory Map

#### **Data Memory**

| 32 Registers<br>64 I/O Registers     | 0x0000 - 0x001F<br>0x0020 - 0x005F |

|--------------------------------------|------------------------------------|

| 160 Ext I/O Reg.                     | 0x0060 - 0x00FF                    |

|                                      | 0x0100                             |

| Internal SRAM<br>(512/1024/1024 x 8) |                                    |

|                                      | 0x02FF/0x04FF/0x04FF               |

#### 5.2.1 Data Memory Access Times

This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two  $clk_{CPU}$  cycles as described in Figure 5-4.

is set, any write to EEPMn will be ignored. During reset, the EEPMn bits will be reset to 0b00 unless the EEPROM is busy programming.

|   | EEPM1 | EEPM0 | Programming<br>Time | Operation                                           |

|---|-------|-------|---------------------|-----------------------------------------------------|

| Γ | 0     | 0     | 3.4 ms              | Erase and Write in one operation (Atomic Operation) |

|   | 0     | 1     | 1.8 ms              | Erase Only                                          |

|   | 1     | 0     | 1.8 ms              | Write Only                                          |

|   | 1     | 1     | _                   | Reserved for future use                             |

#### Bit 3 – EERIE: EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM Ready Interrupt if the I bit in SREG is set. Writing EERIE to zero disables the interrupt. The EEPROM Ready interrupt generates a constant interrupt when EEPE is cleared. The interrupt will not be generated during EEPROM write or SPM.

#### • Bit 2 – EEMPE: EEPROM Master Write Enable

The EEMPE bit determines whether setting EEPE to one causes the EEPROM to be written. When EEMPE is set, setting EEPE within four clock cycles will write data to the EEPROM at the selected address If EEMPE is zero, setting EEPE will have no effect. When EEMPE has been written to one by software, hardware clears the bit to zero after four clock cycles. See the description of the EEPE bit for an EEPROM write procedure.

#### • Bit 1 – EEPE: EEPROM Write Enable

The EEPROM Write Enable Signal EEPE is the write strobe to the EEPROM. When address and data are correctly set up, the EEPE bit must be written to one to write the value into the EEPROM. The EEMPE bit must be written to one before a logical one is written to EEPE, otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 3 and 4 is not essential):

- 1. Wait until EEPE becomes zero.

- 2. Wait until SELFPRGEN in SPMCSR becomes zero.

- 3. Write new EEPROM address to EEAR (optional).

- 4. Write new EEPROM data to EEDR (optional).

- 5. Write a logical one to the EEMPE bit while writing a zero to EEPE in EECR.

- 6. Within four clock cycles after setting EEMPE, write a logical one to EEPE.

The EEPROM can not be programmed during a CPU write to the Flash memory. The software must check that the Flash programming is completed before initiating a new EEPROM write. Step 2 is only relevant if the software contains a Boot Loader allowing the CPU to program the Flash. If the Flash is never being updated by the CPU, step 2 can be omitted. See "Boot Loader Support – Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264 for details about Boot programming.

**Caution:** An interrupt between step 5 and step 6 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR or EEDR Register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the Global Interrupt Flag cleared during all the steps to avoid these problems.

## 6.7 128 kHz Internal Oscillator

The 128 kHz internal Oscillator is a low power Oscillator providing a clock of 128 kHz. The frequency is nominal at 3V and 25°C. This clock may be select as the system clock by programming the CKSEL Fuses to "11" as shown in Table 6-10.

Table 6-10. 128 kHz Internal Oscillator Operating Modes

| Nominal Frequency | CKSEL30 |

|-------------------|---------|

| 128 kHz           | 0011    |

Note: 1. The frequency is preliminary value. Actual value is TBD.

When this clock source is selected, start-up times are determined by the SUT Fuses as shown in Table 6-11.

| Power Conditions    | Start-up Time from Power-<br>down and Power-save | Additional Delay from<br>Reset | SUT10 |

|---------------------|--------------------------------------------------|--------------------------------|-------|

| BOD enabled         | 6 CK                                             | 14CK <sup>(1)</sup>            | 00    |

| Fast rising power   | 6 CK                                             | 14CK + 4 ms                    | 01    |

| Slowly rising power | 6 CK                                             | 14CK + 64 ms                   | 10    |

|                     | Reserved                                         |                                | 11    |

Table 6-11.

Start-up Times for the 128 kHz Internal Oscillator

Note: 1. If the RSTDISBL fuse is programmed, this start-up time will be increased to 14CK + 4.1 ms to ensure programming mode can be entered.

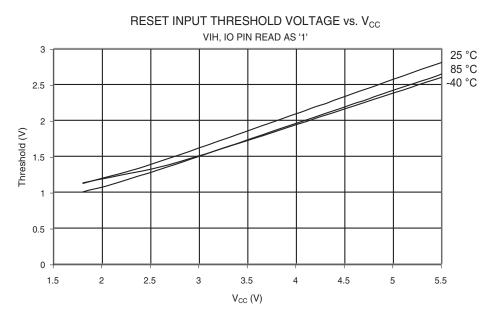

### 6.8 External Clock

To drive the device from an external clock source, XTAL1 should be driven as shown in Figure 6-4 on page 33. To run the device on an external clock, the CKSEL Fuses must be programmed to "0000" (see Table 6-12).

#### Table 6-12. Crystal Oscillator Clock Frequency

| Frequency  | CKSEL30 |

|------------|---------|

| 0 - 20 MHz | 0011    |

#### Figure 6-4. External Clock Drive Configuration

When this clock source is selected, start-up times are determined by the SUT Fuses as shown in Table 6-13.

#### 7.6.1 Power Reduction Register - PRR

| Bit           | 7     | 6      | 5      | 4 | 3      | 2     | 1        | 0     |     |

|---------------|-------|--------|--------|---|--------|-------|----------|-------|-----|

|               | PRTWI | PRTIM2 | PRTIM0 | - | PRTIM1 | PRSPI | PRUSART0 | PRADC | PRR |

| Read/Write    | R/W   | R/W    | R/W    | R | R/W    | R/W   | R/W      | R/W   |     |

| Initial Value | 0     | 0      | 0      | 0 | 0      | 0     | 0        | 0     |     |

#### • Bit 7 - PRTWI: Power Reduction TWI

Writing a logic one to this bit shuts down the TWI by stopping the clock to the module. When waking up the TWI again, the TWI should be re initialized to ensure proper operation.

#### • Bit 6 - PRTIM2: Power Reduction Timer/Counter2

Writing a logic one to this bit shuts down the Timer/Counter2 module in synchronous mode (AS2 is 0). When the Timer/Counter2 is enabled, operation will continue like before the shutdown.

#### Bit 5 - PRTIM0: Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the Timer/Counter0 is enabled, operation will continue like before the shutdown.

#### • Bit 4 - Res: Reserved bit

This bit is reserved in ATmega48/88/168 and will always read as zero.

#### • Bit 3 - PRTIM1: Power Reduction Timer/Counter1

Writing a logic one to this bit shuts down the Timer/Counter1 module. When the Timer/Counter1 is enabled, operation will continue like before the shutdown.

#### • Bit 2 - PRSPI: Power Reduction Serial Peripheral Interface

Writing a logic one to this bit shuts down the Serial Peripheral Interface by stopping the clock to the module. When waking up the SPI again, the SPI should be re initialized to ensure proper operation.

#### • Bit 1 - PRUSART0: Power Reduction USART0

Writing a logic one to this bit shuts down the USART by stopping the clock to the module. When waking up the USART again, the USART should be re initialized to ensure proper operation.

#### • Bit 0 - PRADC: Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. The ADC must be disabled before shut down. The analog comparator cannot use the ADC input MUX when the ADC is shut down.

#### 12.8.6 Timer/Counter Interrupt Mask Register – TIMSK0

| Bit           | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0     | _      |

|---------------|---|---|---|---|---|--------|--------|-------|--------|

|               | - | - | - | - | - | OCIE0B | OCIE0A | TOIE0 | TIMSK0 |

| Read/Write    | R | R | R | R | R | R/W    | R/W    | R/W   | •      |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0      | 0      | 0     |        |

#### • Bits 7..3 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### • Bit 2 – OCIE0B: Timer/Counter Output Compare Match B Interrupt Enable

When the OCIE0B bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter Compare Match B interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter occurs, i.e., when the OCF0B bit is set in the Timer/Counter Interrupt Flag Register – TIFR0.

#### • Bit 1 – OCIE0A: Timer/Counter0 Output Compare Match A Interrupt Enable

When the OCIE0A bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter0 Compare Match A interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter0 occurs, i.e., when the OCF0A bit is set in the Timer/Counter 0 Interrupt Flag Register – TIFR0.

#### • Bit 0 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set in the Timer/Counter 0 Interrupt Flag Register – TIFR0.

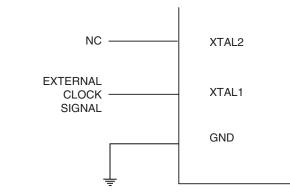

#### 12.8.7 Timer/Counter 0 Interrupt Flag Register – TIFR0

#### Bits 7..3 – Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### • Bit 2 – OCF0B: Timer/Counter 0 Output Compare B Match Flag

The OCF0B bit is set when a Compare Match occurs between the Timer/Counter and the data in OCR0B – Output Compare Register0 B. OCF0B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0B is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0B (Timer/Counter Compare B Match Interrupt Enable), and OCF0B are set, the Timer/Counter Compare Match Interrupt is executed.

#### Bit 1 – OCF0A: Timer/Counter 0 Output Compare A Match Flag

The OCF0A bit is set when a Compare Match occurs between the Timer/Counter0 and the data in OCR0A – Output Compare Register0. OCF0A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0A is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0A (Timer/Counter0 Compare Match Interrupt Enable), and OCF0A are set, the Timer/Counter0 Compare Match Interrupt is executed.

The setup of the OC2x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC2x value is to use the Force Output Compare (FOC2x) strobe bit in Normal mode. The OC2x Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COM2x1:0 bits are not double buffered together with the compare value. Changing the COM2x1:0 bits will take effect immediately.

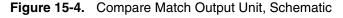

## 15.5 Compare Match Output Unit

The Compare Output mode (COM2x1:0) bits have two functions. The Waveform Generator uses the COM2x1:0 bits for defining the Output Compare (OC2x) state at the next compare match. Also, the COM2x1:0 bits control the OC2x pin output source. Figure 15-4 shows a simplified schematic of the logic affected by the COM2x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM2x1:0 bits are shown. When referring to the OC2x state, the reference is for the internal OC2x Register, not the OC2x pin.

The general I/O port function is overridden by the Output Compare (OC2x) from the Waveform Generator if either of the COM2x1:0 bits are set. However, the OC2x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC2x pin (DDR\_OC2x) must be set as output before the OC2x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC2x state before the output is enabled. Note that some COM2x1:0 bit settings are reserved for certain modes of operation. See Section "15.8" on page 149.

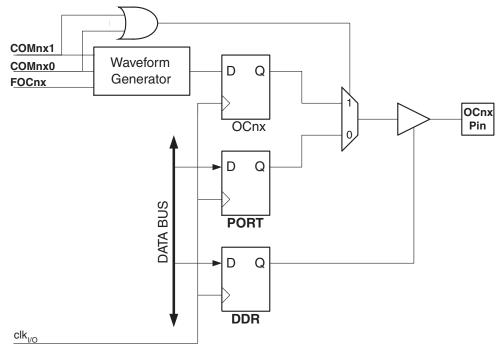

In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 15-6. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

Figure 15-6. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. (See Table 15-3 on page 149). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2x Register at the compare match between OCR2x and TCNT2, and clearing (or setting) the OC2x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clk\_I/O}}}{N \cdot 256}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM2A1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2x to toggle its logical level on each compare match (COM2x1:0 = 1). The waveform

#### • Bit 5 – DORD: Data Order

When the DORD bit is written to one, the LSB of the data word is transmitted first.

When the DORD bit is written to zero, the MSB of the data word is transmitted first.

#### • Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI mode when written to one, and Slave SPI mode when written logic zero. If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI Master mode.

#### • Bit 3 – CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero, SCK is low when idle. Refer to Figure 16-3 and Figure 16-4 for an example. The CPOL functionality is summarized below:

#### Table 16-2. CPOL Functionality

| CPOL | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Rising       | Falling       |

| 1    | Falling      | Rising        |

#### • Bit 2 – CPHA: Clock Phase

The settings of the Clock Phase bit (CPHA) determine if data is sampled on the leading (first) or trailing (last) edge of SCK. Refer to Figure 16-3 and Figure 16-4 for an example. The CPOL functionality is summarized below:

#### Table 16-3.CPHA Functionality

| СРНА | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Sample       | Setup         |

| 1    | Setup        | Sample        |

#### • Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a Master. SPR1 and SPR0 have no effect on the Slave. The relationship between SCK and the Oscillator Clock frequency  $f_{osc}$  is shown in the following table:

Table 16-4.

Relationship Between SCK and the Oscillator Frequency

| SPI2X | SPR1 | SPR0 | SCK Frequency         |

|-------|------|------|-----------------------|

| 0     | 0    | 0    | f <sub>osc</sub> /4   |

| 0     | 0    | 1    | f <sub>osc</sub> /16  |

| 0     | 1    | 0    | f <sub>osc</sub> /64  |

| 0     | 1    | 1    | f <sub>osc</sub> /128 |

| 1     | 0    | 0    | f <sub>osc</sub> /2   |

| 1     | 0    | 1    | f <sub>osc</sub> /8   |

| 1     | 1    | 0    | f <sub>osc</sub> /32  |

| 1     | 1    | 1    | f <sub>osc</sub> /64  |

#### 17.2.3 External Clock

External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 17-2 for details.

External clock input from the XCKn pin is sampled by a synchronization register to minimize the chance of meta-stability. The output from the synchronization register must then pass through an edge detector before it can be used by the Transmitter and Receiver. This process introduces a two CPU clock period delay and therefore the maximum external XCKn clock frequency is limited by the following equation:

$$f_{XCK} < \frac{f_{OSC}}{4}$$

Note that f<sub>osc</sub> depends on the stability of the system clock source. It is therefore recommended to add some margin to avoid possible loss of data due to frequency variations.

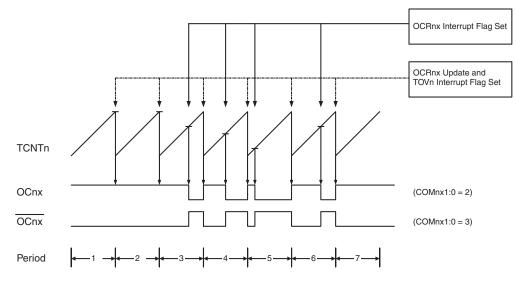

#### 17.2.4 Synchronous Clock Operation

When synchronous mode is used (UMSELn = 1), the XCKn pin will be used as either clock input (Slave) or clock output (Master). The dependency between the clock edges and data sampling or data change is the same. The basic principle is that data input (on RxDn) is sampled at the opposite XCKn clock edge of the edge the data output (TxDn) is changed.

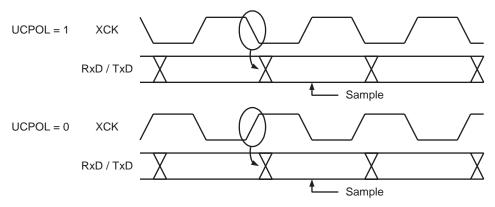

The UCPOLn bit UCRSC selects which XCKn clock edge is used for data sampling and which is used for data change. As Figure 17-3 shows, when UCPOLn is zero the data will be changed at rising XCKn edge and sampled at falling XCKn edge. If UCPOLn is set, the data will be changed at falling XCKn edge and sampled at rising XCKn edge.

#### 17.3 Frame Formats

A serial frame is defined to be one character of data bits with synchronization bits (start and stop bits), and optionally a parity bit for error checking. The USART accepts all 30 combinations of the following as valid frame formats:

- 1 start bit

- 5, 6, 7, 8, or 9 data bits

- no, even or odd parity bit

- 1 or 2 stop bits

## 172 **ATmega48/88/168**

| UCPOLn | Transmitted Data Changed (Output of TxDn Pin) | Received Data Sampled (Input on RxDn Pin) |  |  |  |  |  |  |  |

|--------|-----------------------------------------------|-------------------------------------------|--|--|--|--|--|--|--|

| 0      | Rising XCKn Edge                              | Falling XCKn Edge                         |  |  |  |  |  |  |  |

| 1      | Falling XCKn Edge                             | Rising XCKn Edge                          |  |  |  |  |  |  |  |

#### Table 17-8.UCPOLn Bit Settings

#### 17.9.5 USART Baud Rate Registers – UBRRnL and UBRRnH

| Bit           | 15  | 14  | 13  | 12   | 11      | 10   | 9       | 8   | _      |

|---------------|-----|-----|-----|------|---------|------|---------|-----|--------|

|               | -   | -   | -   | -    |         | UBRR | n[11:8] |     | UBRRnH |

|               |     |     |     | UBRR | ln[7:0] |      |         |     | UBRRnL |

|               | 7   | 6   | 5   | 4    | 3       | 2    | 1       | 0   | -      |

| Read/Write    | R   | R   | R   | R    | R/W     | R/W  | R/W     | R/W |        |

|               | R/W | R/W | R/W | R/W  | R/W     | R/W  | R/W     | R/W |        |

| Initial Value | 0   | 0   | 0   | 0    | 0       | 0    | 0       | 0   |        |

|               | 0   | 0   | 0   | 0    | 0       | 0    | 0       | 0   |        |

|               |     |     |     |      |         |      |         |     |        |

#### • Bit 15:12 - Reserved Bits

These bits are reserved for future use. For compatibility with future devices, these bit must be written to zero when UBRRnH is written.

#### • Bit 11:0 - UBRR11:0: USART Baud Rate Register

This is a 12-bit register which contains the USART baud rate. The UBRRnH contains the four most significant bits, and the UBRRnL contains the eight least significant bits of the USART baud rate. Ongoing transmissions by the Transmitter and Receiver will be corrupted if the baud rate is changed. Writing UBRRnL will trigger an immediate update of the baud rate prescaler.

## 17.10 Examples of Baud Rate Setting

For standard crystal and resonator frequencies, the most commonly used baud rates for asynchronous operation can be generated by using the UBRRn settings in Table 17-9. UBRRn values which yield an actual baud rate differing less than 0.5% from the target baud rate, are bold in the table. Higher error ratings are acceptable, but the Receiver will have less noise resistance when the error ratings are high, especially for large serial frames (see "Asynchronous Operational Range" on page 184). The error values are calculated using the following equation:

$$\operatorname{Error}[\%] = \left(\frac{\operatorname{BaudRate}_{\operatorname{Closest}\operatorname{Match}}}{\operatorname{BaudRate}} - 1\right) \bullet 100\%$$

| Operating Mode             | Equation for Calculating Baud<br>Rate <sup>(1)</sup> | Equation for Calculating UBRRn<br>Value |

|----------------------------|------------------------------------------------------|-----------------------------------------|

| Synchronous Master<br>mode | $BAUD = \frac{f_{OSC}}{2(UBRRn+1)}$                  | $UBRRn = \frac{f_{OSC}}{2BAUD} - 1$     |

**Table 18-1.** Equations for Calculating Baud Rate Register Setting

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps)

| BAUD             | Baud rate (in bits per second, bps)                   |

|------------------|-------------------------------------------------------|

| f <sub>osc</sub> | System Oscillator clock frequency                     |

| UBRRn            | Contents of the UBRRnH and UBRRnL Registers, (0-4095) |

## 18.3 SPI Data Modes and Timing

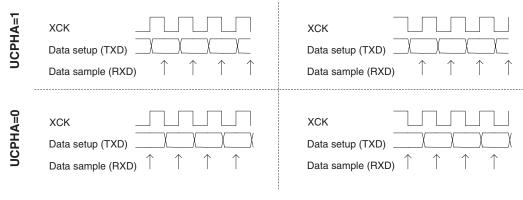

There are four combinations of XCKn (SCK) phase and polarity with respect to serial data, which are determined by control bits UCPHAn and UCPOLn. The data transfer timing diagrams are shown in Figure 18-1. Data bits are shifted out and latched in on opposite edges of the XCKn signal, ensuring sufficient time for data signals to stabilize. The UCPOLn and UCPHAn functionality is summarized in Table 18-2. Note that changing the setting of any of these bits will corrupt all ongoing communication for both the Receiver and Transmitter.

#### Table 18-2. UCPOLn and UCPHAn Functionality-

| UCPOLn | UCPOLn UCPHAn SPI Mode |   | Leading Edge     | Trailing Edge    |

|--------|------------------------|---|------------------|------------------|

| 0      | 0                      | 0 | Sample (Rising)  | Setup (Falling)  |

| 0      | 1                      | 1 | Setup (Rising)   | Sample (Falling) |

| 1      | 0                      | 2 | Sample (Falling) | Setup (Rising)   |

| 1      | 1                      | 3 | Setup (Falling)  | Sample (Rising)  |

Figure 18-1. UCPHAn and UCPOLn data transfer timing diagrams.

#### UCPOL=0

## UCPOL=1

#### • Bits 7..0 – TWD: TWI Data Register

These eight bits constitute the next data byte to be transmitted, or the latest data byte received on the 2-wire Serial Bus.

#### 19.6.5 TWI (Slave) Address Register – TWAR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0     |      |

|---------------|------|------|------|------|------|------|------|-------|------|

|               | TWA6 | TWA5 | TWA4 | TWA3 | TWA2 | TWA1 | TWA0 | TWGCE | TWAR |

| Read/Write    | R/W   | •    |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0     |      |

The TWAR should be loaded with the 7-bit Slave address (in the seven most significant bits of TWAR) to which the TWI will respond when programmed as a Slave Transmitter or Receiver, and not needed in the Master modes. In multi master systems, TWAR must be set in masters which can be addressed as Slaves by other Masters.

The LSB of TWAR is used to enable recognition of the general call address (0x00). There is an associated address comparator that looks for the slave address (or general call address if enabled) in the received serial address. If a match is found, an interrupt request is generated.

#### Bits 7..1 – TWA: TWI (Slave) Address Register

These seven bits constitute the slave address of the TWI unit.

#### • Bit 0 – TWGCE: TWI General Call Recognition Enable Bit

If set, this bit enables the recognition of a General Call given over the 2-wire Serial Bus.

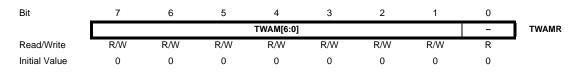

#### 19.6.6 TWI (Slave) Address Mask Register – TWAMR

#### Bits 7..1 – TWAM: TWI Address Mask

The TWAMR can be loaded with a 7-bit Salve Address mask. Each of the bits in TWAMR can mask (disable) the corresponding address bits in the TWI Address Register (TWAR). If the mask bit is set to one then the address match logic ignores the compare between the incoming address bit and the corresponding bit in TWAR. Figure 19-10 shown the address match logic in detail.

# ATmega48/88/168

A START condition is sent by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | тwwс | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

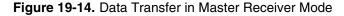

TWEN must be written to one to enable the 2-wire Serial Interface, TWSTA must be written to one to transmit a START condition and TWINT must be set to clear the TWINT Flag. The TWI will then test the 2-wire Serial Bus and generate a START condition as soon as the bus becomes free. After a START condition has been transmitted, the TWINT Flag is set by hardware, and the status code in TWSR will be 0x08 (See Table 19-3). In order to enter MR mode, SLA+R must be transmitted. This is done by writing SLA+R to TWDR. Thereafter the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

When SLA+R have been transmitted and an acknowledgement bit has been received, TWINT is set again and a number of status codes in TWSR are possible. Possible status codes in Master mode are 0x38, 0x40, or 0x48. The appropriate action to be taken for each of these status codes is detailed in Table 19-4. Received data can be read from the TWDR Register when the TWINT Flag is set high by hardware. This scheme is repeated until the last byte has been received. After the last byte has been received, the MR should inform the ST by sending a NACK after the last received data byte. The transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

|       |       |      |       |       |      | 1    |   |      |

|-------|-------|------|-------|-------|------|------|---|------|

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

| value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

After a repeated START condition (state 0x10) the 2-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables

PGWRT bit will auto-clear upon completion of a Page Write, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation if the NRWW section is addressed.

#### • Bit 1 – PGERS: Page Erase

If this bit is written to one at the same time as SELFPRGEN, the next SPM instruction within four clock cycles executes Page Erase. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon completion of a Page Erase, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation if the NRWW section is addressed.

#### Bit 0 – SELFPRGEN: Self Programming Enable

This bit enables the SPM instruction for the next four clock cycles. If written to one together with either RWWSRE, BLBSET, PGWRT or PGERS, the following SPM instruction will have a special meaning, see description above. If only SELFPRGEN is written, the following SPM instruction will store the value in R1:R0 in the temporary page buffer addressed by the Z-pointer. The LSB of the Z-pointer is ignored. The SELFPRGEN bit will auto-clear upon completion of an SPM instruction, or if no SPM instruction is executed within four clock cycles. During Page Erase and Page Write, the SELFPRGEN bit remains high until the operation is completed.

Writing any other combination than "10001", "01001", "00101", "00011" or "00001" in the lower five bits will have no effect.

## 24.6 Addressing the Flash During Self-Programming

The Z-pointer is used to address the SPM commands.

| Bit      | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| ZH (R31) | Z15 | Z14 | Z13 | Z12 | Z11 | Z10 | Z9 | Z8 |

| ZL (R30) | Z7  | Z6  | Z5  | Z4  | Z3  | Z2  | Z1 | Z0 |

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

Since the Flash is organized in pages (see Table 25-8 on page 284), the Program Counter can be treated as having two different sections. One section, consisting of the least significant bits, is addressing the words within a page, while the most significant bits are addressing the pages. This is1 shown in Figure 24-3. Note that the Page Erase and Page Write operations are addressed independently. Therefore it is of major importance that the Boot Loader software addresses the same page in both the Page Erase and Page Write operation. Once a programming operation is initiated, the address is latched and the Z-pointer can be used for other operations.

The only SPM operation that does not use the Z-pointer is Setting the Boot Loader Lock bits. The content of the Z-pointer is ignored and will have no effect on the operation. The LPM instruction does also use the Z-pointer to store the address. Since this instruction addresses the Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used.

|           |       | 0     | iodes . Only Armegaeo/ roo.                                                                                                                                                                                                                                                                   |

|-----------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLB0 Mode | BLB02 | BLB01 |                                                                                                                                                                                                                                                                                               |

| 1         | 1     | 1     | No restrictions for SPM or LPM accessing the Application section.                                                                                                                                                                                                                             |

| 2         | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                       |

| 3         | 0     | 0     | SPM is not allowed to write to the Application section, and LPM executing from the Boot Loader section is not allowed to read from the Application section. If Interrupt Vectors are placed in the Boot Loader section, interrupts are disabled while executing from the Application section. |

| 4         | 0     | 1     | LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section.                                                    |

| BLB1 Mode | BLB12 | BLB11 |                                                                                                                                                                                                                                                                                               |

| 1         | 1     | 1     | No restrictions for SPM or LPM accessing the Boot Loader section.                                                                                                                                                                                                                             |

| 2         | 1     | 0     | SPM is not allowed to write to the Boot Loader section.                                                                                                                                                                                                                                       |

| 3         | 0     | 0     | SPM is not allowed to write to the Boot Loader section, and LPM executing from the Application section is not allowed to read from the Boot Loader section. If Interrupt Vectors are placed in the Application section, interrupts are disabled while executing from the Boot Loader section. |

| 4         | 0     | 1     | LPM executing from the Application section is not allowed to<br>read from the Boot Loader section. If Interrupt Vectors are<br>placed in the Application section, interrupts are disabled while<br>executing from the Boot Loader section.                                                    |

Table 25-3.

Lock Bit Protection Modes<sup>(1)(2)</sup>. Only ATmega88/168.

Notes: 1. Program the Fuse bits and Boot Lock bits before programming the LB1 and LB2.

2. "1" means unprogrammed, "0" means programmed

### 25.2 Fuse Bits

The ATmega48/88/168 has three Fuse bytes. Table 25-4 - Table 25-7 describe briefly the functionality of all the fuses and how they are mapped into the Fuse bytes. Note that the fuses are read as logical zero, "0", if they are programmed.

**Table 25-4.**Extended Fuse Byte for mega48

| Extended Fuse Byte | Bit No | Description             | Default Value    |

|--------------------|--------|-------------------------|------------------|

| -                  | 7      | -                       | 1                |

| _                  | 6      | -                       | 1                |

| _                  | 5      | _                       | 1                |

| _                  | 4      | -                       | 1                |

| _                  | 3      | -                       | 1                |

| -                  | 2      | _                       | 1                |

| -                  | 1      | _                       | 1                |

| SELFPRGEN          | 0      | Self Programming Enable | 1 (unprogrammed) |

ATmega48/88/168

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

- All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon

- 6. Values with "Power Reduction Register PRR" disabled (0x00).

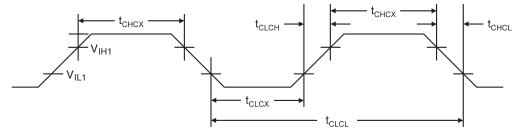

## 26.3 External Clock Drive Waveforms

#### Figure 26-1. External Clock Drive Waveforms

## 26.4 External Clock Drive

| Symbol              | Parameter                                               | V <sub>CC</sub> =1.8-5.5V |      | V <sub>CC</sub> =2.7-5.5V |      | V <sub>CC</sub> =4.5-5.5V |      |       |

|---------------------|---------------------------------------------------------|---------------------------|------|---------------------------|------|---------------------------|------|-------|

|                     |                                                         | Min.                      | Max. | Min.                      | Max. | Min.                      | Max. | Units |

| 1/t <sub>CLCL</sub> | Oscillator<br>Frequency                                 | 0                         | 4    | 0                         | 10   | 0                         | 20   | MHz   |

| t <sub>CLCL</sub>   | Clock Period                                            | 250                       |      | 100                       |      | 50                        |      | ns    |

| t <sub>CHCX</sub>   | High Time                                               | 100                       |      | 40                        |      | 20                        |      | ns    |

| t <sub>CLCX</sub>   | Low Time                                                | 100                       |      | 40                        |      | 20                        |      | ns    |

| t <sub>CLCH</sub>   | Rise Time                                               |                           | 2.0  |                           | 1.6  |                           | 0.5  | μs    |

| t <sub>CHCL</sub>   | Fall Time                                               |                           | 2.0  |                           | 1.6  |                           | 0.5  | μS    |

| $\Delta t_{CLCL}$   | Change in period<br>from one clock<br>cycle to the next |                           | 2    |                           | 2    |                           | 2    | %     |

Table 26-1.External Clock Drive

Note: All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon.

## 26.5 Maximum Speed vs. V<sub>CC</sub>

Maximum frequency is dependent on V<sub>CC.</sub> As shown in Figure 26-2 and Figure 26-3, the Maximum Frequency vs. V<sub>CC</sub> curve is linear between  $1.8V < V_{CC} < 2.7V$  and between  $2.7V < V_{CC} < 4.5V$ .

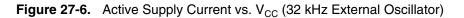

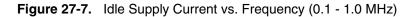

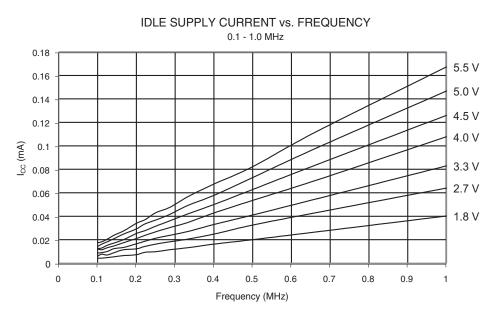

## 27.2 Idle Supply Current

Figure 27-12. Idle Supply Current vs. V<sub>CC</sub> (32 kHz External Oscillator)

## 27.3 Supply Current of I/O modules

The tables and formulas below can be used to calculate the additional current consumption for the different I/O modules in Active and Idle mode. The enabling or disabling of the I/O modules are controlled by the Power Reduction Register. See "Power Reduction Register" on page 39 for details.

| PRR bit  | Typical numbers                |                         |                                |  |  |  |  |

|----------|--------------------------------|-------------------------|--------------------------------|--|--|--|--|

|          | V <sub>CC</sub> = 2V, F = 1MHz | $V_{CC} = 3V, F = 4MHz$ | V <sub>CC</sub> = 5V, F = 8MHz |  |  |  |  |

| PRUSART0 | 8.0 uA                         | 51 uA                   | 220 uA                         |  |  |  |  |

| PRTWI    | 12 uA                          | 75 uA                   | 315 uA                         |  |  |  |  |

| PRTIM2   | 11 uA                          | 72 uA                   | 300 uA                         |  |  |  |  |

| PRTIM1   | 5.0 uA                         | 32 uA                   | 130 uA                         |  |  |  |  |

| PRTIM0   | 4.0 uA                         | 24 uA                   | 100 uA                         |  |  |  |  |

| PRSPI    | 15 uA                          | 95 uA                   | 400 uA                         |  |  |  |  |

| PRADC    | 12 uA                          | 75 uA                   | 315 uA                         |  |  |  |  |

Table 27-1.

Additional Current Consumption for the different I/O modules (absolute values)

# ATmega48/88/168

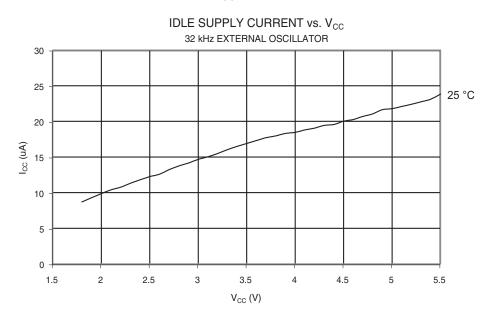

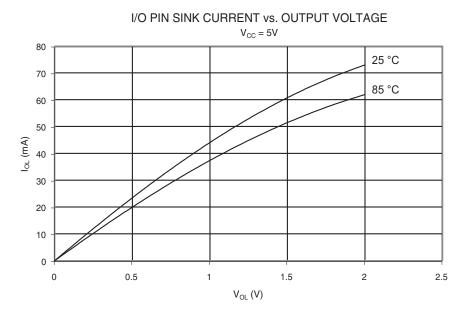

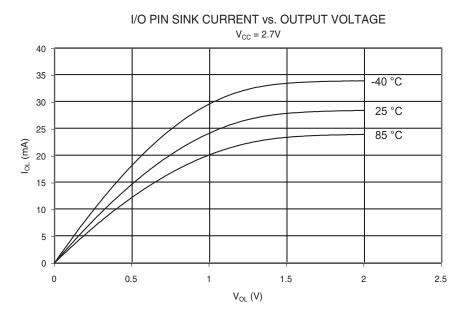

Figure 27-26. I/O Pin Sink Current vs. Output Voltage ( $V_{CC} = 2.7V$ )

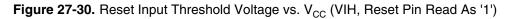

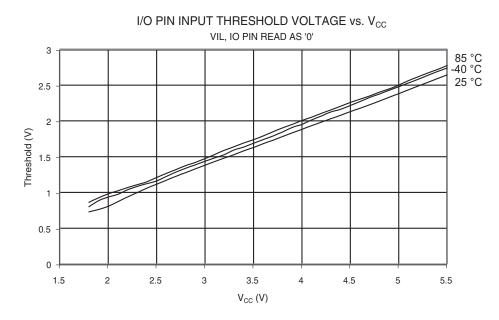

Figure 27-29. I/O Pin Input Threshold Voltage vs. V<sub>CC</sub> (VIL, I/O Pin Read As '0')