Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168-20pi |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In ATmega48, there is no Read-While-Write support and no separate Boot Loader Section. The SPM instruction can execute from the entire Flash.

#### 2.3 Pin Descriptions

| 2.3. | 1 | VCC |

|------|---|-----|

|      |   |     |

- Digital supply voltage.

- 2.3.2 GND

Ground.

#### 2.3.3 Port B (PB7..0) XTAL1/XTAL2/TOSC1/TOSC2

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.

If the Internal Calibrated RC Oscillator is used as chip clock source, PB7..6 is used as TOSC2..1 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.

The various special features of Port B are elaborated in "Alternate Functions of Port B" on page 71 and "System Clock and Clock Options" on page 25.

#### 2.3.4 Port C (PC5..0)

Port C is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The PC5..0 output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### 2.3.5 PC6/RESET

If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electrical characteristics of PC6 differ from those of the other pins of Port C.

If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. The minimum pulse length is given in Table 8-1 on page 44. Shorter pulses are not guaranteed to generate a Reset.

The various special features of Port C are elaborated in "Alternate Functions of Port C" on page 75.

#### 2.3.6 Port D (PD7..0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up

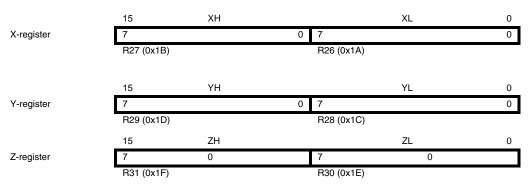

#### 4.5.1 The X-register, Y-register, and Z-register

The registers R26..R31 have some added functions to their general purpose usage. These registers are 16-bit address pointers for indirect addressing of the data space. The three indirect address registers X, Y, and Z are defined as described in Figure 4-3.

Figure 4-3. The X-, Y-, and Z-registers

In the different addressing modes these address registers have functions as fixed displacement, automatic increment, and automatic decrement (see the instruction set reference for details).

#### 4.6 Stack Pointer

The Stack is mainly used for storing temporary data, for storing local variables and for storing return addresses after interrupts and subroutine calls. The Stack Pointer Register always points to the top of the Stack. Note that the Stack is implemented as growing from higher memory locations to lower memory locations. This implies that a Stack PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Interrupt Stacks are located. This Stack space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer must be set to point above 0x0100, preferably RAMEND. The Stack Pointer is decremented by one when data is pushed onto the Stack with the PUSH instruction, and it is decremented by two when the return address is pushed onto the Stack with subroutine call or interrupt. The Stack Pointer is incremented by one when data is popped from the Stack with the POP instruction, and it is incremented by two when data is popped from the Stack with return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is implementation dependent. Note that the data space in some implementations of the AVR architecture is so small that only SPL is needed. In this case, the SPH Register will not be present.

| Bit           | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

|               | SP15   | SP14   | SP13   | SP12   | SP11   | SP10   | SP9    | SP8    | SPH |

|               | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

|               | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |     |

| Read/Write    | R/W    |     |

|               | R/W    |     |

| Initial Value | RAMEND |     |

|               | RAMEND |     |

Assembly Code Example

| <b>in</b> r16, S | SREG    | ; store SREG value               |

|------------------|---------|----------------------------------|

| cli ;            | disable | interrupts during timed sequence |

| <b>sbi</b> EECR, | EEMPE   | ; start EEPROM write             |

| <b>sbi</b> EECR, | EEPE    |                                  |

| out SREG,        | r16     | ; restore SREG value (I-bit)     |

C Code Example

```

char cSREG;

cSREG = SREG; /* store SREG value */

/* disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMPE); /* start EEPROM write */

EECR |= (1<<EEPE);

SREG = cSREG; /* restore SREG value (I-bit) */

```

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in this example.

| Assembly  | Code Example                                                  |

|-----------|---------------------------------------------------------------|

| sei       | set Global Interrupt Enable                                   |

| sleep     | enter sleep, waiting for interrupt                            |

| ; note    | e: will enter sleep before any pending interrupt(s)           |

| C Code Ex | ample                                                         |

| enal      | <pre>ole_interrupt(); /* set Global Interrupt Enable */</pre> |

| slee      | ep(); /* enter sleep, waiting for interrupt */                |

| /* not    | te: will enter sleep before any pending interrupt(s) */       |

#### 4.8.1 Interrupt Response Time

The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. After four clock cycles the program vector address for the actual interrupt handling routine is executed. During this four clock cycle period, the Program Counter is pushed onto the Stack. The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the Program Counter (two bytes) is popped back from the Stack, the Stack Pointer is incremented by two, and the I-bit in SREG is set.

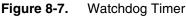

#### 8.2 Watchdog Timer

ATmega48/88/168 has an Enhanced Watchdog Timer (WDT). The main features are:

- Clocked from separate On-chip Oscillator

- 3 Operating modes

- Interrupt

- System Reset

- Interrupt and System Reset

- Selectable Time-out period from 16ms to 8s

- Possible Hardware fuse Watchdog always on (WDTON) for fail-safe mode

The Watchdog Timer (WDT) is a timer counting cycles of a separate on-chip 128 kHz oscillator. The WDT gives an interrupt or a system reset when the counter reaches a given time-out value. In normal operation mode, it is required that the system uses the WDR - Watchdog Timer Reset - instruction to restart the counter before the time-out value is reached. If the system doesn't restart the counter, an interrupt or system reset will be issued.

In Interrupt mode, the WDT gives an interrupt when the timer expires. This interrupt can be used to wake the device from sleep-modes, and also as a general system timer. One example is to limit the maximum time allowed for certain operations, giving an interrupt when the operation has run longer than expected. In System Reset mode, the WDT gives a reset when the timer expires. This is typically used to prevent system hang-up in case of runaway code. The third mode, Interrupt and System Reset mode, combines the other two modes by first giving an interrupt and then switch to System Reset mode. This mode will for instance allow a safe shutdown by saving critical parameters before a system reset.

The Watchdog always on (WDTON) fuse, if programmed, will force the Watchdog Timer to System Reset mode. With the fuse programmed the System Reset mode bit (WDE) and Interrupt mode bit (WDIE) are locked to 1 and 0 respectively. To further ensure program security, alterations to the Watchdog set-up must follow timed sequences. The sequence for clearing WDE and changing time-out configuration is as follows:

Note: If the Watchdog is accidentally enabled, for example by a runaway pointer or brown-out condition, the device will be reset and the Watchdog Timer will stay enabled. If the code is not set up to handle the Watchdog, this might lead to an eternal loop of time-out resets. To avoid this situation, the application software should always clear the Watchdog System Reset Flag (WDRF) and the WDE control bit in the initialisation routine, even if the Watchdog is not in use.

The following code example shows one assembly and one C function for changing the time-out value of the Watchdog Timer.

```

Assembly Code Example<sup>(1)</sup>

WDT_Prescaler_Change:

; Turn off global interrupt

cli

; Reset Watchdog Timer

wdr

; Start timed sequence

lds r16, WDTCSR

ori

r16, (1<<WDCE) | (1<<WDE)

sts WDTCSR, r16

; -- Got four cycles to set the new values from here -

; Set new prescaler(time-out) value = 64K cycles (~0.5 s)

r16, (1<<WDE) | (1<<WDP2) | (1<<WDP0)

ldi

sts WDTCSR, r16

; -- Finished setting new values, used 2 cycles -

; Turn on global interrupt

sei

ret

C Code Example<sup>(1)</sup>

void WDT_Prescaler_Change(void)

{

__disable_interrupt();

__watchdog_reset();

/* Start timed equence */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* Set new prescaler(time-out) value = 64K cycles (~0.5 s) */

WDTCSR = (1<<WDE) | (1<<WDP2) | (1<<WDP0);

_enable_interrupt();

}

```

Note: 1. See "About Code Examples" on page 6.

Note: The Watchdog Timer should be reset before any change of the WDP bits, since a change in the WDP bits can result in a time-out when switching to a shorter time-out period.

#### • Bit 5, 2..0 - WDP3..0: Watchdog Timer Prescaler 3, 2, 1 and 0

The WDP3..0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is running. The different prescaling values and their corresponding time-out periods are shown in Table 8-6 on page 53.

| WDP3 | WDP2 | WDP1 | WDP0 | Number of WDT OscillatorTypical Time-out aCyclesV <sub>CC</sub> = 5.0V |         |  |  |  |

|------|------|------|------|------------------------------------------------------------------------|---------|--|--|--|

| 0    | 0    | 0    | 0    | 2K (2048) cycles 16 ms                                                 |         |  |  |  |

| 0    | 0    | 0    | 1    | 4K (4096) cycles 32 ms                                                 |         |  |  |  |

| 0    | 0    | 1    | 0    | 8K (8192) cycles                                                       | 64 ms   |  |  |  |

| 0    | 0    | 1    | 1    | 16K (16384) cycles                                                     | 0.125 s |  |  |  |

| 0    | 1    | 0    | 0    | 32K (32768) cycles                                                     | 0.25 s  |  |  |  |

| 0    | 1    | 0    | 1    | 64K (65536) cycles                                                     | 0.5 s   |  |  |  |

| 0    | 1    | 1    | 0    | 128K (131072) cycles                                                   | 1.0 s   |  |  |  |

| 0    | 1    | 1    | 1    | 256K (262144) cycles                                                   | 2.0 s   |  |  |  |

| 1    | 0    | 0    | 0    | 512K (524288) cycles 4.0 s                                             |         |  |  |  |

| 1    | 0    | 0    | 1    | 1024K (1048576) cycles                                                 | 8.0 s   |  |  |  |

| 1    | 0    | 1    | 0    |                                                                        |         |  |  |  |

| 1    | 0    | 1    | 1    |                                                                        |         |  |  |  |

| 1    | 1    | 0    | 0    |                                                                        |         |  |  |  |

| 1    | 1    | 0    | 1    | Reserved                                                               |         |  |  |  |

| 1    | 1    | 1    | 0    |                                                                        |         |  |  |  |

| 1    | 1    | 1    | 1    |                                                                        |         |  |  |  |

Table 8-6.Watchdog Timer Prescale Select

#### 10.3.1 MCU Control Register – MCUCR

| Bit           | 7 | 6 | 5 | 4   | 3 | 2 | 1     | 0    | _     |

|---------------|---|---|---|-----|---|---|-------|------|-------|

|               | - | - | - | PUD | - | - | IVSEL | IVCE | MCUCR |

| Read/Write    | R | R | R | R/W | R | R | R/W   | R/W  | •     |

| Initial Value | 0 | 0 | 0 | 0   | 0 | 0 | 0     | 0    |       |

#### • Bit 4 – PUD: Pull-up Disable

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01). See "Configuring the Pin" on page 65 for more details about this feature.

#### 10.3.2 Alternate Functions of Port B

The Port B pins with alternate functions are shown in Table 10-3.

Port Pin **Alternate Functions** XTAL2 (Chip Clock Oscillator pin 2) PB7 TOSC2 (Timer Oscillator pin 2) PCINT7 (Pin Change Interrupt 7) XTAL1 (Chip Clock Oscillator pin 1 or External clock input) PB6 TOSC1 (Timer Oscillator pin 1) PCINT6 (Pin Change Interrupt 6) SCK (SPI Bus Master clock Input) PB5 PCINT5 (Pin Change Interrupt 5) MISO (SPI Bus Master Input/Slave Output) PB4 PCINT4 (Pin Change Interrupt 4) MOSI (SPI Bus Master Output/Slave Input) PB3 OC2A (Timer/Counter2 Output Compare Match A Output) PCINT3 (Pin Change Interrupt 3) SS (SPI Bus Master Slave select) PB2 OC1B (Timer/Counter1 Output Compare Match B Output) PCINT2 (Pin Change Interrupt 2) OC1A (Timer/Counter1 Output Compare Match A Output) PB1 PCINT1 (Pin Change Interrupt 1) ICP1 (Timer/Counter1 Input Capture Input) PB0 CLKO (Divided System Clock Output) PCINT0 (Pin Change Interrupt 0)

Table 10-3. Port B Pins Alternate Functions

The alternate pin configuration is as follows:

#### • XTAL2/TOSC2/PCINT7 - Port B, Bit 7

XTAL2: Chip clock Oscillator pin 2. Used as clock pin for crystal Oscillator or Low-frequency crystal Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

TOSC2: Timer Oscillator pin 2. Used only if internal calibrated RC Oscillator is selected as chip clock source, and the asynchronous timer is enabled by the correct setting in ASSR. When the AS2 bit in ASSR is set (one) and the EXCLK bit is cleared (zero) to enable asynchronous clock-ing of Timer/Counter2 using the Crystal Oscillator, pin PB7 is disconnected from the port, and

#### 11.1.1 External Interrupt Control Register A – EICRA

The External Interrupt Control Register A contains control bits for interrupt sense control.

| Bit           | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     | _     |

|---------------|---|---|---|---|-------|-------|-------|-------|-------|

|               | - | - | - | - | ISC11 | ISC10 | ISC01 | ISC00 | EICRA |

| Read/Write    | R | R | R | R | R/W   | R/W   | R/W   | R/W   | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0     | 0     | 0     | 0     |       |

#### • Bit 7..4 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 11-1. The value on the INT1 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

Table 11-1.

Interrupt 1 Sense Control

| ISC11 | ISC10 | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT1 generates an interrupt request. |

| 1     | 0     | The falling edge of INT1 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.    |

#### • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 11-2. The value on the INT0 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

|       | •     |                                                            |

|-------|-------|------------------------------------------------------------|

| ISC01 | ISC00 | Description                                                |

| 0     | 0     | The low level of INT0 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT0 generates an interrupt request. |

| 1     | 0     | The falling edge of INT0 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.    |

Table 11-2.

Interrupt 0 Sense Control

implies that the length of the falling slope is determined by the previous TOP value, while the length of the rising slope is determined by the new TOP value. When these two values differ the two slopes of the period will differ in length. The difference in length gives the unsymmetrical result on the output.

It is recommended to use the phase and frequency correct mode instead of the phase correct mode when changing the TOP value while the Timer/Counter is running. When using a static TOP value there are practically no differences between the two modes of operation.

In phase correct PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to three (See Table on page 129). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1 when the counter increments, and clearing (or setting) the OC1x Register at compare match between OCR1x and TCNT1 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{OCnxPCPWM} = \frac{f_{\text{clk\_I/O}}}{2 \cdot N \cdot TOP}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x Register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR1x is set equal to BOTTOM the output will be continuously low and if set equal to TOP the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values. If OCR1A is used to define the TOP value (WGM13:0 = 11) and COM1A1:0 = 1, the OC1A output will toggle with a 50% duty cycle.

#### 13.8.5 Phase and Frequency Correct PWM Mode

The phase and frequency correct Pulse Width Modulation, or phase and frequency correct PWM mode (WGM13:0 = 8 or 9) provides a high resolution phase and frequency correct PWM waveform generation option. The phase and frequency correct PWM mode is, like the phase correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared on the compare match between TCNT1 and OCR1x while upcounting, and set on the compare match while downcounting. In inverting Compare Output mode, the operation is inverted. The dual-slope operation gives a lower maximum operation frequency compared to the single-slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The main difference between the phase correct, and the phase and frequency correct PWM mode is the time the OCR1x Register is updated by the OCR1x Buffer Register, (see Figure 13-8 and Figure 13-9).

The PWM resolution for the phase and frequency correct PWM mode can be defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and

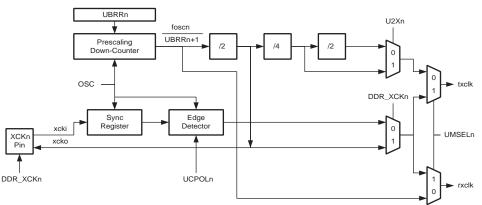

Signal description:

| txclk                     | Transmitter clock (Internal Signal).                                              |

|---------------------------|-----------------------------------------------------------------------------------|

| rxclk                     | Receiver base clock (Internal Signal).                                            |

| <b>xcki</b><br>operation. | Input from XCK pin (internal Signal). Used for synchronous slave                  |

| xcko                      | Clock output to XCK pin (Internal Signal). Used for synchronous master operation. |

| fosc                      | XTAL pin frequency (System Clock).                                                |

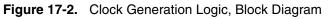

#### 17.2.1 Internal Clock Generation – The Baud Rate Generator

Internal clock generation is used for the asynchronous and the synchronous master modes of operation. The description in this section refers to Figure 17-2.

The USART Baud Rate Register (UBRRn) and the down-counter connected to it function as a programmable prescaler or baud rate generator. The down-counter, running at system clock ( $f_{osc}$ ), is loaded with the UBRRn value each time the counter has counted down to zero or when the UBRRnL Register is written. A clock is generated each time the counter reaches zero. This clock is the baud rate generator clock output (=  $f_{osc}/(UBRRn+1)$ ). The Transmitter divides the baud rate generator clock output by 2, 8 or 16 depending on mode. The baud rate generator output is used directly by the Receiver's clock and data recovery units. However, the recovery units use a state machine that uses 2, 8 or 16 states depending on mode set by the state of the UMSELn, U2Xn and DDR\_XCKn bits.

#### Assembly Code Example<sup>(1)</sup>

```

USART_Receive:

; Wait for data to be received

sbis UCSRnA, RXCn

rjmp USART_Receive

; Get status and 9th bit, then data from buffer

in

r18, UCSRnA

in

r17, UCSRnB

r16, UDRn

in

; If error, return -1

andi r18,(1<<FEn) | (1<<DORn) | (1<<UPEn)

breq USART_ReceiveNoError

1di r17, HIGH(-1)

ldi r16, LOW(-1)

USART_ReceiveNoError:

; Filter the 9th bit, then return

lsr r17

andi r17, 0x01

ret

C Code Example<sup>(1)</sup>

unsigned int USART_Receive( void )

{

unsigned char status, resh, resl;

/* Wait for data to be received */

while ( !(UCSRnA & (1<<RXCn)) )</pre>

/* Get status and 9th bit, then data */

/* from buffer */

status = UCSRnA;

resh = UCSRnB;

resl = UDRn;

/* If error, return -1 */

if ( status & (1<<FEn) | (1<<DORn) | (1<<UPEn) )

return -1;

/* Filter the 9th bit, then return */

resh = (resh >> 1) & 0x01;

return ((resh << 8) | resl);</pre>

}

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The receive function example reads all the I/O Registers into the Register File before any computation is done. This gives an optimal receive buffer utilization since the buffer location read will be free to accept new data as early as possible. baud rate is given as a function parameter. For the assembly code, the baud rate parameter is assumed to be stored in the r17:r16 registers.

| Assembly Code Example <sup>(1)</sup>                                                                                 |

|----------------------------------------------------------------------------------------------------------------------|

| USART_Init:                                                                                                          |

| clr r18                                                                                                              |

| out UBRRnH,r18                                                                                                       |

| out UBRRnL,r18                                                                                                       |

| ; Setting the XCKn port pin as output, enables master mode.                                                          |

| <b>sbi</b> XCKn_DDR, XCKn                                                                                            |

| ; Set MSPI mode of operation and SPI data mode 0.                                                                    |

| ldi r18, (1< <umseln1) (1<<umseln0) (0<<ucphan) (0<<ucpoln)< td=""></umseln1) (1<<umseln0) (0<<ucphan) (0<<ucpoln)<> |

| out UCSRnC,r18                                                                                                       |

| ; Enable receiver and transmitter.                                                                                   |

| <b>ldi</b> r18, (1< <rxenn) (1<<txenn)<="" td=""  =""></rxenn)>                                                      |

| out UCSRnB,r18                                                                                                       |

| ; Set baud rate.                                                                                                     |

| ; IMPORTANT: The Baud Rate must be set after the transmitter is enabled!                                             |

| out UBRRnH, r17                                                                                                      |

| out UBRRnL, r18                                                                                                      |

| ret                                                                                                                  |

| C Code Example <sup>(1)</sup>                                                                                        |

| <b>void</b> USART_Init( <b>unsigned int</b> baud )                                                                   |

| {                                                                                                                    |

| UBRRn = 0;                                                                                                           |

| /* Setting the XCKn port pin as output, enables master mode. */                                                      |

| XCKn_DDR = (1< <xckn);< td=""></xckn);<>                                                                             |

| /* Set MSPI mode of operation and SPI data mode 0. */                                                                |

| UCSRnC = (1< <umseln1) (0<<ucphan)="" (0<<ucpoln);<="" (1<<umseln0)="" td=""  =""></umseln1)>                        |

| /* Enable receiver and transmitter. */                                                                               |

| UCSRnB = (1< <rxenn) (1<<txenn);<="" td=""  =""></rxenn)>                                                            |

| /* Set baud rate. */                                                                                                 |

| /* IMPORTANT: The Baud Rate must be set after the transmitter is enabled $^{*/}$                                     |

| UBRRn = baud;                                                                                                        |

| }                                                                                                                    |

#### 18.5 Data Transfer

Using the USART in MSPI mode requires the Transmitter to be enabled, i.e. the TXENn bit in the UCSRnB register is set to one. When the Transmitter is enabled, the normal port operation of the TxDn pin is overridden and given the function as the Transmitter's serial output. Enabling the receiver is optional and is done by setting the RXENn bit in the UCSRnB register to one. When the receiver is enabled, the normal pin operation of the RxDn pin is overridden and given the function as the Receiver's serial input. The XCKn will in both cases be used as the transfer clock.

#### 21.4.1 ADC Input Channels

When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:

In Single Conversion mode, always select the channel before starting the conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the conversion to complete before changing the channel selection.

In Free Running mode, always select the channel before starting the first conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the first conversion to complete, and then change the channel selection. Since the next conversion has already started automatically, the next result will reflect the previous channel selection. Subsequent conversions will reflect the new channel selection.

#### 21.4.2 ADC Voltage Reference

The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed  $V_{REF}$  will result in codes close to 0x3FF.  $V_{REF}$  can be selected as either AV<sub>CC</sub>, internal 1.1V reference, or external AREF pin.

$AV_{CC}$  is connected to the ADC through a passive switch. The internal 1.1V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground.  $V_{REF}$  can also be measured at the AREF pin with a high impedant voltmeter. Note that  $V_{REF}$  is a high impedant source, and only a capacitive load should be connected in a system.

If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between  $AV_{CC}$  and 1.1V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.

#### 21.5 ADC Noise Canceler

The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:

- a. Make sure that the ADC is enabled and is not busy converting. Single Conversion mode must be selected and the ADC conversion complete interrupt must be enabled.

- b. Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion once the CPU has been halted.

- c. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.

Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before entering such sleep modes to avoid excessive power consumption.

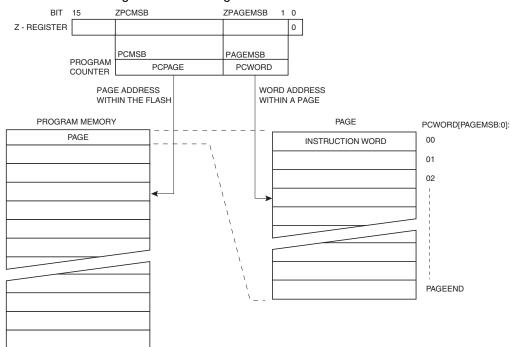

**Figure 24-3.** Addressing the Flash During SPM<sup>(1)</sup>

#### 24.7 Self-Programming the Flash

The program memory is updated in a page by page fashion. Before programming a page with the data stored in the temporary page buffer, the page must be erased. The temporary page buffer is filled one word at a time using SPM and the buffer can be filled either before the Page Erase command or between a Page Erase and a Page Write operation:

Alternative 1, fill the buffer before a Page Erase

- Fill temporary page buffer

- Perform a Page Erase

- Perform a Page Write

Alternative 2, fill the buffer after Page Erase

- Perform a Page Erase

- Fill temporary page buffer

- Perform a Page Write

If only a part of the page needs to be changed, the rest of the page must be stored (for example in the temporary page buffer) before the erase, and then be rewritten. When using alternative 1, the Boot Loader provides an effective Read-Modify-Write feature which allows the user software to first read the page, do the necessary changes, and then write back the modified data. If alternative 2 is used, it is not possible to read the old data while loading since the page is already erased. The temporary page buffer can be accessed in a random sequence. It is essential that the page address used in both the Page Erase and Page Write operation is addressing the same page. See "Simple Assembly Code Example for a Boot Loader" on page 275 for an assembly code example.

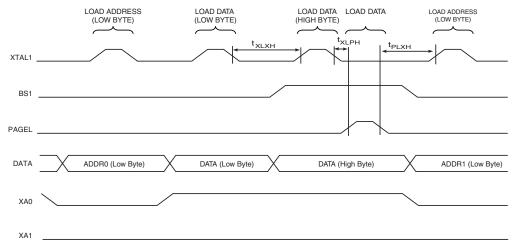

Table 25-12. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                                |

|-----|-----|----------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (High or low address byte determined by BS1). |

| 0   | 1   | Load Data (High or Low data byte for Flash determined by BS1).             |

| 1   | 0   | Load Command                                                               |

| 1   | 1   | No Action, Idle                                                            |

Table 25-13. Command Byte Bit Coding

| Command Byte | Command Executed                          |

|--------------|-------------------------------------------|

| 1000 0000    | Chip Erase                                |

| 0100 0000    | Write Fuse bits                           |

| 0010 0000    | Write Lock bits                           |

| 0001 0000    | Write Flash                               |

| 0001 0001    | Write EEPROM                              |

| 0000 1000    | Read Signature Bytes and Calibration byte |

| 0000 0100    | Read Fuse and Lock bits                   |

| 0000 0010    | Read Flash                                |

| 0000 0011    | Read EEPROM                               |

#### 25.7 Parallel Programming

#### 25.7.1 Enter Programming Mode

The following algorithm puts the device in Parallel (High-voltage) Programming mode:

- 1. Set Prog\_enable pins listed in Table 25-11 on page 285 to "0000", RESET pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND.

Ensure that  $V_{CC}$  reaches at least 1.8V within the next 20  $\mu$ s.

- 3. Wait 20 60 µs, and apply 11.5 12.5V to RESET.

- 4. Keep the Prog\_enable pins unchanged for at least 10µs after the High-voltage has been applied to ensure the Prog\_enable Signature has been latched.

- 5. Wait at least 300 µs before giving any parallel programming commands.

- 6. Exit Programming mode by power the device down or by bringing RESET pin to 0V.

If the rise time of the  $V_{CC}$  is unable to fulfill the requirements listed above, the following alternative algorithm can be used.

- 1. Set Prog\_enable pins listed in Table 25-11 on page 285 to "0000", RESET pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND.

- 3. Monitor  $V_{CC}$ , and as soon as  $V_{CC}$  reaches 0.9 1.1V, apply 11.5 12.5V to RESET.

#### 25.7.14 Reading the Calibration Byte

The algorithm for reading the Calibration byte is as follows (refer to "Programming the Flash" on page 287 for details on Command and Address loading):

- 1. A: Load Command "0000 1000".

- 2. B: Load Address Low Byte, 0x00.

- 3. Set OE to "0", and BS1 to "1". The Calibration byte can now be read at DATA.

- 4. Set OE to "1".

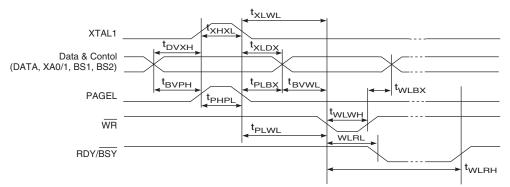

#### 25.7.15 Parallel Programming Characteristics

Figure 25-7. Parallel Programming Timing, Including some General Timing Requirements

Note: 1. The timing requirements shown in Figure 25-7 (i.e., t<sub>DVXH</sub>, t<sub>XHXL</sub>, and t<sub>XLDX</sub>) also apply to loading operation.

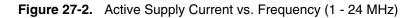

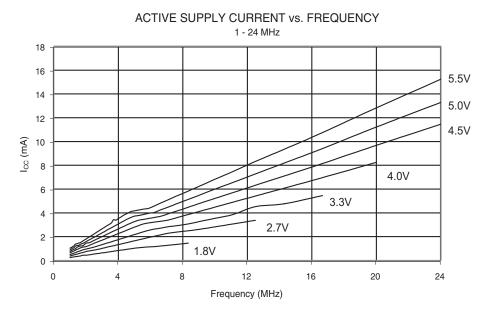

Figure 27-3. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 128 kHz)

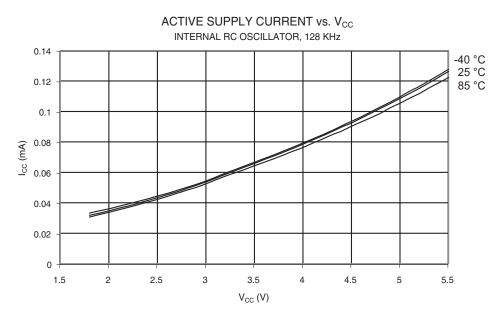

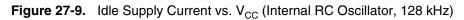

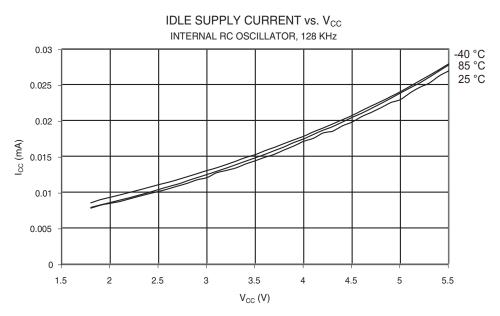

Figure 27-8. Idle Supply Current vs. Frequency (1 - 24 MHz)

### 28. Register Summary

| Address          | Name                 | Bit 7   | Bit 6   | Bit 5  | Bit 4          | Bit 3             | Bit 2          | Bit 1               | Bit 0  | Page    |

|------------------|----------------------|---------|---------|--------|----------------|-------------------|----------------|---------------------|--------|---------|

| (0xFF)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xFE)           | Reserved             | -       | _       | -      | -              | -                 | -              | -                   | -      |         |

| (0xFD)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xFC)           | Reserved             | -       | -       | -      | _              | -                 | -              | -                   | _      |         |

| (0xFB)           | Reserved             | _       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xFA)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF9)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF8)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF7)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF6)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF5)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF4)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF3)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF2)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF1)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xF0)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xEF)<br>(0xEE) | Reserved<br>Reserved |         |         |        |                |                   |                |                     |        |         |

| (0xED)           | Reserved             | _       |         | _      |                |                   |                |                     | _      |         |

| (0xEC)           | Reserved             |         |         | _      | _              |                   |                |                     |        |         |

| (0xEC)<br>(0xEB) | Reserved             | _       | _       | _      |                | _                 | _              | _                   | _      | 1       |

| (0xEA)           | Reserved             | _       | _       | _      | _              | _                 | _              | _                   | _      |         |

| (0xE9)           | Reserved             | -       | _       | _      | _              | _                 | _              | _                   | _      |         |

| (0xE8)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE7)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE6)           | Reserved             | _       | -       | -      | _              | -                 | -              | -                   | _      |         |

| (0xE5)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE4)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE3)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE2)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE1)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xE0)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xDF)           | Reserved             | -       | -       | -      | _              | -                 | -              | -                   | -      |         |

| (0xDE)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xDD)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xDC)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xDB)           | Reserved<br>Reserved | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xDA)<br>(0xD9) | Reserved             | _       |         |        |                |                   |                |                     |        |         |

| (0xD8)           | Reserved             | _       |         |        |                |                   |                |                     |        |         |

| (0xD0)<br>(0xD7) | Reserved             | _       | _       | _      | _              | _                 | _              | _                   | _      |         |

| (0xD6)           | Reserved             | _       | _       | _      | _              | _                 | _              | _                   | _      |         |

| (0xD5)           | Reserved             | _       | _       | _      | _              | _                 | _              | _                   | _      |         |

| (0xD4)           | Reserved             | _       | _       | _      | _              | _                 | _              | _                   | _      |         |

| (0xD3)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xD2)           | Reserved             | -       | -       | _      | _              | _                 | -              | _                   | -      |         |

| (0xD1)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xD0)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xCF)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xCE)           | Reserved             | -       | -       | -      | _              | -                 | _              | -                   | -      |         |

| (0xCD)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xCC)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xCB)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xCA)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xC9)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xC8)           | Reserved             | -       | -       | -      | -              | -                 | -              | -                   | -      |         |

| (0xC7)           | Reserved             | -       | -       | -      |                | -                 | -              | -                   | -      | 107     |

| (0xC6)           | UDR0                 |         |         |        | USART I/O      | Data Register     |                | Data Degister III I |        | 187     |

| (0xC5)           | UBRROH               |         |         |        | LISADT David D | lato Posister Law |                | Rate Register High  | I      | 191     |

| (0xC4)           | UBRROL               | _       | _       | _      | USART Baud F   | Rate Register Low | -              | _                   | -      | 191     |

| (0xC3)<br>(0xC2) | Reserved<br>UCSR0C   | UMSEL01 | UMSEL00 | UPM01  | -<br>UPM00     | USBS0             | UCSZ01 /UDORD0 | UCSZ00 / UCPHA0     | UCPOL0 | 189/203 |

| (0xC2)<br>(0xC1) | UCSR0E               | RXCIE0  | TXCIE0  | UDRIE0 | RXEN0          | TXEN0             | UCSZ01/0D0RD0  | RXB80               | TXB80  | 188     |

| (0xC0)           | UCSR0A               | RXC0    | TXC0    | UDRE0  | FE0            | DOR0              | UPE0           | U2X0                | MPCM0  | 187     |

| (0,00)           | UUUUN                | NAUU    | 1700    | UDREU  | I EV           | DOUN              | UPEU           | 0270                |        | 10/     |

| Address                                                                                                                                                                                                                                                                             | Name                                                                                                                                                                   | Bit 7                                                   | Bit 6                                            | Bit 5                                                           | Bit 4                                                                                                                                           | Bit 3                                                                                                                                                                                                            | Bit 2                                                                                                                                                    | Bit 1                                                            | Bit 0                                                            | Page                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| (0x7D)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        | -                                                                | -                                                                |                                                                                         |

| (0x7C)                                                                                                                                                                                                                                                                              | ADMUX                                                                                                                                                                  | REFS1                                                   | REFS0                                            | ADLAR                                                           | -                                                                                                                                               | MUX3                                                                                                                                                                                                             | MUX2                                                                                                                                                     | MUX1                                                             | MUX0                                                             | 250                                                                                     |

| (0x7B)                                                                                                                                                                                                                                                                              | ADCSRB                                                                                                                                                                 | -                                                       | ACME                                             | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | ADTS2                                                                                                                                                    | ADTS1                                                            | ADTS0                                                            | 253                                                                                     |

| (0x7A)                                                                                                                                                                                                                                                                              | ADCSRA                                                                                                                                                                 | ADEN                                                    | ADSC                                             | ADATE                                                           | ADIF                                                                                                                                            | ADIE                                                                                                                                                                                                             | ADPS2                                                                                                                                                    | ADPS1                                                            | ADPS0                                                            | 251                                                                                     |

| (0x79)                                                                                                                                                                                                                                                                              | ADCH                                                                                                                                                                   |                                                         |                                                  |                                                                 | ADC Data Rec                                                                                                                                    | 0,                                                                                                                                                                                                               |                                                                                                                                                          |                                                                  |                                                                  | 253                                                                                     |

| (0x78)                                                                                                                                                                                                                                                                              | ADCL                                                                                                                                                                   |                                                         |                                                  |                                                                 | ,                                                                                                                                               | ister Low byte                                                                                                                                                                                                   |                                                                                                                                                          |                                                                  |                                                                  | 253                                                                                     |

| (0x77)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        | -                                                                | -                                                                |                                                                                         |

| (0x76)                                                                                                                                                                                                                                                                              | Reserved<br>Reserved                                                                                                                                                   | -                                                       | -                                                |                                                                 | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        |                                                                  | -                                                                |                                                                                         |

| (0x75)<br>(0x74)                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                               | _                                                       | -                                                |                                                                 | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        | _                                                                | -                                                                |                                                                                         |

| (0x74)<br>(0x73)                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                               | _                                                       | _                                                |                                                                 | _                                                                                                                                               |                                                                                                                                                                                                                  | _                                                                                                                                                        |                                                                  | _                                                                |                                                                                         |

| (0x73)<br>(0x72)                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                               |                                                         | _                                                |                                                                 | _                                                                                                                                               | _                                                                                                                                                                                                                | _                                                                                                                                                        |                                                                  | _                                                                |                                                                                         |

| (0x71)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | _                                                       | _                                                | _                                                               | _                                                                                                                                               | _                                                                                                                                                                                                                | _                                                                                                                                                        | _                                                                | _                                                                |                                                                                         |

| (0x70)                                                                                                                                                                                                                                                                              | TIMSK2                                                                                                                                                                 | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | OCIE2B                                                                                                                                                   | OCIE2A                                                           | TOIE2                                                            | 154                                                                                     |

| (0x6F)                                                                                                                                                                                                                                                                              | TIMSK1                                                                                                                                                                 | -                                                       | -                                                | ICIE1                                                           | -                                                                                                                                               | -                                                                                                                                                                                                                | OCIE1B                                                                                                                                                   | OCIE1A                                                           | TOIE1                                                            | 133                                                                                     |

| (0x6E)                                                                                                                                                                                                                                                                              | TIMSK0                                                                                                                                                                 | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | OCIE0B                                                                                                                                                   | OCIE0A                                                           | TOIE0                                                            | 104                                                                                     |

| (0x6D)                                                                                                                                                                                                                                                                              | PCMSK2                                                                                                                                                                 | PCINT23                                                 | PCINT22                                          | PCINT21                                                         | PCINT20                                                                                                                                         | PCINT19                                                                                                                                                                                                          | PCINT18                                                                                                                                                  | PCINT17                                                          | PCINT16                                                          | 87                                                                                      |