Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

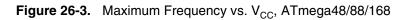

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168-20pu |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7. Power Management and Sleep Modes

Sleep modes enable the application to shut down unused modules in the MCU, thereby saving power. The AVR provides various sleep modes allowing the user to tailor the power consumption to the application's requirements.

To enter any of the five sleep modes, the SE bit in SMCR must be written to logic one and a SLEEP instruction must be executed. The SM2, SM1, and SM0 bits in the SMCR Register select which sleep mode (Idle, ADC Noise Reduction, Power-down, Power-save, or Standby) will be activated by the SLEEP instruction. See Table 7-1 for a summary. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles in addition to the start-up time, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the Register File and SRAM are unaltered when the device wakes up from sleep. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset Vector.

Figure 6-1 on page 25 presents the different clock systems in the ATmega48/88/168, and their distribution. The figure is helpful in selecting an appropriate sleep mode.

# 7.0.1 Sleep Mode Control Register – SMCR

The Sleep Mode Control Register contains control bits for power management.

| Bit           | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   | _    |

|---------------|---|---|---|---|-----|-----|-----|-----|------|

|               | - | - | - | - | SM2 | SM1 | SM0 | SE  | SMCR |

| Read/Write    | R | R | R | R | R/W | R/W | R/W | R/W | -    |

| Initial Value | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |      |

# • Bits 7..4 Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

# • Bits 3..1 – SM2..0: Sleep Mode Select Bits 2, 1, and 0

These bits select between the five available sleep modes as shown in Table 7-1.

| SM2 | SM1 | SM0 | Sleep Mode             |

|-----|-----|-----|------------------------|

| 0   | 0   | 0   | Idle                   |

| 0   | 0   | 1   | ADC Noise Reduction    |

| 0   | 1   | 0   | Power-down             |

| 0   | 1   | 1   | Power-save             |

| 1   | 0   | 0   | Reserved               |

| 1   | 0   | 1   | Reserved               |

| 1   | 1   | 0   | Standby <sup>(1)</sup> |

| 1   | 1   | 1   | Reserved               |

Table 7-1.

Sleep Mode Select

Note: 1. Standby mode is only recommended for use with external crystals or resonators.

# • Bit 0 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmer's

If Timer/Counter2 is enabled, it will keep running during sleep. The device can wake up from either Timer Overflow or Output Compare event from Timer/Counter2 if the corresponding Timer/Counter2 interrupt enable bits are set in TIMSK2, and the Global Interrupt Enable bit in SREG is set.

If Timer/Counter2 is not running, Power-down mode is recommended instead of Power-save mode.

The Timer/Counter2 can be clocked both synchronously and asynchronously in Power-save mode. If Timer/Counter2 is not using the asynchronous clock, the Timer/Counter Oscillator is stopped during sleep. If Timer/Counter2 is not using the synchronous clock, the clock source is stopped during sleep. Note that even if the synchronous clock is running in Power-save, this clock is only available for Timer/Counter2.

# 7.5 Standby Mode

When the SM2..0 bits are 110 and an external crystal/resonator clock option is selected, the SLEEP instruction makes the MCU enter Standby mode. This mode is identical to Power-down with the exception that the Oscillator is kept running. From Standby mode, the device wakes up in six clock cycles.

|                        | Act                | tive C               | lock I            | Doma                       | ins                | Oscil                        | Oscillators Wake-up Sources |                              |                      |        | s                   |     |     |         |

|------------------------|--------------------|----------------------|-------------------|----------------------------|--------------------|------------------------------|-----------------------------|------------------------------|----------------------|--------|---------------------|-----|-----|---------|

| Sleep Mode             | clk <sub>CPU</sub> | clk <sub>FLASH</sub> | clk <sub>iO</sub> | <b>c</b> lk <sub>ADC</sub> | clk <sub>ASY</sub> | Main Clock<br>Source Enabled | Timer Oscillator<br>Enabled | INT1, INT0 and<br>Pin Change | TWI Address<br>Match | Timer2 | SPM/EEPROM<br>Ready | ADC | WDT | Other/O |

| ldle                   |                    |                      | Х                 | Х                          | Х                  | Х                            | X <sup>(2)</sup>            | Х                            | Х                    | Х      | Х                   | Х   | Х   | Х       |

| ADC Noise<br>Reduction |                    |                      |                   | х                          | х                  | х                            | X <sup>(2)</sup>            | X <sup>(3)</sup>             | х                    | х      | х                   | х   | х   |         |

| Power-down             |                    |                      |                   |                            |                    |                              |                             | X <sup>(3)</sup>             | Х                    |        |                     |     | Х   |         |

| Power-save             |                    |                      |                   |                            | Х                  |                              | Х                           | X <sup>(3)</sup>             | Х                    | Х      |                     |     | Х   |         |

| Standby <sup>(1)</sup> |                    |                      |                   |                            |                    | Х                            |                             | X <sup>(3)</sup>             | Х                    |        |                     |     | Х   |         |

Table 7-2.

Active Clock Domains and Wake-up Sources in the Different Sleep Modes.

Notes: 1. Only recommended with external crystal or resonator selected as clock source.

2. If Timer/Counter2 is running in asynchronous mode.

3. For INT1 and INT0, only level interrupt.

# 7.6 Power Reduction Register

The Power Reduction Register, PRR, provides a method to stop the clock to individual peripherals to reduce power consumption. The current state of the peripheral is frozen and the I/O registers can not be read or written. Resources used by the peripheral when stopping the clock will remain occupied, hence the peripheral should in most cases be disabled before stopping the clock. Waking up a module, which is done by clearing the bit in PRR, puts the module in the same state as before shutdown.

Module shutdown can be used in Idle mode and Active mode to significantly reduce the overall power consumption. See "Power-Down Supply Current" on page 315 for examples. In all other sleep modes, the clock is already stopped.

# 9.2 Interrupt Vectors in ATmega88

| Table 9-2. | Reset and Interrupt Vectors in ATmega88 |

|------------|-----------------------------------------|

|            | ricoot and michapt rootoro mirinogaoo   |

| Vector No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                    |

|------------|-----------------------------------|--------------|-------------------------------------------------------------------------|

| 1          | 0x000 <sup>(1)</sup>              | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2          | 0x001                             | INT0         | External Interrupt Request 0                                            |

| 3          | 0x002                             | INT1         | External Interrupt Request 1                                            |

| 4          | 0x003                             | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5          | 0x004                             | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6          | 0x005                             | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7          | 0x006                             | WDT          | Watchdog Time-out Interrupt                                             |

| 8          | 0x007                             | TIMER2 COMPA | Timer/Counter2 Compare Match A                                          |

| 9          | 0x008                             | TIMER2 COMPB | Timer/Counter2 Compare Match B                                          |

| 10         | 0x009                             | TIMER2 OVF   | Timer/Counter2 Overflow                                                 |

| 11         | 0x00A                             | TIMER1 CAPT  | Timer/Counter1 Capture Event                                            |

| 12         | 0x00B                             | TIMER1 COMPA | Timer/Counter1 Compare Match A                                          |

| 13         | 0x00C                             | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                          |

| 14         | 0x00D                             | TIMER1 OVF   | Timer/Counter1 Overflow                                                 |

| 15         | 0x00E                             | TIMER0 COMPA | Timer/Counter0 Compare Match A                                          |

| 16         | 0x00F                             | TIMER0 COMPB | Timer/Counter0 Compare Match B                                          |

| 17         | 0x010                             | TIMER0 OVF   | Timer/Counter0 Overflow                                                 |

| 18         | 0x011                             | SPI, STC     | SPI Serial Transfer Complete                                            |

| 19         | 0x012                             | USART, RX    | USART Rx Complete                                                       |

| 20         | 0x013                             | USART, UDRE  | USART, Data Register Empty                                              |

| 21         | 0x014                             | USART, TX    | USART, Tx Complete                                                      |

| 22         | 0x015                             | ADC          | ADC Conversion Complete                                                 |

| 23         | 0x016                             | EE READY     | EEPROM Ready                                                            |

| 24         | 0x017                             | ANALOG COMP  | Analog Comparator                                                       |

| 25         | 0x018                             | TWI          | 2-wire Serial Interface                                                 |

| 26         | 0x019                             | SPM READY    | Store Program Memory Ready                                              |

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at

reset, see "Boot Loader Support - Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264.

2. When the IVSEL bit in MCUCR is set, Interrupt Vectors will be moved to the start of the Boot Flash Section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash Section.

Table 9-3 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

The setup of the OC0x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0x value is to use the Force Output Compare (FOC0x) strobe bits in Normal mode. The OC0x Registers keep their values even when changing between Waveform Generation modes.

Be aware that the COM0x1:0 bits are not double buffered together with the compare value. Changing the COM0x1:0 bits will take effect immediately.

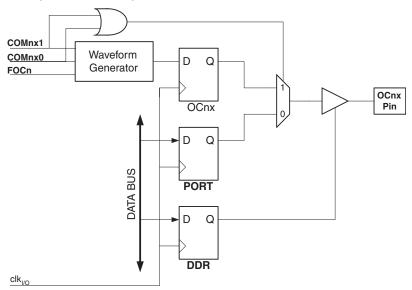

# 12.5 Compare Match Output Unit

The Compare Output mode (COM0x1:0) bits have two functions. The Waveform Generator uses the COM0x1:0 bits for defining the Output Compare (OC0x) state at the next compare match. Also, the COM0x1:0 bits control the OC0x pin output source. Figure 12-4 shows a simplified schematic of the logic affected by the COM0x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O port control registers (DDR and PORT) that are affected by the COM0x1:0 bits are shown. When referring to the OC0x state, the reference is for the internal OC0x Register, not the OC0x pin. If a system reset occur, the OC0x Register is reset to "0".

Figure 12-4. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OC0x) from the Waveform Generator if either of the COM0x1:0 bits are set. However, the OC0x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC0x pin (DDR\_OC0x) must be set as output before the OC0x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC0x state before the output is enabled. Note that some COM0x1:0 bit settings are reserved for certain modes of operation. See Section "12.8" on page 99.

#### 12.5.1 Compare Output Mode and Waveform Generation

The Waveform Generator uses the COM0x1:0 bits differently in Normal, CTC, and PWM modes. For all modes, setting the COM0x1:0 = 0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next compare match. For compare output actions in the Table 12-7 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

| COM0B1 | COM0B0 | Description                                                                                 |

|--------|--------|---------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected.                                                   |

| 0      | 1      | Reserved                                                                                    |

| 1      | 0      | Clear OC0B on Compare Match when up-counting. Set OC0B on Compare Match when down-counting. |

| 1      | 1      | Set OC0B on Compare Match when up-counting. Clear OC0B on Compare Match when down-counting. |

Table 12-7.

Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 96 for more details.

## • Bits 3, 2 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

## • Bits 1:0 - WGM01:0: Waveform Generation Mode

Combined with the WGM02 bit found in the TCCR0B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of waveform generation to be used, see Table 12-8. Modes of operation supported by the Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare Match (CTC) mode, and two types of Pulse Width Modulation (PWM) modes (see "Modes of Operation" on page 93).

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of<br>OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|------|-------|-------|-------|---------------------------------------|------|----------------------|--------------------------------------|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate            | MAX                                  |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP                  | BOTTOM                               |

| 2    | 0     | 1     | 0     | СТС                                   | OCRA | Immediate            | MAX                                  |

| 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | TOP                  | MAX                                  |

| 4    | 1     | 0     | 0     | Reserved                              | _    | _                    | _                                    |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP                  | BOTTOM                               |

| 6    | 1     | 1     | 0     | Reserved                              | _    | _                    | _                                    |

| 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | TOP                  | TOP                                  |

Table 12-8.

Waveform Generation Mode Bit Description

Notes: 1. MAX = 0xFF 2. BOTTOM = 0x00

prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCR1x Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR1x Buffer Register, and if double buffering is disabled the CPU will access the OCR1x directly. The content of the OCR1x (Buffer or Compare) Register is only changed by a write operation (the Timer/Counter does not update this register automatically as the TCNT1 and ICR1 Register). Therefore OCR1x is not read via the high byte temporary register (TEMP). However, it is a good practice to read the low byte first as when accessing other 16-bit registers. Writing the OCR1x Registers must be done via the TEMP Register since the compare of all 16 bits is done continuously. The high byte (OCR1xH) has to be written first. When the high byte I/O location is written by the CPU, the TEMP Register will be updated by the value written. Then when the low byte (OCR1xL) is written to the lower eight bits, the high byte will be copied into the upper 8-bits of either the OCR1x buffer or OCR1x Compare Register in the same system clock cycle.

For more information of how to access the 16-bit registers refer to "Accessing 16-bit Registers" on page 108.

### 13.6.1 Force Output Compare

In non-PWM Waveform Generation modes, the match output of the comparator can be forced by writing a one to the *Force Output Compare* (FOC1x) bit. Forcing compare match will not set the OCF1x Flag or reload/clear the timer, but the OC1x pin will be updated as if a real compare match had occurred (the COM11:0 bits settings define whether the OC1x pin is set, cleared or toggled).

#### 13.6.2 Compare Match Blocking by TCNT1 Write

All CPU writes to the TCNT1 Register will block any compare match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCR1x to be initialized to the same value as TCNT1 without triggering an interrupt when the Timer/Counter clock is enabled.

## 13.6.3 Using the Output Compare Unit

Since writing TCNT1 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT1 when using any of the Output Compare channels, independent of whether the Timer/Counter is running or not. If the value written to TCNT1 equals the OCR1x value, the compare match will be missed, resulting in incorrect waveform generation. Do not write the TCNT1 equal to TOP in PWM modes with variable TOP values. The compare match for the TOP will be ignored and the counter will continue to 0xFFFF. Similarly, do not write the TCNT1 value equal to BOTTOM when the counter is downcounting.

The setup of the OC1x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC1x value is to use the Force Output Compare (FOC1x) strobe bits in Normal mode. The OC1x Register keeps its value even when changing between Waveform Generation modes.

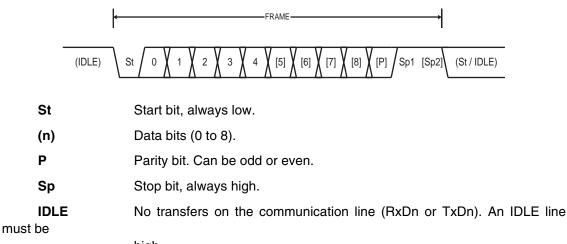

Be aware that the COM1x1:0 bits are not double buffered together with the compare value. Changing the COM1x1:0 bits will take effect immediately. A frame starts with the start bit followed by the least significant data bit. Then the next data bits, up to a total of nine, are succeeding, ending with the most significant bit. If enabled, the parity bit is inserted after the data bits, before the stop bits. When a complete frame is transmitted, it can be directly followed by a new frame, or the communication line can be set to an idle (high) state. Figure 17-4 illustrates the possible combinations of the frame formats. Bits inside brackets are optional.

high.

The frame format used by the USART is set by the UCSZn2:0, UPMn1:0 and USBSn bits in UCSRnB and UCSRnC. The Receiver and Transmitter use the same setting. Note that changing the setting of any of these bits will corrupt all ongoing communication for both the Receiver and Transmitter.

The USART Character SiZe (UCSZn2:0) bits select the number of data bits in the frame. The USART Parity mode (UPMn1:0) bits enable and set the type of parity bit. The selection between one or two stop bits is done by the USART Stop Bit Select (USBSn) bit. The Receiver ignores the second stop bit. An FE (Frame Error) will therefore only be detected in the cases where the first stop bit is zero.

# 17.3.1 Parity Bit Calculation

The parity bit is calculated by doing an exclusive-or of all the data bits. If odd parity is used, the result of the exclusive or is inverted. The relation between the parity bit and data bits is as follows:

$\begin{array}{l} P_{even} = d_{n-1} \oplus \ldots \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 0 \\ P_{odd} = d_{n-1} \oplus \ldots \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 1 \end{array}$

| P <sub>even</sub> | Parity bit using even parity |

|-------------------|------------------------------|

|-------------------|------------------------------|

P<sup>odd</sup> Parity bit using odd parity

d<sub>n</sub> Data bit n of the character

If used, the parity bit is located between the last data bit and first stop bit of a serial frame.

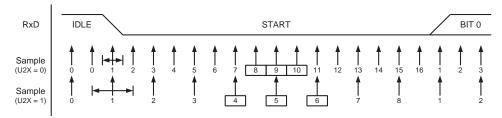

When the clock recovery logic detects a high (idle) to low (start) transition on the RxDn line, the start bit detection sequence is initiated. Let sample 1 denote the first zero-sample as shown in the figure. The clock recovery logic then uses samples 8, 9, and 10 for Normal mode, and samples 4, 5, and 6 for Double Speed mode (indicated with sample numbers inside boxes on the figure), to decide if a valid start bit is received. If two or more of these three samples have logical high levels (the majority wins), the start bit is rejected as a noise spike and the Receiver starts looking for the next high to low-transition. If however, a valid start bit is detected, the clock recovery logic is synchronized and the data recovery can begin. The synchronization process is repeated for each start bit.

# 17.7.2 Asynchronous Data Recovery

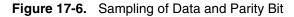

When the receiver clock is synchronized to the start bit, the data recovery can begin. The data recovery unit uses a state machine that has 16 states for each bit in Normal mode and eight states for each bit in Double Speed mode. Figure 17-6 shows the sampling of the data bits and the parity bit. Each of the samples is given a number that is equal to the state of the recovery unit.

The decision of the logic level of the received bit is taken by doing a majority voting of the logic value to the three samples in the center of the received bit. The center samples are emphasized on the figure by having the sample number inside boxes. The majority voting process is done as follows: If two or all three samples have high levels, the received bit is registered to be a logic 1. If two or all three samples have low levels, the received bit is registered to be a logic 0. This majority voting process acts as a low pass filter for the incoming signal on the RxDn pin. The receivery process is then repeated until a complete frame is received. Including the first stop bit. Note that the Receiver only uses the first stop bit of a frame.

Figure 17-7 shows the sampling of the stop bit and the earliest possible beginning of the start bit of the next frame.

## • Bit 5 – UDRIEn: USART Data Register Empty Interrupt Enable n

Writing this bit to one enables interrupt on the UDREn Flag. A Data Register Empty interrupt will be generated only if the UDRIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the UDREn bit in UCSRnA is set.

### • Bit 4 – RXENn: Receiver Enable n

Writing this bit to one enables the USART Receiver. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FEn, DORn, and UPEn Flags.

## • Bit 3 – TXENn: Transmitter Enable n

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn port.

## • Bit 2 – UCSZn2: Character Size n

The UCSZn2 bits combined with the UCSZn1:0 bit in UCSRnC sets the number of data bits (Character SiZe) in a frame the Receiver and Transmitter use.

## • Bit 1 - RXB8n: Receive Data Bit 8 n

RXB8n is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDRn.

#### • Bit 0 – TXB8n: Transmit Data Bit 8 n

TXB8n is the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. Must be written before writing the low bits to UDRn.

# 17.9.4 USART Control and Status Register n C – UCSRnC

| Bit           | 7       | 6       | 5     | 4     | 3     | 2      | 1      | 0      | _      |

|---------------|---------|---------|-------|-------|-------|--------|--------|--------|--------|

|               | UMSELn1 | UMSELn0 | UPMn1 | UPMn0 | USBSn | UCSZn1 | UCSZn0 | UCPOLn | UCSRnC |

| Read/Write    | R/W     | R/W     | R/W   | R/W   | R/W   | R/W    | R/W    | R/W    | •      |

| Initial Value | 0       | 0       | 0     | 0     | 0     | 1      | 1      | 0      |        |

#### • Bits 7:6 – UMSELn1:0 USART Mode Select

These bits select the mode of operation of the USARTn as shown in Table 17-4.

#### Table 17-4. UMSELn Bits Settings

| UMSELn1 | UMSELn0 | Mode                              |

|---------|---------|-----------------------------------|

| 0       | 0       | Asynchronous USART                |

| 0       | 1       | Synchronous USART                 |

| 1       | 0       | (Reserved)                        |

| 1       | 1       | Master SPI (MSPIM) <sup>(1)</sup> |

Note: 1. See "USART in SPI Mode" on page 196 for full description of the Master SPI Mode (MSPIM) operation

After initialization the USART is ready for doing data transfers. A data transfer is initiated by writing to the UDRn I/O location. This is the case for both sending and receiving data since the transmitter controls the transfer clock. The data written to UDRn is moved from the transmit buffer to the shift register when the shift register is ready to send a new frame.

Note: To keep the input buffer in sync with the number of data bytes transmitted, the UDRn register must be read once for each byte transmitted. The input buffer operation is identical to normal USART mode, i.e. if an overflow occurs the character last received will be lost, not the first data in the buffer. This means that if four bytes are transferred, byte 1 first, then byte 2, 3, and 4, and the UDRn is not read before all transfers are completed, then byte 3 to be received will be lost, and not byte 1.

The following code examples show a simple USART in MSPIM mode transfer function based on polling of the Data Register Empty (UDREn) Flag and the Receive Complete (RXCn) Flag. The USART has to be initialized before the function can be used. For the assembly code, the data to be sent is assumed to be stored in Register R16 and the data received will be available in the same register (R16) after the function returns.

The function simply waits for the transmit buffer to be empty by checking the UDREn Flag, before loading it with new data to be transmitted. The function then waits for data to be present in the receive buffer by checking the RXCn Flag, before reading the buffer and returning the value.

## 21.4.1 ADC Input Channels

When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:

In Single Conversion mode, always select the channel before starting the conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the conversion to complete before changing the channel selection.

In Free Running mode, always select the channel before starting the first conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the first conversion to complete, and then change the channel selection. Since the next conversion has already started automatically, the next result will reflect the previous channel selection. Subsequent conversions will reflect the new channel selection.

## 21.4.2 ADC Voltage Reference

The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed  $V_{REF}$  will result in codes close to 0x3FF.  $V_{REF}$  can be selected as either AV<sub>CC</sub>, internal 1.1V reference, or external AREF pin.

$AV_{CC}$  is connected to the ADC through a passive switch. The internal 1.1V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground.  $V_{REF}$  can also be measured at the AREF pin with a high impedant voltmeter. Note that  $V_{REF}$  is a high impedant source, and only a capacitive load should be connected in a system.

If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between  $AV_{CC}$  and 1.1V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.

# 21.5 ADC Noise Canceler

The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:

- a. Make sure that the ADC is enabled and is not busy converting. Single Conversion mode must be selected and the ADC conversion complete interrupt must be enabled.

- b. Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion once the CPU has been halted.

- c. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.

Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before entering such sleep modes to avoid excessive power consumption.

| Variable |          | Corresponding<br>Z-value <sup>(1)</sup> | Description                                                                                                                 |

|----------|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PCMSB    | 12       |                                         | Most significant bit in the Program Counter. (The Program Counter is 12 bits PC[11:0])                                      |

| PAGEMSB  | 5        |                                         | Most significant bit which is used to address<br>the words within one page (64 words in a page<br>requires 6 bits PC [5:0]) |

| ZPCMSB   |          | Z13                                     | Bit in Z-register that is mapped to PCMSB. Because Z0 is not used, the ZPCMSB equals PCMSB + 1.                             |

| ZPAGEMSB |          | Z6                                      | Bit in Z-register that is mapped to PAGEMSB.<br>Because Z0 is not used, the ZPAGEMSB equals<br>PAGEMSB + 1.                 |

| PCPAGE   | PC[12:6] | Z13:Z7                                  | Program counter page address: Page select, for page erase and page write                                                    |

| PCWORD   | PC[5:0]  | Z6:Z1                                   | Program counter word address: Word select, for filling temporary buffer (must be zero during page write operation)          |

Table 24-11.

Explanation of Different Variables used in Figure 24-3 and the Mapping to the Z-pointer, ATmega168

Note: 1. Z15:Z14: always ignored

Z0: should be zero for all SPM commands, byte select for the LPM instruction. See "Addressing the Flash During Self-Programming" on page 270 for details about the use of Z-pointer during Self-Programming.

# 25.4 Calibration Byte

The ATmega48/88/168 has a byte calibration value for the internal RC Oscillator. This byte resides in the high byte of address 0x000 in the signature address space. During reset, this byte is automatically written into the OSCCAL Register to ensure correct frequency of the calibrated RC Oscillator.

# 25.5 Page Size

| Table 23-0. No. of Words in a rage and No. of rages in the riash |                         |           |         |                 |          |       |

|------------------------------------------------------------------|-------------------------|-----------|---------|-----------------|----------|-------|

| Device                                                           | Flash Size              | Page Size | PCWORD  | No. of<br>Pages | PCPAGE   | PCMSB |

| ATmega48                                                         | 2K words<br>(4K bytes)  | 32 words  | PC[4:0] | 64              | PC[10:5] | 10    |

| ATmega88                                                         | 4K words<br>(8K bytes)  | 32 words  | PC[4:0] | 128             | PC[11:5] | 11    |

| ATmega168                                                        | 8K words<br>(16K bytes) | 64 words  | PC[5:0] | 128             | PC[12:6] | 12    |

Table 25-8.

No. of Words in a Page and No. of Pages in the Flash

| Table 25-9. | No. of Words in a Page and No. of Pages in the EEPROM |

|-------------|-------------------------------------------------------|

|-------------|-------------------------------------------------------|

| Device    | EEPROM<br>Size | Page<br>Size | PCWORD   | No. of<br>Pages | PCPAGE   | EEAMSB |

|-----------|----------------|--------------|----------|-----------------|----------|--------|

| ATmega48  | 256 bytes      | 4 bytes      | EEA[1:0] | 64              | EEA[7:2] | 7      |

| ATmega88  | 512 bytes      | 4 bytes      | EEA[1:0] | 128             | EEA[8:2] | 8      |

| ATmega168 | 512 bytes      | 4 bytes      | EEA[1:0] | 128             | EEA[8:2] | 8      |

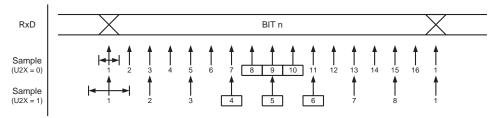

# 25.6 Parallel Programming Parameters, Pin Mapping, and Commands

This section describes how to parallel program and verify Flash Program memory, EEPROM Data memory, Memory Lock bits, and Fuse bits in the ATmega48/88/168. Pulses are assumed to be at least 250 ns unless otherwise noted.

# 25.6.1 Signal Names

In this section, some pins of the ATmega48/88/168 are referenced by signal names describing their functionality during parallel programming, see Figure 25-1 and Table 25-10. Pins not described in the following table are referenced by pin names.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding is shown in Table 25-12.

When pulsing  $\overline{WR}$  or  $\overline{OE}$ , the command loaded determines the action executed. The different Commands are shown in Table 25-13.

- 5. E: Latch data (give PAGEL a positive pulse).

- K: Repeat 3 through 5 until the entire buffer is filled.

## L: Program EEPROM page

- 1. Set BS1 to "0".

- 2. Give WR a negative pulse. This starts programming of the EEPROM page. RDY/BSY goes low.

- Wait until to RDY/BSY goes high before programming the next page (See Figure 25-4 for signal waveforms).

#### Figure 25-4. Programming the EEPROM Waveforms

#### 25.7.6 Reading the Flash

The algorithm for reading the Flash memory is as follows (refer to "Programming the Flash" on page 287 for details on Command and Address loading):

- 1. A: Load Command "0000 0010".

- 2. G: Load Address High Byte (0x00 0xFF).

- 3. B: Load Address Low Byte (0x00 0xFF).

- 4. Set OE to "0", and BS1 to "0". The Flash word low byte can now be read at DATA.

- 5. Set BS1 to "1". The Flash word high byte can now be read at DATA.

- 6. Set OE to "1".

#### 25.7.7 Reading the EEPROM

The algorithm for reading the EEPROM memory is as follows (refer to "Programming the Flash" on page 287 for details on Command and Address loading):

- 1. A: Load Command "0000 0011".

- 2. G: Load Address High Byte (0x00 0xFF).

- 3. B: Load Address Low Byte (0x00 0xFF).

- 4. Set  $\overline{OE}$  to "0", and BS1 to "0". The EEPROM Data byte can now be read at DATA.

- 5. Set OE to "1".

|                   | 5 5 7 (                    | <i>.</i> | `   | ,   |       |

|-------------------|----------------------------|----------|-----|-----|-------|

| Symbol            | Parameter                  | Min      | Тур | Max | Units |

| t <sub>BVDV</sub> | BS1 Valid to DATA valid    | 0        |     | 250 | ns    |

| t <sub>OLDV</sub> | OE Low to DATA Valid       |          |     | 250 | ns    |

| t <sub>OHDZ</sub> | OE High to DATA Tri-stated |          |     | 250 | ns    |

**Table 25-14.** Parallel Programming Characteristics,  $V_{CC} = 5V \pm 10\%$  (Continued)

Notes: 1. t<sub>WLRH</sub> is valid for the Write Flash, Write EEPROM, Write Fuse bits and Write Lock bits commands.

2. t<sub>WLRH CE</sub> is valid for the Chip Erase command.

# 25.8 Serial Downloading

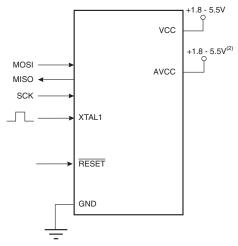

Both the Flash and EEPROM memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output). After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase operations can be executed. NOTE, in Table 25-15 on page 296, the pin mapping for SPI programming is listed. Not all parts use the SPI pins dedicated for the internal SPI interface.

Figure 25-10. Serial Programming and Verify<sup>(1)</sup>

Notes: 1. If the device is clocked by the internal Oscillator, it is no need to connect a clock source to the XTAL1 pin.

2.  $V_{CC}$  - 0.3V <  $AV_{CC}$  <  $V_{CC}$  + 0.3V, however,  $AV_{CC}$  should always be within 1.8 - 5.5V

When programming the EEPROM, an auto-erase cycle is built into the self-timed programming operation (in the Serial mode ONLY) and there is no need to first execute the Chip Erase instruction. The Chip Erase operation turns the content of every memory location in both the Program and EEPROM arrays into 0xFF.

Depending on CKSEL Fuses, a valid clock must be present. The minimum low and high periods for the serial clock (SCK) input are defined as follows:

Low: > 2 CPU clock cycles for  $f_{ck}$  < 12 MHz, 3 CPU clock cycles for  $f_{ck}$  >= 12 MHz High: > 2 CPU clock cycles for  $f_{ck}$  < 12 MHz, 3 CPU clock cycles for  $f_{ck}$  >= 12 MHz

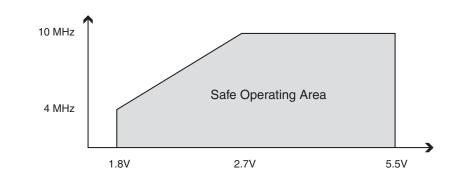

Figure 26-2. Maximum Frequency vs. V<sub>CC</sub>, ATmega48V/88V/168V

# 26.6 2-wire Serial Interface Characteristics

Table 26-2 describes the requirements for devices connected to the 2-wire Serial Bus. The ATmega48/88/168 2-wire Serial Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 26-4.

Table 26-2. 2-wire Serial Bus Requirements

| Symbol             | Parameter                                        | Condition                                      | Min                                      | Мах                   | Units |

|--------------------|--------------------------------------------------|------------------------------------------------|------------------------------------------|-----------------------|-------|

| VIL                | Input Low-voltage                                |                                                | -0.5                                     | 0.3 V <sub>CC</sub>   | V     |

| VIH                | Input High-voltage                               |                                                | 0.7 V <sub>CC</sub>                      | V <sub>CC</sub> + 0.5 | V     |

| (1)<br>Vhys        | Hysteresis of Schmitt Trigger Inputs             |                                                | 0.05 V <sub>CC</sub> <sup>(2)</sup>      | _                     | V     |

| VOL <sup>(1)</sup> | Output Low-voltage                               | 3 mA sink current                              | 0                                        | 0.4                   | V     |

| tr <sup>(1)</sup>  | Rise Time for both SDA and SCL                   |                                                | 20 + 0.1C <sub>b</sub> <sup>(3)(2)</sup> | 300                   | ns    |

| (1)<br>tof         | Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ | 10 pF < C <sub>b</sub> < 400 pF <sup>(3)</sup> | 20 + 0.1C <sub>b</sub> <sup>(3)(2)</sup> | 250                   | ns    |

| tSP <sup>(1)</sup> | Spikes Suppressed by Input Filter                |                                                | 0                                        | 50 <sup>(2)</sup>     | ns    |

| l <sub>i</sub>     | Input Current each I/O Pin                       | $0.1V_{\rm CC} < V_{\rm i} < 0.9V_{\rm CC}$    | -10                                      | 10                    | μA    |

| PRR bit  | Additional Current consumption<br>compared to Active with external<br>clock<br>(see Figure 27-1 and Figure 27-2) | Additional Current consumption<br>compared to Idle with external clock<br>(see Figure 27-7 and Figure 27-8) |

|----------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| PRUSART0 | 3.3%                                                                                                             | 18%                                                                                                         |

| PRTWI    | 4.8%                                                                                                             | 26%                                                                                                         |

| PRTIM2   | 4.7%                                                                                                             | 25%                                                                                                         |

| PRTIM1   | 2.0%                                                                                                             | 11%                                                                                                         |

| PRTIM0   | 1.6%                                                                                                             | 8.5%                                                                                                        |

| PRSPI    | 6.1%                                                                                                             | 33%                                                                                                         |

| PRADC    | 4.9%                                                                                                             | 26%                                                                                                         |

Table 27-2. Additional Current Consumption (percentage) in Active and Idle mode

It is possible to calculate the typical current consumption based on the numbers from Table 2 for other  $V_{CC}$  and frequency settings than listed in Table 1.

#### 27.3.0.1 Example 1

Calculate the expected current consumption in idle mode with USART0, TIMER1, and TWI enabled at  $V_{CC} = 3.0V$  and F = 1MHz. From Table 2, third column, we see that we need to add 18% for the USART0, 26% for the TWI, and 11% for the TIMER1 module. Reading from Figure 3, we find that the idle current consumption is ~0,075mA at  $V_{CC} = 3.0V$  and F = 1MHz. The total current consumption in idle mode with USART0, TIMER1, and TWI enabled, gives:

ICCtotal  $\approx 0.075 mA \bullet (1 + 0.18 + 0.26 + 0.11) \approx 0.116 mA$

#### 27.3.0.2 Example 2

Same conditions as in example 1, but in active mode instead. From Table 2, second column we see that we need to add 3.3% for the USART0, 4.8% for the TWI, and 2.0% for the TIMER1 module. Reading from Figure 1, we find that the active current consumption is ~0,42mA at  $V_{CC}$  = 3.0V and F = 1MHz. The total current consumption in idle mode with USART0, TIMER1, and TWI enabled, gives:

$ICC_{total} \approx 0.42 mA \bullet (1 + 0.033 + 0.048 + 0.02) \approx 0.46 mA$

#### 27.3.0.3 Example 3

All I/O modules should be enabled. Calculate the expected current consumption in active mode at  $V_{CC} = 3.6V$  and F = 10MHz. We find the active current consumption without the I/O modules to be ~ 4.0mA (from Figure 2). Then, by using the numbers from Table 2 - second column, we find the total current consumption:

$ICC_{total} \approx 4.0 mA \bullet (1 + 0.033 + 0.048 + 0.047 + 0.02 + 0.016 + 0.061 + 0.049) \approx 5.1 mA$

27.9 Pin Thresholds and Hysteresis

|    | 17.10Examples of Baud Rate Setting                            | 191 |

|----|---------------------------------------------------------------|-----|

| 18 | USART in SPI Mode                                             | 196 |

|    | 18.1Overview                                                  | 196 |

|    | 18.2Clock Generation                                          | 196 |

|    | 18.3SPI Data Modes and Timing                                 | 197 |

|    | 18.4Frame Formats                                             | 198 |

|    | 18.5Data Transfer                                             | 199 |

|    | 18.6USART MSPIM Register Description                          | 201 |

|    | 18.7AVR USART MSPIM vs. AVR SPI                               | 204 |

| 19 | 2-wire Serial Interface                                       | 205 |

|    | 19.1Features                                                  | 205 |

|    | 19.22-wire Serial Interface Bus Definition                    | 205 |

|    | 19.3Data Transfer and Frame Format                            | 206 |

|    | 19.4Multi-master Bus Systems, Arbitration and Synchronization | 209 |

|    | 19.5Overview of the TWI Module                                | 211 |

|    | 19.6TWI Register Description                                  | 213 |

|    | 19.7Using the TWI                                             | 217 |

|    | 19.8Transmission Modes                                        | 221 |

|    | 19.9Multi-master Systems and Arbitration                      | 234 |

| 20 | Analog Comparator                                             | 235 |

|    | 20.1Analog Comparator Multiplexed Input                       | 237 |

| 21 | Analog-to-Digital Converter                                   | 239 |

|    | 21.1Features                                                  | 239 |

|    | 21.2Starting a Conversion                                     | 241 |

|    | 21.3Prescaling and Conversion Timing                          | 242 |

|    | 21.4Changing Channel or Reference Selection                   | 244 |

|    | 21.5ADC Noise Canceler                                        | 245 |

|    | 21.6ADC Conversion Result                                     | 250 |

| 22 | debugWIRE On-chip Debug System                                | 255 |

|    | 22.1Features                                                  | 255 |

|    | 22.20verview                                                  | 255 |

|    | 22.3Physical Interface                                        | 255 |

|    | 22.4Software Break Points                                     | 256 |

|    | 22.5Limitations of debugWIRE                                  | 256 |