#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-TQFP                                                                   |

| Supplier Device Package    | 32-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168v-10ai |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

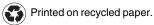

# Figure 6-3. Crystal Oscillator Connections

Table 6-6.

Start-up Times for the Full Swing Crystal Oscillator Clock Selection

| Oscillator Source /<br>Power Conditions  | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | CKSEL0 | SUT10 |

|------------------------------------------|----------------------------------------------------|------------------------------------------------------------|--------|-------|

| Ceramic resonator, fast rising power     | 258 CK                                             | 14CK + 4.1 ms <sup>(1)</sup>                               | 0      | 00    |

| Ceramic resonator, slowly rising power   | 258 CK                                             | 14CK + 65 ms <sup>(1)</sup>                                | 0      | 01    |

| Ceramic resonator, BOD enabled           | 1K CK                                              | 14CK <sup>(2)</sup>                                        | 0      | 10    |

| Ceramic resonator, fast rising power     | 1K CK                                              | 14CK + 4.1 ms <sup>(2)</sup>                               | 0      | 11    |

| Ceramic resonator, slowly rising power   | 1K CK                                              | 14CK + 65 ms <sup>(2)</sup>                                | 1      | 00    |

| Crystal Oscillator, BOD<br>enabled       | 16K CK                                             | 14CK                                                       | 1      | 01    |

| Crystal Oscillator, fast<br>rising power | 16K CK                                             | 14CK + 4.1 ms                                              | 1      | 10    |

| Crystal Oscillator, slowly rising power  | 16K CK                                             | 14CK + 65 ms                                               | 1      | 11    |

Notes: 1. These options should only be used when not operating close to the maximum frequency of the device, and only if frequency stability at start-up is not important for the application. These options are not suitable for crystals.

2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum frequency of the device, and if frequency stability at start-up is not important for the application.

| CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | <b>Clock Division Factor</b> |  |

|--------|--------|--------|--------|------------------------------|--|

| 0      | 0      | 0      | 0      | 1                            |  |

| 0      | 0      | 0      | 1      | 2                            |  |

| 0      | 0      | 1      | 0      | 4                            |  |

| 0      | 0      | 1      | 1      | 8                            |  |

| 0      | 1      | 0      | 0      | 16                           |  |

| 0      | 1      | 0      | 1      | 32                           |  |

| 0      | 1      | 1      | 0      | 64                           |  |

| 0      | 1      | 1      | 1      | 128                          |  |

| 1      | 0      | 0      | 0      | 256                          |  |

| 1      | 0      | 0      | 1      | Reserved                     |  |

| 1      | 0      | 1      | 0      | Reserved                     |  |

| 1      | 0      | 1      | 1      | Reserved                     |  |

| 1      | 1      | 0      | 0      | Reserved                     |  |

| 1      | 1      | 0      | 1      | Reserved                     |  |

| 1      | 1      | 1      | 0      | Reserved                     |  |

| 1      | 1      | 1      | 1      | Reserved                     |  |

ATmega48/88/168

| /            |                                          |                                           |

|--------------|------------------------------------------|-------------------------------------------|

| 0x0033RESET: | ldi                                      | r16, high(RAMEND); Main program start     |

| 0x0034       | out                                      | SPH,r16 ; Set Stack Pointer to top of RAM |

| 0x0035       | ldi                                      | r16, low(RAMEND)                          |

| 0x0036       | out                                      | SPL,r16                                   |

| 0x0037       | sei                                      | ; Enable interrupts                       |

| 0x0038       | <instr< th=""><th>&gt; xxx</th></instr<> | > xxx                                     |

|              |                                          |                                           |

. . . ... ...

When the BOOTRST Fuse is unprogrammed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address          | Labels | Code                                                       |                 | С | Comments                           |

|------------------|--------|------------------------------------------------------------|-----------------|---|------------------------------------|

| 0x0000           | RESET: | ldi                                                        | r16,high(RAMENI | ) | ; Main program start               |

| 0x0001           |        | out                                                        | SPH,r16         | ; | Set Stack Pointer to top of RAM    |

| 0x0002           |        | ldi                                                        | r16,low(RAMEND) | ) |                                    |

| 0x0003<br>0x0004 |        | out<br>sei                                                 | SPL,r16         | ; | Enable interrupts                  |

| 0x0005           |        | <instr< th=""><th>&gt; xxx</th><th></th><th></th></instr<> | > xxx           |   |                                    |

| ;                |        |                                                            |                 |   |                                    |

| .org 0xC         | 02     |                                                            |                 |   |                                    |

| 0x1C02           |        | jmp                                                        | EXT_INT0        | ; | IRQ0 Handler                       |

| 0x1C04           |        | jmp                                                        | EXT_INT1        | ; | IRQ1 Handler                       |

|                  |        |                                                            |                 | ; |                                    |

| 0x1C32           |        | jmp                                                        | SPM_RDY         | ; | Store Program Memory Ready Handler |

When the BOOTRST Fuse is programmed and the Boot section size set to 2K bytes, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address Labels | Code                                                       | Com           | nen | ts                                 |

|----------------|------------------------------------------------------------|---------------|-----|------------------------------------|

| .org 0x0002    |                                                            |               |     |                                    |

| 0x0002         | jmp                                                        | EXT_INT0      | ;   | IRQ0 Handler                       |

| 0x0004         | jmp                                                        | EXT_INT1      | ;   | IRQ1 Handler                       |

|                |                                                            | •••           | ;   |                                    |

| 0x0032         | jmp                                                        | SPM_RDY       | ;   | Store Program Memory Ready Handler |

| ;              |                                                            |               |     |                                    |

| .org 0x1C00    |                                                            |               |     |                                    |

| 0x1C00 RESET:  | ldi                                                        | r16,high(RAME | ND) | ; Main program start               |

| 0x1C01         | out                                                        | SPH,r16       | ;   | Set Stack Pointer to top of RAM    |

| 0x1C02         | ldi                                                        | r16,low(RAMEN | D)  |                                    |

| 0x1C03         | out                                                        | SPL,r16       |     |                                    |

| 0x1C04         | sei                                                        |               | ;   | Enable interrupts                  |

| 0x1C05         | <instr< td=""><td>&gt; xxx</td><td></td><td></td></instr<> | > xxx         |     |                                    |

When the BOOTRST Fuse is programmed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

becomes the inverting output of the Oscillator amplifier. In this mode, a crystal Oscillator is connected to this pin, and the pin cannot be used as an I/O pin.

PCINT7: Pin Change Interrupt source 7. The PB7 pin can serve as an external interrupt source.

If PB7 is used as a clock pin, DDB7, PORTB7 and PINB7 will all read 0.

# • XTAL1/TOSC1/PCINT6 - Port B, Bit 6

XTAL1: Chip clock Oscillator pin 1. Used for all chip clock sources except internal calibrated RC Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

TOSC1: Timer Oscillator pin 1. Used only if internal calibrated RC Oscillator is selected as chip clock source, and the asynchronous timer is enabled by the correct setting in ASSR. When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PB6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

PCINT6: Pin Change Interrupt source 6. The PB6 pin can serve as an external interrupt source.

If PB6 is used as a clock pin, DDB6, PORTB6 and PINB6 will all read 0.

# • SCK/PCINT5 – Port B, Bit 5

SCK: Master Clock output, Slave Clock input pin for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB5 bit.

PCINT5: Pin Change Interrupt source 5. The PB5 pin can serve as an external interrupt source.

# • MISO/PCINT4 – Port B, Bit 4

MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input regardless of the setting of DDB4. When the SPI is enabled as a Slave, the data direction of this pin is controlled by DDB4. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB4 bit.

PCINT4: Pin Change Interrupt source 4. The PB4 pin can serve as an external interrupt source.

# MOSI/OC2/PCINT3 – Port B, Bit 3

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB3. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB3. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB3 bit.

OC2, Output Compare Match Output: The PB3 pin can serve as an external output for the Timer/Counter2 Compare Match. The PB3 pin has to be configured as an output (DDB3 set (one)) to serve this function. The OC2 pin is also the output pin for the PWM mode timer function.

PCINT3: Pin Change Interrupt source 3. The PB3 pin can serve as an external interrupt source.

# • SS/OC1B/PCINT2 – Port B, Bit 2

$\overline{SS}$ : Slave Select input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB2. As a Slave, the SPI is activated when this pin is driven low.

| Signal<br>Name | PB7/XTAL2/<br>TOSC2/PCINT7 <sup>(1)</sup>  | PB6/XTAL1/<br>TOSC1/PCINT6 <sup>(1)</sup> | PB5/SCK/<br>PCINT5        | PB4/MISO/<br>PCINT4            |

|----------------|--------------------------------------------|-------------------------------------------|---------------------------|--------------------------------|

| PUOE           | INTRC • EXTCK+<br>AS2                      | INTRC + AS2                               | SPE • MSTR                | SPE • MSTR                     |

| PUOV           | 0                                          | 0                                         | PORTB5 • PUD              | PORTB4 • PUD                   |

| DDOE           | INTRC • EXTCK+<br>AS2                      | INTRC + AS2                               | SPE • MSTR                | SPE • MSTR                     |

| DDOV           | 0                                          | 0                                         | 0                         | 0                              |

| PVOE           | 0                                          | 0                                         | SPE • MSTR                | SPE • MSTR                     |

| PVOV           | 0                                          | 0                                         | SCK OUTPUT                | SPI SLAVE<br>OUTPUT            |

| DIEOE          | INTRC • EXTCK +<br>AS2 + PCINT7 •<br>PCIE0 | INTRC + AS2 +<br>PCINT6 • PCIE0           | PCINT5 • PCIE0            | PCINT4 • PCIE0                 |

| DIEOV          | (INTRC + EXTCK) •<br>AS2                   | INTRC • AS2                               | 1                         | 1                              |

| DI             | PCINT7 INPUT                               | PCINT6 INPUT                              | PCINT5 INPUT<br>SCK INPUT | PCINT4 INPUT<br>SPI MSTR INPUT |

| AIO            | Oscillator Output                          | Oscillator/Clock<br>Input                 | -                         | -                              |

Table 10-4.

Overriding Signals for Alternate Functions in PB7..PB4

Notes: 1. INTRC means that one of the internal RC Oscillators are selected (by the CKSEL fuses), EXTCK means that external clock is selected (by the CKSEL fuses).

| Signal<br>Name | PB3/MOSI/<br>OC2/PCINT3         |                        |                | PB0/ICP1/<br>PCINT0        |

|----------------|---------------------------------|------------------------|----------------|----------------------------|

| PUOE           | SPE • MSTR                      | SPE • MSTR             | 0              | 0                          |

| PUOV           | PORTB3 • PUD                    | PORTB2 • PUD           | 0              | 0                          |

| DDOE           | SPE • MSTR                      | SPE • MSTR             | 0              | 0                          |

| DDOV           | 0                               | 0                      | 0              | 0                          |

| PVOE           | SPE • MSTR +<br>OC2A ENABLE     | OC1B ENABLE            | OC1A ENABLE    | 0                          |

| PVOV           | SPI MSTR OUTPUT<br>+ OC2A       | OC1B                   | OC1A           | 0                          |

| DIEOE          | PCINT3 • PCIE0                  | PCINT2 • PCIE0         | PCINT1 • PCIE0 | PCINT0 • PCIE0             |

| DIEOV          | 1                               | 1                      | 1              | 1                          |

| DI             | PCINT3 INPUT<br>SPI SLAVE INPUT | PCINT2 INPUT<br>SPI SS | PCINT1 INPUT   | PCINT0 INPUT<br>ICP1 INPUT |

| AIO            | _                               | -                      | -              | -                          |

**Table 10-5.** Overriding Signals for Alternate Functions in PB3..PB0

# ATmega48/88/168

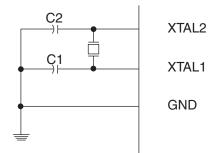

Figure 13-13. Timer/Counter Timing Diagram, with Prescaler ( ${\rm f}_{\rm clk\_I/O}/8)$

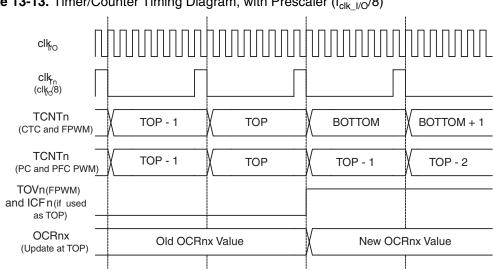

# 15.10 Timer/Counter Prescaler

Figure 15-12. Prescaler for Timer/Counter2

The clock source for Timer/Counter2 is named  $clk_{T2S}$ .  $clk_{T2S}$  is by default connected to the main system I/O clock  $clk_{IO}$ . By setting the AS2 bit in ASSR, Timer/Counter2 is asynchronously clocked from the TOSC1 pin. This enables use of Timer/Counter2 as a Real Time Counter (RTC). When AS2 is set, pins TOSC1 and TOSC2 are disconnected from Port C. A crystal can then be connected between the TOSC1 and TOSC2 pins to serve as an independent clock source for Timer/Counter2. The Oscillator is optimized for use with a 32.768 kHz crystal. Applying an external clock source to TOSC1 is not recommended.

For Timer/Counter2, the possible prescaled selections are:  $clk_{T2S}/8$ ,  $clk_{T2S}/32$ ,  $clk_{T2S}/64$ ,  $clk_{T2S}/128$ ,  $clk_{T2S}/256$ , and  $clk_{T2S}/1024$ . Additionally,  $clk_{T2S}$  as well as 0 (stop) may be selected. Setting the PSRASY bit in GTCCR resets the prescaler. This allows the user to operate with a predictable prescaler.

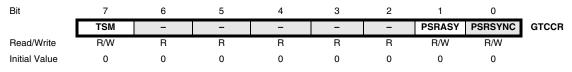

# 15.10.1 General Timer/Counter Control Register – GTCCR

## Bit 1 – PSRASY: Prescaler Reset Timer/Counter2

When this bit is one, the Timer/Counter2 prescaler will be reset. This bit is normally cleared immediately by hardware. If the bit is written when Timer/Counter2 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset. The bit will not be cleared by hardware if the TSM bit is set. Refer to the description of the "Bit 7 – TSM: Timer/Counter Synchronization Mode" on page 137 for a description of the Timer/Counter Synchronization mode.

# **17. USART0**

The Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART) is a highly flexible serial communication device. The main features are:

- Full Duplex Operation (Independent Serial Receive and Transmit Registers)

- Asynchronous or Synchronous Operation

- Master or Slave Clocked Synchronous Operation

- High Resolution Baud Rate Generator

- Supports Serial Frames with 5, 6, 7, 8, or 9 Data Bits and 1 or 2 Stop Bits

- Odd or Even Parity Generation and Parity Check Supported by Hardware

- Data OverRun Detection

- Framing Error Detection

- Noise Filtering Includes False Start Bit Detection and Digital Low Pass Filter

- Three Separate Interrupts on TX Complete, TX Data Register Empty and RX Complete

- Multi-processor Communication Mode

- Double Speed Asynchronous Communication Mode

The USART can also be used in Master SPI mode, see "USART in SPI Mode" on page 196. The Power Reduction USART bit, PRUSARTO, in "Power Reduction Register - PRR" on page 40 must be disabled by writing a logical zero to it.

# 17.1 Overview

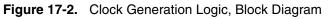

A simplified block diagram of the USART Transmitter is shown in Figure 17-1. CPU accessible I/O Registers and I/O pins are shown in bold.

The dashed boxes in the block diagram separate the three main parts of the USART (listed from the top): Clock Generator, Transmitter and Receiver. Control Registers are shared by all units. The Clock Generation logic consists of synchronization logic for external clock input used by synchronous slave operation, and the baud rate generator. The XCKn (Transfer Clock) pin is only used by synchronous transfer mode. The Transmitter consists of a single write buffer, a serial Shift Register, Parity Generator and Control logic for handling different serial frame formats. The write buffer allows a continuous transfer of data without any delay between frames. The Receiver is the most complex part of the USART module due to its clock and data recovery units. The recovery units are used for asynchronous data reception. In addition to the recovery units, the Receiver includes a Parity Checker, Control logic, a Shift Register and a two level receive buffer (UDRn). The Receiver supports the same frame formats as the Transmitter, and can detect Frame Error, Data OverRun and Parity Errors.

Signal description:

| txclk                     | Transmitter clock (Internal Signal).                                              |  |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| rxclk                     | Receiver base clock (Internal Signal).                                            |  |  |  |  |  |

| <b>xcki</b><br>operation. | Input from XCK pin (internal Signal). Used for synchronous slave                  |  |  |  |  |  |

| xcko                      | Clock output to XCK pin (Internal Signal). Used for synchronous master operation. |  |  |  |  |  |

| fosc                      | XTAL pin frequency (System Clock).                                                |  |  |  |  |  |

# 17.2.1 Internal Clock Generation – The Baud Rate Generator

Internal clock generation is used for the asynchronous and the synchronous master modes of operation. The description in this section refers to Figure 17-2.

The USART Baud Rate Register (UBRRn) and the down-counter connected to it function as a programmable prescaler or baud rate generator. The down-counter, running at system clock ( $f_{osc}$ ), is loaded with the UBRRn value each time the counter has counted down to zero or when the UBRRnL Register is written. A clock is generated each time the counter reaches zero. This clock is the baud rate generator clock output (=  $f_{osc}/(UBRRn+1)$ ). The Transmitter divides the baud rate generator clock output by 2, 8 or 16 depending on mode. The baud rate generator output is used directly by the Receiver's clock and data recovery units. However, the recovery units use a state machine that uses 2, 8 or 16 states depending on mode set by the state of the UMSELn, U2Xn and DDR\_XCKn bits.

# • Bit 5 – UDRIEn: USART Data Register Empty Interrupt Enable n

Writing this bit to one enables interrupt on the UDREn Flag. A Data Register Empty interrupt will be generated only if the UDRIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the UDREn bit in UCSRnA is set.

#### • Bit 4 – RXENn: Receiver Enable n

Writing this bit to one enables the USART Receiver. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FEn, DORn, and UPEn Flags.

# • Bit 3 – TXENn: Transmitter Enable n

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn port.

# • Bit 2 – UCSZn2: Character Size n

The UCSZn2 bits combined with the UCSZn1:0 bit in UCSRnC sets the number of data bits (Character SiZe) in a frame the Receiver and Transmitter use.

# • Bit 1 - RXB8n: Receive Data Bit 8 n

RXB8n is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDRn.

#### • Bit 0 – TXB8n: Transmit Data Bit 8 n

TXB8n is the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. Must be written before writing the low bits to UDRn.

# 17.9.4 USART Control and Status Register n C – UCSRnC

| Bit           | 7       | 6       | 5     | 4     | 3     | 2      | 1      | 0      | _      |

|---------------|---------|---------|-------|-------|-------|--------|--------|--------|--------|

|               | UMSELn1 | UMSELn0 | UPMn1 | UPMn0 | USBSn | UCSZn1 | UCSZn0 | UCPOLn | UCSRnC |

| Read/Write    | R/W     | R/W     | R/W   | R/W   | R/W   | R/W    | R/W    | R/W    | •      |

| Initial Value | 0       | 0       | 0     | 0     | 0     | 1      | 1      | 0      |        |

#### • Bits 7:6 – UMSELn1:0 USART Mode Select

These bits select the mode of operation of the USARTn as shown in Table 17-4.

#### Table 17-4. UMSELn Bits Settings

| UMSELn1 | UMSELn0 Mode |                                   |

|---------|--------------|-----------------------------------|

| 0       | 0            | Asynchronous USART                |

| 0       | 1            | Synchronous USART                 |

| 1       | 0            | (Reserved)                        |

| 1       | 1            | Master SPI (MSPIM) <sup>(1)</sup> |

Note: 1. See "USART in SPI Mode" on page 196 for full description of the Master SPI Mode (MSPIM) operation

# • Bits 5:4 – UPMn1:0: Parity Mode

These bits enable and set type of parity generation and check. If enabled, the Transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The Receiver will generate a parity value for the incoming data and compare it to the UPMn setting. If a mismatch is detected, the UPEn Flag in UCSRnA will be set.

| UPMn1 | UPMn0 | Parity Mode          |

|-------|-------|----------------------|

| 0     | 0     | Disabled             |

| 0     | 1     | Reserved             |

| 1     | 0     | Enabled, Even Parity |

| 1     | 1     | Enabled, Odd Parity  |

Table 17-5.

UPMn Bits Settings

#### • Bit 3 – USBSn: Stop Bit Select

This bit selects the number of stop bits to be inserted by the Transmitter. The Receiver ignores this setting.

| Table 17-6. | USBS Bit Settings |

|-------------|-------------------|

|-------------|-------------------|

| USBSn | Stop Bit(s) |

|-------|-------------|

| 0     | 1-bit       |

| 1     | 2-bit       |

#### • Bit 2:1 – UCSZn1:0: Character Size

The UCSZn1:0 bits combined with the UCSZn2 bit in UCSRnB sets the number of data bits (Character SiZe) in a frame the Receiver and Transmitter use.

| Table 17-7. | UCSZn Bits Settings |

|-------------|---------------------|

|-------------|---------------------|

| UCSZn2 | UCSZn1 | UCSZn0 | Character Size |

|--------|--------|--------|----------------|

| 0      | 0      | 0      | 5-bit          |

| 0      | 0      | 1      | 6-bit          |

| 0      | 1      | 0      | 7-bit          |

| 0      | 1      | 1      | 8-bit          |

| 1      | 0      | 0      | Reserved       |

| 1      | 0      | 1      | Reserved       |

| 1      | 1      | 0      | Reserved       |

| 1      | 1      | 1      | 9-bit          |

#### • Bit 0 – UCPOLn: Clock Polarity

This bit is used for synchronous mode only. Write this bit to zero when asynchronous mode is used. The UCPOLn bit sets the relationship between data output change and data input sample, and the synchronous clock (XCKn).

The upper 7 bits are the address to which the 2-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (0x00), otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | тимс | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "0" (write), the TWI will operate in SR mode, otherwise ST mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 19-5. The Slave Receiver mode may also be entered if arbitration is lost while the TWI is in the Master mode (see states 0x68 and 0x78).

If the TWEA bit is reset during a transfer, the TWI will return a "Not Acknowledge" ("1") to SDA after the next received data byte. This can be used to indicate that the Slave is not able to receive any more bytes. While TWEA is zero, the TWI does not acknowledge its own slave address. However, the 2-wire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the 2-wire Serial Bus.

In all sleep modes other than Idle mode, the clock system to the TWI is turned off. If the TWEA bit is set, the interface can still acknowledge its own slave address or the general call address by using the 2-wire Serial Bus clock as a clock source. The part will then wake up from sleep and the TWI will hold the SCL clock low during the wake up and until the TWINT Flag is cleared (by writing it to one). Further data reception will be carried out as normal, with the AVR clocks running as normal. Observe that if the AVR is set up with a long start-up time, the SCL line may be held low for a long time, blocking other data transmissions.

Note that the 2-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these Sleep modes.

20-2. If ACME is cleared or ADEN is set, AIN1 is applied to the negative input to the Analog Comparator.

| ACME | ADEN | MUX20 | Analog Comparator Negative Input |  |  |  |  |  |  |

|------|------|-------|----------------------------------|--|--|--|--|--|--|

| 0    | х    | xxx   | AIN1                             |  |  |  |  |  |  |

| 1    | 1    | xxx   | AIN1                             |  |  |  |  |  |  |

| 1    | 0    | 000   | ADC0                             |  |  |  |  |  |  |

| 1    | 0    | 001   | ADC1                             |  |  |  |  |  |  |

| 1    | 0    | 010   | ADC2                             |  |  |  |  |  |  |

| 1    | 0    | 011   | ADC3                             |  |  |  |  |  |  |

| 1    | 0    | 100   | ADC4                             |  |  |  |  |  |  |

| 1    | 0    | 101   | ADC5                             |  |  |  |  |  |  |

| 1    | 0    | 110   | ADC6                             |  |  |  |  |  |  |

| 1    | 0    | 111   | ADC7                             |  |  |  |  |  |  |

Table 20-2. Analog Comparator Multiplexed Input

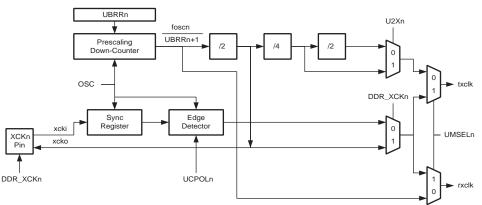

# 20.1.1 Digital Input Disable Register 1 – DIDR1

#### • Bit 7..2 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 1, 0 – AIN1D, AIN0D: AIN1, AIN0 Digital Input Disable

When this bit is written logic one, the digital input buffer on the AIN1/0 pin is disabled. The corresponding PIN Register bit will always read as zero when this bit is set. When an analog signal is applied to the AIN1/0 pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer.

# • Bit 0 – SELFPRGEN: Self Programming Enable

This bit enables the SPM instruction for the next four clock cycles. If written to one together with either RWWSRE, BLBSET, PGWRT, or PGERS, the following SPM instruction will have a special meaning, see description above. If only SELFPRGEN is written, the following SPM instruction will store the value in R1:R0 in the temporary page buffer addressed by the Z-pointer. The LSB of the Z-pointer is ignored. The SELFPRGEN bit will auto-clear upon completion of an SPM instruction, or if no SPM instruction is executed within four clock cycles. During Page Erase and Page Write, the SELFPRGEN bit remains high until the operation is completed.

Writing any other combination than "10001", "01001", "00101", "00011" or "00001" in the lower five bits will have no effect.

#### 23.1.2 EEPROM Write Prevents Writing to SPMCSR

Note that an EEPROM write operation will block all software programming to Flash. Reading the Fuses and Lock bits from software will also be prevented during the EEPROM write operation. It is recommended that the user checks the status bit (EEPE) in the EECR Register and verifies that the bit is cleared before writing to the SPMCSR Register.

#### 23.1.3 Reading the Fuse and Lock Bits from Software

It is possible to read both the Fuse and Lock bits from software. To read the Lock bits, load the Z-pointer with 0x0001 and set the BLBSET and SELFPRGEN bits in SPMCSR. When an LPM instruction is executed within three CPU cycles after the BLBSET and SELFPRGEN bits are set in SPMCSR, the value of the Lock bits will be loaded in the destination register. The BLBSET and SELFPRGEN bits will auto-clear upon completion of reading the Lock bits or if no LPM instruction is executed within three CPU cycles or no SPM instruction is executed within four CPU cycles. When BLBSET and SELFPRGEN are cleared, LPM will work as described in the Instruction set Manual.

The algorithm for reading the Fuse Low byte is similar to the one described above for reading the Lock bits. To read the Fuse Low byte, load the Z-pointer with 0x0000 and set the BLBSET and SELFPRGEN bits in SPMCSR. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Fuse Low byte (FLB) will be loaded in the destination register as shown below.See Table 25-5 on page 282 for a detailed description and mapping of the Fuse Low byte.

| Bit | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----|------|------|------|------|------|------|------|------|

| Rd  | FLB7 | FLB6 | FLB5 | FLB4 | FLB3 | FLB2 | FLB1 | FLB0 |

Similarly, when reading the Fuse High byte (FHB), load 0x0003 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Fuse High byte will be loaded in the destination register as shown below. See Table 25-4 on page 281 for detailed description and mapping of the Extended Fuse byte.

| Bit | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----|------|------|------|------|------|------|------|------|

| Rd  | FHB7 | FHB6 | FHB5 | FHB4 | FHB3 | FHB2 | FHB1 | FHB0 |

Similarly, when reading the Extended Fuse byte (EFB), load 0x0002 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Extended Fuse byte will be loaded in the destination register as

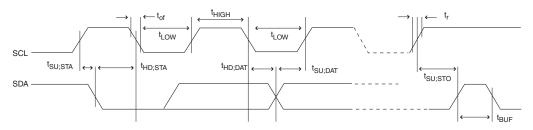

# Figure 26-4. 2-wire Serial Bus Timing

# 26.7 SPI Timing Characteristics

See Figure 26-5 and Figure 26-6 for details.

**Table 26-3.**SPI Timing Parameters

|    | Description                 | Mode   | Min                 | Тур                    | Max  |    |

|----|-----------------------------|--------|---------------------|------------------------|------|----|

| 1  | SCK period                  | Master |                     | See Table 16-4         |      |    |

| 2  | SCK high/low                | Master |                     | 50% duty cycle         |      |    |

| 3  | Rise/Fall time              | Master |                     | 3.6                    |      |    |

| 4  | Setup                       | Master |                     | 10                     |      |    |

| 5  | Hold                        | Master |                     | 10                     |      |    |

| 6  | Out to SCK                  | Master |                     | 0.5 ∙ t <sub>sck</sub> |      |    |

| 7  | SCK to out                  | Master |                     | 10                     |      |    |

| 8  | SCK to out high             | Master |                     | 10                     |      |    |

| 9  | SS low to out               | Slave  |                     | 15                     |      |    |

| 10 | SCK period                  | Slave  | 4 ∙ t <sub>ck</sub> |                        |      | ns |

| 11 | SCK high/low <sup>(1)</sup> | Slave  | 2 ∙ t <sub>ck</sub> |                        |      |    |

| 12 | Rise/Fall time              | Slave  |                     |                        | 1600 |    |

| 13 | Setup                       | Slave  | 10                  |                        |      |    |

| 14 | Hold                        | Slave  | t <sub>ck</sub>     |                        |      |    |

| 15 | SCK to out                  | Slave  |                     | 15                     |      |    |

| 16 | SCK to SS high              | Slave  | 20                  |                        |      |    |

| 17 | SS high to tri-state        | Slave  |                     | 10                     |      |    |

| 18 | SS low to SCK               | Slave  | 20                  |                        |      |    |

Note: 1. In SPI Programming mode the minimum SCK high/low period is:

- 2  $t_{CLCL}$  for  $f_{CK}$  < 12 MHz

- 3  $t_{CLCL}$  for  $f_{CK}$  > 12 MHz

- 2. All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon.

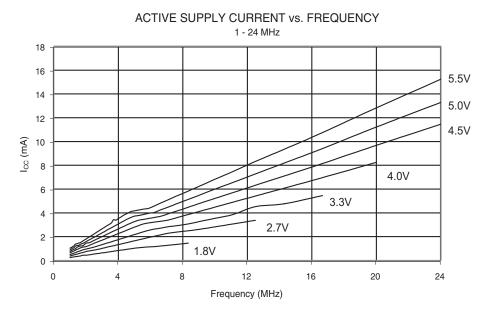

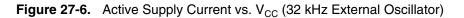

Figure 27-3. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 128 kHz)

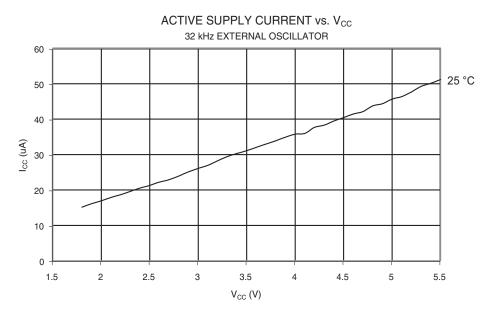

# 27.2 Idle Supply Current

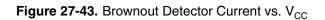

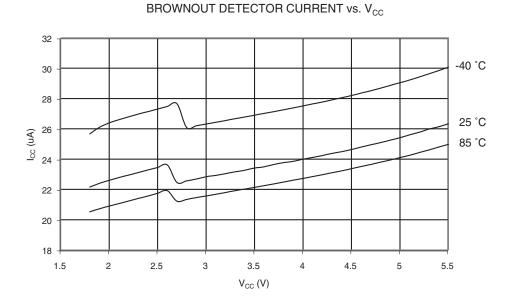

# 27.12 Current Consumption of Peripheral Units

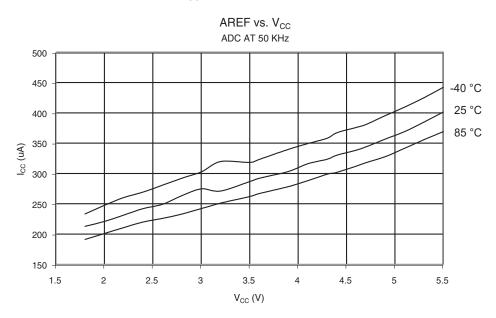

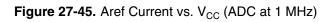

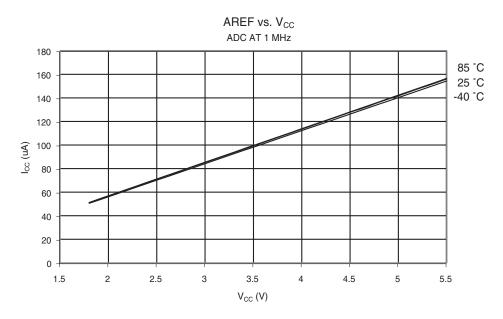

Figure 27-44. ADC Current vs. V<sub>CC</sub> (ADC at 50 kHz)

# ATmega48/88/168

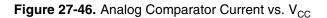

ANALOG COMPARATOR CURRENT vs.  $V_{\text{CC}}$

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

# **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

# Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

*Memory* 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

# Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

# Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2005. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, AVR<sup>®</sup>, and AVR Studio<sup>®</sup> are registered trademarks, and Everywhere You Are<sup>SM</sup> are the trademarks of Atmel Corporation or its subsidiaries. Microsoft<sup>®</sup>, Windows<sup>®</sup>, Windows NT<sup>®</sup>, and Windows XP<sup>®</sup> are the registered trademarks of Microsoft Corporation. Other terms and product names may be trademarks of others.