Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-TQFP                                                                   |

| Supplier Device Package    | 32-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168v-10au |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. AVR CPU Core

## 4.1 Introduction

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

## 4.2 Architectural Overview

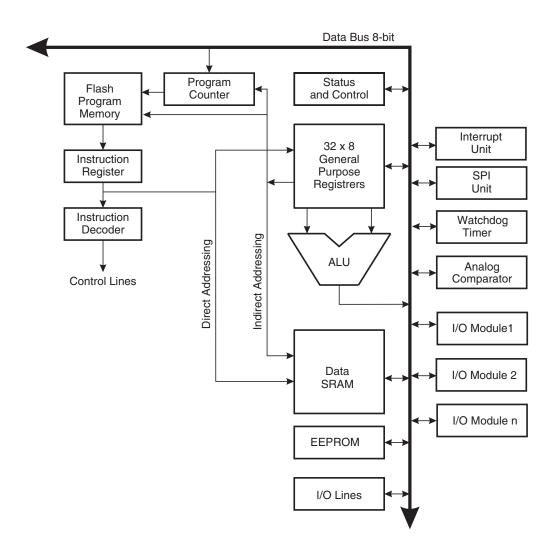

Figure 4-1. Block Diagram of the AVR Architecture

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

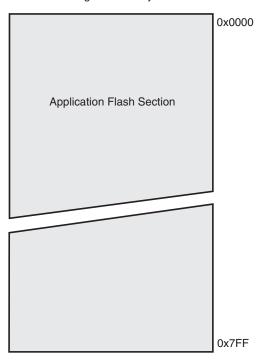

#### Figure 5-1. Program Memory Map, ATmega48

Program Memory

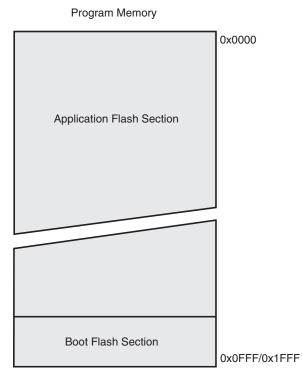

## Figure 5-2. Program Memory Map, ATmega88 and ATmega168

## 5.4 I/O Memory

The I/O space definition of the ATmega48/88/168 is shown in "Register Summary" on page 334.

All ATmega48/88/168 I/Os and peripherals are placed in the I/O space. All I/O locations may be accessed by the LD/LDS/LDD and ST/STS/STD instructions, transferring data between the 32 general purpose working registers and the I/O space. I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set section for more details. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega48/88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

The I/O and peripherals control registers are explained in later sections.

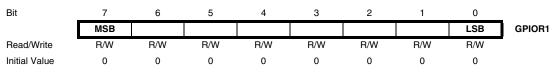

#### 5.4.1 General Purpose I/O Registers

The ATmega48/88/168 contains three General Purpose I/O Registers. These registers can be used for storing any information, and they are particularly useful for storing global variables and Status Flags. General Purpose I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI, CBI, SBIS, and SBIC instructions.

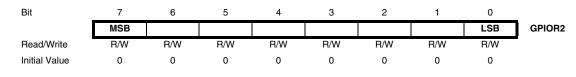

#### 5.4.2 General Purpose I/O Register 2 – GPIOR2

#### 5.4.3 General Purpose I/O Register 1 – GPIOR1

#### 5.4.4 General Purpose I/O Register 0 – GPIOR0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

|               | MSB |     |     |     |     |     |     | LSB | GPIOR0 |

| Read/Write    | R/W |        |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

When this Oscillator is selected, start-up times are determined by the SUT Fuses as shown in Table 6-9 on page 32.

| Power Conditions    | Start-up Time from Power-<br>down and Power-save | Additional Delay from<br>Reset (V <sub>CC</sub> = 5.0V) | SUT10 |

|---------------------|--------------------------------------------------|---------------------------------------------------------|-------|

| BOD enabled         | 6 CK                                             | 14CK <sup>(1)</sup>                                     | 00    |

| Fast rising power   | 6 CK                                             | 14CK + 4.1 ms                                           | 01    |

| Slowly rising power | 6 CK                                             | 14CK + 65 ms <sup>(2)</sup>                             | 10    |

|                     | Reserved                                         |                                                         | 11    |

**Table 6-9.** Start-up times for the internal calibrated RC Oscillator clock selection

Note: 1. If the RSTDISBL fuse is programmed, this start-up time will be increased to 14CK + 4.1 ms to ensure programming mode can be entered.

2. The device is shipped with this option selected.

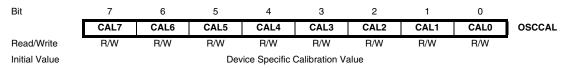

#### 6.6.1 Oscillator Calibration Register – OSCCAL

#### • Bits 7..0 – CAL7..0: Oscillator Calibration Value

The Oscillator Calibration Register is used to trim the Calibrated Internal RC Oscillator to remove process variations from the oscillator frequency. The factory-calibrated value is automatically written to this register during chip reset, giving an oscillator frequency of 8.0 MHz at 25°C. The application software can write this register to change the oscillator frequency. The oscillator can be calibrated to any frequency in the range 7.3 - 8.1 MHz within  $\pm$ 1% accuracy. Calibration outside that range is not guaranteed.

Note that this oscillator is used to time EEPROM and Flash write accesses, and these write times will be affected accordingly. If the EEPROM or Flash are written, do not calibrate to more than 8.8 MHz. Otherwise, the EEPROM or Flash write may fail.

The CAL7 bit determines the range of operation for the oscillator. Setting this bit to 0 gives the lowest frequency range, setting this bit to 1 gives the highest frequency range. The two frequency ranges are overlapping, in other words a setting of OSCCAL = 0x7F gives a higher frequency than OSCCAL = 0x80.

The CAL6..0 bits are used to tune the frequency within the selected range. A setting of 0x00 gives the lowest frequency in that range, and a setting of 0x7F gives the highest frequency in the range. Incrementing CAL6..0 by 1 will give a frequency increment of less than 2% in the frequency range 7.3 - 8.1 MHz.

# 8. System Control and Reset

#### 8.0.1 Resetting the AVR

During reset, all I/O Registers are set to their initial values, and the program starts execution from the Reset Vector. For the ATmega168, the instruction placed at the Reset Vector must be a JMP – Absolute Jump – instruction to the reset handling routine. For the ATmega48 and ATmega88, the instruction placed at the Reset Vector must be an RJMP – Relative Jump – instruction to the reset handling routine. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa (ATmega88/168 only). The circuit diagram in Figure 8-1 shows the reset logic. Table 8-1 defines the electrical parameters of the reset circuitry.

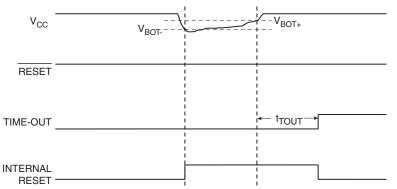

The I/O ports of the AVR are immediately reset to their initial state when a reset source goes active. This does not require any clock source to be running.

After all reset sources have gone inactive, a delay counter is invoked, stretching the internal reset. This allows the power to reach a stable level before normal operation starts. The time-out period of the delay counter is defined by the user through the SUT and CKSEL Fuses. The different selections for the delay period are presented in "Clock Sources" on page 26.

#### 8.0.2 Reset Sources

The ATmega48/88/168 has four sources of reset:

- Power-on Reset. The MCU is reset when the supply voltage is below the Power-on Reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for longer than the minimum pulse length.

- Watchdog System Reset. The MCU is reset when the Watchdog Timer period expires and the Watchdog System Reset mode is enabled.

- Brown-out Reset. The MCU is reset when the supply voltage  $V_{CC}$  is below the Brown-out Reset threshold ( $V_{BOT}$ ) and the Brown-out Detector is enabled.

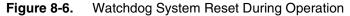

#### 8.0.6 Watchdog System Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period  $t_{TOUT}$ . Refer to page 49 for details on operation of the Watchdog Timer.

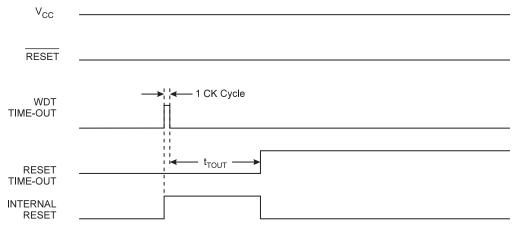

#### 8.0.7 MCU Status Register – MCUSR

The MCU Status Register provides information on which reset source caused an MCU reset.

#### • Bit 7..4: Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### Bit 3 – WDRF: Watchdog System Reset Flag

This bit is set if a Watchdog System Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

#### Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

# ATmega48/88/168

| 0xC1B          | out                                                                                                               | SPH,r16        | ; | Set : | Stack  | Pointer  | to | top | of | RAM |

|----------------|-------------------------------------------------------------------------------------------------------------------|----------------|---|-------|--------|----------|----|-----|----|-----|

| 0xC1C          | ldi                                                                                                               | r16,low(RAMEND | ) |       |        |          |    |     |    |     |

| 0xC1D<br>0xC1E | out<br>sei                                                                                                        | SPL,r16        | ; | Enab  | le int | terrupts |    |     |    |     |

| 0xC1F          | <inst:< td=""><td>r&gt; xxx</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></inst:<> | r> xxx         |   |       |        |          |    |     |    |     |

## 9.3 Interrupt Vectors in ATmega168

#### Table 9-4. Reset and Interrupt Vectors in ATmega168

| VectorNo. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                    |

|-----------|-----------------------------------|--------------|-------------------------------------------------------------------------|

| 1         | 0x0000 <sup>(1)</sup>             | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2         | 0x0002                            | INTO         | External Interrupt Request 0                                            |

| 3         | 0x0004                            | INT1         | External Interrupt Request 1                                            |

| 4         | 0x0006                            | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5         | 0x0008                            | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6         | 0x000A                            | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7         | 0x000C                            | WDT          | Watchdog Time-out Interrupt                                             |

| 8         | 0x000E                            | TIMER2 COMPA | Timer/Counter2 Compare Match A                                          |

| 9         | 0x0010                            | TIMER2 COMPB | Timer/Counter2 Compare Match B                                          |

| 10        | 0x0012                            | TIMER2 OVF   | Timer/Counter2 Overflow                                                 |

| 11        | 0x0014                            | TIMER1 CAPT  | Timer/Counter1 Capture Event                                            |

| 12        | 0x0016                            | TIMER1 COMPA | Timer/Counter1 Compare Match A                                          |

| 13        | 0x0018                            | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                          |

| 14        | 0x001A                            | TIMER1 OVF   | Timer/Counter1 Overflow                                                 |

| 15        | 0x001C                            | TIMER0 COMPA | Timer/Counter0 Compare Match A                                          |

| 16        | 0x001E                            | TIMER0 COMPB | Timer/Counter0 Compare Match B                                          |

| 17        | 0x0020                            | TIMER0 OVF   | Timer/Counter0 Overflow                                                 |

| 18        | 0x0022                            | SPI, STC     | SPI Serial Transfer Complete                                            |

| 19        | 0x0024                            | USART, RX    | USART Rx Complete                                                       |

| 20        | 0x0026                            | USART, UDRE  | USART, Data Register Empty                                              |

| 21        | 0x0028                            | USART, TX    | USART, Tx Complete                                                      |

| 22        | 0x002A                            | ADC          | ADC Conversion Complete                                                 |

| 23        | 0x002C                            | EE READY     | EEPROM Ready                                                            |

| 24        | 0x002E                            | ANALOG COMP  | Analog Comparator                                                       |

| 25        | 0x0030                            | TWI          | 2-wire Serial Interface                                                 |

| 26        | 0x0032                            | SPM READY    | Store Program Memory Ready                                              |

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at reset, see "Boot Loader Support – Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264.

Table 10-7 and Table 10-8 relate the alternate functions of Port C to the overriding signals shown in Figure 10-5 on page 69.

| Signal<br>Name | PC6/RESET/PCINT14             | PC5/SCL/ADC5/PCINT13    | PC4/SDA/ADC4/PCINT12    |

|----------------|-------------------------------|-------------------------|-------------------------|

| PUOE           | RSTDISBL                      | TWEN                    | TWEN                    |

| PUOV           | 1                             | PORTC5 • PUD            | PORTC4 • PUD            |

| DDOE           | RSTDISBL                      | TWEN                    | TWEN                    |

| DDOV           | 0                             | SCL_OUT                 | SDA_OUT                 |

| PVOE           | 0                             | TWEN                    | TWEN                    |

| PVOV           | 0                             | 0                       | 0                       |

| DIEOE          | RSTDISBL + PCINT14 •<br>PCIE1 | PCINT13 • PCIE1 + ADC5D | PCINT12 • PCIE1 + ADC4D |

| DIEOV          | RSTDISBL                      | PCINT13 • PCIE1         | PCINT12 • PCIE1         |

| DI             | PCINT14 INPUT                 | PCINT13 INPUT           | PCINT12 INPUT           |

| AIO            | RESET INPUT                   | ADC5 INPUT / SCL INPUT  | ADC4 INPUT / SDA INPUT  |

Table 10-7.

Overriding Signals for Alternate Functions in PC6..PC4<sup>(1)</sup>

Note: 1. When enabled, the 2-wire Serial Interface enables slew-rate controls on the output pins PC4 and PC5. This is not shown in the figure. In addition, spike filters are connected between the AIO outputs shown in the port figure and the digital logic of the TWI module.

| Signal<br>Name | PC3/ADC3/<br>PCINT11       | PC2/ADC2/<br>PCINT10       | PC1/ADC1/<br>PCINT9       | PC0/ADC0/<br>PCINT8       |

|----------------|----------------------------|----------------------------|---------------------------|---------------------------|

| PUOE           | 0                          | 0                          | 0                         | 0                         |

| PUOV           | 0                          | 0                          | 0                         | 0                         |

| DDOE           | 0                          | 0                          | 0                         | 0                         |

| DDOV           | 0                          | 0                          | 0                         | 0                         |

| PVOE           | 0                          | 0                          | 0                         | 0                         |

| PVOV           | 0                          | 0                          | 0                         | 0                         |

| DIEOE          | PCINT11 • PCIE1 +<br>ADC3D | PCINT10 • PCIE1 +<br>ADC2D | PCINT9 • PCIE1 +<br>ADC1D | PCINT8 • PCIE1 +<br>ADC0D |

| DIEOV          | PCINT11 • PCIE1            | PCINT10 • PCIE1            | PCINT9 • PCIE1            | PCINT8 • PCIE1            |

| DI             | PCINT11 INPUT              | PCINT10 INPUT              | PCINT9 INPUT              | PCINT8 INPUT              |

| AIO            | ADC3 INPUT                 | ADC2 INPUT                 | ADC1 INPUT                | ADC0 INPUT                |

# ATmega48/88/168

#### 11.1.2 External Interrupt Mask Register – EIMSK

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    | _     |

|---------------|---|---|---|---|---|---|------|------|-------|

|               | - | - | - | - | - | - | INT1 | INT0 | EIMSK |

| Read/Write    | R | R | R | R | R | R | R/W  | R/W  | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |       |

#### • Bit 7..2 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 1 – INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the External Interrupt Control Register A (EICRA) define whether the external interrupt is activated on rising and/or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from the INT1 Interrupt Vector.

#### • Bit 0 – INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the External Interrupt Control Register A (EICRA) define whether the external interrupt is activated on rising and/or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from the INT0 Interrupt Vector.

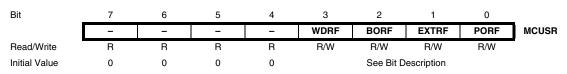

#### 11.1.3 External Interrupt Flag Register – EIFR

#### • Bit 7..2 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 1 – INTF1: External Interrupt Flag 1

When an edge or logic change on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in EIMSK are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT1 is configured as a level interrupt.

#### • Bit 0 – INTF0: External Interrupt Flag 0

When an edge or logic change on the INT0 pin triggers an interrupt request, INTF0 becomes set (one). If the I-bit in SREG and the INT0 bit in EIMSK are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT0 is configured as a level interrupt.

Table 12-7 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

| COM0B1 | COM0B0 | Description                                                                                 |

|--------|--------|---------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected.                                                   |

| 0      | 1      | Reserved                                                                                    |

| 1      | 0      | Clear OC0B on Compare Match when up-counting. Set OC0B on Compare Match when down-counting. |

| 1      | 1      | Set OC0B on Compare Match when up-counting. Clear OC0B on Compare Match when down-counting. |

Table 12-7.

Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 96 for more details.

#### • Bits 3, 2 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### • Bits 1:0 - WGM01:0: Waveform Generation Mode

Combined with the WGM02 bit found in the TCCR0B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of waveform generation to be used, see Table 12-8. Modes of operation supported by the Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare Match (CTC) mode, and two types of Pulse Width Modulation (PWM) modes (see "Modes of Operation" on page 93).

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of<br>OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|------|-------|-------|-------|---------------------------------------|------|----------------------|--------------------------------------|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate            | MAX                                  |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP                  | BOTTOM                               |

| 2    | 0     | 1     | 0     | СТС                                   | OCRA | Immediate            | MAX                                  |

| 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | TOP                  | MAX                                  |

| 4    | 1     | 0     | 0     | Reserved                              | _    | _                    | _                                    |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP                  | BOTTOM                               |

| 6    | 1     | 1     | 0     | Reserved –                            |      | _                    | _                                    |

| 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | TOP                  | TOP                                  |

Table 12-8.

Waveform Generation Mode Bit Description

Notes: 1. MAX = 0xFF 2. BOTTOM = 0x00

| CS02 | CS01 | CS00 | 00 Description                                          |  |  |  |  |

|------|------|------|---------------------------------------------------------|--|--|--|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped)                 |  |  |  |  |

| 0    | 0    | 1    | clk <sub>I/O</sub> /(No prescaling)                     |  |  |  |  |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |  |  |  |  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |  |  |  |  |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |  |  |  |  |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |  |  |  |  |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |  |  |  |  |

| 1    | 1    | 1    | External clock source on T0 pin. Clock on rising edge.  |  |  |  |  |

Table 12-9. Clock Select Bit Description

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

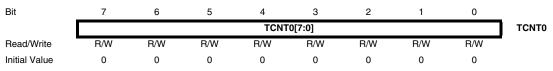

#### 12.8.3 Timer/Counter Register – TCNT0

The Timer/Counter Register gives direct access, both for read and write operations, to the Timer/Counter unit 8-bit counter. Writing to the TCNT0 Register blocks (removes) the Compare Match on the following timer clock. Modifying the counter (TCNT0) while the counter is running, introduces a risk of missing a Compare Match between TCNT0 and the OCR0x Registers.

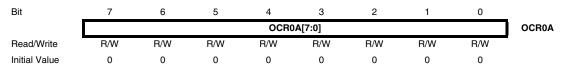

#### 12.8.4 Output Compare Register A – OCR0A

The Output Compare Register A contains an 8-bit value that is continuously compared with the counter value (TCNT0). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC0A pin.

#### 12.8.5 Output Compare Register B – OCR0B

| Bit           | 7          | 6   | 5   | 4   | 3   | 2   | 1     | 0   | _ |

|---------------|------------|-----|-----|-----|-----|-----|-------|-----|---|

|               | OCR0B[7:0] |     |     |     |     |     | OCR0B |     |   |

| Read/Write    | R/W        | R/W | R/W | R/W | R/W | R/W | R/W   | R/W | - |

| Initial Value | 0          | 0   | 0   | 0   | 0   | 0   | 0     | 0   |   |

The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNT0). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC0B pin.

# ATmega48/88/168

output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7 (See Table 15-4 on page 150). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by clearing (or setting) the OC2x Register at the compare match between OCR2x and TCNT2 when the counter increments, and setting (or clearing) the OC2x Register at compare match between OCR2x and TCNT2 when the counter increments, and setting (or clearing) the OC2x Register at compare match between OCR2x and TCNT2 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{OCnxPCPWM} = \frac{f_{\text{clk}\_I/O}}{N \cdot 510}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR2A is set equal to BOTTOM, the output will be continuously low and if set equal to MAX the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values.

At the very start of period 2 in Figure 15-7 OCnx has a transition from high to low even though there is no Compare Match. The point of this transition is to guarantee symmetry around BOT-TOM. There are two cases that give a transition without Compare Match.

- OCR2A changes its value from MAX, like in Figure 15-7. When the OCR2A value is MAX the OCn pin value is the same as the result of a down-counting compare match. To ensure symmetry around BOTTOM the OCn value at MAX must correspond to the result of an up-counting Compare Match.

- The timer starts counting from a value higher than the one in OCR2A, and for that reason misses the Compare Match and hence the OCn change that would have happened on the way up.

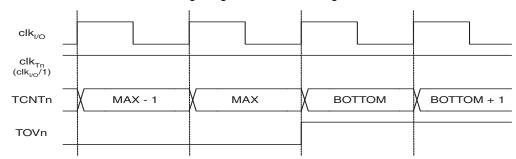

### 15.7 Timer/Counter Timing Diagrams

The following figures show the Timer/Counter in synchronous mode, and the timer clock ( $clk_{T2}$ ) is therefore shown as a clock enable signal. In asynchronous mode,  $clk_{I/O}$  should be replaced by the Timer/Counter Oscillator clock. The figures include information on when Interrupt Flags are set. Figure 15-8 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other than phase correct PWM mode.

Figure 15-8. Timer/Counter Timing Diagram, no Prescaling

Figure 15-9 shows the same timing data, but with the prescaler enabled.

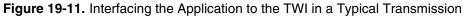

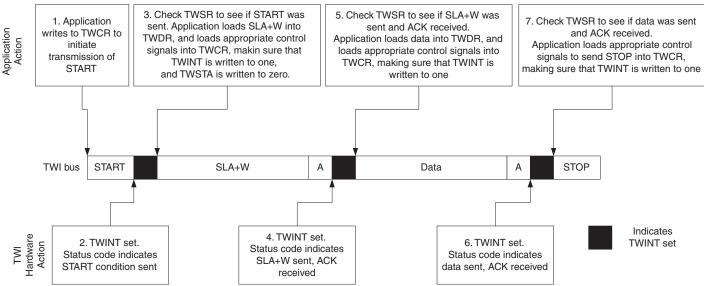

- 1. The first step in a TWI transmission is to transmit a START condition. This is done by writing a specific value into TWCR, instructing the TWI hardware to transmit a START condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the START condition.

- 2. When the START condition has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the START condition has successfully been sent.

- 3. The application software should now examine the value of TWSR, to make sure that the START condition was successfully transmitted. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load SLA+W into TWDR. Remember that TWDR is used both for address and data. After TWDR has been loaded with the desired SLA+W, a specific value must be written to TWCR, instructing the TWI hardware to transmit the SLA+W present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the address packet.

- 4. When the address packet has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the address packet has successfully been sent. The status code will also reflect whether a Slave acknowledged the packet or not.

- 5. The application software should now examine the value of TWSR, to make sure that the address packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load a data packet into TWDR. Subsequently, a specific value must be written to TWCR, instructing the TWI hardware to transmit the data packet present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will

shown below. See Table 25-5 on page 282 for detailed description and mapping of the Extended Fuse byte.

Bit 7 6 5 3 2 0 4 1 Rd FHB7 FHB6 FHB5 FHB4 FHB3 FHB2 FHB1 FHB0

Fuse and Lock bits that are programmed, will be read as zero. Fuse and Lock bits that are unprogrammed, will be read as one.

#### 23.1.4 Preventing Flash Corruption

During periods of low  $V_{CC}$ , the Flash program can be corrupted because the supply voltage is too low for the CPU and the Flash to operate properly. These issues are the same as for board level systems using the Flash, and the same design solutions should be applied.

A Flash program corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the Flash requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage for executing instructions is too low.

Flash corruption can easily be avoided by following these design recommendations (one is sufficient):

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the SPMCSR Register and thus the Flash from unintentional writes.

#### 23.1.5 Programming Time for Flash when Using SPM

The calibrated RC Oscillator is used to time Flash accesses. Table 24-5 shows the typical programming time for Flash accesses from the CPU.

#### Table 23-1. SPM Programming Time

| Symbol                                                           | Min Programming Time | Max Programming Time |

|------------------------------------------------------------------|----------------------|----------------------|

| Flash write (Page Erase, Page Write, and write Lock bits by SPM) | 3.7 ms               | 4.5 ms               |

#### 23.1.6 Simple Assembly Code Example for a Boot Loader

Note that the RWWSB bit will always be read as zero in ATmega48. Nevertheless, it is recommended to check this bit as shown in the code example, to ensure compatibility with devices supporting Read-While-Write.

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data low byte (0x00 0xFF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- 2. Give PAGEL a positive pulse. This latches the data bytes. (See Figure 25-3 for signal waveforms)

F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 25-2 on page 289. Note that if less than eight bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address low byte are used to address the page when performing a Page Write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- H. Program Page

- 1. Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- 2. Wait until RDY/BSY goes high (See Figure 25-3 for signal waveforms).

I. Repeat B through H until the entire Flash is programmed or until all data has been programmed.

J. End Page Programming

- 1. 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set DATA to "0000 0000". This is the command for No Operation.

- 3. Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

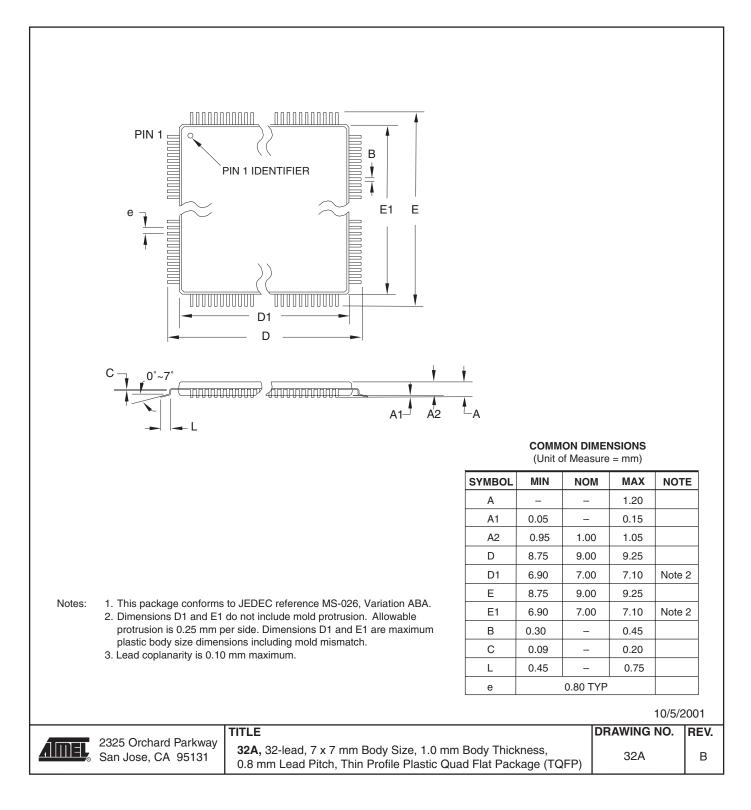

# 31. Packaging Information

## 31.1 32A

# 32. Errata

## 32.1 Errata ATmega48

The revision letter in this section refers to the revision of the ATmega48 device.

#### 32.1.1 Rev A

- Wrong values read after Erase Only operation

- Watchdog Timer Interrupt disabled

- Start-up time with Crystal Oscillator is higher than expected

- High Power Consumption in Power-down with External Clock

- Asynchronous Oscillator does not stop in Power-down

#### 1. Wrong values read after Erase Only operation

At supply voltages below 2.7 V, an EEPROM location that is erased by the Erase Only operation may read as programmed (0x00).

#### **Problem Fix/Workaround**

If it is necessary to read an EEPROM location after Erase Only, use an Atomic Write operation with 0xFF as data in order to erase a location. In any case, the Write Only operation can be used as intended. Thus no special considerations are needed as long as the erased location is not read before it is programmed.

#### 2. Watchdog Timer Interrupt disabled

If the watchdog timer interrupt flag is not cleared before a new timeout occurs, the watchdog will be disabled, and the interrupt flag will automatically be cleared. This is only applicable in interrupt only mode. If the Watchdog is configured to reset the device in the watchdog time-out following an interrupt, the device works correctly.

#### Problem fix / Workaround

Make sure there is enough time to always service the first timeout event before a new watchdog timeout occurs. This is done by selecting a long enough time-out period.

#### 3. Start-up time with Crystal Oscillator is higher than expected

The clock counting part of the start-up time is about 2 times higher than expected for all start-up periods when running on an external Crystal. This applies only when waking up by reset. Wake-up from power down is not affected. For most settings, the clock counting parts is a small fraction of the overall start-up time, and thus, the problem can be ignored. The exception is when using a very low frequency crystal like for instance a 32 kHz clock crystal.

#### Problem fix / Workaround

No known workaround.

#### 4. High Power Consumption in Power-down with External Clock

The power consumption in power down with an active external clock is about 10 times higher than when using internal RC or external oscillators.

#### Problem fix / Workaround

Stop the external clock when the device is in power down.

#### 5. Asynchronous Oscillator does not stop in Power-down

# 33. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

### 33.1 Rev. 2545E-02/05

- 1. MLF-package alternative changed to "Quad Flat No-Lead/Micro Lead Frame Package QFN/MLF".

- 2. Updated "The EEPROM Control Register EECR" on page 19.

- 3. Updated "Calibrated Internal RC Oscillator" on page 31.

- 4. Updated "External Clock" on page 33.

- 5. Updated Table 8-1 on page 44, Table 26-3 on page 304, Table 26-1 on page 301and Table 25-16 on page 297

- 6. Added "Pin Change Interrupt Timing" on page 83

- 7. Updated "8-bit Timer/Counter Block Diagram" on page 88.

- 8. Updated "Store Program Memory Control and Status Register SPMCSR" on page 259.

- 9. Updated "Enter Programming Mode" on page 286.

- 10. Updated "DC Characteristics" on page 299.

- 11. Updated "Ordering Information" on page 341.

- 12. Updated "Errata ATmega88" on page 348 and "Errata ATmega168" on page 349.

### 33.2 Rev. 2545D-07/04

- 1. Updated instructions used with WDTCSR in relevant code examples.

- 2. Updated Table 6-5 on page 29, Table 8-2 on page 46, Table 24-9 on page 278, and Table 24-11 on page 279.

- 3. Updated "System Clock Prescaler" on page 34.

- Moved "Timer/Counter2 Interrupt Mask Register TIMSK2" and "Timer/Counter2 Interrupt Flag Register – TIFR2" to "8-bit Timer/Counter Register Description" on page 149.

- 5. Updated cross-reference in "Electrical Interconnection" on page 206.

- 6. Updated equation in "Bit Rate Generator Unit" on page 211.

- 7. Added "Page Size" on page 284.

- 8. Updated "Serial Programming Algorithm" on page 296.

- 9. Updated Ordering Information for "ATmega168" on page 343.

- 10. Updated "Errata ATmega88" on page 348 and "Errata ATmega168" on page 349.

- 11. Updated equation in "Bit Rate Generator Unit" on page 211.

#### 33.3 Rev. 2545C-04/04

- 1. Speed Grades changed: 12MHz to 10MHz and 24MHz to 20MHz

- 2. Updated "Maximum Speed vs. VCC" on page 301.

- 3. Updated "Ordering Information" on page 341.

- 4. Updated "Errata ATmega88" on page 348.

# 350 ATmega48/88/168

# **Table of Contents**

|   | Features                                                | 1  |

|---|---------------------------------------------------------|----|

| 1 | Pin Configurations                                      | 2  |

|   | 1.1Disclaimer                                           | 3  |

| 2 | Overview                                                | 3  |

|   | 2.1Block Diagram                                        | 3  |

|   | 2.2Comparison Between ATmega48, ATmega88, and ATmega168 | 4  |

|   | 2.3Pin Descriptions                                     | 5  |

| 3 | About Code Examples                                     | 6  |

| 4 | AVR CPU Core                                            | 7  |

|   | 4.1 Introduction                                        | 7  |

|   | 4.2Architectural Overview                               | 7  |

|   | 4.3ALU – Arithmetic Logic Unit                          | 8  |

|   | 4.4Status Register                                      | 9  |

|   | 4.5General Purpose Register File                        | 10 |

|   | 4.6Stack Pointer                                        | 11 |

|   | 4.7Instruction Execution Timing                         | 12 |

|   | 4.8Reset and Interrupt Handling                         | 12 |

| 5 | AVR ATmega48/88/168 Memories                            | 15 |

|   | 5.1In-System Reprogrammable Flash Program Memory        | 15 |

|   | 5.2SRAM Data Memory                                     | 17 |

|   | 5.3EEPROM Data Memory                                   | 18 |

|   | 5.4I/O Memory                                           | 24 |

| 6 | System Clock and Clock Options                          | 25 |

|   | 6.1Clock Systems and their Distribution                 | 25 |

|   | 6.2Clock Sources                                        | 26 |

|   | 6.3Low Power Crystal Oscillator                         | 27 |

|   | 6.4Full Swing Crystal Oscillator                        | 29 |

|   | 6.5Low Frequency Crystal Oscillator                     | 31 |

|   | 6.6Calibrated Internal RC Oscillator                    | 31 |

|   | 6.7128 kHz Internal Oscillator                          | 33 |

|   | 6.8External Clock                                       | 33 |

|   | 6.9Clock Output Buffer                                  | 34 |

|    | 27.4Power-Down Supply Current                           |     |

|----|---------------------------------------------------------|-----|

|    | 27.5Power-Save Supply Current                           |     |

|    | 27.6Standby Supply Current                              |     |

|    | 27.7Pin Pull-up                                         |     |

|    | 27.8Pin Driver Strength                                 |     |

|    | 27.9Pin Thresholds and Hysteresis                       |     |

|    | 27.10BOD Thresholds and Analog Comparator Offset        |     |

|    | 27.11Internal Oscillator Speed                          |     |

|    | 27.12Current Consumption of Peripheral Units            |     |

|    | 27.13Current Consumption in Reset and Reset Pulse width |     |

| 28 | Register Summary                                        |     |

| 29 | Instruction Set Summary                                 |     |

| 30 | Ordering Information                                    |     |

|    | 30.1ATmega48                                            |     |

|    | 30.2ATmega88                                            |     |

|    | 30.3ATmega168                                           |     |

| 31 | Packaging Information                                   |     |

|    | 31.132A                                                 |     |

|    | 31.228P3                                                |     |

|    | 31.332M1-A                                              |     |

| 32 | Errata                                                  |     |

|    | 32.1Errata ATmega48                                     |     |

|    | 32.2Errata ATmega88                                     |     |

|    | 32.3Errata ATmega168                                    |     |

| 33 | Datasheet Revision History                              |     |

|    | 33.1Rev. 2545E-02/05                                    | 350 |

|    | 33.2Rev. 2545D-07/04                                    | 350 |

|    | 33.3Rev. 2545C-04/04                                    |     |

|    | 33.4Rev. 2545B-01/04                                    | 351 |

|    | Table of Contents                                       | i   |