#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 23                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 512 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168v-10aur |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

# 2. Overview

The ATmega48/88/168 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega48/88/168 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

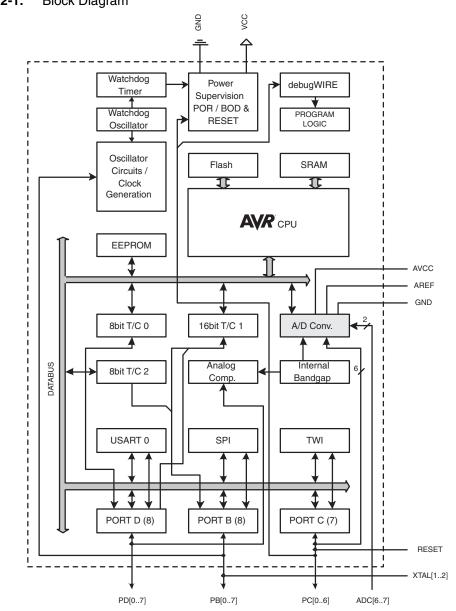

## 2.1 Block Diagram

## Figure 2-1. Block Diagram

# 7. Power Management and Sleep Modes

Sleep modes enable the application to shut down unused modules in the MCU, thereby saving power. The AVR provides various sleep modes allowing the user to tailor the power consumption to the application's requirements.

To enter any of the five sleep modes, the SE bit in SMCR must be written to logic one and a SLEEP instruction must be executed. The SM2, SM1, and SM0 bits in the SMCR Register select which sleep mode (Idle, ADC Noise Reduction, Power-down, Power-save, or Standby) will be activated by the SLEEP instruction. See Table 7-1 for a summary. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles in addition to the start-up time, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the Register File and SRAM are unaltered when the device wakes up from sleep. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset Vector.

Figure 6-1 on page 25 presents the different clock systems in the ATmega48/88/168, and their distribution. The figure is helpful in selecting an appropriate sleep mode.

### 7.0.1 Sleep Mode Control Register – SMCR

The Sleep Mode Control Register contains control bits for power management.

| Bit           | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   | _    |

|---------------|---|---|---|---|-----|-----|-----|-----|------|

|               | - | - | - | - | SM2 | SM1 | SM0 | SE  | SMCR |

| Read/Write    | R | R | R | R | R/W | R/W | R/W | R/W | -    |

| Initial Value | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |      |

#### • Bits 7..4 Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bits 3..1 – SM2..0: Sleep Mode Select Bits 2, 1, and 0

These bits select between the five available sleep modes as shown in Table 7-1.

| SM2 | SM1 | SM0 | Sleep Mode             |

|-----|-----|-----|------------------------|

| 0   | 0   | 0   | Idle                   |

| 0   | 0   | 1   | ADC Noise Reduction    |

| 0   | 1   | 0   | Power-down             |

| 0   | 1   | 1   | Power-save             |

| 1   | 0   | 0   | Reserved               |

| 1   | 0   | 1   | Reserved               |

| 1   | 1   | 0   | Standby <sup>(1)</sup> |

| 1   | 1   | 1   | Reserved               |

Table 7-1.

Sleep Mode Select

Note: 1. Standby mode is only recommended for use with external crystals or resonators.

#### • Bit 0 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmer's

- In the same operation, write a logic one to the Watchdog change enable bit (WDCE) and WDE. A logic one must be written to WDE regardless of the previous value of the WDE bit.

- 2. Within the next four clock cycles, write the WDE and Watchdog prescaler bits (WDP) as desired, but with the WDCE bit cleared. This must be done in one operation.

The following code example shows one assembly and one C function for turning off the Watchdog Timer. The example assumes that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during the execution of these functions.

```

Assembly Code Example<sup>(1)</sup>

WDT_off:

; Turn off global interrupt

cli

; Reset Watchdog Timer

wdr

; Clear WDRF in MCUSR

in

r16, MCUSR

andi r16, (0xff & (0<<WDRF))

out

MCUSR, r16

; Write logical one to WDCE and WDE

; Keep old prescaler setting to prevent unintentional time-out

lds r16, WDTCSR

r16, (1<<WDCE) | (1<<WDE)

ori

sts WDTCSR, r16

; Turn off WDT

ldi

r16, (0<<WDE)

sts WDTCSR, r16

; Turn on global interrupt

sei

ret

C Code Example<sup>(1)</sup>

void WDT_off(void)

{

__disable_interrupt();

__watchdog_reset();

/* Clear WDRF in MCUSR */

MCUSR &= \sim (1 < < WDRF);

/* Write logical one to WDCE and WDE */

/* Keep old prescaler setting to prevent unintentional time-out */

WDTCSR \mid = (1<<WDCE) \mid (1<<WDE);

/* Turn off WDT */

WDTCSR = 0 \times 00;

__enable_interrupt();

}

```

Note: 1. See "About Code Examples" on page 6.

## 9.2 Interrupt Vectors in ATmega88

| Table 9-2. | Reset and Interrupt Vectors in ATmega88 |

|------------|-----------------------------------------|

|            | ricoot and michapt rootoro mirinogaoo   |

| Vector No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                    |

|------------|-----------------------------------|--------------|-------------------------------------------------------------------------|

| 1          | 0x000 <sup>(1)</sup>              | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2          | 0x001                             | INT0         | External Interrupt Request 0                                            |

| 3          | 0x002                             | INT1         | External Interrupt Request 1                                            |

| 4          | 0x003                             | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5          | 0x004                             | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6          | 0x005                             | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7          | 0x006                             | WDT          | Watchdog Time-out Interrupt                                             |

| 8          | 0x007                             | TIMER2 COMPA | Timer/Counter2 Compare Match A                                          |

| 9          | 0x008                             | TIMER2 COMPB | Timer/Counter2 Compare Match B                                          |

| 10         | 0x009                             | TIMER2 OVF   | Timer/Counter2 Overflow                                                 |

| 11         | 0x00A                             | TIMER1 CAPT  | Timer/Counter1 Capture Event                                            |

| 12         | 0x00B                             | TIMER1 COMPA | Timer/Counter1 Compare Match A                                          |

| 13         | 0x00C                             | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                          |

| 14         | 0x00D                             | TIMER1 OVF   | Timer/Counter1 Overflow                                                 |

| 15         | 0x00E                             | TIMER0 COMPA | Timer/Counter0 Compare Match A                                          |

| 16         | 0x00F                             | TIMER0 COMPB | Timer/Counter0 Compare Match B                                          |

| 17         | 0x010                             | TIMER0 OVF   | Timer/Counter0 Overflow                                                 |

| 18         | 0x011                             | SPI, STC     | SPI Serial Transfer Complete                                            |

| 19         | 0x012                             | USART, RX    | USART Rx Complete                                                       |

| 20         | 0x013                             | USART, UDRE  | USART, Data Register Empty                                              |

| 21         | 0x014                             | USART, TX    | USART, Tx Complete                                                      |

| 22         | 0x015                             | ADC          | ADC Conversion Complete                                                 |

| 23         | 0x016                             | EE READY     | EEPROM Ready                                                            |

| 24         | 0x017                             | ANALOG COMP  | Analog Comparator                                                       |

| 25         | 0x018                             | TWI          | 2-wire Serial Interface                                                 |

| 26         | 0x019                             | SPM READY    | Store Program Memory Ready                                              |

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at

reset, see "Boot Loader Support - Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264.

2. When the IVSEL bit in MCUCR is set, Interrupt Vectors will be moved to the start of the Boot Flash Section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash Section.

Table 9-3 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

| Signal<br>Name | PB7/XTAL2/<br>TOSC2/PCINT7 <sup>(1)</sup>  | PB6/XTAL1/<br>TOSC1/PCINT6 <sup>(1)</sup> | PB5/SCK/<br>PCINT5        | PB4/MISO/<br>PCINT4            |

|----------------|--------------------------------------------|-------------------------------------------|---------------------------|--------------------------------|

| PUOE           | INTRC • EXTCK+<br>AS2                      | INTRC + AS2                               | SPE • MSTR                | SPE • MSTR                     |

| PUOV           | 0                                          | 0                                         | PORTB5 • PUD              | PORTB4 • PUD                   |

| DDOE           | INTRC • EXTCK+<br>AS2                      | INTRC + AS2                               | SPE • MSTR                | SPE • MSTR                     |

| DDOV           | 0                                          | 0                                         | 0                         | 0                              |

| PVOE           | 0                                          | 0                                         | SPE • MSTR                | SPE • MSTR                     |

| PVOV           | 0                                          | 0                                         | SCK OUTPUT                | SPI SLAVE<br>OUTPUT            |

| DIEOE          | INTRC • EXTCK +<br>AS2 + PCINT7 •<br>PCIE0 | INTRC + AS2 +<br>PCINT6 • PCIE0           | PCINT5 • PCIE0            | PCINT4 • PCIE0                 |

| DIEOV          | (INTRC + EXTCK) •<br>AS2                   | INTRC • AS2                               | 1                         | 1                              |

| DI             | PCINT7 INPUT                               | PCINT6 INPUT                              | PCINT5 INPUT<br>SCK INPUT | PCINT4 INPUT<br>SPI MSTR INPUT |

| AIO            | Oscillator Output                          | Oscillator/Clock<br>Input                 | -                         | -                              |

Table 10-4.

Overriding Signals for Alternate Functions in PB7..PB4

Notes: 1. INTRC means that one of the internal RC Oscillators are selected (by the CKSEL fuses), EXTCK means that external clock is selected (by the CKSEL fuses).

| Signal<br>Name | PB3/MOSI/<br>OC2/PCINT3         | PB2/ <del>SS</del> /<br>OC1B/PCINT2 | PB1/OC1A/<br>PCINT1 | PB0/ICP1/<br>PCINT0        |

|----------------|---------------------------------|-------------------------------------|---------------------|----------------------------|

| PUOE           | SPE • MSTR                      | SPE • MSTR                          | 0                   | 0                          |

| PUOV           | PORTB3 • PUD                    | PORTB2 • PUD                        | 0                   | 0                          |

| DDOE           | SPE • MSTR                      | SPE • MSTR                          | 0                   | 0                          |

| DDOV           | 0                               | 0                                   | 0                   | 0                          |

| PVOE           | SPE • MSTR +<br>OC2A ENABLE     | OC1B ENABLE                         | OC1A ENABLE         | 0                          |

| PVOV           | SPI MSTR OUTPUT<br>+ OC2A       | OC1B                                | OC1A                | 0                          |

| DIEOE          | PCINT3 • PCIE0                  | PCINT2 • PCIE0                      | PCINT1 • PCIE0      | PCINT0 • PCIE0             |

| DIEOV          | 1                               | 1                                   | 1                   | 1                          |

| DI             | PCINT3 INPUT<br>SPI SLAVE INPUT | PCINT2 INPUT<br>SPI SS              | PCINT1 INPUT        | PCINT0 INPUT<br>ICP1 INPUT |

| AIO            | _                               | -                                   | -                   | -                          |

**Table 10-5.** Overriding Signals for Alternate Functions in PB3..PB0

#### 11.1.1 External Interrupt Control Register A – EICRA

The External Interrupt Control Register A contains control bits for interrupt sense control.

| Bit           | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     | _     |

|---------------|---|---|---|---|-------|-------|-------|-------|-------|

|               | - | - | - | - | ISC11 | ISC10 | ISC01 | ISC00 | EICRA |

| Read/Write    | R | R | R | R | R/W   | R/W   | R/W   | R/W   | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0     | 0     | 0     | 0     |       |

#### • Bit 7..4 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 11-1. The value on the INT1 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

Table 11-1.

Interrupt 1 Sense Control

| ISC11 | ISC10 | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT1 generates an interrupt request. |

| 1     | 0     | The falling edge of INT1 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.    |

#### • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 11-2. The value on the INT0 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

| ISC01 | ISC00 | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT0 generates an interrupt request. |

| 1     | 0     | The falling edge of INT0 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.    |

Table 11-2.

Interrupt 0 Sense Control

#### Assembly Code Example<sup>(1)</sup>

| TIM16_ReadTCNT1:                  |

|-----------------------------------|

| ; Save global interrupt flag      |

| in r18,SREG                       |

| ; Disable interrupts              |

| cli                               |

| ; Read TCNT <b>1</b> into r17:r16 |

| in r16,TCNT1L                     |

| in r17, TCNT1H                    |

| ; Restore global interrupt flag   |

| out SREG, r18                     |

| ret                               |

C Code Example<sup>(1)</sup>

```

unsigned int TIM16_ReadTCNT1( void )

{

unsigned char sreg;

unsigned int i;

/* Save global interrupt flag */

sreg = SREG;

/* Disable interrupts */

_CLI();

/* Read TCNT1 into i */

i = TCNT1;

/* Restore global interrupt flag */

SREG = sreg;

return i;

}

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNT1 value in the r17:r16 register pair.

The following code examples show how to do an atomic write of the TCNT1 Register contents. Writing any of the OCR1A/B or ICR1 Registers can be done by using the same principle.

# ATmega48/88/168

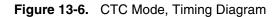

An interrupt can be generated at each time the counter value reaches the TOP value by either using the OCF1A or ICF1 Flag according to the register used to define the TOP value. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing the TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR1A or ICR1 is lower than the current value of TCNT1, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. In many cases this feature is not desirable. An alternative will then be to use the fast PWM mode using OCR1A for defining TOP (WGM13:0 = 15) since the OCR1A then will be double buffered.

For generating a waveform output in CTC mode, the OC1A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM1A1:0 = 1). The OC1A value will not be visible on the port pin unless the data direction for the pin is set to output (DDR\_OC1A = 1). The waveform generated will have a maximum frequency of  $f_{OC1A} = f_{clk_l/O}/2$  when OCR1A is set to zero (0x0000). The waveform frequency is defined by the following equation:

$$f_{OCnA} = \frac{f_{clk\_I/O}}{2 \cdot N \cdot (1 + OCRnA)}$$

The N variable represents the prescaler factor (1, 8, 64, 256, or 1024).

As for the Normal mode of operation, the TOV1 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x0000.

### 13.8.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM13:0 = 5, 6, 7, 14, or 15) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM options by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is set on the compare match between TCNT1 and OCR1x, and cleared at TOP. In inverting Compare Output mode output is cleared on compare match and set at TOP. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct and phase and frequency correct PWM modes that use dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), hence reduces total system cost.

# 13.10 16-bit Timer/Counter Register Description

#### 13.10.1 Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     | _      |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

|               | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | WGM11 | WGM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

#### • Bit 7:6 – COM1A1:0: Compare Output Mode for Channel A

#### • Bit 5:4 – COM1B1:0: Compare Output Mode for Channel B

The COM1A1:0 and COM1B1:0 control the Output Compare pins (OC1A and OC1B respectively) behavior. If one or both of the COM1A1:0 bits are written to one, the OC1A output overrides the normal port functionality of the I/O pin it is connected to. If one or both of the COM1B1:0 bit are written to one, the OC1B output overrides the normal port functionality of the I/O pin it is connected to. However, note that the *Data Direction Register* (DDR) bit corresponding to the OC1A or OC1B pin must be set in order to enable the output driver.

When the OC1A or OC1B is connected to the pin, the function of the COM1x1:0 bits is dependent of the WGM13:0 bits setting. Table 13-1 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to a Normal or a CTC mode (non-PWM).

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                 |

|---------------|---------------|-------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.              |

| 0             | 1             | Toggle OC1A/OC1B on Compare Match.                          |

| 1             | 0             | Clear OC1A/OC1B on Compare Match (Set output to low level). |

| 1             | 1             | Set OC1A/OC1B on Compare Match (Set output to high level).  |

Table 13-1. Compare Output Mode, non-PWM

Table 13-2 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to the fast PWM mode.

|  | Table 13-2. | Compare | Output Mode, | Fast PWM <sup>(1)</sup> |

|--|-------------|---------|--------------|-------------------------|

|--|-------------|---------|--------------|-------------------------|

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                                                                                                                                       |

|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.                                                                                                                                    |

| 0             | 1             | WGM13:0 = 14 or 15: Toggle OC1A on Compare<br>Match, OC1B disconnected (normal port operation).<br>For all other WGM1 settings, normal port operation,<br>OC1A/OC1B disconnected. |

| 1             | 0             | Clear OC1A/OC1B on Compare Match, set<br>OC1A/OC1B at TOP                                                                                                                         |

| 1             | 1             | Set OC1A/OC1B on Compare Match, clear<br>OC1A/OC1B at TOP                                                                                                                         |

A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. In this case the compare match is ignored, but the set or clear is done at TOP. See Section "13.8.3" on page 119. for more details.

A FOC1A/FOC1B strobe will not generate any interrupt nor will it clear the timer in Clear Timer on Compare match (CTC) mode using OCR1A as TOP.

The FOC1A/FOC1B bits are always read as zero.

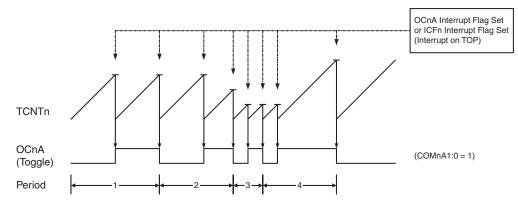

#### 13.10.4 Timer/Counter1 – TCNT1H and TCNT1L

The two *Timer/Counter* I/O locations (TCNT1H and TCNT1L, combined TCNT1) give direct access, both for read and for write operations, to the Timer/Counter unit 16-bit counter. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See Section "13.2" on page 108.

Modifying the counter (TCNT1) while the counter is running introduces a risk of missing a compare match between TCNT1 and one of the OCR1x Registers.

Writing to the TCNT1 Register blocks (removes) the compare match on the following timer clock for all compare units.

#### 13.10.5 Output Compare Register 1 A – OCR1AH and OCR1AL

| Bit           | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0      | _      |

|---------------|-------------|-----|-----|-----|-----|-----|-----|--------|--------|

|               | OCR1A[15:8] |     |     |     |     |     |     |        | OCR1AH |

|               | OCR1A[7:0]  |     |     |     |     |     |     | OCR1AL |        |

| Read/Write    | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W    |        |

| Initial Value | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0      |        |

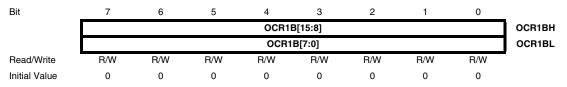

#### 13.10.6 Output Compare Register 1 B – OCR1BH and OCR1BL

The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNT1). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC1x pin.

The Output Compare Registers are 16-bit in size. To ensure that both the high and low bytes are written simultaneously when the CPU writes to these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See Section "13.2" on page 108.

generated will have a maximum frequency of  $f_{oc2} = f_{clk_l/O}/2$  when OCR2A is set to zero. This feature is similar to the OC2A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

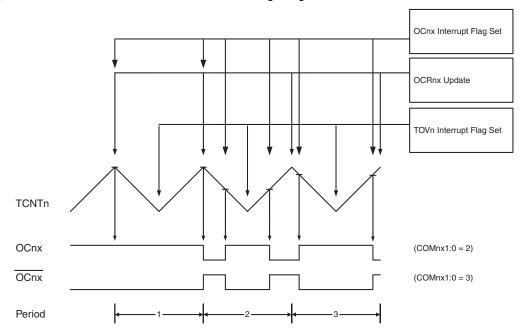

#### 15.6.4 Phase Correct PWM Mode

The phase correct PWM mode (WGM22:0 = 1 or 5) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to TOP and then from TOP to BOT-TOM. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. In non-inverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x while upcounting, and set on the compare match while downcount-ing. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

In phase correct PWM mode the counter is incremented until the counter value matches TOP. When the counter reaches TOP, it changes the count direction. The TCNT2 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown on Figure 15-7. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value.

In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM. An inverted PWM

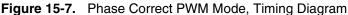

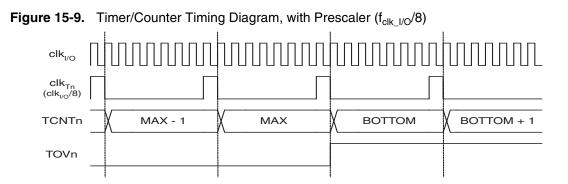

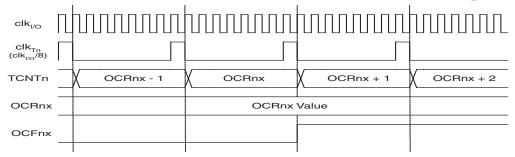

Figure 15-10 shows the setting of OCF2A in all modes except CTC mode.

Figure 15-10. Timer/Counter Timing Diagram, Setting of OCF2A, with Prescaler ( $f_{clk_l/O}/8$ )

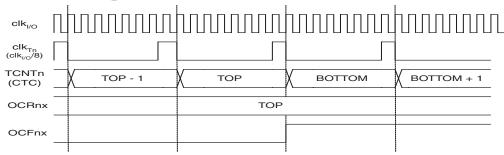

Figure 15-11 shows the setting of OCF2A and the clearing of TCNT2 in CTC mode.

Figure 15-11. Timer/Counter Timing Diagram, Clear Timer on Compare Match mode, with Prescaler (f<sub>clk\_l/O</sub>/8)

## 17.5 Data Transmission – The USART Transmitter

The USART Transmitter is enabled by setting the *Transmit Enable* (TXEN) bit in the UCSRnB Register. When the Transmitter is enabled, the normal port operation of the TxDn pin is overridden by the USART and given the function as the Transmitter's serial output. The baud rate, mode of operation and frame format must be set up once before doing any transmissions. If synchronous operation is used, the clock on the XCKn pin will be overridden and used as transmission clock.

#### 17.5.1 Sending Frames with 5 to 8 Data Bit

A data transmission is initiated by loading the transmit buffer with the data to be transmitted. The CPU can load the transmit buffer by writing to the UDRn I/O location. The buffered data in the transmit buffer will be moved to the Shift Register when the Shift Register is ready to send a new frame. The Shift Register is loaded with new data if it is in idle state (no ongoing transmission) or immediately after the last stop bit of the previous frame is transmitted. When the Shift Register is loaded with new data, it will transfer one complete frame at the rate given by the Baud Register, U2Xn bit or by XCKn depending on mode of operation.

The following code examples show a simple USART transmit function based on polling of the *Data Register Empty* (UDREn) Flag. When using frames with less than eight bits, the most significant bits written to the UDRn are ignored. The USART has to be initialized before the function can be used. For the assembly code, the data to be sent is assumed to be stored in Register R16

```

Assembly Code Example<sup>(1)</sup>

```

```

USART_Transmit:

; Wait for empty transmit buffer

sbis UCSRnA,UDREn

rjmp USART_Transmit

; Put data (r16) into buffer, sends the data

out UDRn,r16

ret

```

C Code Example<sup>(1)</sup>

```

void USART_Transmit( unsigned char data )

{

/* Wait for empty transmit buffer */

while ( !( UCSRnA & (1<<UDREn)) )

;

/* Put data into buffer, sends the data */

UDRn = data;

}</pre>

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The function simply waits for the transmit buffer to be empty by checking the UDREn Flag, before loading it with new data to be transmitted. If the Data Register Empty interrupt is utilized, the interrupt routine writes the data into the buffer.

#### 19.8.2 Master Receiver Mode

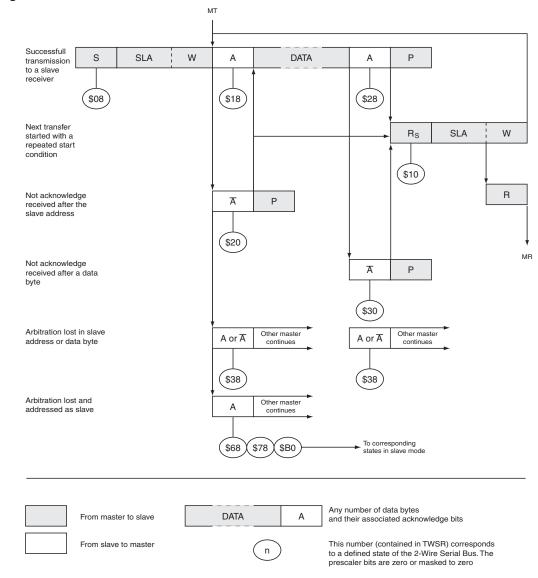

In the Master Receiver mode, a number of data bytes are received from a Slave Transmitter (Slave see Figure 19-14). In order to enter a Master mode, a START condition must be transmitted. The format of the following address packet determines whether Master Transmitter or Master Receiver mode is to be entered. If SLA+W is transmitted, MT mode is entered, if SLA+R is transmitted, MR mode is entered. All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

## 21.6 ADC Conversion Result

After the conversion is complete (ADIF is high), the conversion result can be found in the ADC Result Registers (ADCL, ADCH).

For single ended conversion, the result is

$$ADC = \frac{V_{IN} \cdot 1024}{V_{REF}}$$

where  $V_{IN}$  is the voltage on the selected input pin and  $V_{REF}$  the selected voltage reference (see Table 21-2 on page 250 and Table 21-3 on page 251). 0x000 represents analog ground, and 0x3FF represents the selected reference voltage minus one LSB.

#### 21.6.1 ADC Multiplexer Selection Register – ADMUX

| Bit           | 7     | 6     | 5     | 4 | 3    | 2    | 1    | 0    | _     |

|---------------|-------|-------|-------|---|------|------|------|------|-------|

|               | REFS1 | REFS0 | ADLAR | _ | MUX3 | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write    | R/W   | R/W   | R/W   | R | R/W  | R/W  | R/W  | R/W  | -     |

| Initial Value | 0     | 0     | 0     | 0 | 0    | 0    | 0    | 0    |       |

#### • Bit 7:6 - REFS1:0: Reference Selection Bits

These bits select the voltage reference for the ADC, as shown in Table 21-2. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set). The internal voltage reference options may not be used if an external reference voltage is being applied to the AREF pin.

#### Table 21-2. Voltage Reference Selections for ADC

| REFS1 | REFS0 | Voltage Reference Selection                                         |

|-------|-------|---------------------------------------------------------------------|

| 0     | 0     | AREF, Internal V <sub>ref</sub> turned off                          |

| 0     | 1     | AV <sub>CC</sub> with external capacitor at AREF pin                |

| 1     | 0     | Reserved                                                            |

| 1     | 1     | Internal 1.1V Voltage Reference with external capacitor at AREF pin |

#### • Bit 5 – ADLAR: ADC Left Adjust Result

The ADLAR bit affects the presentation of the ADC conversion result in the ADC Data Register. Write one to ADLAR to left adjust the result. Otherwise, the result is right adjusted. Changing the ADLAR bit will affect the ADC Data Register immediately, regardless of any ongoing conversions. For a complete description of this bit, see "The ADC Data Register – ADCL and ADCH" on page 253.

#### • Bit 4 – Res: Reserved Bit

This bit is an unused bit in the ATmega48/88/168, and will always read as zero.

• Bits 3:0 – MUX3:0: Analog Channel Selection Bits

#### 23.0.3 Performing a Page Write

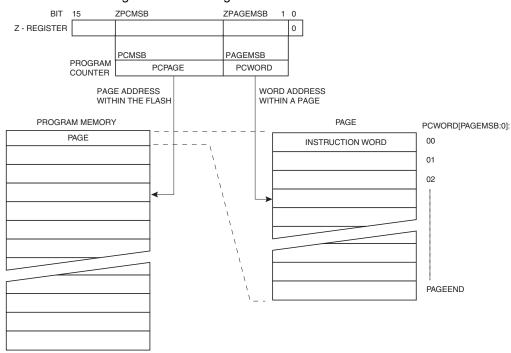

To execute Page Write, set up the address in the Z-pointer, write "00000101" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored. The page address must be written to PCPAGE. Other bits in the Z-pointer must be written to zero during this operation.

• The CPU is halted during the Page Write operation.

#### 23.1 Addressing the Flash During Self-Programming

The Z-pointer is used to address the SPM commands.

| Bit      | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| ZH (R31) | Z15 | Z14 | Z13 | Z12 | Z11 | Z10 | Z9 | Z8 |

| ZL (R30) | Z7  | Z6  | Z5  | Z4  | Z3  | Z2  | Z1 | Z0 |

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

Since the Flash is organized in pages (see Table 25-8 on page 284), the Program Counter can be treated as having two different sections. One section, consisting of the least significant bits, is addressing the words within a page, while the most significant bits are addressing the pages. This is shown in Figure 24-3. Note that the Page Erase and Page Write operations are addressed independently. Therefore it is of major importance that the software addresses the same page in both the Page Erase and Page Write operation.

The LPM instruction uses the Z-pointer to store the address. Since this instruction addresses the Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used.

#### Figure 23-1. Addressing the Flash During SPM<sup>(1)</sup>

Note: 1. The different variables used in Figure 24-3 are listed in Table 25-8 on page 284.

## 25.4 Calibration Byte

The ATmega48/88/168 has a byte calibration value for the internal RC Oscillator. This byte resides in the high byte of address 0x000 in the signature address space. During reset, this byte is automatically written into the OSCCAL Register to ensure correct frequency of the calibrated RC Oscillator.

## 25.5 Page Size

| Table 23-0. No. of Words in a rage and No. of rages in the rash |                         |           |         |                 |          |       |  |

|-----------------------------------------------------------------|-------------------------|-----------|---------|-----------------|----------|-------|--|

| Device                                                          | Flash Size              | Page Size | PCWORD  | No. of<br>Pages | PCPAGE   | PCMSB |  |

| ATmega48                                                        | 2K words<br>(4K bytes)  | 32 words  | PC[4:0] | 64              | PC[10:5] | 10    |  |

| ATmega88                                                        | 4K words<br>(8K bytes)  | 32 words  | PC[4:0] | 128             | PC[11:5] | 11    |  |

| ATmega168                                                       | 8K words<br>(16K bytes) | 64 words  | PC[5:0] | 128             | PC[12:6] | 12    |  |

Table 25-8.

No. of Words in a Page and No. of Pages in the Flash

| Table 25-9. | No. of Words in a Page and No. of Pages in the EEPROM |

|-------------|-------------------------------------------------------|

|-------------|-------------------------------------------------------|

| Device    | EEPROM<br>Size | Page<br>Size | PCWORD   | No. of<br>Pages | PCPAGE   | EEAMSB |

|-----------|----------------|--------------|----------|-----------------|----------|--------|

| ATmega48  | 256 bytes      | 4 bytes      | EEA[1:0] | 64              | EEA[7:2] | 7      |

| ATmega88  | 512 bytes      | 4 bytes      | EEA[1:0] | 128             | EEA[8:2] | 8      |

| ATmega168 | 512 bytes      | 4 bytes      | EEA[1:0] | 128             | EEA[8:2] | 8      |

## 25.6 Parallel Programming Parameters, Pin Mapping, and Commands

This section describes how to parallel program and verify Flash Program memory, EEPROM Data memory, Memory Lock bits, and Fuse bits in the ATmega48/88/168. Pulses are assumed to be at least 250 ns unless otherwise noted.

#### 25.6.1 Signal Names

In this section, some pins of the ATmega48/88/168 are referenced by signal names describing their functionality during parallel programming, see Figure 25-1 and Table 25-10. Pins not described in the following table are referenced by pin names.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding is shown in Table 25-12.

When pulsing  $\overline{WR}$  or  $\overline{OE}$ , the command loaded determines the action executed. The different Commands are shown in Table 25-13.

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data low byte (0x00 0xFF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- 2. Give PAGEL a positive pulse. This latches the data bytes. (See Figure 25-3 for signal waveforms)

F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 25-2 on page 289. Note that if less than eight bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address low byte are used to address the page when performing a Page Write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- H. Program Page

- 1. Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- 2. Wait until RDY/BSY goes high (See Figure 25-3 for signal waveforms).

I. Repeat B through H until the entire Flash is programmed or until all data has been programmed.

J. End Page Programming

- 1. 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set DATA to "0000 0000". This is the command for No Operation.

- 3. Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

| Mnemonics                | Operands | Description             | Operation                                | Flags | #Clocks |  |  |  |  |

|--------------------------|----------|-------------------------|------------------------------------------|-------|---------|--|--|--|--|

| POP                      | Rd       | Pop Register from Stack | $Rd \leftarrow STACK$                    | None  | 2       |  |  |  |  |

| MCU CONTROL INSTRUCTIONS |          |                         |                                          |       |         |  |  |  |  |

| NOP                      |          | No Operation            |                                          | None  | 1       |  |  |  |  |

| SLEEP                    |          | Sleep                   | (see specific descr. for Sleep function) | None  | 1       |  |  |  |  |

| WDR                      |          | Watchdog Reset          | (see specific descr. for WDR/timer)      | None  | 1       |  |  |  |  |

| BREAK                    |          | Break                   | For On-chip Debug Only                   | None  | N/A     |  |  |  |  |

Note: 1. These instructions are only available in ATmega168.

# **Table of Contents**

|   | Features                                                | 1  |

|---|---------------------------------------------------------|----|

| 1 | Pin Configurations                                      | 2  |

|   | 1.1Disclaimer                                           | 3  |

| 2 | Overview                                                | 3  |

|   | 2.1Block Diagram                                        | 3  |

|   | 2.2Comparison Between ATmega48, ATmega88, and ATmega168 | 4  |

|   | 2.3Pin Descriptions                                     | 5  |

| 3 | About Code Examples                                     | 6  |

| 4 | AVR CPU Core                                            | 7  |

|   | 4.1 Introduction                                        | 7  |

|   | 4.2Architectural Overview                               | 7  |

|   | 4.3ALU – Arithmetic Logic Unit                          | 8  |

|   | 4.4Status Register                                      | 9  |

|   | 4.5General Purpose Register File                        | 10 |

|   | 4.6Stack Pointer                                        | 11 |

|   | 4.7Instruction Execution Timing                         | 12 |

|   | 4.8Reset and Interrupt Handling                         | 12 |

| 5 | AVR ATmega48/88/168 Memories                            | 15 |

|   | 5.1In-System Reprogrammable Flash Program Memory        | 15 |

|   | 5.2SRAM Data Memory                                     | 17 |

|   | 5.3EEPROM Data Memory                                   | 18 |

|   | 5.4I/O Memory                                           | 24 |

| 6 | System Clock and Clock Options                          | 25 |

|   | 6.1Clock Systems and their Distribution                 | 25 |

|   | 6.2Clock Sources                                        | 26 |

|   | 6.3Low Power Crystal Oscillator                         | 27 |

|   | 6.4Full Swing Crystal Oscillator                        | 29 |

|   | 6.5Low Frequency Crystal Oscillator                     | 31 |

|   | 6.6Calibrated Internal RC Oscillator                    | 31 |

|   | 6.7128 kHz Internal Oscillator                          | 33 |

|   | 6.8External Clock                                       | 33 |

|   | 6.9Clock Output Buffer                                  | 34 |