Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                   |

|----------------------------|------------------------------------------------------------|

| Core Processor             | AVR                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 10MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                      |

| Number of I/O              | 23                                                         |

| Program Memory Size        | 16KB (8K × 16)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 512 x 8                                                    |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                |

| Data Converters            | A/D 6x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Through Hole                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | 28-PDIP                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega168v-10pi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

The various special features of Port D are elaborated in "Alternate Functions of Port D" on page 78.

# 2.3.7 AV<sub>cc</sub>

2.3.9

$AV_{CC}$  is the supply voltage pin for the A/D Converter, PC3..0, and ADC7..6. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. Note that PC6..4 use digital supply voltage,  $V_{CC}$ .

# 2.3.8 AREF AREF is the analog reference pin for the A/D Converter.

# ADC7..6 (TQFP and QFN/MLF Package Only)

In the TQFP and QFN/MLF package, ADC7..6 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.

# 3. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

Assembly Code Example

| <b>in</b> r16, S | SREG    | ; store SREG value               |

|------------------|---------|----------------------------------|

| cli ;            | disable | interrupts during timed sequence |

| <b>sbi</b> EECR, | EEMPE   | ; start EEPROM write             |

| <b>sbi</b> EECR, | EEPE    |                                  |

| out SREG,        | r16     | ; restore SREG value (I-bit)     |

C Code Example

```

char cSREG;

cSREG = SREG; /* store SREG value */

/* disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMPE); /* start EEPROM write */

EECR |= (1<<EEPE);

SREG = cSREG; /* restore SREG value (I-bit) */

```

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in this example.

| Assembly  | Code Example                                                  |

|-----------|---------------------------------------------------------------|

| sei       | : set Global Interrupt Enable                                 |

| sleep     | enter sleep, waiting for interrupt                            |

| ; note    | e: will enter sleep before any pending interrupt(s)           |

| C Code Ex | ample                                                         |

| enal      | <pre>ole_interrupt(); /* set Global Interrupt Enable */</pre> |

| slee      | ep(); /* enter sleep, waiting for interrupt */                |

| /* not    | te: will enter sleep before any pending interrupt(s) */       |

# 4.8.1 Interrupt Response Time

The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. After four clock cycles the program vector address for the actual interrupt handling routine is executed. During this four clock cycle period, the Program Counter is pushed onto the Stack. The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the Program Counter (two bytes) is popped back from the Stack, the Stack Pointer is incremented by two, and the I-bit in SREG is set.

Note: If the Watchdog is accidentally enabled, for example by a runaway pointer or brown-out condition, the device will be reset and the Watchdog Timer will stay enabled. If the code is not set up to handle the Watchdog, this might lead to an eternal loop of time-out resets. To avoid this situation, the application software should always clear the Watchdog System Reset Flag (WDRF) and the WDE control bit in the initialisation routine, even if the Watchdog is not in use.

The following code example shows one assembly and one C function for changing the time-out value of the Watchdog Timer.

```

Assembly Code Example<sup>(1)</sup>

WDT_Prescaler_Change:

; Turn off global interrupt

cli

; Reset Watchdog Timer

wdr

; Start timed sequence

lds r16, WDTCSR

ori

r16, (1<<WDCE) | (1<<WDE)

sts WDTCSR, r16

; -- Got four cycles to set the new values from here -

; Set new prescaler(time-out) value = 64K cycles (~0.5 s)

r16, (1<<WDE) | (1<<WDP2) | (1<<WDP0)

ldi

sts WDTCSR, r16

; -- Finished setting new values, used 2 cycles -

; Turn on global interrupt

sei

ret

C Code Example<sup>(1)</sup>

void WDT_Prescaler_Change(void)

{

__disable_interrupt();

__watchdog_reset();

/* Start timed equence */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* Set new prescaler(time-out) value = 64K cycles (~0.5 s) */

WDTCSR = (1<<WDE) | (1<<WDP2) | (1<<WDP0);

_enable_interrupt();

}

```

Note: 1. See "About Code Examples" on page 6.

Note: The Watchdog Timer should be reset before any change of the WDP bits, since a change in the WDP bits can result in a time-out when switching to a shorter time-out period.

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O.

# 10.2 Ports as General Digital I/O

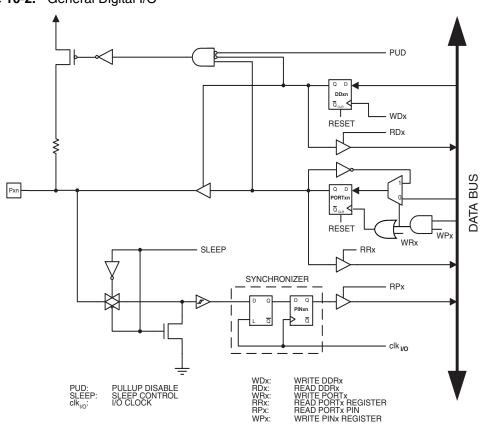

The ports are bi-directional I/O ports with optional internal pull-ups. Figure 10-2 shows a functional description of one I/O-port pin, here generically called Pxn.

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports.

# 10.2.1 Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in "Register Description for I/O Ports" on page 81, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

becomes the inverting output of the Oscillator amplifier. In this mode, a crystal Oscillator is connected to this pin, and the pin cannot be used as an I/O pin.

PCINT7: Pin Change Interrupt source 7. The PB7 pin can serve as an external interrupt source.

If PB7 is used as a clock pin, DDB7, PORTB7 and PINB7 will all read 0.

# • XTAL1/TOSC1/PCINT6 - Port B, Bit 6

XTAL1: Chip clock Oscillator pin 1. Used for all chip clock sources except internal calibrated RC Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

TOSC1: Timer Oscillator pin 1. Used only if internal calibrated RC Oscillator is selected as chip clock source, and the asynchronous timer is enabled by the correct setting in ASSR. When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PB6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

PCINT6: Pin Change Interrupt source 6. The PB6 pin can serve as an external interrupt source.

If PB6 is used as a clock pin, DDB6, PORTB6 and PINB6 will all read 0.

# • SCK/PCINT5 – Port B, Bit 5

SCK: Master Clock output, Slave Clock input pin for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB5 bit.

PCINT5: Pin Change Interrupt source 5. The PB5 pin can serve as an external interrupt source.

# • MISO/PCINT4 – Port B, Bit 4

MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input regardless of the setting of DDB4. When the SPI is enabled as a Slave, the data direction of this pin is controlled by DDB4. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB4 bit.

PCINT4: Pin Change Interrupt source 4. The PB4 pin can serve as an external interrupt source.

# MOSI/OC2/PCINT3 – Port B, Bit 3

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB3. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB3. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB3 bit.

OC2, Output Compare Match Output: The PB3 pin can serve as an external output for the Timer/Counter2 Compare Match. The PB3 pin has to be configured as an output (DDB3 set (one)) to serve this function. The OC2 pin is also the output pin for the PWM mode timer function.

PCINT3: Pin Change Interrupt source 3. The PB3 pin can serve as an external interrupt source.

# • SS/OC1B/PCINT2 – Port B, Bit 2

$\overline{SS}$ : Slave Select input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB2. As a Slave, the SPI is activated when this pin is driven low.

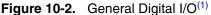

Figure 12-3. Output Compare Unit, Block Diagram

The OCR0x Registers are double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR0x Compare Registers to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCR0x Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR0x Buffer Register, and if double buffering is disabled the CPU will access the OCR0x directly.

# 12.4.1 Force Output Compare

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0x) bit. Forcing compare match will not set the OCF0x Flag or reload/clear the timer, but the OC0x pin will be updated as if a real compare match had occurred (the COM0x1:0 bits settings define whether the OC0x pin is set, cleared or toggled).

# 12.4.2 Compare Match Blocking by TCNT0 Write

All CPU write operations to the TCNT0 Register will block any compare match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0x to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.

# 12.4.3 Using the Output Compare Unit

Since writing TCNT0 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the Output Compare Unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0x value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is downcounting.

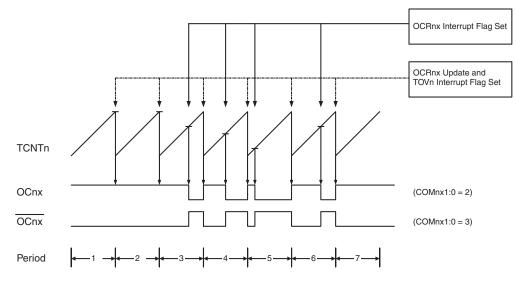

In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 15-6. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

Figure 15-6. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. (See Table 15-3 on page 149). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2x Register at the compare match between OCR2x and TCNT2, and clearing (or setting) the OC2x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clk\_I/O}}}{N \cdot 256}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM2A1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2x to toggle its logical level on each compare match (COM2x1:0 = 1). The waveform

contains data to be transmitted that has not yet been moved into the Shift Register. For compatibility with future devices, always write this bit to zero when writing the UCSRnA Register.

When the Data Register Empty Interrupt Enable (UDRIEn) bit in UCSRnB is written to one, the USART Data Register Empty Interrupt will be executed as long as UDREn is set (provided that global interrupts are enabled). UDREn is cleared by writing UDRn. When interrupt-driven data transmission is used, the Data Register Empty interrupt routine must either write new data to UDRn in order to clear UDREn or disable the Data Register Empty interrupt, otherwise a new interrupt will occur once the interrupt routine terminates.

The Transmit Complete (TXCn) Flag bit is set one when the entire frame in the Transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer. The TXCn Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXCn Flag is useful in half-duplex communication interfaces (like the RS-485 standard), where a transmitting application must enter receive mode and free the communication bus immediately after completing the transmission.

When the Transmit Compete Interrupt Enable (TXCIEn) bit in UCSRnB is set, the USART Transmit Complete Interrupt will be executed when the TXCn Flag becomes set (provided that global interrupts are enabled). When the transmit complete interrupt is used, the interrupt handling routine does not have to clear the TXCn Flag, this is done automatically when the interrupt is executed.

### 17.5.4 Parity Generator

The Parity Generator calculates the parity bit for the serial frame data. When parity bit is enabled (UPMn1 = 1), the transmitter control logic inserts the parity bit between the last data bit and the first stop bit of the frame that is sent.

### 17.5.5 Disabling the Transmitter

The disabling of the Transmitter (setting the TXEN to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn pin.

## 17.6 Data Reception – The USART Receiver

The USART Receiver is enabled by writing the Receive Enable (RXENn) bit in the UCSRnB Register to one. When the Receiver is enabled, the normal pin operation of the RxDn pin is overridden by the USART and given the function as the Receiver's serial input. The baud rate, mode of operation and frame format must be set up once before any serial reception can be done. If synchronous operation is used, the clock on the XCKn pin will be used as transfer clock.

## 17.6.1 Receiving Frames with 5 to 8 Data Bits

The Receiver starts data reception when it detects a valid start bit. Each bit that follows the start bit will be sampled at the baud rate or XCKn clock, and shifted into the Receive Shift Register until the first stop bit of a frame is received. A second stop bit will be ignored by the Receiver. When the first stop bit is received, i.e., a complete serial frame is present in the Receive Shift Register, the contents of the Shift Register will be moved into the receive buffer. The receive buffer can then be read by reading the UDRn I/O location.

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|---------------------|---------------------------------------|

| 5                        | 93.20                 | 106.67                | +6.67/-6.8          | ± 3.0                                 |

| 6                        | 94.12                 | 105.79                | +5.79/-5.88         | ± 2.5                                 |

| 7                        | 94.81                 | 105.11                | +5.11/-5.19         | ± 2.0                                 |

| 8                        | 95.36                 | 104.58                | +4.58/-4.54         | ± 2.0                                 |

| 9                        | 95.81                 | 104.14                | +4.14/-4.19         | ± 1.5                                 |

| 10                       | 96.17                 | 103.78                | +3.78/-3.83         | ± 1.5                                 |

Table 17-2.

Recommended Maximum Receiver Baud Rate Error for Normal Speed Mode (U2Xn = 0)

Table 17-3.Recommended Maximum Receiver Baud Rate Error for Double Speed Mode<br/>(U2Xn = 1)

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|---------------------|---------------------------------------|

| 5                        | 94.12                 | 105.66                | +5.66/-5.88         | ± 2.5                                 |

| 6                        | 94.92                 | 104.92                | +4.92/-5.08         | ± 2.0                                 |

| 7                        | 95.52                 | 104,35                | +4.35/-4.48         | ± 1.5                                 |

| 8                        | 96.00                 | 103.90                | +3.90/-4.00         | ± 1.5                                 |

| 9                        | 96.39                 | 103.53                | +3.53/-3.61         | ± 1.5                                 |

| 10                       | 96.70                 | 103.23                | +3.23/-3.30         | ± 1.0                                 |

The recommendations of the maximum receiver baud rate error was made under the assumption that the Receiver and Transmitter equally divides the maximum total error.

There are two possible sources for the receivers baud rate error. The Receiver's system clock (XTAL) will always have some minor instability over the supply voltage range and the temperature range. When using a crystal to generate the system clock, this is rarely a problem, but for a resonator the system clock may differ more than 2% depending of the resonators tolerance. The second source for the error is more controllable. The baud rate generator can not always do an exact division of the system frequency to get the baud rate wanted. In this case an UBRRn value that gives an acceptable low error can be used if possible.

# 17.8 Multi-processor Communication Mode

Setting the Multi-processor Communication mode (MPCMn) bit in UCSRnA enables a filtering function of incoming frames received by the USART Receiver. Frames that do not contain address information will be ignored and not put into the receive buffer. This effectively reduces the number of incoming frames that has to be handled by the CPU, in a system with multiple MCUs that communicate via the same serial bus. The Transmitter is unaffected by the MPCMn setting, but has to be used differently when it is a part of a system utilizing the Multi-processor Communication mode.

If the Receiver is set up to receive frames that contain 5 to 8 data bits, then the first stop bit indicates if the frame contains data or address information. If the Receiver is set up for frames with

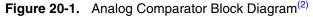

Notes:

#### : 1. See Table 20-2 on page 238.

2. Refer to Figure 1-1 on page 2 and Table 10-9 on page 78 for Analog Comparator pin placement.

## 20.0.1 ADC Control and Status Register B – ADCSRB

| Bit           | 7 | 6    | 5 | 4 | 3 | 2     | 1     | 0     | _      |

|---------------|---|------|---|---|---|-------|-------|-------|--------|

|               | - | ACME | - | - | - | ADTS2 | ADTS1 | ADTS0 | ADCSRB |

| Read/Write    | R | R/W  | R | R | R | R/W   | R/W   | R/W   |        |

| Initial Value | 0 | 0    | 0 | 0 | 0 | 0     | 0     | 0     |        |

## Bit 6 – ACME: Analog Comparator Multiplexer Enable

When this bit is written logic one and the ADC is switched off (ADEN in ADCSRA is zero), the ADC multiplexer selects the negative input to the Analog Comparator. When this bit is written logic zero, AIN1 is applied to the negative input of the Analog Comparator. For a detailed description of this bit, see "Analog Comparator Multiplexed Input" on page 237.

## 20.0.2 Analog Comparator Control and Status Register – ACSR

| Bit           | 7   | 6    | 5   | 4   | 3    | 2    | 1     | 0     | _    |

|---------------|-----|------|-----|-----|------|------|-------|-------|------|

|               | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR |

| Read/Write    | R/W | R/W  | R   | R/W | R/W  | R/W  | R/W   | R/W   | -    |

| Initial Value | 0   | 0    | N/A | 0   | 0    | 0    | 0     | 0     |      |

## • Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

## Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AINO is applied to the positive input of the Analog Comparator. See Section "8.1" on page 48.

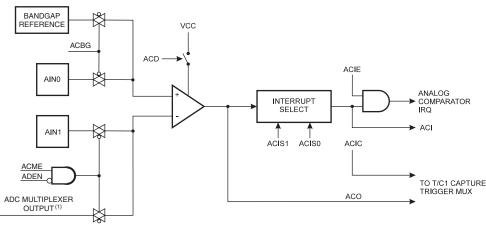

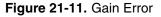

Figure 21-10. Offset Error

Gain error: After adjusting for offset, the gain error is found as the deviation of the last transition (0x3FE to 0x3FF) compared to the ideal transition (at 1.5 LSB below maximum). Ideal value: 0 LSB

• Integral Non-linearity (INL): After adjusting for offset and gain error, the INL is the maximum deviation of an actual transition compared to an ideal transition for any code. Ideal value: 0 LSB.

trigger signal. If ADEN in ADCSRA is set, this will start a conversion. Switching to Free Running mode (ADTS[2:0]=0) will not cause a trigger event, even if the ADC Interrupt Flag is set.

| ADTS2 | ADTS1 | ADTS0 | Trigger Source                 |

|-------|-------|-------|--------------------------------|

| 0     | 0     | 0     | Free Running mode              |

| 0     | 0     | 1     | Analog Comparator              |

| 0     | 1     | 0     | External Interrupt Request 0   |

| 0     | 1     | 1     | Timer/Counter0 Compare Match A |

| 1     | 0     | 0     | Timer/Counter0 Overflow        |

| 1     | 0     | 1     | Timer/Counter1 Compare Match B |

| 1     | 1     | 0     | Timer/Counter1 Overflow        |

| 1     | 1     | 1     | Timer/Counter1 Capture Event   |

Table 21-5.

ADC Auto Trigger Source Selections

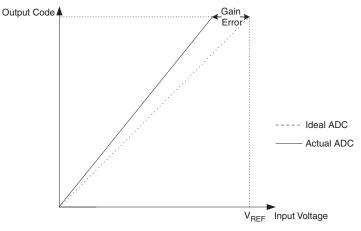

## 21.6.5 Digital Input Disable Register 0 – DIDR0

## • Bits 7:6 - Res: Reserved Bits

These bits are reserved for future use. To ensure compatibility with future devices, these bits must be written to zero when DIDR0 is written.

## • Bit 5:0 – ADC5D..ADC0D: ADC5..0 Digital Input Disable

When this bit is written logic one, the digital input buffer on the corresponding ADC pin is disabled. The corresponding PIN Register bit will always read as zero when this bit is set. When an analog signal is applied to the ADC5..0 pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer.

Note that ADC pins ADC7 and ADC6 do not have digital input buffers, and therefore do not require Digital Input Disable bits.

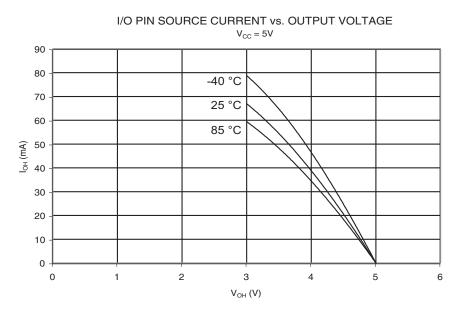

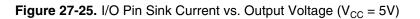

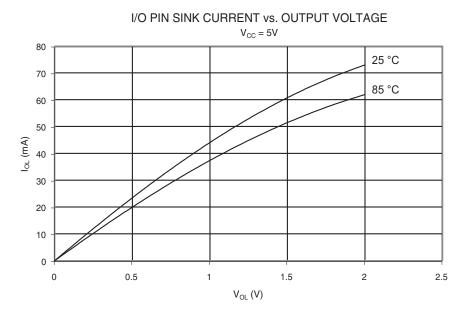

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

- All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon

- 6. Values with "Power Reduction Register PRR" disabled (0x00).

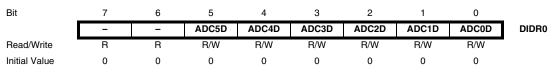

# 26.3 External Clock Drive Waveforms

### Figure 26-1. External Clock Drive Waveforms

# 26.4 External Clock Drive

|                     |                                                         | V <sub>CC</sub> =1 | V <sub>CC</sub> =1.8-5.5V |      | V <sub>CC</sub> =2.7-5.5V |      | V <sub>CC</sub> =4.5-5.5V |       |

|---------------------|---------------------------------------------------------|--------------------|---------------------------|------|---------------------------|------|---------------------------|-------|

| Symbol              | Parameter                                               | Min.               | Max.                      | Min. | Max.                      | Min. | Max.                      | Units |

| 1/t <sub>CLCL</sub> | Oscillator<br>Frequency                                 | 0                  | 4                         | 0    | 10                        | 0    | 20                        | MHz   |

| t <sub>CLCL</sub>   | Clock Period                                            | 250                |                           | 100  |                           | 50   |                           | ns    |

| t <sub>CHCX</sub>   | High Time                                               | 100                |                           | 40   |                           | 20   |                           | ns    |

| t <sub>CLCX</sub>   | Low Time                                                | 100                |                           | 40   |                           | 20   |                           | ns    |

| t <sub>CLCH</sub>   | Rise Time                                               |                    | 2.0                       |      | 1.6                       |      | 0.5                       | μs    |

| t <sub>CHCL</sub>   | Fall Time                                               |                    | 2.0                       |      | 1.6                       |      | 0.5                       | μS    |

| $\Delta t_{CLCL}$   | Change in period<br>from one clock<br>cycle to the next |                    | 2                         |      | 2                         |      | 2                         | %     |

Table 26-1.External Clock Drive

Note: All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon.

# 26.5 Maximum Speed vs. V<sub>CC</sub>

Maximum frequency is dependent on V<sub>CC.</sub> As shown in Figure 26-2 and Figure 26-3, the Maximum Frequency vs. V<sub>CC</sub> curve is linear between  $1.8V < V_{CC} < 2.7V$  and between  $2.7V < V_{CC} < 4.5V$ .

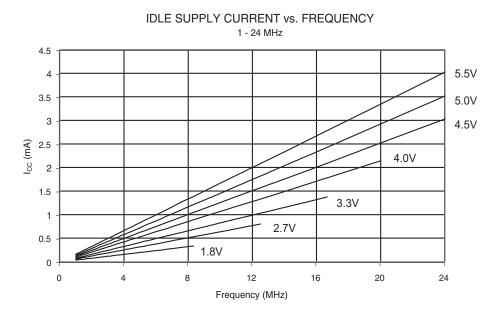

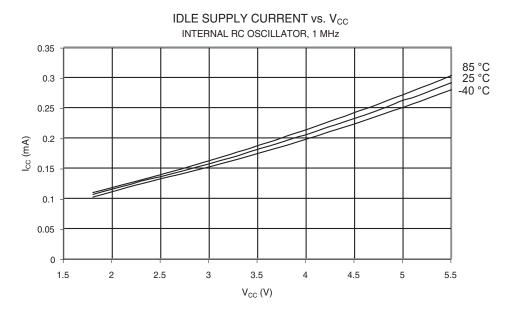

Figure 27-8. Idle Supply Current vs. Frequency (1 - 24 MHz)

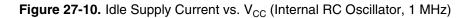

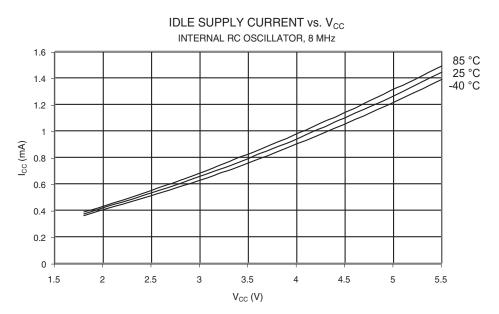

Figure 27-11. Idle Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 8 MHz)

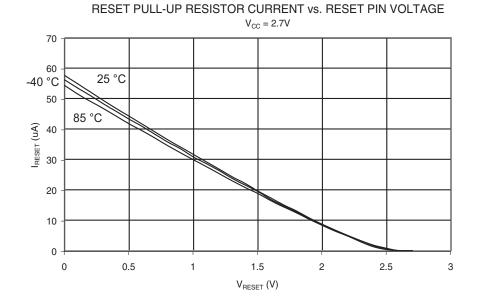

Figure 27-21. Reset Pull-Up Resistor Current vs. Reset Pin Voltage (V<sub>CC</sub> = 2.7V)

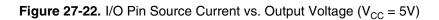

# 27.8 Pin Driver Strength

Figure 27-26. I/O Pin Sink Current vs. Output Voltage ( $V_{CC} = 2.7V$ )

# 30.3 ATmega168

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code                  | Package <sup>(1)</sup> | Operational Range |

|----------------------------|--------------|--------------------------------|------------------------|-------------------|

|                            |              | ATmega168V-10AI                | 32A                    |                   |

|                            |              | ATmega168V-10PI                | 28P3                   |                   |

| 10                         |              | ATmega168V-10MI                | 32M1-A                 | Industrial        |

| 10                         | 1.8 - 5.5    | ATmega168V-10AU <sup>(2)</sup> | 32A                    | (-40°C to 85°C)   |

|                            |              | ATmega168V-10PU <sup>(2)</sup> | 28P3                   |                   |

|                            |              | ATmega168V-10MU <sup>(2)</sup> | 32M1-A                 |                   |

|                            |              | ATmega168-20AI                 | 32A                    |                   |

|                            |              | ATmega168-20PI                 | 28P3                   |                   |

| 00                         | 2.7 - 5.5    | ATmega168-20MI                 | 32M1-A                 | Industrial        |

| 20                         |              | ATmega168-20AU <sup>(2)</sup>  | 32A                    | (-40°C to 85°C)   |

|                            |              | ATmega168-20PU <sup>(2)</sup>  | 28P3                   |                   |

|                            |              | ATmega168-20MU <sup>(2)</sup>  | 32M1-A                 |                   |

Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. See Figure 26-2 on page 302 and Figure 26-3 on page 302.

|        | Package Type                                                                                      |

|--------|---------------------------------------------------------------------------------------------------|

| 32A    | 32-lead, Thin (1.0 mm) Plastic Quad Flat Package (TQFP)                                           |

| 28P3   | 28-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                          |

| 32M1-A | 32-pad, 5 x 5 x 1.0 body, Lead Pitch 0.50 mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF) |

# 33. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

# 33.1 Rev. 2545E-02/05

- 1. MLF-package alternative changed to "Quad Flat No-Lead/Micro Lead Frame Package QFN/MLF".

- 2. Updated "The EEPROM Control Register EECR" on page 19.

- 3. Updated "Calibrated Internal RC Oscillator" on page 31.

- 4. Updated "External Clock" on page 33.

- 5. Updated Table 8-1 on page 44, Table 26-3 on page 304, Table 26-1 on page 301and Table 25-16 on page 297

- 6. Added "Pin Change Interrupt Timing" on page 83

- 7. Updated "8-bit Timer/Counter Block Diagram" on page 88.

- 8. Updated "Store Program Memory Control and Status Register SPMCSR" on page 259.

- 9. Updated "Enter Programming Mode" on page 286.

- 10. Updated "DC Characteristics" on page 299.

- 11. Updated "Ordering Information" on page 341.

- 12. Updated "Errata ATmega88" on page 348 and "Errata ATmega168" on page 349.

# 33.2 Rev. 2545D-07/04

- 1. Updated instructions used with WDTCSR in relevant code examples.

- 2. Updated Table 6-5 on page 29, Table 8-2 on page 46, Table 24-9 on page 278, and Table 24-11 on page 279.

- 3. Updated "System Clock Prescaler" on page 34.

- Moved "Timer/Counter2 Interrupt Mask Register TIMSK2" and "Timer/Counter2 Interrupt Flag Register – TIFR2" to "8-bit Timer/Counter Register Description" on page 149.

- 5. Updated cross-reference in "Electrical Interconnection" on page 206.

- 6. Updated equation in "Bit Rate Generator Unit" on page 211.

- 7. Added "Page Size" on page 284.

- 8. Updated "Serial Programming Algorithm" on page 296.

- 9. Updated Ordering Information for "ATmega168" on page 343.

- 10. Updated "Errata ATmega88" on page 348 and "Errata ATmega168" on page 349.

- 11. Updated equation in "Bit Rate Generator Unit" on page 211.

# 33.3 Rev. 2545C-04/04

- 1. Speed Grades changed: 12MHz to 10MHz and 24MHz to 20MHz

- 2. Updated "Maximum Speed vs. VCC" on page 301.

- 3. Updated "Ordering Information" on page 341.

- 4. Updated "Errata ATmega88" on page 348.

# 350 ATmega48/88/168

|    | 17.10Examples of Baud Rate Setting                            | 191 |

|----|---------------------------------------------------------------|-----|

| 18 | USART in SPI Mode                                             | 196 |

|    | 18.10verview                                                  | 196 |

|    | 18.2Clock Generation                                          | 196 |

|    | 18.3SPI Data Modes and Timing                                 | 197 |

|    | 18.4Frame Formats                                             | 198 |

|    | 18.5Data Transfer                                             | 199 |

|    | 18.6USART MSPIM Register Description                          | 201 |

|    | 18.7AVR USART MSPIM vs. AVR SPI                               | 204 |

| 19 | 2-wire Serial Interface                                       | 205 |

|    | 19.1Features                                                  | 205 |

|    | 19.22-wire Serial Interface Bus Definition                    | 205 |

|    | 19.3Data Transfer and Frame Format                            | 206 |

|    | 19.4Multi-master Bus Systems, Arbitration and Synchronization | 209 |

|    | 19.5Overview of the TWI Module                                | 211 |

|    | 19.6TWI Register Description                                  | 213 |

|    | 19.7Using the TWI                                             | 217 |

|    | 19.8Transmission Modes                                        | 221 |

|    | 19.9Multi-master Systems and Arbitration                      | 234 |

| 20 | Analog Comparator                                             | 235 |

|    | 20.1Analog Comparator Multiplexed Input                       | 237 |

| 21 | Analog-to-Digital Converter                                   | 239 |

|    | 21.1Features                                                  | 239 |

|    | 21.2Starting a Conversion                                     | 241 |

|    | 21.3Prescaling and Conversion Timing                          | 242 |

|    | 21.4Changing Channel or Reference Selection                   | 244 |

|    | 21.5ADC Noise Canceler                                        | 245 |

|    | 21.6ADC Conversion Result                                     | 250 |

| 22 | debugWIRE On-chip Debug System                                | 255 |

|    | 22.1Features                                                  | 255 |

|    | 22.20verview                                                  | 255 |

|    | 22.3Physical Interface                                        | 255 |

|    | 22.4Software Break Points                                     | 256 |

|    | 22.5Limitations of debugWIRE                                  | 256 |