Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168v-10pu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

The various special features of Port D are elaborated in "Alternate Functions of Port D" on page 78.

## 2.3.7 AV<sub>cc</sub>

2.3.9

$AV_{CC}$  is the supply voltage pin for the A/D Converter, PC3..0, and ADC7..6. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. Note that PC6..4 use digital supply voltage,  $V_{CC}$ .

#### 2.3.8 AREF AREF is the analog reference pin for the A/D Converter.

# ADC7..6 (TQFP and QFN/MLF Package Only)

In the TQFP and QFN/MLF package, ADC7..6 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.

## 3. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

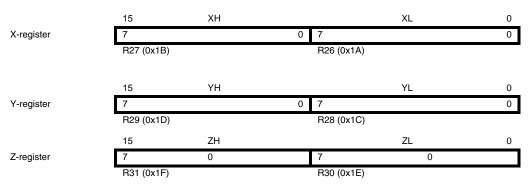

#### 4.5.1 The X-register, Y-register, and Z-register

The registers R26..R31 have some added functions to their general purpose usage. These registers are 16-bit address pointers for indirect addressing of the data space. The three indirect address registers X, Y, and Z are defined as described in Figure 4-3.

Figure 4-3. The X-, Y-, and Z-registers

In the different addressing modes these address registers have functions as fixed displacement, automatic increment, and automatic decrement (see the instruction set reference for details).

#### 4.6 Stack Pointer

The Stack is mainly used for storing temporary data, for storing local variables and for storing return addresses after interrupts and subroutine calls. The Stack Pointer Register always points to the top of the Stack. Note that the Stack is implemented as growing from higher memory locations to lower memory locations. This implies that a Stack PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Interrupt Stacks are located. This Stack space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer must be set to point above 0x0100, preferably RAMEND. The Stack Pointer is decremented by one when data is pushed onto the Stack with the PUSH instruction, and it is decremented by two when the return address is pushed onto the Stack with subroutine call or interrupt. The Stack Pointer is incremented by one when data is popped from the Stack with the POP instruction, and it is incremented by two when data is popped from the Stack with return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is implementation dependent. Note that the data space in some implementations of the AVR architecture is so small that only SPL is needed. In this case, the SPH Register will not be present.

| Bit           | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

|               | SP15   | SP14   | SP13   | SP12   | SP11   | SP10   | SP9    | SP8    | SPH |

|               | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

|               | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |     |

| Read/Write    | R/W    |     |

|               | R/W    |     |

| Initial Value | RAMEND |     |

|               | RAMEND |     |

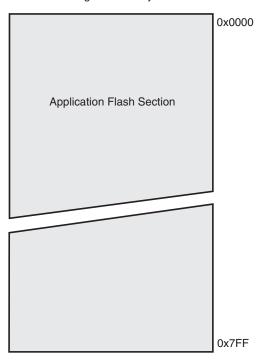

#### Figure 5-1. Program Memory Map, ATmega48

Program Memory

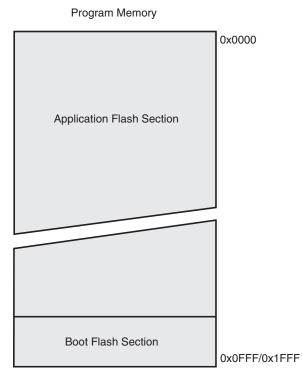

### Figure 5-2. Program Memory Map, ATmega88 and ATmega168

#### 5.3.2 The EEPROM Address Register – EEARH and EEARL

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | _     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

|               | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Х     |       |

|               | Х     | х     | х     | х     | х     | х     | х     | Х     |       |

#### • Bits 15..9 – Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### • Bits 8..0 – EEAR8..0: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL specify the EEPROM address in the 256/512/512 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 255/511/511. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

EEAR8 is an unused bit in ATmega48 and must always be written to zero.

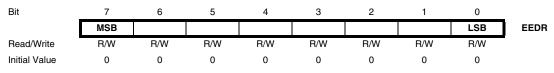

#### 5.3.3 The EEPROM Data Register – EEDR

#### Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR Register contains the data to be written to the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

#### 5.3.4 The EEPROM Control Register – EECR

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|---------------|---|---|-------|-------|-------|-------|------|------|------|

|               | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write    | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | •    |

| Initial Value | 0 | 0 | х     | х     | 0     | 0     | х    | 0    |      |

#### • Bits 7..6 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

### • Bits 5, 4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits

The EEPROM Programming mode bit setting defines which programming action that will be triggered when writing EEPE. It is possible to program data in one atomic operation (erase the old value and program the new value) or to split the Erase and Write operations in two different operations. The Programming times for the different modes are shown in Table 5-1. While EEPE

# 7. Power Management and Sleep Modes

Sleep modes enable the application to shut down unused modules in the MCU, thereby saving power. The AVR provides various sleep modes allowing the user to tailor the power consumption to the application's requirements.

To enter any of the five sleep modes, the SE bit in SMCR must be written to logic one and a SLEEP instruction must be executed. The SM2, SM1, and SM0 bits in the SMCR Register select which sleep mode (Idle, ADC Noise Reduction, Power-down, Power-save, or Standby) will be activated by the SLEEP instruction. See Table 7-1 for a summary. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles in addition to the start-up time, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the Register File and SRAM are unaltered when the device wakes up from sleep. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset Vector.

Figure 6-1 on page 25 presents the different clock systems in the ATmega48/88/168, and their distribution. The figure is helpful in selecting an appropriate sleep mode.

#### 7.0.1 Sleep Mode Control Register – SMCR

The Sleep Mode Control Register contains control bits for power management.

| Bit           | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   | _    |

|---------------|---|---|---|---|-----|-----|-----|-----|------|

|               | - | - | - | - | SM2 | SM1 | SM0 | SE  | SMCR |

| Read/Write    | R | R | R | R | R/W | R/W | R/W | R/W | -    |

| Initial Value | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |      |

#### • Bits 7..4 Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bits 3..1 – SM2..0: Sleep Mode Select Bits 2, 1, and 0

These bits select between the five available sleep modes as shown in Table 7-1.

| SM2 | SM1 | SM0 | Sleep Mode             |

|-----|-----|-----|------------------------|

| 0   | 0   | 0   | Idle                   |

| 0   | 0   | 1   | ADC Noise Reduction    |

| 0   | 1   | 0   | Power-down             |

| 0   | 1   | 1   | Power-save             |

| 1   | 0   | 0   | Reserved               |

| 1   | 0   | 1   | Reserved               |

| 1   | 1   | 0   | Standby <sup>(1)</sup> |

| 1   | 1   | 1   | Reserved               |

Table 7-1.

Sleep Mode Select

Note: 1. Standby mode is only recommended for use with external crystals or resonators.

#### • Bit 0 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmer's

ATmega48/88/168

| /            |                                          |                                           |

|--------------|------------------------------------------|-------------------------------------------|

| 0x0033RESET: | ldi                                      | r16, high(RAMEND); Main program start     |

| 0x0034       | out                                      | SPH,r16 ; Set Stack Pointer to top of RAM |

| 0x0035       | ldi                                      | r16, low(RAMEND)                          |

| 0x0036       | out                                      | SPL,r16                                   |

| 0x0037       | sei                                      | ; Enable interrupts                       |

| 0x0038       | <instr< th=""><th>&gt; xxx</th></instr<> | > xxx                                     |

|              |                                          |                                           |

. . . ... ...

When the BOOTRST Fuse is unprogrammed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address          | Labels | Code                                                       |                 | С  | Comments                           |

|------------------|--------|------------------------------------------------------------|-----------------|----|------------------------------------|

| 0x0000           | RESET: | ldi                                                        | r16,high(RAMENI | )) | ; Main program start               |

| 0x0001           |        | out                                                        | SPH,r16         | ;  | Set Stack Pointer to top of RAM    |

| 0x0002           |        | ldi                                                        | r16,low(RAMEND) | )  |                                    |

| 0x0003<br>0x0004 |        | out<br>sei                                                 | SPL,r16         | ;  | Enable interrupts                  |

| 0x0005           |        | <instr< th=""><th>&gt; xxx</th><th></th><th></th></instr<> | > xxx           |    |                                    |

| ;                |        |                                                            |                 |    |                                    |

| .org 0xC         | 02     |                                                            |                 |    |                                    |

| 0x1C02           |        | jmp                                                        | EXT_INT0        | ;  | IRQ0 Handler                       |

| 0x1C04           |        | jmp                                                        | EXT_INT1        | ;  | IRQ1 Handler                       |

|                  |        |                                                            |                 | ;  |                                    |

| 0x1C32           |        | jmp                                                        | SPM_RDY         | ;  | Store Program Memory Ready Handler |

When the BOOTRST Fuse is programmed and the Boot section size set to 2K bytes, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address Labels | Code                                                       | Com           | nen | ts                                 |

|----------------|------------------------------------------------------------|---------------|-----|------------------------------------|

| .org 0x0002    |                                                            |               |     |                                    |

| 0x0002         | jmp                                                        | EXT_INT0      | ;   | IRQ0 Handler                       |

| 0x0004         | jmp                                                        | EXT_INT1      | ;   | IRQ1 Handler                       |

|                |                                                            | •••           | ;   |                                    |

| 0x0032         | jmp                                                        | SPM_RDY       | ;   | Store Program Memory Ready Handler |

| ;              |                                                            |               |     |                                    |

| .org 0x1C00    |                                                            |               |     |                                    |

| 0x1C00 RESET:  | ldi                                                        | r16,high(RAME | ND) | ; Main program start               |

| 0x1C01         | out                                                        | SPH,r16       | ;   | Set Stack Pointer to top of RAM    |

| 0x1C02         | ldi                                                        | r16,low(RAMEN | D)  |                                    |

| 0x1C03         | out                                                        | SPL,r16       |     |                                    |

| 0x1C04         | sei                                                        |               | ;   | Enable interrupts                  |

| 0x1C05         | <instr< td=""><td>&gt; xxx</td><td></td><td></td></instr<> | > xxx         |     |                                    |

When the BOOTRST Fuse is programmed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

#### 11.1.1 External Interrupt Control Register A – EICRA

The External Interrupt Control Register A contains control bits for interrupt sense control.

| Bit           | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     | _     |

|---------------|---|---|---|---|-------|-------|-------|-------|-------|

|               | - | - | - | - | ISC11 | ISC10 | ISC01 | ISC00 | EICRA |

| Read/Write    | R | R | R | R | R/W   | R/W   | R/W   | R/W   | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0     | 0     | 0     | 0     |       |

#### • Bit 7..4 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 11-1. The value on the INT1 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

Table 11-1.

Interrupt 1 Sense Control

| ISC11 | ISC10 | Description                                                |

|-------|-------|------------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT1 generates an interrupt request. |

| 1     | 0     | The falling edge of INT1 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.    |

#### • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 11-2. The value on the INT0 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

|       | •     |                                                            |

|-------|-------|------------------------------------------------------------|

| ISC01 | ISC00 | Description                                                |

| 0     | 0     | The low level of INT0 generates an interrupt request.      |

| 0     | 1     | Any logical change on INT0 generates an interrupt request. |

| 1     | 0     | The falling edge of INT0 generates an interrupt request.   |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.    |

Table 11-2.

Interrupt 0 Sense Control

#### • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set, the Timer/Counter0 Overflow interrupt is executed.

The setting of this flag is dependent of the WGM02:0 bit setting. Refer to Table 12-8, "Waveform Generation Mode Bit Description" on page 101.

# 13. 16-bit Timer/Counter1 with PWM

The 16-bit Timer/Counter unit allows accurate program execution timing (event management), wave generation, and signal timing measurement. The main features are:

- True 16-bit Design (i.e., Allows 16-bit PWM)

- Two independent Output Compare Units

- Double Buffered Output Compare Registers

- One Input Capture Unit

- Input Capture Noise Canceler

- Clear Timer on Compare Match (Auto Reload)

- Glitch-free, Phase Correct Pulse Width Modulator (PWM)

- Variable PWM Period

- Frequency Generator

- External Event Counter

- Four independent interrupt Sources (TOV1, OCF1A, OCF1B, and ICF1)

#### 13.1 Overview

Most register and bit references in this section are written in general form. A lower case "n" replaces the Timer/Counter number, and a lower case "x" replaces the Output Compare unit channel. However, when using the register or bit defines in a program, the precise form must be used, i.e., TCNT1 for accessing Timer/Counter1 counter value and so on.

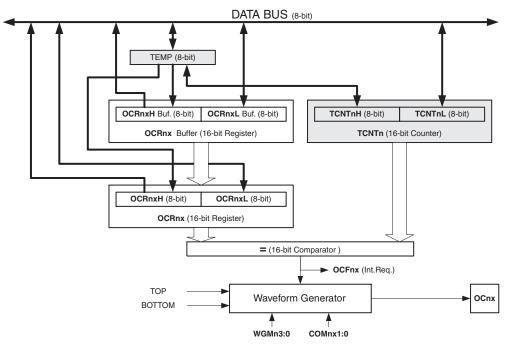

A simplified block diagram of the 16-bit Timer/Counter is shown in Figure 13-1. For the actual placement of I/O pins, refer to "Pinout ATmega48/88/168" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "16-bit Timer/Counter Register Description" on page 128.

The PRTIM1 bit in "Power Reduction Register - PRR" on page 40 must be written to zero to enable Timer/Counter1 module.

#### Assembly Code Example<sup>(1)</sup>

| TIM16_ReadTCNT1:                  |

|-----------------------------------|

| ; Save global interrupt flag      |

| in r18,SREG                       |

| ; Disable interrupts              |

| cli                               |

| ; Read TCNT <b>1</b> into r17:r16 |

| in r16,TCNT1L                     |

| in r17, TCNT1H                    |

| ; Restore global interrupt flag   |

| out SREG, r18                     |

| ret                               |

C Code Example<sup>(1)</sup>

```

unsigned int TIM16_ReadTCNT1( void )

{

unsigned char sreg;

unsigned int i;

/* Save global interrupt flag */

sreg = SREG;

/* Disable interrupts */

_CLI();

/* Read TCNT1 into i */

i = TCNT1;

/* Restore global interrupt flag */

SREG = sreg;

return i;

}

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNT1 value in the r17:r16 register pair.

The following code examples show how to do an atomic write of the TCNT1 Register contents. Writing any of the OCR1A/B or ICR1 Registers can be done by using the same principle.

cleared by software (writing a logical one to the I/O bit location). For measuring frequency only, the clearing of the ICF1 Flag is not required (if an interrupt handler is used).

### 13.6 Output Compare Units

The 16-bit comparator continuously compares TCNT1 with the *Output Compare Register* (OCR1x). If TCNT equals OCR1x the comparator signals a match. A match will set the *Output Compare Flag* (OCF1x) at the next timer clock cycle. If enabled (OCIE1x = 1), the Output Compare Flag generates an Output Compare interrupt. The OCF1x Flag is automatically cleared when the interrupt is executed. Alternatively the OCF1x Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the *Waveform Generation mode* (WGM13:0) bits and *Compare Output mode* (COM1x1:0) bits. The TOP and BOTTOM signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation (See Section "13.8" on page 118.)

A special feature of Output Compare unit A allows it to define the Timer/Counter TOP value (i.e., counter resolution). In addition to the counter resolution, the TOP value defines the period time for waveforms generated by the Waveform Generator.

Figure 13-4 shows a block diagram of the Output Compare unit. The small "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B). The elements of the block diagram that are not directly a part of the Output Compare unit are gray shaded.

Figure 13-4. Output Compare Unit, Block Diagram

The OCR1x Register is double buffered when using any of the twelve *Pulse Width Modulation* (PWM) modes. For the Normal and *Clear Timer on Compare* (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR1x Compare Register to either TOP or BOTTOM of the counting sequence. The synchronization

# ATmega48/88/168

to be written anytime. When the OCR1A I/O location is written the value written will be put into the OCR1A Buffer Register. The OCR1A Compare Register will then be updated with the value in the Buffer Register at the next timer clock cycle the TCNT1 matches TOP. The update is done at the same timer clock cycle as the TCNT1 is cleared and the TOV1 Flag is set.

Using the ICR1 Register for defining TOP works well when using fixed TOP values. By using ICR1, the OCR1A Register is free to be used for generating a PWM output on OC1A. However, if the base PWM frequency is actively changed (by changing the TOP value), using the OCR1A as TOP is clearly a better choice due to its double buffer feature.

In fast PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to three (see Table on page 128). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1, and clearing (or setting) the OC1x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{clk\_I/O}}{N \cdot (1 + TOP)}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x Register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR1x is set equal to BOTTOM (0x0000) the output will be a narrow spike for each TOP+1 timer clock cycle. Setting the OCR1x equal to TOP will result in a constant high or low output (depending on the polarity of the output set by the COM1x1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC1A to toggle its logical level on each compare match (COM1A1:0 = 1). This applies only if OCR1A is used to define the TOP value (WGM13:0 = 15). The waveform generated will have a maximum frequency of  $f_{OC1A} = f_{clk\_l/O}/2$  when OCR1A is set to zero (0x0000). This feature is similar to the OC1A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

#### 13.8.4 Phase Correct PWM Mode

The *phase correct Pulse Width Modulation* or phase correct PWM mode (WGM13:0 = 1, 2, 3, 10, or 11) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is, like the phase and frequency correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared on the compare match between TCNT1 and OCR1x while upcounting, and set on the compare match while downcounting. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The PWM resolution for the phase correct PWM mode can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to

# 14. Timer/Counter0 and Timer/Counter1 Prescalers

"8-bit Timer/Counter0 with PWM" on page 88 and "16-bit Timer/Counter1 with PWM" on page 106 share the same prescaler module, but the Timer/Counters can have different prescaler settings. The description below applies to both Timer/Counter1 and Timer/Counter0.

#### 14.0.1 Internal Clock Source

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system clock frequency ( $f_{CLK_{-}I/O}$ ). Alternatively, one of four taps from the prescaler can be used as a clock source. The prescaled clock has a frequency of either  $f_{CLK_{-}I/O}/8$ ,  $f_{CLK_{-}I/O}/64$ ,  $f_{CLK_{-}I/O}/256$ , or  $f_{CLK_{-}I/O}/1024$ .

#### 14.0.2 Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of the Timer/Counter, and it is shared by Timer/Counter1 and Timer/Counter0. Since the prescaler is not affected by the Timer/Counter's clock select, the state of the prescaler will have implications for situations where a prescaled clock is used. One example of prescaling artifacts occurs when the timer is enabled and clocked by the prescaler (6 > CSn2:0 > 1). The number of system clock cycles from when the timer is enabled to the first count occurs can be from 1 to N+1 system clock cycles, where N equals the prescaler divisor (8, 64, 256, or 1024).

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program execution. However, care must be taken if the other Timer/Counter that shares the same prescaler also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is connected to.

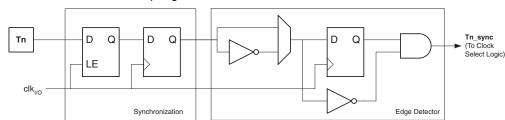

#### 14.0.3 External Clock Source

An external clock source applied to the T1/T0 pin can be used as Timer/Counter clock  $(clk_{T1}/clk_{T0})$ . The T1/T0 pin is sampled once every system clock cycle by the pin synchronization logic. The synchronized (sampled) signal is then passed through the edge detector. Figure 14-1 shows a functional equivalent block diagram of the T1/T0 synchronization and edge detector logic. The registers are clocked at the positive edge of the internal system clock ( $clk_{I/O}$ ). The latch is transparent in the high period of the internal system clock.

The edge detector generates one  $clk_{T1}/clk_{T0}$  pulse for each positive (CSn2:0 = 7) or negative (CSn2:0 = 6) edge it detects.

Figure 14-1. T1/T0 Pin Sampling

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles from an edge has been applied to the T1/T0 pin to the counter is updated.

nine data bits, then the ninth bit (RXB8n) is used for identifying address and data frames. When the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the frame type bit is zero the frame is a data frame.

The Multi-processor Communication mode enables several slave MCUs to receive data from a master MCU. This is done by first decoding an address frame to find out which MCU has been addressed. If a particular slave MCU has been addressed, it will receive the following data frames as normal, while the other slave MCUs will ignore the received frames until another address frame is received.

#### 17.8.1 Using MPCMn

For an MCU to act as a master MCU, it can use a 9-bit character frame format (UCSZn = 7). The ninth bit (TXB8n) must be set when an address frame (TXB8n = 1) or cleared when a data frame (TXB = 0) is being transmitted. The slave MCUs must in this case be set to use a 9-bit character frame format.

The following procedure should be used to exchange data in Multi-processor Communication mode:

- 1. All Slave MCUs are in Multi-processor Communication mode (MPCMn in UCSRnA is set).

- 2. The Master MCU sends an address frame, and all slaves receive and read this frame. In the Slave MCUs, the RXCn Flag in UCSRnA will be set as normal.

- Each Slave MCU reads the UDRn Register and determines if it has been selected. If so, it clears the MPCMn bit in UCSRnA, otherwise it waits for the next address byte and keeps the MPCMn setting.

- 4. The addressed MCU will receive all data frames until a new address frame is received. The other Slave MCUs, which still have the MPCMn bit set, will ignore the data frames.

- 5. When the last data frame is received by the addressed MCU, the addressed MCU sets the MPCMn bit and waits for a new address frame from master. The process then repeats from 2.

Using any of the 5- to 8-bit character frame formats is possible, but impractical since the Receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult since the Transmitter and Receiver uses the same character size setting. If 5- to 8-bit character frames are used, the Transmitter must be set to use two stop bit (USBSn = 1) since the first stop bit is used for indicating the frame type.

Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCMn bit. The MPCMn bit shares the same I/O location as the TXCn Flag and this might accidentally be cleared when using SBI or CBI instructions.

#### • Bit 0 - UCPOLn: Clock Polarity

The UCPOLn bit sets the polarity of the XCKn clock. The combination of the UCPOLn and UCPHAn bit settings determine the timing of the data transfer. Refer to the SPI Data Modes and Timing section page 4 for details.

#### 18.6.5 USART MSPIM Baud Rate Registers - UBRRnL and UBRRnH

The function and bit description of the baud rate registers in MSPI mode is identical to normal USART operation. See "USART Baud Rate Registers – UBRRnL and UBRRnH" on page 191.

#### 18.7 AVR USART MSPIM vs. AVR SPI

The USART in MSPIM mode is fully compatible with the AVR SPI regarding:

- Master mode timing diagram.

- The UCPOLn bit functionality is identical to the SPI CPOL bit.

- The UCPHAn bit functionality is identical to the SPI CPHA bit.

- The UDORDn bit functionality is identical to the SPI DORD bit.

However, since the USART in MSPIM mode reuses the USART resources, the use of the USART in MSPIM mode is somewhat different compared to the SPI. In addition to differences of the control register bits, and that only master operation is supported by the USART in MSPIM mode, the following features differ between the two modules:

- The USART in MSPIM mode includes (double) buffering of the transmitter. The SPI has no buffer.

- The USART in MSPIM mode receiver includes an additional buffer level.

- The SPI WCOL (Write Collision) bit is not included in USART in MSPIM mode.

- The SPI double speed mode (SPI2X) bit is not included. However, the same effect is achieved by setting UBRRn accordingly.

- Interrupt timing is not compatible.

- Pin control differs due to the master only operation of the USART in MSPIM mode.

A comparison of the USART in MSPIM mode and the SPI pins is shown in Table 18-4 on page 204.

| USART_MSPIM | SPI       | Comment                         |

|-------------|-----------|---------------------------------|

| TxDn        | MOSI      | Master Out only                 |

| RxDn        | MISO      | Master In only                  |

| XCKn        | SCK       | (Functionally identical)        |

| (N/A)       | <u>55</u> | Not supported by USART in MSPIM |

**Table 18-4.**Comparison of USART in MSPIM mode and SPI pins.

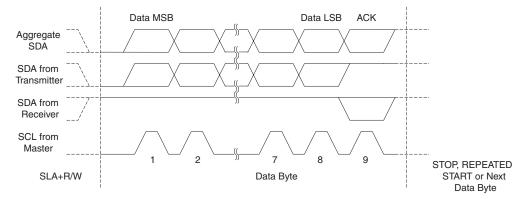

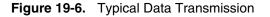

#### 19.3.4 Data Packet Format

All data packets transmitted on the TWI bus are nine bits long, consisting of one data byte and an acknowledge bit. During a data transfer, the Master generates the clock and the START and STOP conditions, while the Receiver is responsible for acknowledging the reception. An Acknowledge (ACK) is signalled by the Receiver pulling the SDA line low during the ninth SCL cycle. If the Receiver leaves the SDA line high, a NACK is signalled. When the Receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the Transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first.

#### Figure 19-5. Data Packet Format

#### 19.3.5 Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the Wired-ANDing of the SCL line can be used to implement handshaking between the Master and the Slave. The Slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the Master is too fast for the Slave, or the Slave needs extra time for processing between the data transmissions. The Slave extending the SCL low period will not affect the SCL high period, which is determined by the Master. As a consequence, the Slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

Figure 19-6 shows a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

;-the routine writes one page of data from RAM to Flash ; the first data location in RAM is pointed to by the Y pointer ; the first data location in Flash is pointed to by the Z-pointer ;-error handling is not included ;-the routine must be placed inside the Boot space ; (at least the Do\_spm sub routine). Only code inside NRWW section can ; be read during Self-Programming (Page Erase and Page Write). ;-registers used: r0, r1, temp1 (r16), temp2 (r17), looplo (r24), ; loophi (r25), spmcrval (r20) ; storing and restoring of registers is not included in the routine ; register usage can be optimized at the expense of code size ;-It is assumed that either the interrupt table is moved to the Boot ; loader section or that the interrupts are disabled. .equ PAGESIZEB = PAGESIZE\*2 ; PAGESIZEB is page size in BYTES, not words .org SMALLBOOTSTART Write\_page: ; Page Erase ldi spmcrval, (1<<PGERS) | (1<<SELFPRGEN)</pre> rcallDo spm ; re-enable the RWW section ldi spmcrval, (1<<RWWSRE) | (1<<SELFPRGEN)</pre> rcallDo\_spm ; transfer data from RAM to Flash page buffer ldi looplo, low(PAGESIZEB) ; init loop variable ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256 Wrloop: ld r0, Y+ ld r1, Y+ ldi spmcrval, (1<<SELFPRGEN) rcallDo\_spm adiw ZH:ZL, 2 sbiw loophi:looplo, 2 ;use subi for PAGESIZEB<=256 brne Wrloop ; execute Page Write subi ZL, low(PAGESIZEB) ;restore pointer ;not required for PAGESIZEB<=256 sbci ZH, high(PAGESIZEB) ldi spmcrval, (1<<PGWRT) | (1<<SELFPRGEN)</pre> rcallDo\_spm ; re-enable the RWW section ldi spmcrval, (1<<RWWSRE) | (1<<SELFPRGEN)</pre> rcallDo\_spm ; read back and check, optional ldi looplo, low(PAGESIZEB) ;init loop variable ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256 subi YL, low(PAGESIZEB) ;restore pointer sbci YH, high(PAGESIZEB) Rdloop: lpm r0, Z+ ld r1, Y+ cpse r0, r1 rjmp Error ;use subi for PAGESIZEB<=256 sbiw loophi:looplo, 1 brne Rdloop

shown below. Refer to Table 25-6 on page 282 for detailed description and mapping of the Fuse High byte.

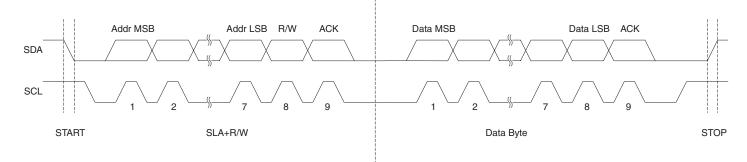

Bit 7 6 5 3 2 0 4 1 Rd FHB7 FHB6 FHB5 FHB4 FHB3 FHB2 FHB1 FHB0

When reading the Extended Fuse byte, load 0x0002 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Extended Fuse byte (EFB) will be loaded in the destination register as shown below. Refer to Table 25-4 on page 281 for detailed description and mapping of the Extended Fuse byte.

Fuse and Lock bits that are programmed, will be read as zero. Fuse and Lock bits that are unprogrammed, will be read as one.

#### 24.7.10 Preventing Flash Corruption

During periods of low  $V_{CC}$ , the Flash program can be corrupted because the supply voltage is too low for the CPU and the Flash to operate properly. These issues are the same as for board level systems using the Flash, and the same design solutions should be applied.

A Flash program corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the Flash requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage for executing instructions is too low.

Flash corruption can easily be avoided by following these design recommendations (one is sufficient):

- 1. If there is no need for a Boot Loader update in the system, program the Boot Loader Lock bits to prevent any Boot Loader software updates.

- 2. Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the SPMCSR Register and thus the Flash from unintentional writes.

#### 24.7.11 Programming Time for Flash when Using SPM

The calibrated RC Oscillator is used to time Flash accesses. Table 24-5 shows the typical programming time for Flash accesses from the CPU.

#### **Table 24-5.**SPM Programming Time

| Symbol                                                           | Min Programming Time | Max Programming Time |

|------------------------------------------------------------------|----------------------|----------------------|

| Flash write (Page Erase, Page Write, and write Lock bits by SPM) | 3.7 ms               | 4.5 ms               |

#### Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |           | Instructio                 |                   |                   |                                                                                                                                          |  |  |

|-------------------------------------------|-----------|----------------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instruction                               | Byte 1    | Byte 1 Byte 2 Byte 3 Byte4 |                   | Byte4             | Operation                                                                                                                                |  |  |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001 | 0000 0000                  | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |  |  |

| Write EEPROM Memory<br>Page (page access) | 1100 0010 | 00xx xx <b>aa</b>          | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |  |  |

| Read Lock bits                            | 0101 1000 | 0000 0000                  | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |  |  |

| Write Lock bits                           | 1010 1100 | 111x xxxx                  | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |  |  |

| Read Signature Byte                       | 0011 0000 | 000x xxxx                  | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |  |  |

| Write Fuse bits                           | 1010 1100 | 1010 0000                  | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |  |  |

| Write Fuse High bits                      | 1010 1100 | 1010 1000                  | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |  |  |

| Write Extended Fuse Bits                  | 1010 1100 | 1010 0100                  | xxxx xxxx         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |  |  |

| Read Fuse bits                            | 0101 0000 | 0000 0000                  | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |  |  |

| Read Fuse High bits                       | 0101 1000 | 0000 1000                  | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |  |  |

| Read Extended Fuse Bits                   | 0101 0000 | 0000 1000                  | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |  |  |

| Read Calibration Byte                     | 0011 1000 | 000x xxxx                  | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |  |  |

| Poll RDY/BSY                              | 1111 0000 | 0000 0000                  | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |  |  |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

#### 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

# 336 ATmega48/88/168

| Address                                                                                                                                                                                                                                                                             | Name                                                                                                                                                                   | Bit 7                                                   | Bit 6                                            | Bit 5                                                           | Bit 4                                                                                                                                           | Bit 3                                                                                                                                                                                                            | Bit 2                                                                                                                                                    | Bit 1                                                            | Bit 0                                                            | Page                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| (0x7D)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        | -                                                                | -                                                                |                                                                                         |

| (0x7C)                                                                                                                                                                                                                                                                              | ADMUX                                                                                                                                                                  | REFS1                                                   | REFS0                                            | ADLAR                                                           | -                                                                                                                                               | MUX3                                                                                                                                                                                                             | MUX2                                                                                                                                                     | MUX1                                                             | MUX0                                                             | 250                                                                                     |

| (0x7B)                                                                                                                                                                                                                                                                              | ADCSRB                                                                                                                                                                 | -                                                       | ACME                                             | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | ADTS2                                                                                                                                                    | ADTS1                                                            | ADTS0                                                            | 253                                                                                     |

| (0x7A)                                                                                                                                                                                                                                                                              | ADCSRA                                                                                                                                                                 | ADEN                                                    | ADSC                                             | ADATE                                                           | ADIF                                                                                                                                            | ADIE                                                                                                                                                                                                             | ADPS2                                                                                                                                                    | ADPS1                                                            | ADPS0                                                            | 251                                                                                     |

| (0x79)                                                                                                                                                                                                                                                                              | ADCH                                                                                                                                                                   |                                                         |                                                  |                                                                 | ADC Data Rec                                                                                                                                    | 0,                                                                                                                                                                                                               |                                                                                                                                                          |                                                                  |                                                                  | 253                                                                                     |

| (0x78)                                                                                                                                                                                                                                                                              | ADCL                                                                                                                                                                   |                                                         |                                                  |                                                                 | ,                                                                                                                                               | ister Low byte                                                                                                                                                                                                   |                                                                                                                                                          |                                                                  |                                                                  | 253                                                                                     |

| (0x77)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        | -                                                                | -                                                                |                                                                                         |

| (0x76)                                                                                                                                                                                                                                                                              | Reserved<br>Reserved                                                                                                                                                   | -                                                       | -                                                |                                                                 | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        |                                                                  | -                                                                |                                                                                         |

| (0x75)<br>(0x74)                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                               | _                                                       | -                                                |                                                                 | -                                                                                                                                               | -                                                                                                                                                                                                                | -                                                                                                                                                        | _                                                                | -                                                                |                                                                                         |

| (0x74)<br>(0x73)                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                               | _                                                       | _                                                |                                                                 | _                                                                                                                                               | _                                                                                                                                                                                                                | _                                                                                                                                                        |                                                                  | _                                                                |                                                                                         |

| (0x73)<br>(0x72)                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                               |                                                         | _                                                |                                                                 | _                                                                                                                                               | _                                                                                                                                                                                                                | _                                                                                                                                                        |                                                                  | _                                                                |                                                                                         |

| (0x71)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | _                                                       | _                                                | _                                                               | _                                                                                                                                               | _                                                                                                                                                                                                                | _                                                                                                                                                        | _                                                                | _                                                                |                                                                                         |

| (0x70)                                                                                                                                                                                                                                                                              | TIMSK2                                                                                                                                                                 | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | OCIE2B                                                                                                                                                   | OCIE2A                                                           | TOIE2                                                            | 154                                                                                     |

| (0x6F)                                                                                                                                                                                                                                                                              | TIMSK1                                                                                                                                                                 | -                                                       | -                                                | ICIE1                                                           | -                                                                                                                                               | -                                                                                                                                                                                                                | OCIE1B                                                                                                                                                   | OCIE1A                                                           | TOIE1                                                            | 133                                                                                     |

| (0x6E)                                                                                                                                                                                                                                                                              | TIMSK0                                                                                                                                                                 | -                                                       | -                                                | -                                                               | -                                                                                                                                               | -                                                                                                                                                                                                                | OCIE0B                                                                                                                                                   | OCIE0A                                                           | TOIE0                                                            | 104                                                                                     |

| (0x6D)                                                                                                                                                                                                                                                                              | PCMSK2                                                                                                                                                                 | PCINT23                                                 | PCINT22                                          | PCINT21                                                         | PCINT20                                                                                                                                         | PCINT19                                                                                                                                                                                                          | PCINT18                                                                                                                                                  | PCINT17                                                          | PCINT16                                                          | 87                                                                                      |

| (0x6C)                                                                                                                                                                                                                                                                              | PCMSK1                                                                                                                                                                 | -                                                       | PCINT14                                          | PCINT13                                                         | PCINT12                                                                                                                                         | PCINT11                                                                                                                                                                                                          | PCINT10                                                                                                                                                  | PCINT9                                                           | PCINT8                                                           | 87                                                                                      |

| (0x6B)                                                                                                                                                                                                                                                                              | PCMSK0                                                                                                                                                                 | PCINT7                                                  | PCINT6                                           | PCINT5                                                          | PCINT4                                                                                                                                          | PCINT3                                                                                                                                                                                                           | PCINT2                                                                                                                                                   | PCINT1                                                           | PCINT0                                                           | 87                                                                                      |

| (0x6A)                                                                                                                                                                                                                                                                              | Reserved                                                                                                                                                               | -                                                       | -                                                | -                                                               | _                                                                                                                                               | _                                                                                                                                                                                                                | _                                                                                                                                                        | -                                                                | -                                                                |                                                                                         |