# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48-20aj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8. System Control and Reset

#### 8.0.1 Resetting the AVR

During reset, all I/O Registers are set to their initial values, and the program starts execution from the Reset Vector. For the ATmega168, the instruction placed at the Reset Vector must be a JMP – Absolute Jump – instruction to the reset handling routine. For the ATmega48 and ATmega88, the instruction placed at the Reset Vector must be an RJMP – Relative Jump – instruction to the reset handling routine. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa (ATmega88/168 only). The circuit diagram in Figure 8-1 shows the reset logic. Table 8-1 defines the electrical parameters of the reset circuitry.

The I/O ports of the AVR are immediately reset to their initial state when a reset source goes active. This does not require any clock source to be running.

After all reset sources have gone inactive, a delay counter is invoked, stretching the internal reset. This allows the power to reach a stable level before normal operation starts. The time-out period of the delay counter is defined by the user through the SUT and CKSEL Fuses. The different selections for the delay period are presented in "Clock Sources" on page 26.

#### 8.0.2 Reset Sources

The ATmega48/88/168 has four sources of reset:

- Power-on Reset. The MCU is reset when the supply voltage is below the Power-on Reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for longer than the minimum pulse length.

- Watchdog System Reset. The MCU is reset when the Watchdog Timer period expires and the Watchdog System Reset mode is enabled.

- Brown-out Reset. The MCU is reset when the supply voltage  $V_{CC}$  is below the Brown-out Reset threshold ( $V_{BOT}$ ) and the Brown-out Detector is enabled.

ATmega48/88/168

| /            |                                          |                                           |

|--------------|------------------------------------------|-------------------------------------------|

| 0x0033RESET: | ldi                                      | r16, high(RAMEND); Main program start     |

| 0x0034       | out                                      | SPH,r16 ; Set Stack Pointer to top of RAM |

| 0x0035       | ldi                                      | r16, low(RAMEND)                          |

| 0x0036       | out                                      | SPL,r16                                   |

| 0x0037       | sei                                      | ; Enable interrupts                       |

| 0x0038       | <instr< th=""><th>&gt; xxx</th></instr<> | > xxx                                     |

|              |                                          |                                           |

. . . ... ...

When the BOOTRST Fuse is unprogrammed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address          | Labels | Code                                                       |                 | С  | Comments                           |

|------------------|--------|------------------------------------------------------------|-----------------|----|------------------------------------|

| 0x0000           | RESET: | ldi                                                        | r16,high(RAMENI | )) | ; Main program start               |

| 0x0001           |        | out                                                        | SPH,r16         | ;  | Set Stack Pointer to top of RAM    |

| 0x0002           |        | ldi                                                        | r16,low(RAMEND) | )  |                                    |

| 0x0003<br>0x0004 |        | out<br>sei                                                 | SPL,r16         | ;  | Enable interrupts                  |

| 0x0005           |        | <instr< th=""><th>&gt; xxx</th><th></th><th></th></instr<> | > xxx           |    |                                    |

| ;                |        |                                                            |                 |    |                                    |

| .org 0xC         | 02     |                                                            |                 |    |                                    |

| 0x1C02           |        | jmp                                                        | EXT_INT0        | ;  | IRQ0 Handler                       |

| 0x1C04           |        | jmp                                                        | EXT_INT1        | ;  | IRQ1 Handler                       |

|                  |        |                                                            |                 | ;  |                                    |

| 0x1C32           |        | jmp                                                        | SPM_RDY         | ;  | Store Program Memory Ready Handler |

When the BOOTRST Fuse is programmed and the Boot section size set to 2K bytes, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address Labels | Code                                                       | Com           | nen | ts                                 |

|----------------|------------------------------------------------------------|---------------|-----|------------------------------------|

| .org 0x0002    |                                                            |               |     |                                    |

| 0x0002         | jmp                                                        | EXT_INT0      | ;   | IRQ0 Handler                       |

| 0x0004         | jmp                                                        | EXT_INT1      | ;   | IRQ1 Handler                       |

|                |                                                            | •••           | ;   |                                    |

| 0x0032         | jmp                                                        | SPM_RDY       | ;   | Store Program Memory Ready Handler |

| ;              |                                                            |               |     |                                    |

| .org 0x1C00    |                                                            |               |     |                                    |

| 0x1C00 RESET:  | ldi                                                        | r16,high(RAME | ND) | ; Main program start               |

| 0x1C01         | out                                                        | SPH,r16       | ;   | Set Stack Pointer to top of RAM    |

| 0x1C02         | ldi                                                        | r16,low(RAMEN | D)  |                                    |

| 0x1C03         | out                                                        | SPL,r16       |     |                                    |

| 0x1C04         | sei                                                        |               | ;   | Enable interrupts                  |

| 0x1C05         | <instr< td=""><td>&gt; xxx</td><td></td><td></td></instr<> | > xxx         |     |                                    |

When the BOOTRST Fuse is programmed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

#### • Bit 0 – IVCE: Interrupt Vector Change Enable

The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts, as explained in the IVSEL description above. See Code Example below.

```

Assembly Code Example

```

```

Move_interrupts:

; Enable change of Interrupt Vectors

ldi r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ldi r16, (1<<IVSEL)

out MCUCR, r16

ret

```

C Code Example

```

void Move_interrupts(void)

```

```

{

/* Enable change of Interrupt Vectors */

MCUCR = (1<<IVCE);

/* Move interrupts to Boot Flash section */

MCUCR = (1<<IVSEL);

}</pre>

```

This bit is not available in ATmega48.

#### 10.3.4 Alternate Functions of Port D

The Port D pins with alternate functions are shown in Table 10-9.

| Port Pin | Alternate Function                                                                                                                      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PD7      | AIN1 (Analog Comparator Negative Input)<br>PCINT23 (Pin Change Interrupt 23)                                                            |

| PD6      | AIN0 (Analog Comparator Positive Input)<br>OC0A (Timer/Counter0 Output Compare Match A Output)<br>PCINT22 (Pin Change Interrupt 22)     |

| PD5      | T1 (Timer/Counter 1 External Counter Input)<br>OC0B (Timer/Counter0 Output Compare Match B Output)<br>PCINT21 (Pin Change Interrupt 21) |

| PD4      | XCK (USART External Clock Input/Output)<br>T0 (Timer/Counter 0 External Counter Input)<br>PCINT20 (Pin Change Interrupt 20)             |

| PD3      | INT1 (External Interrupt 1 Input)<br>OC2B (Timer/Counter2 Output Compare Match B Output)<br>PCINT19 (Pin Change Interrupt 19)           |

| PD2      | INT0 (External Interrupt 0 Input)<br>PCINT18 (Pin Change Interrupt 18)                                                                  |

| PD1      | TXD (USART Output Pin)<br>PCINT17 (Pin Change Interrupt 17)                                                                             |

| PD0      | RXD (USART Input Pin)<br>PCINT16 (Pin Change Interrupt 16)                                                                              |

The alternate pin configuration is as follows:

#### • AIN1/OC2B/PCINT23 – Port D, Bit 7

AIN1, Analog Comparator Negative Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

PCINT23: Pin Change Interrupt source 23. The PD7 pin can serve as an external interrupt source.

#### AIN0/OC0A/PCINT22 – Port D, Bit 6

AIN0, Analog Comparator Positive Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

OC0A, Output Compare Match output: The PD6 pin can serve as an external output for the Timer/Counter0 Compare Match A. The PD6 pin has to be configured as an output (DDD6 set (one)) to serve this function. The OC0A pin is also the output pin for the PWM mode timer function.

PCINT22: Pin Change Interrupt source 22. The PD6 pin can serve as an external interrupt source.

# 12. 8-bit Timer/Counter0 with PWM

Timer/Counter0 is a general purpose 8-bit Timer/Counter module, with two independent Output Compare Units, and with PWM support. It allows accurate program execution timing (event management) and wave generation. The main features are:

- Two Independent Output Compare Units

- Double Buffered Output Compare Registers

- Clear Timer on Compare Match (Auto Reload)

- Glitch Free, Phase Correct Pulse Width Modulator (PWM)

- Variable PWM Period

- Frequency Generator

- Three Independent Interrupt Sources (TOV0, OCF0A, and OCF0B)

## 12.1 Overview

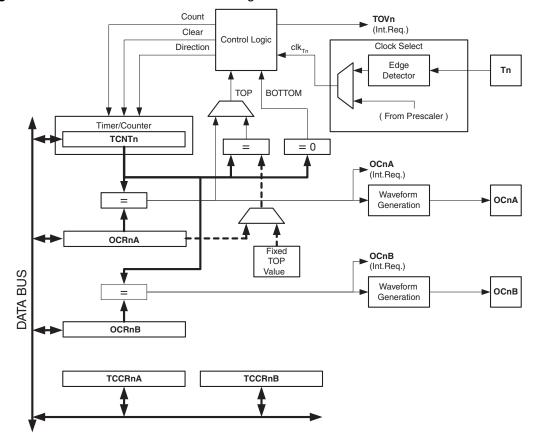

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 12-1. For the actual placement of I/O pins, refer to "Pinout ATmega48/88/168" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "8-bit Timer/Counter Register Description" on page 99.

The PRTIM0 bit in "Power Reduction Register - PRR" on page 40 must be written to zero to enable Timer/Counter0 module.

#### Figure 12-1. 8-bit Timer/Counter Block Diagram

# 15.10 Timer/Counter Prescaler

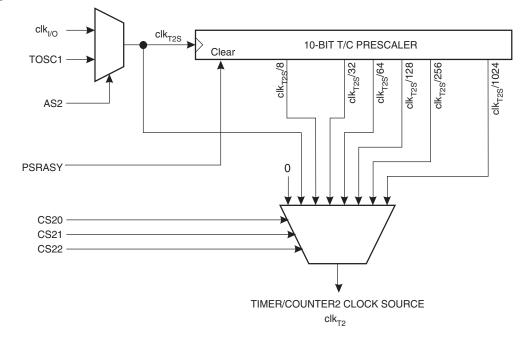

Figure 15-12. Prescaler for Timer/Counter2

The clock source for Timer/Counter2 is named  $clk_{T2S}$ .  $clk_{T2S}$  is by default connected to the main system I/O clock  $clk_{IO}$ . By setting the AS2 bit in ASSR, Timer/Counter2 is asynchronously clocked from the TOSC1 pin. This enables use of Timer/Counter2 as a Real Time Counter (RTC). When AS2 is set, pins TOSC1 and TOSC2 are disconnected from Port C. A crystal can then be connected between the TOSC1 and TOSC2 pins to serve as an independent clock source for Timer/Counter2. The Oscillator is optimized for use with a 32.768 kHz crystal. Applying an external clock source to TOSC1 is not recommended.

For Timer/Counter2, the possible prescaled selections are:  $clk_{T2S}/8$ ,  $clk_{T2S}/32$ ,  $clk_{T2S}/64$ ,  $clk_{T2S}/128$ ,  $clk_{T2S}/256$ , and  $clk_{T2S}/1024$ . Additionally,  $clk_{T2S}$  as well as 0 (stop) may be selected. Setting the PSRASY bit in GTCCR resets the prescaler. This allows the user to operate with a predictable prescaler.

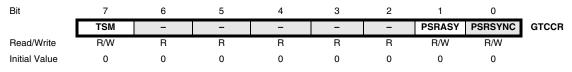

#### 15.10.1 General Timer/Counter Control Register – GTCCR

#### Bit 1 – PSRASY: Prescaler Reset Timer/Counter2

When this bit is one, the Timer/Counter2 prescaler will be reset. This bit is normally cleared immediately by hardware. If the bit is written when Timer/Counter2 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset. The bit will not be cleared by hardware if the TSM bit is set. Refer to the description of the "Bit 7 – TSM: Timer/Counter Synchronization Mode" on page 137 for a description of the Timer/Counter Synchronization mode.

# 17.4 USART Initialization

The USART has to be initialized before any communication can take place. The initialization process normally consists of setting the baud rate, setting frame format and enabling the Transmitter or the Receiver depending on the usage. For interrupt driven USART operation, the Global Interrupt Flag should be cleared (and interrupts globally disabled) when doing the initialization.

Before doing a re-initialization with changed baud rate or frame format, be sure that there are no ongoing transmissions during the period the registers are changed. The TXCn Flag can be used to check that the Transmitter has completed all transfers, and the RXC Flag can be used to check that there are no unread data in the receive buffer. Note that the TXCn Flag must be cleared before each transmission (before UDRn is written) if it is used for this purpose.

The following simple USART initialization code examples show one assembly and one C function that are equal in functionality. The examples assume asynchronous operation using polling (no interrupts enabled) and a fixed frame format. The baud rate is given as a function parameter.

contains data to be transmitted that has not yet been moved into the Shift Register. For compatibility with future devices, always write this bit to zero when writing the UCSRnA Register.

When the Data Register Empty Interrupt Enable (UDRIEn) bit in UCSRnB is written to one, the USART Data Register Empty Interrupt will be executed as long as UDREn is set (provided that global interrupts are enabled). UDREn is cleared by writing UDRn. When interrupt-driven data transmission is used, the Data Register Empty interrupt routine must either write new data to UDRn in order to clear UDREn or disable the Data Register Empty interrupt, otherwise a new interrupt will occur once the interrupt routine terminates.

The Transmit Complete (TXCn) Flag bit is set one when the entire frame in the Transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer. The TXCn Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXCn Flag is useful in half-duplex communication interfaces (like the RS-485 standard), where a transmitting application must enter receive mode and free the communication bus immediately after completing the transmission.

When the Transmit Compete Interrupt Enable (TXCIEn) bit in UCSRnB is set, the USART Transmit Complete Interrupt will be executed when the TXCn Flag becomes set (provided that global interrupts are enabled). When the transmit complete interrupt is used, the interrupt handling routine does not have to clear the TXCn Flag, this is done automatically when the interrupt is executed.

#### 17.5.4 Parity Generator

The Parity Generator calculates the parity bit for the serial frame data. When parity bit is enabled (UPMn1 = 1), the transmitter control logic inserts the parity bit between the last data bit and the first stop bit of the frame that is sent.

#### 17.5.5 Disabling the Transmitter

The disabling of the Transmitter (setting the TXEN to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn pin.

#### 17.6 Data Reception – The USART Receiver

The USART Receiver is enabled by writing the Receive Enable (RXENn) bit in the UCSRnB Register to one. When the Receiver is enabled, the normal pin operation of the RxDn pin is overridden by the USART and given the function as the Receiver's serial input. The baud rate, mode of operation and frame format must be set up once before any serial reception can be done. If synchronous operation is used, the clock on the XCKn pin will be used as transfer clock.

#### 17.6.1 Receiving Frames with 5 to 8 Data Bits

The Receiver starts data reception when it detects a valid start bit. Each bit that follows the start bit will be sampled at the baud rate or XCKn clock, and shifted into the Receive Shift Register until the first stop bit of a frame is received. A second stop bit will be ignored by the Receiver. When the first stop bit is received, i.e., a complete serial frame is present in the Receive Shift Register, the contents of the Shift Register will be moved into the receive buffer. The receive buffer can then be read by reading the UDRn I/O location.

# 18. USART in SPI Mode

The Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART) can be set to a master SPI compliant mode of operation. The Master SPI Mode (MSPIM) has the following features:

- Full Duplex, Three-wire Synchronous Data Transfer

- Master Operation

- Supports all four SPI Modes of Operation (Mode 0, 1, 2, and 3)

- LSB First or MSB First Data Transfer (Configurable Data Order)

- Queued Operation (Double Buffered)

- High Resolution Baud Rate Generator

- High Speed Operation (fXCKmax = fCK/2)

- Flexible Interrupt Generation

## 18.1 Overview

Setting both UMSELn1:0 bits to one enables the USART in MSPIM logic. In this mode of operation the SPI master control logic takes direct control over the USART resources. These resources include the transmitter and receiver shift register and buffers, and the baud rate generator. The parity generator and checker, the data and clock recovery logic, and the RX and TX control logic is disabled. The USART RX and TX control logic is replaced by a common SPI transfer control logic. However, the pin control logic and interrupt generation logic is identical in both modes of operation.

The I/O register locations are the same in both modes. However, some of the functionality of the control registers changes when using MSPIM.

#### 18.2 Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. For USART MSPIM mode of operation only internal clock generation (i.e. master operation) is supported. The Data Direction Register for the XCKn pin (DDR\_XCKn) must therefore be set to one (i.e. as output) for the USART in MSPIM to operate correctly. Preferably the DDR\_XCKn should be set up before the USART in MSPIM is enabled (i.e. TXENn and RXENn bit set to one).

The internal clock generation used in MSPIM mode is identical to the USART synchronous master mode. The baud rate or UBRRn setting can therefore be calculated using the same equations, see Table 18-1:

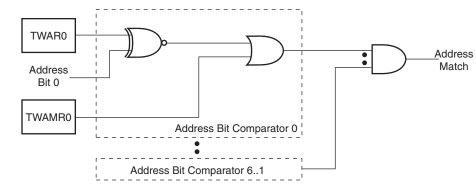

#### Figure 19-10. TWI Address Match Logic, Block Diagram

#### • Bit 0 - Res: Reserved Bit

This bit is an unused bit in the ATmega48/88/168, and will always read as zero.

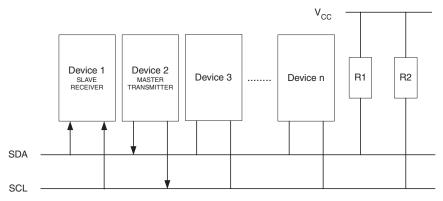

## 19.7 Using the TWI

The AVR TWI is byte-oriented and interrupt based. Interrupts are issued after all bus events, like reception of a byte or transmission of a START condition. Because the TWI is interrupt-based, the application software is free to carry on other operations during a TWI byte transfer. Note that the TWI Interrupt Enable (TWIE) bit in TWCR together with the Global Interrupt Enable bit in SREG allow the application to decide whether or not assertion of the TWINT Flag should generate an interrupt request. If the TWIE bit is cleared, the application must poll the TWINT Flag in order to detect actions on the TWI bus.

When the TWINT Flag is asserted, the TWI has finished an operation and awaits application response. In this case, the TWI Status Register (TWSR) contains a value indicating the current state of the TWI bus. The application software can then decide how the TWI should behave in the next TWI bus cycle by manipulating the TWCR and TWDR Registers.

Figure 19-11 is a simple example of how the application can interface to the TWI hardware. In this example, a Master wishes to transmit a single data byte to a Slave. This description is quite abstract, a more detailed explanation follows later in this section. A simple code example implementing the desired behavior is also presented.

After a repeated START condition (state 0x10) the 2-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control of the bus.

Slave mode entered

becomes free

A START condition will be transmitted when the bus

Х

| Table 19-3.              | Status codes for Maste                                         |                                        |            |           |           |          |                                                                                                          |

|--------------------------|----------------------------------------------------------------|----------------------------------------|------------|-----------|-----------|----------|----------------------------------------------------------------------------------------------------------|

| Status Code              | Otatura of the Quarter Control Dura                            |                                        | tion Softw | vare Resp | onse      |          |                                                                                                          |

| (TWSR)<br>Prescaler Bits | Status of the 2-wire Serial Bus<br>and 2-wire Serial Interface | To/from TWDR                           |            | To        | TWCR      | -        |                                                                                                          |

| are 0                    | Hardware                                                       |                                        | STA        | STO       | TWIN<br>T | TWE<br>A | Next Action Taken by TWI Hardware                                                                        |

| 0x08                     | A START condition has been transmitted                         | Load SLA+W                             | 0          | 0         | 1         | Х        | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                            |

| 0x10                     | A repeated START condition has been transmitted                | Load SLA+W or                          | 0          | 0         | 1         | Х        | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                            |

|                          |                                                                | Load SLA+R                             | 0          | 0         | 1         | Х        | SLA+R will be transmitted;<br>Logic will switch to Master Receiver mode                                  |

| 0x18                     | SLA+W has been transmitted;<br>ACK has been received           | Load data byte or                      | 0          | 0         | 1         | х        | Data byte will be transmitted and ACK or NOT ACK will be received                                        |

|                          |                                                                | No TWDR action or<br>No TWDR action or | 1<br>0     | 0<br>1    | 1<br>1    | X<br>X   | Repeated START will be transmitted<br>STOP condition will be transmitted and<br>TWSTO Flag will be reset |

|                          |                                                                | No TWDR action                         | 1          | 1         | 1         | х        | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset            |

| 0x20                     | SLA+W has been transmitted;<br>NOT ACK has been received       | Load data byte or                      | 0          | 0         | 1         | х        | Data byte will be transmitted and ACK or NOT ACK will be received                                        |

|                          |                                                                | No TWDR action or                      | 1          | 0         | 1         | Х        | Repeated START will be transmitted                                                                       |

|                          |                                                                | No TWDR action or                      | 0          | 1         | 1         | X        | STOP condition will be transmitted and<br>TWSTO Flag will be reset                                       |

|                          |                                                                | No TWDR action                         | 1          | 1         | 1         | Х        | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset            |

| 0x28                     | Data byte has been transmit-<br>ted;                           | Load data byte or                      | 0          | 0         | 1         | Х        | Data byte will be transmitted and ACK or NOT ACK will be received                                        |

|                          | ACK has been received                                          | No TWDR action or                      | 1          | 0         | 1         | Х        | Repeated START will be transmitted                                                                       |

|                          |                                                                | No TWDR action or                      | 0          | 1         | 1         | Х        | STOP condition will be transmitted and<br>TWSTO Flag will be reset                                       |

|                          |                                                                | No TWDR action                         | 1          | 1         | 1         | Х        | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset            |

| 0x30                     | Data byte has been transmit-<br>ted;                           | Load data byte or                      | 0          | 0         | 1         | х        | Data byte will be transmitted and ACK or NOT ACK will be received                                        |

|                          | NOT ACK has been received                                      | No TWDR action or                      | 1          | 0         | 1         | Х        | Repeated START will be transmitted                                                                       |

|                          |                                                                | No TWDR action or                      | 0          | 1         | 1         | Х        | STOP condition will be transmitted and<br>TWSTO Flag will be reset                                       |

|                          |                                                                | No TWDR action                         | 1          | 1         | 1         | Х        | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset            |

| 0x38                     | Arbitration lost in SLA+W or                                   | No TWDR action or                      | 0          | 0         | 1         | Х        | 2-wire Serial Bus will be released and not addressed                                                     |

No TWDR action

Та

0

1

1

data bytes

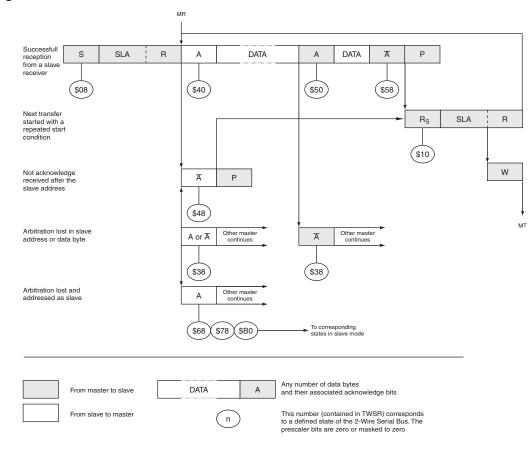

Figure 19-15. Formats and States in the Master Receiver Mode

#### 19.8.3 Slave Receiver Mode

In the Slave Receiver mode, a number of data bytes are received from a Master Transmitter (see Figure 19-16). All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

Figure 19-16. Data transfer in Slave Receiver mode

To initiate the Slave Receiver mode, TWAR and TWCR must be initialized as follows:

| TWAR  | TWA6 | TWA5 | TWA4   | TWA3           | TWA2    | TWA1 | TWA0 | TWGCE |

|-------|------|------|--------|----------------|---------|------|------|-------|

| value |      |      | Device | 's Own Slave A | Address |      |      |       |

20-2. If ACME is cleared or ADEN is set, AIN1 is applied to the negative input to the Analog Comparator.

| ACME | ADEN | MUX20 | Analog Comparator Negative Input |  |  |  |  |  |

|------|------|-------|----------------------------------|--|--|--|--|--|

| 0    | х    | xxx   | AIN1                             |  |  |  |  |  |

| 1    | 1    | xxx   | AIN1                             |  |  |  |  |  |

| 1    | 0    | 000   | ADC0                             |  |  |  |  |  |

| 1    | 0    | 001   | ADC1                             |  |  |  |  |  |

| 1    | 0    | 010   | ADC2                             |  |  |  |  |  |

| 1    | 0    | 011   | ADC3                             |  |  |  |  |  |

| 1    | 0    | 100   | ADC4                             |  |  |  |  |  |

| 1    | 0    | 101   | ADC5                             |  |  |  |  |  |

| 1    | 0    | 110   | ADC6                             |  |  |  |  |  |

| 1    | 0    | 111   | ADC7                             |  |  |  |  |  |

Table 20-2. Analog Comparator Multiplexed Input

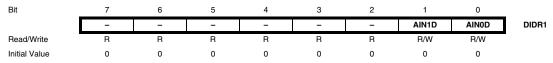

## 20.1.1 Digital Input Disable Register 1 – DIDR1

#### • Bit 7..2 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 1, 0 – AIN1D, AIN0D: AIN1, AIN0 Digital Input Disable

When this bit is written logic one, the digital input buffer on the AIN1/0 pin is disabled. The corresponding PIN Register bit will always read as zero when this bit is set. When an analog signal is applied to the AIN1/0 pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer.

#### 23.1.1 Store Program Memory Control and Status Register – SPMCSR

The Store Program Memory Control and Status Register contains the control bits needed to control the Program memory operations.

| Bit           | 7     | 6     | 5 | 4      | 3      | 2     | 1     | 0         | _      |

|---------------|-------|-------|---|--------|--------|-------|-------|-----------|--------|

|               | SPMIE | RWWSB | - | RWWSRE | BLBSET | PGWRT | PGERS | SELFPRGEN | SPMCSR |

| Read/Write    | R/W   | R     | R | R/W    | R/W    | R/W   | R/W   | R/W       | •      |

| Initial Value | 0     | 0     | 0 | 0      | 0      | 0     | 0     | 0         |        |

#### Bit 7 – SPMIE: SPM Interrupt Enable

When the SPMIE bit is written to one, and the I-bit in the Status Register is set (one), the SPM ready interrupt will be enabled. The SPM ready Interrupt will be executed as long as the SELF-PRGEN bit in the SPMCSR Register is cleared. The interrupt will not be generated during EEPROM write or SPM.

#### • Bit 6 - RWWSB: Read-While-Write Section Busy

This bit is for compatibility with devices supporting Read-While-Write. It will always read as zero in ATmega48.

#### • Bit 5 - Res: Reserved Bit

This bit is a reserved bit in the ATmega48/88/168 and will always read as zero.

#### • Bit 4 – RWWSRE: Read-While-Write Section Read Enable

The functionality of this bit in ATmega48 is a subset of the functionality in ATmega88/168. If the RWWSRE bit is written while filling the temporary page buffer, the temporary page buffer will be cleared and the data will be lost.

#### • Bit 3 – BLBSET: Boot Lock Bit Set

The functionality of this bit in ATmega48 is a subset of the functionality in ATmega88/168. An LPM instruction within three cycles after BLBSET and SELFPRGEN are set in the SPMCSR Register, will read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register. See "Reading the Fuse and Lock Bits from Software" on page 260 for details.

#### • Bit 2 – PGWRT: Page Write

If this bit is written to one at the same time as SELFPRGEN, the next SPM instruction within four clock cycles executes Page Write, with the data stored in the temporary buffer. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGWRT bit will auto-clear upon completion of a Page Write, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

#### • Bit 1 – PGERS: Page Erase

If this bit is written to one at the same time as SELFPRGEN, the next SPM instruction within four clock cycles executes Page Erase. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon completion of a Page Erase, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

the RWWSB by writing the RWWSRE. See "Simple Assembly Code Example for a Boot Loader" on page 275 for an example.

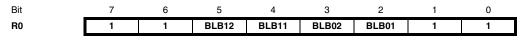

#### 24.7.7 Setting the Boot Loader Lock Bits by SPM

To set the Boot Loader Lock bits, write the desired data to R0, write "X0001001" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The only accessible Lock bits are the Boot Lock bits that may prevent the Application and Boot Loader section from any software update by the MCU.

See Table 24-2 and Table 24-3 for how the different settings of the Boot Loader bits affect the Flash access.

If bits 5..2 in R0 are cleared (zero), the corresponding Boot Lock bit will be programmed if an SPM instruction is executed within four cycles after BLBSET and SELFPRGEN are set in SPMCSR. The Z-pointer is don't care during this operation, but for future compatibility it is recommended to load the Z-pointer with 0x0001 (same as used for reading the  $IO_{ck}$  bits). For future compatibility it is also recommended to set bits 7, 6, 1, and 0 in R0 to "1" when writing the Lock bits. When programming the Lock bits the entire Flash can be read during the operation.

#### 24.7.8 EEPROM Write Prevents Writing to SPMCSR

Note that an EEPROM write operation will block all software programming to Flash. Reading the Fuses and Lock bits from software will also be prevented during the EEPROM write operation. It is recommended that the user checks the status bit (EEPE) in the EECR Register and verifies that the bit is cleared before writing to the SPMCSR Register.

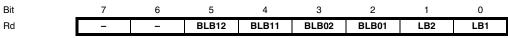

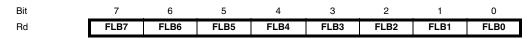

#### 24.7.9 Reading the Fuse and Lock Bits from Software

It is possible to read both the Fuse and Lock bits from software. To read the Lock bits, load the Z-pointer with 0x0001 and set the BLBSET and SELFPRGEN bits in SPMCSR. When an LPM instruction is executed within three CPU cycles after the BLBSET and SELFPRGEN bits are set in SPMCSR, the value of the Lock bits will be loaded in the destination register. The BLBSET and SELFPRGEN bits will auto-clear upon completion of reading the Lock bits or if no LPM instruction is executed within three CPU cycles or no SPM instruction is executed within four CPU cycles. When BLBSET and SELFPRGEN are cleared, LPM will work as described in the Instruction set Manual.

The algorithm for reading the Fuse Low byte is similar to the one described above for reading the Lock bits. To read the Fuse Low byte, load the Z-pointer with 0x0000 and set the BLBSET and SELFPRGEN bits in SPMCSR. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Fuse Low byte (FLB) will be loaded in the destination register as shown below. Refer to Table 25-5 on page 282 for a detailed description and mapping of the Fuse Low byte.

Similarly, when reading the Fuse High byte, load 0x0003 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Fuse High byte (FHB) will be loaded in the destination register as

| Variable |          | Corresponding<br>Z-value <sup>(1)</sup> | Description                                                                                                                 |

|----------|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PCMSB    | 12       |                                         | Most significant bit in the Program Counter. (The Program Counter is 12 bits PC[11:0])                                      |

| PAGEMSB  | 5        |                                         | Most significant bit which is used to address<br>the words within one page (64 words in a page<br>requires 6 bits PC [5:0]) |

| ZPCMSB   |          | Z13                                     | Bit in Z-register that is mapped to PCMSB. Because Z0 is not used, the ZPCMSB equals PCMSB + 1.                             |

| ZPAGEMSB |          | Z6                                      | Bit in Z-register that is mapped to PAGEMSB.<br>Because Z0 is not used, the ZPAGEMSB equals<br>PAGEMSB + 1.                 |

| PCPAGE   | PC[12:6] | Z13:Z7                                  | Program counter page address: Page select, for page erase and page write                                                    |

| PCWORD   | PC[5:0]  | Z6:Z1                                   | Program counter word address: Word select, for filling temporary buffer (must be zero during page write operation)          |

Table 24-11.

Explanation of Different Variables used in Figure 24-3 and the Mapping to the Z-pointer, ATmega168

Note: 1. Z15:Z14: always ignored

Z0: should be zero for all SPM commands, byte select for the LPM instruction. See "Addressing the Flash During Self-Programming" on page 270 for details about the use of Z-pointer during Self-Programming.

| Low Fuse Byte         | Bit No | Description          | Default Value                   |

|-----------------------|--------|----------------------|---------------------------------|

| CKDIV8 <sup>(4)</sup> | 7      | Divide clock by 8    | 0 (programmed)                  |

| CKOUT <sup>(3)</sup>  | 6      | Clock output         | 1 (unprogrammed)                |

| SUT1                  | 5      | Select start-up time | 1 (unprogrammed) <sup>(1)</sup> |

| SUT0                  | 4      | Select start-up time | 0 (programmed) <sup>(1)</sup>   |

| CKSEL3                | 3      | Select Clock source  | 0 (programmed) <sup>(2)</sup>   |

| CKSEL2                | 2      | Select Clock source  | 0 (programmed) <sup>(2)</sup>   |

| CKSEL1                | 1      | Select Clock source  | 1 (unprogrammed) <sup>(2)</sup> |

| CKSEL0                | 0      | Select Clock source  | 0 (programmed) <sup>(2)</sup>   |

Table 25-7.Fuse Low Byte

Note: 1. The default value of SUT1..0 results in maximum start-up time for the default clock source. See Table 6-9 on page 32 for details.

- 2. The default setting of CKSEL3..0 results in internal RC Oscillator @ 8 MHz. See Table 6-8 on page 31 for details.

- 3. The CKOUT Fuse allows the system clock to be output on PORTB0. See "Clock Output Buffer" on page 34 for details.

- 4. See "System Clock Prescaler" on page 34 for details.

The status of the Fuse bits is not affected by Chip Erase. Note that the Fuse bits are locked if Lock bit1 (LB1) is programmed. Program the Fuse bits before programming the Lock bits.

## 25.2.1 Latching of Fuses

The fuse values are latched when the device enters programming mode and changes of the fuse values will have no effect until the part leaves Programming mode. This does not apply to the EESAVE Fuse which will take effect once it is programmed. The fuses are also latched on Power-up in Normal mode.

## 25.3 Signature Bytes

All Atmel microcontrollers have a three-byte signature code which identifies the device. This code can be read in both serial and parallel mode, also when the device is locked. The three bytes reside in a separate address space.

#### 25.3.1 ATmega48 Signature Bytes

- 1. 0x000: 0x1E (indicates manufactured by Atmel).

- 2. 0x001: 0x92 (indicates 4KB Flash memory).

- 3. 0x002: 0x05 (indicates ATmega48 device when 0x001 is 0x92).

## 25.3.2 ATmega88 Signature Bytes

- 1. 0x000: 0x1E (indicates manufactured by Atmel).

- 2. 0x001: 0x93 (indicates 8KB Flash memory).

- 3. 0x002: 0x0A (indicates ATmega88 device when 0x001 is 0x93).

#### 25.3.3 ATmega168 Signature Bytes

- 1. 0x000: 0x1E (indicates manufactured by Atmel).

- 2. 0x001: 0x94 (indicates 16KB Flash memory).

- 3. 0x002: 0x06 (indicates ATmega168 device when 0x001 is 0x94).

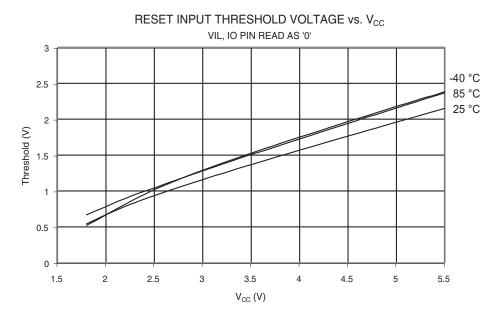

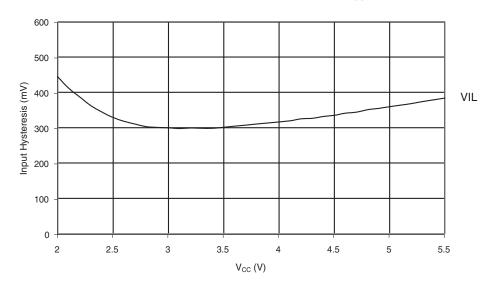

Figure 27-31. Reset Input Threshold Voltage vs.  $V_{CC}$  (VIL, Reset Pin Read As '0')

RESET PIN INPUT HYSTERESIS vs.  $V_{cc}$

ATmega48/88/168

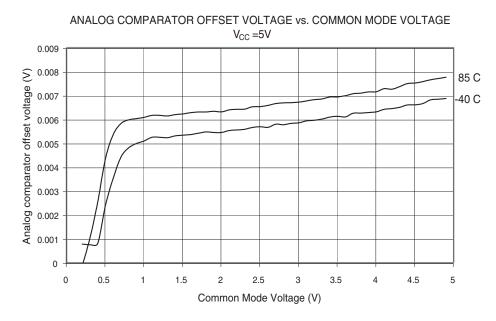

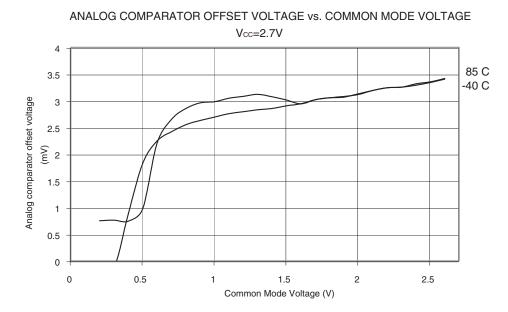

Figure 27-38. Analog Comparator Offset Voltage vs. Common Mode Voltage (V<sub>CC</sub>=2.7V)

# 29. Instruction Set Summary

| Mnemonics           | Operands         | Description                              | Operation                                                               | Flags          | #Clocks |

|---------------------|------------------|------------------------------------------|-------------------------------------------------------------------------|----------------|---------|

| ARITHMETIC AND L    | OGIC INSTRUCTION | <u> </u>                                 |                                                                         |                | -       |

| ADD                 | Rd, Rr           | Add two Registers                        | $Rd \leftarrow Rd + Rr$                                                 | Z,C,N,V,H      | 1       |

| ADC                 | Rd, Rr           | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$                                             | Z,C,N,V,H      | 1       |

| ADIW                | Rdl,K            | Add Immediate to Word                    | $Rdh:Rdl \leftarrow Rdh:Rdl + K$                                        | Z,C,N,V,S      | 2       |

| SUB                 | Rd, Rr           | Subtract two Registers                   | $Rd \leftarrow Rd - Rr$                                                 | Z,C,N,V,H      | 1       |

| SUBI                | Rd, K            | Subtract Constant from Register          | $Rd \leftarrow Rd - K$                                                  | Z,C,N,V,H      | 1       |

| SBC                 | Rd, Rr           | Subtract with Carry two Registers        | $Rd \leftarrow Rd - Rr - C$                                             | Z,C,N,V,H      | 1       |

| SBCI                | Rd, K            | Subtract with Carry Constant from Reg.   | $Rd \gets Rd - K - C$                                                   | Z,C,N,V,H      | 1       |

| SBIW                | Rdl,K            | Subtract Immediate from Word             | $Rdh:Rdl \leftarrow Rdh:Rdl - K$                                        | Z,C,N,V,S      | 2       |

| AND                 | Rd, Rr           | Logical AND Registers                    | $Rd \leftarrow Rd \bullet Rr$                                           | Z,N,V          | 1       |

| ANDI                | Rd, K            | Logical AND Register and Constant        | $Rd \leftarrow Rd \bullet K$                                            | Z,N,V          | 1       |

| OR                  | Rd, Rr           | Logical OR Registers                     | Rd ← Rd v Rr                                                            | Z,N,V          | 1       |

| ORI                 | Rd, K            | Logical OR Register and Constant         | $Rd \leftarrow Rd \lor K$                                               | Z,N,V          | 1       |

| EOR                 | Rd, Rr           | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$                                            | Z,N,V          | 1       |

| COM                 | Rd               | One's Complement                         | $Rd \leftarrow 0xFF - Rd$                                               | Z,C,N,V        | 1       |

| NEG                 | Rd               | Two's Complement                         | Rd ← 0x00 – Rd                                                          | Z,C,N,V,H      | 1       |

| SBR                 | Rd,K             | Set Bit(s) in Register                   | $Rd \leftarrow Rd \vee K$                                               | Z,N,V          | 1       |

| CBR                 | Rd,K             | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \bullet (0xFF - K)$                                   | Z,N,V          | 1       |

| INC                 | Rd               | Increment                                | $Rd \leftarrow Rd + 1$                                                  | Z,N,V          | 1       |

| DEC                 | Rd               | Decrement                                | $Rd \leftarrow Rd - 1$                                                  | Z,N,V<br>Z,N,V | 1       |

|                     |                  |                                          |                                                                         |                |         |

| TST                 | Rd               | Test for Zero or Minus                   | $Rd \leftarrow Rd \bullet Rd$                                           | Z,N,V          | 1       |

| CLR                 | Rd               | Clear Register                           | $Rd \leftarrow Rd \oplus Rd$                                            | Z,N,V          | 1       |

| SER                 | Rd               | Set Register                             | Rd ← 0xFF                                                               | None           | 1       |

| MUL                 | Rd, Rr           | Multiply Unsigned                        | $R1:R0 \leftarrow Rd x Rr$                                              | Z,C            | 2       |

| MULS                | Rd, Rr           | Multiply Signed                          | $R1:R0 \leftarrow Rd \times Rr$                                         | Z,C            | 2       |

| MULSU               | Rd, Rr           | Multiply Signed with Unsigned            | $R1:R0 \leftarrow Rd \times Rr$                                         | Z,C            | 2       |

| FMUL                | Rd, Rr           | Fractional Multiply Unsigned             | $R1:R0 \leftarrow (Rd x Rr) << 1$                                       | Z,C            | 2       |

| FMULS               | Rd, Rr           | Fractional Multiply Signed               | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                  | Z,C            | 2       |

| FMULSU              | Rd, Rr           | Fractional Multiply Signed with Unsigned | R1:R0 $\leftarrow$ (Rd x Rr) << 1                                       | Z,C            | 2       |

| BRANCH INSTRUC      | TIONS            |                                          | _                                                                       |                |         |

| RJMP                | k                | Relative Jump                            | $PC \leftarrow PC + k + 1$                                              | None           | 2       |

| IJMP                |                  | Indirect Jump to (Z)                     | $PC \leftarrow Z$                                                       | None           | 2       |

| JMP <sup>(1)</sup>  | k                | Direct Jump                              | PC ← k                                                                  | None           | 3       |

| RCALL               | k                | Relative Subroutine Call                 | $PC \leftarrow PC + k + 1$                                              | None           | 3       |

| ICALL               |                  | Indirect Call to (Z)                     | $PC \leftarrow Z$                                                       | None           | 3       |

| CALL <sup>(1)</sup> | k                | Direct Subroutine Call                   | PC ← k                                                                  | None           | 4       |

| RET                 |                  | Subroutine Return                        | $PC \leftarrow STACK$                                                   | None           | 4       |

| RETI                |                  | Interrupt Return                         | $PC \leftarrow STACK$                                                   | 1              | 4       |

| CPSE                | Rd,Rr            | Compare, Skip if Equal                   | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$                       | None           | 1/2/3   |

| CP                  | Rd,Rr            | Compare                                  | Rd – Rr                                                                 | Z, N,V,C,H     | 1       |

| CPC                 | Rd,Rr            | Compare with Carry                       | Rd – Rr – C                                                             | Z, N,V,C,H     | 1       |

|                     |                  |                                          |                                                                         |                |         |

| CPI                 | Rd,K             | Compare Register with Immediate          | Rd – K                                                                  | Z, N,V,C,H     | 1       |

| SBRC                | Rr, b            | Skip if Bit in Register Cleared          | if $(\text{Rr}(b)=0) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$ | None           | 1/2/3   |

| SBRS                | Rr, b            | Skip if Bit in Register is Set           | if $(\text{Rr}(b)=1) \text{PC} \leftarrow \text{PC} + 2 \text{ or } 3$  | None           | 1/2/3   |

| SBIC                | P, b             | Skip if Bit in I/O Register Cleared      | if (P(b)=0) PC ← PC + 2 or 3                                            | None           | 1/2/3   |

| SBIS                | P, b             | Skip if Bit in I/O Register is Set       | if (P(b)=1) PC $\leftarrow$ PC + 2 or 3                                 | None           | 1/2/3   |

| BRBS                | s, k             | Branch if Status Flag Set                | if $(SREG(s) = 1)$ then $PC \leftarrow PC + k + 1$                      | None           | 1/2     |

| BRBC                | s, k             | Branch if Status Flag Cleared            | if (SREG(s) = 0) then $PC \leftarrow PC + k + 1$                        | None           | 1/2     |

| BREQ                | k                | Branch if Equal                          | if (Z = 1) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRNE                | k                | Branch if Not Equal                      | if (Z = 0) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRCS                | k                | Branch if Carry Set                      | if (C = 1) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRCC                | k                | Branch if Carry Cleared                  | if (C = 0) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRSH                | k                | Branch if Same or Higher                 | if (C = 0) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRLO                | k                | Branch if Lower                          | if (C = 1) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRMI                | k                | Branch if Minus                          | if (N = 1) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRPL                | k                | Branch if Plus                           | if (N = 0) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRGE                | k                | Branch if Greater or Equal, Signed       | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1                   | None           | 1/2     |

| BRLT                | k                | Branch if Less Than Zero, Signed         | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1                   | None           | 1/2     |

|                     |                  |                                          |                                                                         |                |         |

| BRHS                | k                | Branch if Half Carry Flag Set            | if $(H = 1)$ then PC $\leftarrow$ PC + k + 1                            | None           | 1/2     |

| BRHC                | k                | Branch if Half Carry Flag Cleared        | if (H = 0) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRTS                | k                | Branch if T Flag Set                     | if (T = 1) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRTC                | k                | Branch if T Flag Cleared                 | if (T = 0) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BRVS                | k                | Branch if Overflow Flag is Set           | if (V = 1) then PC $\leftarrow$ PC + k + 1                              | None           | 1/2     |

| BITTE               |                  |                                          |                                                                         |                |         |