# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48-20au |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

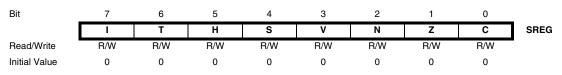

#### 4.4 Status Register

The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.

The AVR Status Register - SREG - is defined as:

#### • Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.

#### • Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

#### • Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful in BCD arithmetic. See the "Instruction Set Description" for detailed information.

#### • Bit 4 – S: Sign Bit, S = N $\oplus$ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the "Instruction Set Description" for detailed information.

#### • Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the "Instruction Set Description" for detailed information.

#### • Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

#### • Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

#### Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

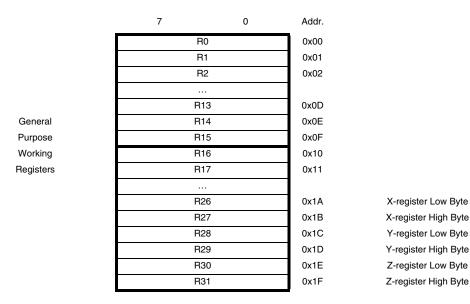

#### 4.5 General Purpose Register File

The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are supported by the Register File:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

Figure 4-2 shows the structure of the 32 general purpose working registers in the CPU.

Figure 4-2. AVR CPU General Purpose Working Registers

Most of the instructions operating on the Register File have direct access to all registers, and most of them are single cycle instructions.

As shown in Figure 4-2, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-pointer registers can be set to index any register in the file.

#### 5.3.2 The EEPROM Address Register – EEARH and EEARL

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | _     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

|               | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Х     |       |

|               | Х     | х     | х     | х     | х     | х     | х     | Х     |       |

#### • Bits 15..9 – Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### • Bits 8..0 – EEAR8..0: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL specify the EEPROM address in the 256/512/512 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 255/511/511. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

EEAR8 is an unused bit in ATmega48 and must always be written to zero.

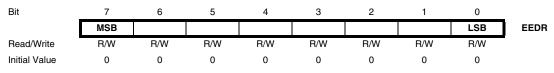

#### 5.3.3 The EEPROM Data Register – EEDR

#### Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR Register contains the data to be written to the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

#### 5.3.4 The EEPROM Control Register – EECR

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|---------------|---|---|-------|-------|-------|-------|------|------|------|

|               | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write    | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | •    |

| Initial Value | 0 | 0 | х     | х     | 0     | 0     | х    | 0    |      |

#### • Bits 7..6 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### • Bits 5, 4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits

The EEPROM Programming mode bit setting defines which programming action that will be triggered when writing EEPE. It is possible to program data in one atomic operation (erase the old value and program the new value) or to split the Erase and Write operations in two different operations. The Programming times for the different modes are shown in Table 5-1. While EEPE

When the write access time has elapsed, the EEPE bit is cleared by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEPE has been set, the CPU is halted for two cycles before the next instruction is executed.

#### • Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEPE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

The calibrated Oscillator is used to time the EEPROM accesses. Table 5-2 lists the typical programming time for EEPROM access from the CPU.

Table 5-2.

EEPROM Programming Time

| Symbol                     | Number of Calibrated RC Oscillator Cycles | Typ Programming Time |

|----------------------------|-------------------------------------------|----------------------|

| EEPROM write<br>(from CPU) | 26,368                                    | 3.3 ms               |

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

#### 8.2.1 Watchdog Timer Control Register - WDTCSR

| Bit           | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    | _      |

|---------------|------|------|------|------|-----|------|------|------|--------|

|               | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | -      |

| Initial Value | 0    | 0    | 0    | 0    | х   | 0    | 0    | 0    |        |

#### • Bit 7 - WDIF: Watchdog Interrupt Flag

This bit is set when a time-out occurs in the Watchdog Timer and the Watchdog Timer is configured for interrupt. WDIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, WDIF is cleared by writing a logic one to the flag. When the I-bit in SREG and WDIE are set, the Watchdog Time-out Interrupt is executed.

#### Bit 6 - WDIE: Watchdog Interrupt Enable

When this bit is written to one and the I-bit in the Status Register is set, the Watchdog Interrupt is enabled. If WDE is cleared in combination with this setting, the Watchdog Timer is in Interrupt Mode, and the corresponding interrupt is executed if time-out in the Watchdog Timer occurs.

If WDE is set, the Watchdog Timer is in Interrupt and System Reset Mode. The first time-out in the Watchdog Timer will set WDIF. Executing the corresponding interrupt vector will clear WDIE and WDIF automatically by hardware (the Watchdog goes to System Reset Mode). This is useful for keeping the Watchdog Timer security while using the interrupt. To stay in Interrupt and System Reset Mode, WDIE must be set after each interrupt. This should however not be done within the interrupt service routine itself, as this might compromise the safety-function of the Watchdog System Reset mode. If the interrupt is not executed before the next time-out, a System Reset will be applied.

| WDTON | WDE | WDIE | Mode                               | Action on Time-out                         |

|-------|-----|------|------------------------------------|--------------------------------------------|

| 0     | 0   | 0    | Stopped                            | None                                       |

| 0     | 0   | 1    | Interrupt Mode                     | Interrupt                                  |

| 0     | 1   | 0    | System Reset Mode                  | Reset                                      |

| 0     | 1   | 1    | Interrupt and System Reset<br>Mode | Interrupt, then go to System<br>Reset Mode |

| 1     | х   | x    | System Reset Mode                  | Reset                                      |

Table 8-5.Watchdog Timer Configuration

#### • Bit 4 - WDCE: Watchdog Change Enable

This bit is used in timed sequences for changing WDE and prescaler bits. To clear the WDE bit, and/or change the prescaler bits, WDCE must be set.

Once written to one, hardware will clear WDCE after four clock cycles.

#### Bit 3 - WDE: Watchdog System Reset Enable

WDE is overridden by WDRF in MCUSR. This means that WDE is always set when WDRF is set. To clear WDE, WDRF must be cleared first. This feature ensures multiple resets during conditions causing failure, and a safe start-up after the failure.

#### 13.7 Compare Match Output Unit

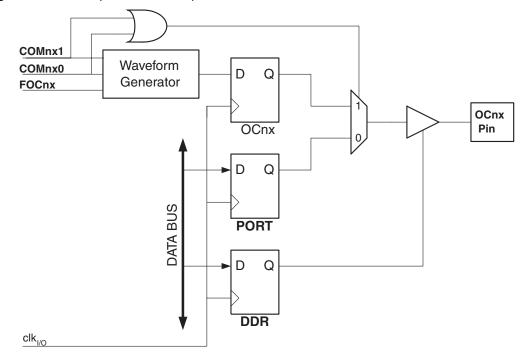

The *Compare Output mode* (COM1x1:0) bits have two functions. The Waveform Generator uses the COM1x1:0 bits for defining the Output Compare (OC1x) state at the next compare match. Secondly the COM1x1:0 bits control the OC1x pin output source. Figure 13-5 shows a simplified schematic of the logic affected by the COM1x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM1x1:0 bits are shown. When referring to the OC1x state, the reference is for the internal OC1x Register, not the OC1x pin. If a system reset occur, the OC1x Register is reset to "0".

Figure 13-5. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OC1x) from the Waveform Generator if either of the COM1x1:0 bits are set. However, the OC1x pin direction (input or output) is still controlled by the *Data Direction Register* (DDR) for the port pin. The Data Direction Register bit for the OC1x pin (DDR\_OC1x) must be set as output before the OC1x value is visible on the pin. The port override function is generally independent of the Waveform Generation mode, but there are some exceptions. Refer to Table 13-1, Table 13-2 and Table 13-3 for details.

The design of the Output Compare pin logic allows initialization of the OC1x state before the output is enabled. Note that some COM1x1:0 bit settings are reserved for certain modes of operation. See Section "13.10" on page 128.

The COM1x1:0 bits have no effect on the Input Capture unit.

#### 13.7.1 Compare Output Mode and Waveform Generation

The Waveform Generator uses the COM1x1:0 bits differently in normal, CTC, and PWM modes. For all modes, setting the COM1x1:0 = 0 tells the Waveform Generator that no action on the OC1x Register is to be performed on the next compare match. For compare output actions in the

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of<br>Operation  | ТОР    | Update of<br>OCR1x at | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|-------------------------------------|--------|-----------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                              | 0xFFFF | Immediate             | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit           | 0x00FF | TOP                   | BOTTOM              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit           | 0x01FF | TOP                   | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit          | 0x03FF | TOP                   | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | CTC                                 | OCR1A  | Immediate             | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                     | 0x00FF | TOP                   | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                     | 0x01FF | TOP                   | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                    | 0x03FF | TOP                   | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency Correct    | ICR1   | воттом                | BOTTOM              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct | OCR1A  | воттом                | BOTTOM              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                  | ICR1   | TOP                   | BOTTOM              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                  | OCR1A  | TOP                   | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                                 | ICR1   | Immediate             | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                          | _      | _                     | _                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                            | ICR1   | TOP                   | TOP                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                            | OCR1A  | TOP                   | TOP                 |

Table 13-4.

Waveform Generation Mode Bit Description<sup>(1)</sup>

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

#### 13.10.2 Timer/Counter1 Control Register B – TCCR1B

| Bit           | 7     | 6     | 5 | 4     | 3     | 2    | 1    | 0    | _      |

|---------------|-------|-------|---|-------|-------|------|------|------|--------|

|               | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  | -      |

| Initial Value | 0     | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

#### • Bit 7 – ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the noise canceler is activated, the input from the Input Capture pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four Oscillator cycles when the noise canceler is enabled.

#### • Bit 6 – ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture pin (ICP1) that is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

#### • Bit 3 – OCR2AUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2A is written, this bit becomes set. When OCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2A is ready to be updated with a new value.

#### • Bit 2 – OCR2BUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2B is written, this bit becomes set. When OCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2B is ready to be updated with a new value.

#### • Bit 1 – TCR2AUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2A is written, this bit becomes set. When TCCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2A is ready to be updated with a new value.

#### • Bit 0 – TCR2BUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2B is written, this bit becomes set. When TCCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2B is ready to be updated with a new value.

If a write is performed to any of the five Timer/Counter2 Registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur.

The mechanisms for reading TCNT2, OCR2A, OCR2B, TCCR2A and TCCR2B are different. When reading TCNT2, the actual timer value is read. When reading OCR2A, OCR2B, TCCR2A and TCCR2B the value in the temporary storage register is read.

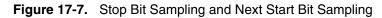

The same majority voting is done to the stop bit as done for the other bits in the frame. If the stop bit is registered to have a logic 0 value, the Frame Error (FEn) Flag will be set.

A new high to low transition indicating the start bit of a new frame can come right after the last of the bits used for majority voting. For Normal Speed mode, the first low level sample can be at point marked (A) in Figure 17-7. For Double Speed mode the first low level must be delayed to (B). (C) marks a stop bit of full length. The early start bit detection influences the operational range of the Receiver.

#### 17.7.3 Asynchronous Operational Range

The operational range of the Receiver is dependent on the mismatch between the received bit rate and the internally generated baud rate. If the Transmitter is sending frames at too fast or too slow bit rates, or the internally generated baud rate of the Receiver does not have a similar (see Table 17-2) base frequency, the Receiver will not be able to synchronize the frames to the start bit.

The following equations can be used to calculate the ratio of the incoming data rate and internal receiver baud rate.

$$R_{slow} = \frac{(D+1)S}{S-1+D\cdot S+S_F} \qquad \qquad R_{fast} = \frac{(D+2)S}{(D+1)S+S_M}$$

**D** Sum of character size and parity size (D = 5 to 10 bit)

- **S** Samples per bit. S = 16 for Normal Speed mode and S = 8 for Double Speed mode.

- $S_F$  First sample number used for majority voting.  $S_F = 8$  for normal speed and  $S_F = 4$  for Double Speed mode.

- $S_M$  Middle sample number used for majority voting.  $S_M = 9$  for normal speed and  $S_M = 5$  for Double Speed mode.

- **R**<sub>slow</sub> is the ratio of the slowest incoming data rate that can be accepted in relation to the receiver baud rate. R<sub>fast</sub> is the ratio of the fastest incoming data rate that can be accepted in relation to the receiver baud rate.

Table 17-2 and Table 17-3 list the maximum receiver baud rate error that can be tolerated. Note that Normal Speed mode has higher toleration of baud rate variations.

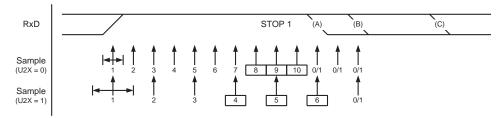

depicted below, START and STOP conditions are signalled by changing the level of the SDA line when the SCL line is high.

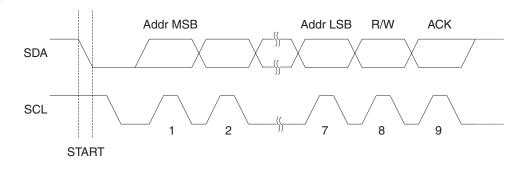

#### 19.3.3 Address Packet Format

All address packets transmitted on the TWI bus are 9 bits long, consisting of 7 address bits, one READ/WRITE control bit and an acknowledge bit. If the READ/WRITE bit is set, a read operation is to be performed, otherwise a write operation should be performed. When a Slave recognizes that it is being addressed, it should acknowledge by pulling SDA low in the ninth SCL (ACK) cycle. If the addressed Slave is busy, or for some other reason can not service the Master's request, the SDA line should be left high in the ACK clock cycle. The Master can then transmit a STOP condition, or a REPEATED START condition to initiate a new transmission. An address packet consisting of a slave address and a READ or a WRITE bit is called SLA+R or SLA+W, respectively.

The MSB of the address byte is transmitted first. Slave addresses can freely be allocated by the designer, but the address 0000 000 is reserved for a general call.

When a general call is issued, all slaves should respond by pulling the SDA line low in the ACK cycle. A general call is used when a Master wishes to transmit the same message to several slaves in the system. When the general call address followed by a Write bit is transmitted on the bus, all slaves set up to acknowledge the general call will pull the SDA line low in the ack cycle. The following data packets will then be received by all the slaves that acknowledged the general call. Note that transmitting the general call address followed by a Read bit is meaningless, as this would cause contention if several slaves started transmitting different data.

All addresses of the format 1111 xxx should be reserved for future purposes.

Figure 19-4. Address Packet Format

able. As long as the TWINT Flag is set, the SCL line is held low. This allows the application software to complete its tasks before allowing the TWI transmission to continue.

The TWINT Flag is set in the following situations:

- After the TWI has transmitted a START/REPEATED START condition.

- After the TWI has transmitted SLA+R/W.

- After the TWI has transmitted an address byte.

- After the TWI has lost arbitration.

- After the TWI has been addressed by own slave address or general call.

- After the TWI has received a data byte.

- After a STOP or REPEATED START has been received while still addressed as a Slave.

- When a bus error has occurred due to an illegal START or STOP condition.

#### 19.6 TWI Register Description

#### 19.6.1 TWI Bit Rate Register – TWBR

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | TWBR7 | TWBR6 | TWBR5 | TWBR4 | TWBR3 | TWBR2 | TWBR1 | TWBR0 | TWBR |

| Read/Write    | R/W   |      |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

#### • Bits 7..0 - TWI Bit Rate Register

TWBR selects the division factor for the bit rate generator. The bit rate generator is a frequency divider which generates the SCL clock frequency in the Master modes. See "Bit Rate Generator Unit" on page 211 for calculating bit rates.

#### 19.6.2 TWI Control Register – TWCR

| Bit           | 7     | 6    | 5     | 4     | 3    | 2    | 1 | 0    | _    |

|---------------|-------|------|-------|-------|------|------|---|------|------|

|               | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE | TWCR |

| Read/Write    | R/W   | R/W  | R/W   | R/W   | R    | R/W  | R | R/W  | -    |

| Initial Value | 0     | 0    | 0     | 0     | 0    | 0    | 0 | 0    |      |

The TWCR is used to control the operation of the TWI. It is used to enable the TWI, to initiate a Master access by applying a START condition to the bus, to generate a Receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the bus are written to the TWDR. It also indicates a write collision if data is attempted written to TWDR while the register is inaccessible.

#### • Bit 7 – TWINT: TWI Interrupt Flag

This bit is set by hardware when the TWI has finished its current job and expects application software response. If the I-bit in SREG and TWIE in TWCR are set, the MCU will jump to the TWI Interrupt Vector. While the TWINT Flag is set, the SCL low period is stretched. The TWINT Flag must be cleared by software by writing a logic one to it. Note that this flag is not automatically cleared by hardware when executing the interrupt routine. Also note that clearing this flag starts the operation of the TWI, so all accesses to the TWI Address Register (TWAR), TWI Status Register (TWSR), and TWI Data Register (TWDR) must be complete before clearing this flag.

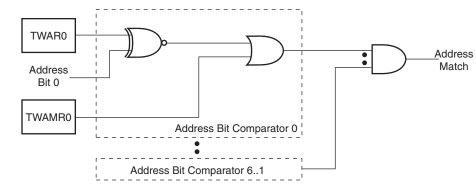

#### Figure 19-10. TWI Address Match Logic, Block Diagram

#### • Bit 0 - Res: Reserved Bit

This bit is an unused bit in the ATmega48/88/168, and will always read as zero.

#### 19.7 Using the TWI

The AVR TWI is byte-oriented and interrupt based. Interrupts are issued after all bus events, like reception of a byte or transmission of a START condition. Because the TWI is interrupt-based, the application software is free to carry on other operations during a TWI byte transfer. Note that the TWI Interrupt Enable (TWIE) bit in TWCR together with the Global Interrupt Enable bit in SREG allow the application to decide whether or not assertion of the TWINT Flag should generate an interrupt request. If the TWIE bit is cleared, the application must poll the TWINT Flag in order to detect actions on the TWI bus.

When the TWINT Flag is asserted, the TWI has finished an operation and awaits application response. In this case, the TWI Status Register (TWSR) contains a value indicating the current state of the TWI bus. The application software can then decide how the TWI should behave in the next TWI bus cycle by manipulating the TWCR and TWDR Registers.

Figure 19-11 is a simple example of how the application can interface to the TWI hardware. In this example, a Master wishes to transmit a single data byte to a Slave. This description is quite abstract, a more detailed explanation follows later in this section. A simple code example implementing the desired behavior is also presented.

not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the data packet.

- 6. When the data packet has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the data packet has successfully been sent. The status code will also reflect whether a Slave acknowledged the packet or not.

- 7. The application software should now examine the value of TWSR, to make sure that the data packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must write a specific value to TWCR, instructing the TWI hardware to transmit a STOP condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the STOP condition. Note that TWINT is NOT set after a STOP condition has been sent.

Even though this example is simple, it shows the principles involved in all TWI transmissions. These can be summarized as follows:

- When the TWI has finished an operation and expects application response, the TWINT Flag is set. The SCL line is pulled low until TWINT is cleared.

- When the TWINT Flag is set, the user must update all TWI Registers with the value relevant for the next TWI bus cycle. As an example, TWDR must be loaded with the value to be transmitted in the next bus cycle.

- After all TWI Register updates and other pending application software tasks have been completed, TWCR is written. When writing TWCR, the TWINT bit should be set. Writing a one to TWINT clears the flag. The TWI will then commence executing whatever operation was specified by the TWCR setting.

In the following an assembly and C implementation of the example is given. Note that the code below assumes that several definitions have been made, for example by using include-files.

| value                                                                                | Device's Own Slave Address                                                 |            |  |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|--|--|--|--|--|

| The upper seven bits are the address to which the 2-wire Serial Interface will respo |                                                                            |            |  |  |  |  |  |

| addressed by a                                                                       | Master. If the LSB is set, the TWI will respond to the general call addres | ss (0x00), |  |  |  |  |  |

otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "1" (read), the TWI will operate in ST mode, otherwise SR mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 19-6. The Slave Transmitter mode may also be entered if arbitration is lost while the TWI is in the Master mode (see state 0xB0).

If the TWEA bit is written to zero during a transfer, the TWI will transmit the last byte of the transfer. State 0xC0 or state 0xC8 will be entered, depending on whether the Master Receiver transmits a NACK or ACK after the final byte. The TWI is switched to the not addressed Slave mode, and will ignore the Master if it continues the transfer. Thus the Master Receiver receives all "1" as serial data. State 0xC8 is entered if the Master demands additional data bytes (by transmitting ACK), even though the Slave has transmitted the last byte (TWEA zero and expecting NACK from the Master).

While TWEA is zero, the TWI does not respond to its own slave address. However, the 2-wire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the 2-wire Serial Bus.

In all sleep modes other than Idle mode, the clock system to the TWI is turned off. If the TWEA bit is set, the interface can still acknowledge its own slave address or the general call address by using the 2-wire Serial Bus clock as a clock source. The part will then wake up from sleep and the TWI will hold the SCL clock will low during the wake up and until the TWINT Flag is cleared (by writing it to one). Further data transmission will be carried out as normal, with the AVR clocks running as normal. Observe that if the AVR is set up with a long start-up time, the SCL line may be held low for a long time, blocking other data transmissions.

Note that the 2-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these sleep modes.

| Table 19-6.         Status Codes for Slave Transmitter |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Status Code                                                                  |                                                                      | Application Software Response       |         |        | oonse     |                                                                                                                                                      |                                                                                                                                                                                          |

|------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|---------|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler                                                          | Status of the 2-wire Serial Bus<br>and 2-wire Serial Interface Hard- |                                     | To TWCR |        |           |                                                                                                                                                      | _                                                                                                                                                                                        |

| Bits<br>are 0                                                                | ware                                                                 | To/from TWDR                        | STA     | STO    | TWIN<br>T | TWE<br>A                                                                                                                                             | Next Action Taken by TWI Hardware                                                                                                                                                        |

| 0xA8                                                                         | Own SLA+R has been received;<br>ACK has been returned                | Load data byte or<br>Load data byte | x<br>x  | 0<br>0 | 1<br>1    | 0<br>1                                                                                                                                               | Last data byte will be transmitted and NOT ACK should<br>be received<br>Data byte will be transmitted and ACK should be re-                                                              |

| 0xB0                                                                         | Arbitration lost in SLA+R/W as<br>Master; own SLA+R has been         | Load data byte or                   | x       | 0      | 1         | 0                                                                                                                                                    | ceived<br>Last data byte will be transmitted and NOT ACK should<br>be received                                                                                                           |

|                                                                              | received; ACK has been returned                                      | Load data byte                      | х       | 0      | 1         | 1                                                                                                                                                    | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| 0xB8                                                                         | Data byte in TWDR has been transmitted; ACK has been                 | Load data byte or                   | х       | 0      | 1         | 0                                                                                                                                                    | Last data byte will be transmitted and NOT ACK should be received                                                                                                                        |

|                                                                              | received                                                             | Load data byte                      | х       | 0      | 1         | 1                                                                                                                                                    | Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                            |

| 0xC0 Data byte in TWDR has been<br>transmitted; NOT ACK has been<br>received | transmitted; NOT ACK has been                                        | No TWDR action or No TWDR action or | 0       | 0      | 1         | 0                                                                                                                                                    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA<br>Switched to the not addressed Slave mode;                                                               |

|                                                                              | leceiveu                                                             |                                     |         |        |           |                                                                                                                                                      | own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"                                                                                                                     |

|                                                                              | No TWDR action or                                                    | 1                                   | 0       | 1      | 0         | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free |                                                                                                                                                                                          |

|                                                                              |                                                                      | No TWDR action                      | 1       | 0      | 1         | 1                                                                                                                                                    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

| 0xC8                                                                         | Last data byte in TWDR has been transmitted (TWEA = "0"); ACK        | No TWDR action or                   | 0       | 0      | 1         | 0                                                                                                                                                    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA                                                                                                            |

|                                                                              | has been received                                                    | No TWDR action or                   | 0       | 0      | 1         | 1                                                                                                                                                    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"                                                                        |

|                                                                              |                                                                      | No TWDR action or                   | 1       | 0      | 1         | 0                                                                                                                                                    | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free                                     |

|                                                                              |                                                                      | No TWDR action                      | 1       | 0      | 1         | 1                                                                                                                                                    | Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

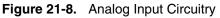

#### 21.5.1 Analog Input Circuitry

The analog input circuitry for single ended channels is illustrated in Figure 21-8. An analog source applied to ADCn is subjected to the pin capacitance and input leakage of that pin, regard-less of whether that channel is selected as input for the ADC. When the channel is selected, the source must drive the S/H capacitor through the series resistance (combined resistance in the input path).

The ADC is optimized for analog signals with an output impedance of approximately 10 k $\Omega$  or less. If such a source is used, the sampling time will be negligible. If a source with higher impedance is used, the sampling time will depend on how long time the source needs to charge the S/H capacitor, with can vary widely. The user is recommended to only use low impedant sources with slowly varying signals, since this minimizes the required charge transfer to the S/H capacitor.

Signal components higher than the Nyquist frequency ( $f_{ADC}/2$ ) should not be present for either kind of channels, to avoid distortion from unpredictable signal convolution. The user is advised to remove high frequency components with a low-pass filter before applying the signals as inputs to the ADC.

#### 21.5.2 Analog Noise Canceling Techniques

Digital circuitry inside and outside the device generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

- a. Keep analog signal paths as short as possible. Make sure analog tracks run over the analog ground plane, and keep them well away from high-speed switching digital tracks.

- b. The  $AV_{CC}$  pin on the device should be connected to the digital  $V_{CC}$  supply voltage via an LC network as shown in Figure 21-9.

- c. Use the ADC noise canceler function to reduce induced noise from the CPU.

- d. If any ADC [3..0] port pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress. However, using the 2-wire Interface (ADC4

### 22. debugWIRE On-chip Debug System

#### 22.1 Features

- Complete Program Flow Control

- Emulates All On-chip Functions, Both Digital and Analog, except RESET Pin

- Real-time Operation

- Symbolic Debugging Support (Both at C and Assembler Source Level, or for Other HLLs)

- Unlimited Number of Program Break Points (Using Software Break Points)

- Non-intrusive Operation

- Electrical Characteristics Identical to Real Device

- Automatic Configuration System

- High-Speed Operation

- Programming of Non-volatile Memories

#### 22.2 Overview

The debugWIRE On-chip debug system uses a One-wire, bi-directional interface to control the program flow, execute AVR instructions in the CPU and to program the different non-volatile memories.

#### 22.3 Physical Interface

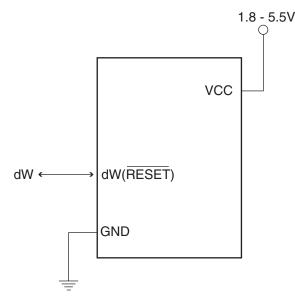

When the debugWIRE Enable (DWEN) Fuse is programmed and Lock bits are unprogrammed, the debugWIRE system within the target device is activated. The RESET port pin is configured as a wire-AND (open-drain) bi-directional I/O pin with pull-up enabled and becomes the communication gateway between target and emulator.

#### Figure 22-1. The debugWIRE Setup

Figure 22-1 shows the schematic of a target MCU, with debugWIRE enabled, and the emulator connector. The system clock is not affected by debugWIRE and will always be the clock source selected by the CKSEL Fuses.

```

; return to RWW section

; verify that RWW section is safe to read

Return:

in

temp1, SPMCSR

sbrs temp1, RWWSB

; If RWWSB is set, the RWW section is not ready yet

ret

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SELFPRGEN)

rcallDo_spm

rjmp Return

Do_spm:

; check for previous SPM complete

Wait_spm:

in temp1, SPMCSR

sbrc temp1, SELFPRGEN

rjmp Wait_spm

; input: spmcrval determines SPM action

; disable interrupts if enabled, store status

in

temp2, SREG

cli

; check that no EEPROM write access is present

Wait_ee:

sbic EECR, EEPE

rjmp Wait_ee

; SPM timed sequence

out SPMCSR, spmcrval

spm

; restore SREG (to enable interrupts if originally enabled)

out SREG, temp2

ret

```

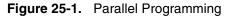

Note:  $V_{CC}$  - 0.3V < AV<sub>CC</sub> < V<sub>CC</sub> + 0.3V, however, AV<sub>CC</sub> should always be within 4.5 - 5.5V

| Signal Name in<br>Programming Mode | Pin Name           | I/O | Function                                                                    |

|------------------------------------|--------------------|-----|-----------------------------------------------------------------------------|

| RDY/BSY                            | PD1                | 0   | 0: Device is busy programming, 1: Device is ready for new command           |

| ŌĒ                                 | PD2                | I   | Output Enable (Active low)                                                  |

| WR                                 | PD3                | I   | Write Pulse (Active low)                                                    |

| BS1                                | PD4                | I   | Byte Select 1 ("0" selects Low byte, "1" selects High byte)                 |

| XA0                                | PD5                | I   | XTAL Action Bit 0                                                           |

| XA1                                | PD6                | I   | XTAL Action Bit 1                                                           |

| PAGEL                              | PD7                | I   | Program memory and EEPROM Data Page Load                                    |

| BS2                                | PC2                | I   | Byte Select 2 ("0" selects Low byte, "1" selects 2'nd High byte)            |

| DATA                               | {PC[1:0]: PB[5:0]} | I/O | Bi-directional Data bus (Output when $\overline{\text{OE} \text{ is low})}$ |

Table 25-10. Pin Name Mapping

|  | Table 25-11. | Pin Values | Used to | Enter | Programming | Mode |

|--|--------------|------------|---------|-------|-------------|------|

|--|--------------|------------|---------|-------|-------------|------|

| Pin   | Symbol         | Value |

|-------|----------------|-------|

| PAGEL | Prog_enable[3] | 0     |

| XA1   | Prog_enable[2] | 0     |

| XA0   | Prog_enable[1] | 0     |

| BS1   | Prog_enable[0] | 0     |

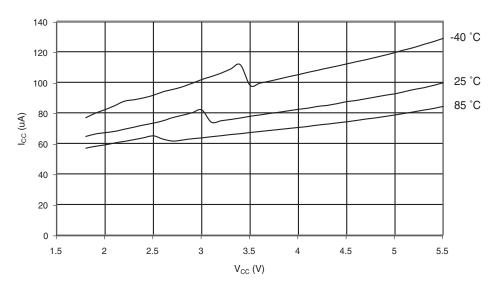

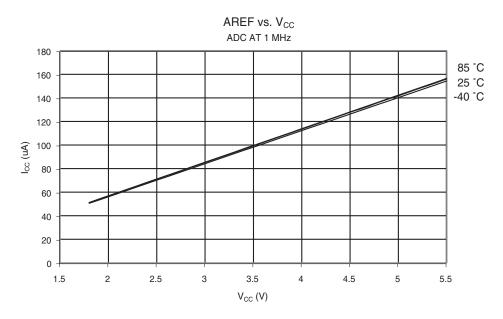

ANALOG COMPARATOR CURRENT vs.  $V_{\text{CC}}$