#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 4KB (2K × 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-TQFP                                                                  |

| Supplier Device Package    | 32-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48-20aur |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

The various special features of Port D are elaborated in "Alternate Functions of Port D" on page 78.

# 2.3.7 AV<sub>cc</sub>

2.3.9

$AV_{CC}$  is the supply voltage pin for the A/D Converter, PC3..0, and ADC7..6. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. Note that PC6..4 use digital supply voltage,  $V_{CC}$ .

## 2.3.8 AREF AREF is the analog reference pin for the A/D Converter.

# ADC7..6 (TQFP and QFN/MLF Package Only)

In the TQFP and QFN/MLF package, ADC7..6 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.

# 3. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

#### Assembly Code Example

```

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR,r16

; Write logical one to EEMPE

sbi EECR, EEMPE

; Start eeprom write by setting EEPE

sbi EECR, EEPE

ret

```

#### C Code Example

```

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEPE))

;

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR |= (1<<EEMPE);

/* Start eeprom write by setting EEPE */

EECR |= (1<<EEPE);

}</pre>

```

dependent as shown in "ATmega48/88/168 Typical Characteristics – Preliminary Data" on page 307.

| Typ Time-out (V <sub>CC</sub> = 5.0V) | Typ Time-out (V <sub>CC</sub> = 3.0V) | Number of Cycles |  |  |  |  |  |  |  |

|---------------------------------------|---------------------------------------|------------------|--|--|--|--|--|--|--|

| 0 ms                                  | 0 ms                                  | 0                |  |  |  |  |  |  |  |

| 4.1 ms                                | 4.3 ms                                | 4K (4,096)       |  |  |  |  |  |  |  |

| 65 ms                                 | 69 ms                                 | 8K (8,192)       |  |  |  |  |  |  |  |

Table 6-2. Number of Watchdog Oscillator Cycles

Main purpose of the delay is to keep the AVR in reset until it is supplied with minimum  $V_{CC}$ . The delay will not monitor the actual voltage and it will be required to select a delay longer than the  $V_{CC}$  rise time. If this is not possible, an internal or external Brown-Out Detection circuit should be used. A BOD circuit will ensure sufficient  $V_{CC}$  before it releases the reset, and the time-out delay can be disabled. Disabling the time-out delay without utilizing a Brown-Out Detection circuit is not recommended.

The oscillator is required to oscillate for a minimum number of cycles before the clock is considered stable. An internal ripple counter monitors the oscillator output clock, and keeps the internal reset active for a given number of clock cycles. The reset is then released and the device will start to execute. The recommended oscillator start-up time is dependent on the clock type, and varies from 6 cycles for an externally applied clock to 32K cycles for a low frequency crystal.

The start-up sequence for the clock includes both the time-out delay and the start-up time when the device starts up from reset. When starting up from Power-save or Power-down mode,  $V_{CC}$  is assumed to be at a sufficient level and only the start-up time is included.

## 6.3 Low Power Crystal Oscillator

Pins XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in Figure 6-2. Either a quartz crystal or a ceramic resonator may be used.

This Crystal Oscillator is a low power oscillator, with reduced voltage swing on the XTAL2 output. It gives the lowest power consumption, but is not capable of driving other clock inputs, and may be more susceptible to noise in noisy environments. In these cases, refer to the "Full Swing Crystal Oscillator" on page 29.

C1 and C2 should always be equal for both crystals and resonators. The optimal value of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for choosing capacitors for use with crystals are given in Table 6-3. For ceramic resonators, the capacitor values given by the manufacturer should be used.

the 2-wire Serial Interface. In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal, and the pin is driven by an open drain driver with slew-rate limitation.

PC4 can also be used as ADC input Channel 4. Note that ADC input channel 4 uses digital power.

PCINT12: Pin Change Interrupt source 12. The PC4 pin can serve as an external interrupt source.

#### • ADC3/PCINT11 – Port C, Bit 3

PC3 can also be used as ADC input Channel 3. Note that ADC input channel 3 uses analog power.

PCINT11: Pin Change Interrupt source 11. The PC3 pin can serve as an external interrupt source.

#### • ADC2/PCINT10 – Port C, Bit 2

PC2 can also be used as ADC input Channel 2. Note that ADC input channel 2 uses analog power.

PCINT10: Pin Change Interrupt source 10. The PC2 pin can serve as an external interrupt source.

#### • ADC1/PCINT9 – Port C, Bit 1

PC1 can also be used as ADC input Channel 1. Note that ADC input channel 1 uses analog power.

PCINT9: Pin Change Interrupt source 9. The PC1 pin can serve as an external interrupt source.

#### ADC0/PCINT8 – Port C, Bit 0

PC0 can also be used as ADC input Channel 0. Note that ADC input channel 0 uses analog power.

PCINT8: Pin Change Interrupt source 8. The PC0 pin can serve as an external interrupt source.

| Signal<br>Name | PD7/AIN1<br>/PCINT23 | PD6/AIN0/<br>OC0A/PCINT22 | PD5/T1/OC0B/<br>PCINT21   | PD4/XCK/<br>T0/PCINT20                 |

|----------------|----------------------|---------------------------|---------------------------|----------------------------------------|

| PUOE           | 0                    | 0                         | 0                         | 0                                      |

| PUO            | 0                    | 0                         | 0                         | 0                                      |

| DDOE           | 0                    | 0                         | 0                         | 0                                      |

| DDOV           | 0                    | 0                         | 0                         | 0                                      |

| PVOE           | 0                    | OC0A ENABLE               | OC0B ENABLE               | UMSEL                                  |

| PVOV           | 0                    | OC0A                      | OC0B                      | XCK OUTPUT                             |

| DIEOE          | PCINT23 • PCIE2      | PCINT22 • PCIE2           | PCINT21 • PCIE2           | PCINT20 • PCIE2                        |

| DIEOV          | 1                    | 1                         | 1                         | 1                                      |

| DI             | PCINT23 INPUT        | PCINT22 INPUT             | PCINT21 INPUT<br>T1 INPUT | PCINT20 INPUT<br>XCK INPUT<br>T0 INPUT |

| AIO            | AIN1 INPUT           | AIN0 INPUT                | -                         | -                                      |

Table 10-10.

Overriding Signals for Alternate Functions PD7..PD4

Table 10-11.

Overriding Signals for Alternate Functions in PD3..PD0

| Signal<br>Name | PD3/OC2B/INT1/<br>PCINT19        | PD2/INT0/<br>PCINT18             | PD1/TXD/<br>PCINT17 | PD0/RXD/<br>PCINT16  |

|----------------|----------------------------------|----------------------------------|---------------------|----------------------|

| PUOE           | 0                                | 0                                | TXEN                | RXEN                 |

| PUO            | 0                                | 0                                | 0                   | PORTD0 • PUD         |

| DDOE           | 0                                | 0                                | TXEN                | RXEN                 |

| DDOV           | 0                                | 0                                | 1                   | 0                    |

| PVOE           | OC2B ENABLE                      | 0                                | TXEN                | 0                    |

| PVOV           | OC2B                             | 0                                | TXD                 | 0                    |

| DIEOE          | INT1 ENABLE +<br>PCINT19 • PCIE2 | INT0 ENABLE +<br>PCINT18 • PCIE1 | PCINT17 • PCIE2     | PCINT16 • PCIE2      |

| DIEOV          | 1                                | 1                                | 1                   | 1                    |

| DI             | PCINT19 INPUT<br>INT1 INPUT      | PCINT18 INPUT<br>INT0 INPUT      | PCINT17 INPUT       | PCINT16 INPUT<br>RXD |

| AIO            | -                                | -                                | -                   | _                    |

# 10.4 Register Description for I/O Ports

# 10.4.1 The Port B Data Register – PORTB

10.4.2

10.4.3

10.4.4

10.4.5

|              | Bit                                                  | 7                                         | 6                                      | 5                       | 4                       | 3                       | 2                       | 1                  | 0                  |      |

|--------------|------------------------------------------------------|-------------------------------------------|----------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------|--------------------|------|

|              |                                                      | PORTB7                                    | PORTB6                                 | PORTB5                  | PORTB4                  | PORTB3                  | PORTB2                  | PORTB1             | PORTB0             | PORT |

|              | Read/Write                                           | R/W                                       | R/W                                    | R/W                     | R/W                     | R/W                     | R/W                     | R/W                | R/W                |      |

|              | Initial Value                                        | 0                                         | 0                                      | 0                       | 0                       | 0                       | 0                       | 0                  | 0                  |      |

| The Port B I | Data Direction                                       | Registe                                   | - DDRB                                 |                         |                         |                         |                         |                    |                    |      |

|              | Bit                                                  | 7                                         | 6                                      | 5                       | 4                       | 3                       | 2                       | 1                  | 0                  |      |

|              |                                                      | DDB7                                      | DDB6                                   | DDB5                    | DDB4                    | DDB3                    | DDB2                    | DDB1               | DDB0               | DDR  |

|              | Read/Write                                           | R/W                                       | R/W                                    | R/W                     | R/W                     | R/W                     | R/W                     | R/W                | R/W                |      |

|              | Initial Value                                        | 0                                         | 0                                      | 0                       | 0                       | 0                       | 0                       | 0                  | 0                  |      |

| he Port B I  | Input Pins Add                                       | ress – P                                  | INB                                    |                         |                         |                         |                         |                    |                    |      |

|              | Bit                                                  | 7                                         | 6                                      | 5                       | 4                       | 3                       | 2                       | 1                  | 0                  |      |

|              |                                                      | PINB7                                     | PINB6                                  | PINB5                   | PINB4                   | PINB3                   | PINB2                   | PINB1              | PINB0              | PIN  |

|              | Read/Write                                           | R                                         | R                                      | R                       | R                       | R                       | R                       | R                  | R                  |      |

|              | Initial Value                                        | N/A                                       | N/A                                    | N/A                     | N/A                     | N/A                     | N/A                     | N/A                | N/A                |      |

|              |                                                      |                                           |                                        |                         |                         |                         |                         |                    |                    |      |

| The Port C I | Data Register -                                      | - PORTC                                   | ;                                      |                         |                         |                         |                         |                    |                    |      |

| he Port C I  | Data Register -<br><sub>Bit</sub>                    | - PORTC                                   | 6                                      | 5                       | 4                       | 3                       | 2                       | 1                  | 0                  |      |

| he Port C I  | -                                                    |                                           |                                        | 5<br><b>PORTC5</b>      | 4<br>PORTC4             | 3<br>PORTC3             | 2<br>PORTC2             | 1<br>PORTC1        | 0<br>PORTC0        | POR  |

| he Port C I  | -                                                    | 7                                         | 6                                      |                         |                         |                         |                         |                    |                    | POR  |

| he Port C I  | Bit                                                  | 7                                         | 6<br>PORTC6                            | PORTC5                  | PORTC4                  | PORTC3                  | PORTC2                  | PORTC1             | PORTC0             | POR  |

|              | Bit<br>Read/Write                                    | 7<br>-<br>R<br>0                          | 6<br>PORTC6<br>R/W<br>0                | PORTC5<br>R/W           | PORTC4<br>R/W           | PORTC3<br>R/W           | PORTC2<br>R/W           | PORTC1<br>R/W      | PORTC0<br>R/W      | POR  |

|              | Bit<br>Read/Write<br>Initial Value                   | 7<br>-<br>R<br>0                          | 6<br>PORTC6<br>R/W<br>0                | PORTC5<br>R/W           | PORTC4<br>R/W           | PORTC3<br>R/W           | PORTC2<br>R/W           | PORTC1<br>R/W      | PORTC0<br>R/W      | POR  |

|              | Bit<br>Read/Write<br>Initial Value<br>Data Direction | 7<br>-<br>R<br>0<br>Register              | 6<br>PORTC6<br>R/W<br>0<br>- DDRC      | PORTC5<br>R/W<br>0      | R/W<br>0                | PORTC3<br>R/W<br>0      | PORTC2<br>R/W<br>0      | PORTC1<br>R/W<br>0 | PORTC0<br>R/W<br>0 |      |

|              | Bit<br>Read/Write<br>Initial Value<br>Data Direction | 7<br>-<br>R<br>0<br><b>Registe</b> i<br>7 | 6<br>PORTC6<br>R/W<br>0<br>- DDRC<br>6 | PORTC5<br>R/W<br>0<br>5 | PORTC4<br>R/W<br>0<br>4 | PORTC3<br>R/W<br>0<br>3 | PORTC2<br>R/W<br>0<br>2 | PORTC1<br>R/W<br>0 | PORTCO<br>R/W<br>0 | POR  |

## 10.4.6 The Port C Input Pins Address – PINC

| Bit           | 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|---|-------|-------|-------|-------|-------|-------|-------|------|

|               | - | PINC6 | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 | PINC |

| Read/Write    | R | R     | R     | R     | R     | R     | R     | R     | -    |

| Initial Value | 0 | N/A   |      |

## 10.4.7 The Port D Data Register – PORTD

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|               | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

## 10.4.8 The Port D Data Direction Register – DDRD

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

|               | DDD7 | DDD6 | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 | DDRD |

| Read/Write    | R/W  | •    |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

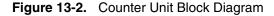

## 13.4 Counter Unit

The main part of the 16-bit Timer/Counter is the programmable 16-bit bi-directional counter unit. Figure 13-2 shows a block diagram of the counter and its surroundings.

Signal description (internal signals):

| Count             | Increment or decrement TCNT1 by 1.                     |

|-------------------|--------------------------------------------------------|

| Direction         | Select between increment and decrement.                |

| Clear             | Clear TCNT1 (set all bits to zero).                    |

| clk <sub>T1</sub> | Timer/Counter clock.                                   |

| ТОР               | Signalize that TCNT1 has reached maximum value.        |

| воттом            | Signalize that TCNT1 has reached minimum value (zero). |

The 16-bit counter is mapped into two 8-bit I/O memory locations: *Counter High* (TCNT1H) containing the upper eight bits of the counter, and *Counter Low* (TCNT1L) containing the lower eight bits. The TCNT1H Register can only be indirectly accessed by the CPU. When the CPU does an access to the TCNT1H I/O location, the CPU accesses the high byte temporary register (TEMP). The temporary register is updated with the TCNT1H value when the TCNT1L is read, and TCNT1H is updated with the temporary register value when TCNT1L is written. This allows the CPU to read or write the entire 16-bit counter value within one clock cycle via the 8-bit data bus. It is important to notice that there are special cases of writing to the TCNT1 Register when the counter is counting that will give unpredictable results. The special cases are described in the sections where they are of importance.

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each *timer clock* ( $clk_{T1}$ ). The  $clk_{T1}$  can be generated from an external or internal clock source, selected by the *Clock Select* bits (CS12:0). When no clock source is selected (CS12:0 = 0) the timer is stopped. However, the TCNT1 value can be accessed by the CPU, independent of whether  $clk_{T1}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the *Waveform Generation mode* bits (WGM13:0) located in the *Timer/Counter Control Registers* A and B (TCCR1A and TCCR1B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC1x. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 118.

non-PWM modes refer to Table 13-1 on page 128. For fast PWM mode refer to Table 13-2 on page 128, and for phase correct and phase and frequency correct PWM refer to Table 13-3 on page 129.

A change of the COM1x1:0 bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC1x strobe bits.

## 13.8 Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the combination of the *Waveform Generation mode* (WGM13:0) and *Compare Output mode* (COM1x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM1x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM1x1:0 bits control whether the output should be set, cleared or toggle at a compare match (See Section "13.7" on page 117.)

For detailed timing information refer to "Timer/Counter Timing Diagrams" on page 125.

## 13.8.1 Normal Mode

The simplest mode of operation is the *Normal mode* (WGM13:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 16-bit value (MAX = 0xFFFF) and then restarts from the BOTTOM (0x0000). In normal operation the *Timer/Counter Overflow Flag* (TOV1) will be set in the same timer clock cycle as the TCNT1 becomes zero. The TOV1 Flag in this case behaves like a 17th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV1 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Input Capture unit is easy to use in Normal mode. However, observe that the maximum interval between the external events must not exceed the resolution of the counter. If the interval between events are too long, the timer overflow interrupt or the prescaler must be used to extend the resolution for the capture unit.

The Output Compare units can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

#### 13.8.2 Clear Timer on Compare Match (CTC) Mode

In *Clear Timer on Compare* or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 Register are used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 = 12). The OCR1A or ICR1 define the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 13-6. The counter value (TCNT1) increases until a compare match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared.

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of<br>Operation  | ТОР    | Update of<br>OCR1x at | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|-------------------------------------|--------|-----------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                              | 0xFFFF | Immediate             | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit           | 0x00FF | TOP                   | BOTTOM              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit           | 0x01FF | TOP                   | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit          | 0x03FF | TOP                   | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | CTC                                 | OCR1A  | Immediate             | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                     | 0x00FF | TOP                   | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                     | 0x01FF | TOP                   | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                    | 0x03FF | TOP                   | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct | ICR1   | воттом                | BOTTOM              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct | OCR1A  | воттом                | BOTTOM              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                  | ICR1   | TOP                   | BOTTOM              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                  | OCR1A  | TOP                   | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                                 | ICR1   | Immediate             | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                          | _      | _                     | _                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                            | ICR1   | TOP                   | TOP                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                            | OCR1A  | TOP                   | TOP                 |

Table 13-4.

Waveform Generation Mode Bit Description<sup>(1)</sup>

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

## 13.10.2 Timer/Counter1 Control Register B – TCCR1B

| Bit           | 7     | 6     | 5 | 4     | 3     | 2    | 1    | 0    | _      |

|---------------|-------|-------|---|-------|-------|------|------|------|--------|

|               | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  | -      |

| Initial Value | 0     | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

## • Bit 7 – ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the noise canceler is activated, the input from the Input Capture pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four Oscillator cycles when the noise canceler is enabled.

#### • Bit 6 – ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture pin (ICP1) that is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

## 13.10.9 Timer/Counter1 Interrupt Flag Register – TIFR1

| Bit           | 7 | 6 | 5    | 4 | 3 | 2     | 1     | 0    | _     |

|---------------|---|---|------|---|---|-------|-------|------|-------|

|               | - | - | ICF1 | - | - | OCF1B | OCF1A | TOV1 | TIFR1 |

| Read/Write    | R | R | R/W  | R | R | R/W   | R/W   | R/W  | -     |

| Initial Value | 0 | 0 | 0    | 0 | 0 | 0     | 0     | 0    |       |

#### • Bit 7, 6 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 5 – ICF1: Timer/Counter1, Input Capture Flag

This flag is set when a capture event occurs on the ICP1 pin. When the Input Capture Register (ICR1) is set by the WGM13:0 to be used as the TOP value, the ICF1 Flag is set when the counter reaches the TOP value.

ICF1 is automatically cleared when the Input Capture Interrupt Vector is executed. Alternatively, ICF1 can be cleared by writing a logic one to its bit location.

#### Bit 4, 3 – Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### Bit 2 – OCF1B: Timer/Counter1, Output Compare B Match Flag

This flag is set in the timer clock cycle after the counter (TCNT1) value matches the Output Compare Register B (OCR1B).

Note that a Forced Output Compare (FOC1B) strobe will not set the OCF1B Flag.

OCF1B is automatically cleared when the Output Compare Match B Interrupt Vector is executed. Alternatively, OCF1B can be cleared by writing a logic one to its bit location.

#### • Bit 1 – OCF1A: Timer/Counter1, Output Compare A Match Flag

This flag is set in the timer clock cycle after the counter (TCNT1) value matches the Output Compare Register A (OCR1A).

Note that a Forced Output Compare (FOC1A) strobe will not set the OCF1A Flag.

OCF1A is automatically cleared when the Output Compare Match A Interrupt Vector is executed. Alternatively, OCF1A can be cleared by writing a logic one to its bit location.

#### Bit 0 – TOV1: Timer/Counter1, Overflow Flag

The setting of this flag is dependent of the WGM13:0 bits setting. In Normal and CTC modes, the TOV1 Flag is set when the timer overflows. Refer to Table 13-4 on page 130 for the TOV1 Flag behavior when using another WGM13:0 bit setting.

TOV1 is automatically cleared when the Timer/Counter1 Overflow Interrupt Vector is executed. Alternatively, TOV1 can be cleared by writing a logic one to its bit location.

## 14.0.4 General Timer/Counter Control Register – GTCCR

| Bit           | 7   | 6 | 5 | 4 | 3 | 2 | 1      | 0       | _     |

|---------------|-----|---|---|---|---|---|--------|---------|-------|

|               | TSM | - | - | - | - | - | PSRASY | PSRSYNC | GTCCR |

| Read/Write    | R/W | R | R | R | R | R | R/W    | R/W     | •     |

| Initial Value | 0   | 0 | 0 | 0 | 0 | 0 | 0      | 0       |       |

## • Bit 7 – TSM: Timer/Counter Synchronization Mode

Writing the TSM bit to one activates the Timer/Counter Synchronization mode. In this mode, the value that is written to the PSRASY and PSRSYNC bits is kept, hence keeping the corresponding prescaler reset signals asserted. This ensures that the corresponding Timer/Counters are halted and can be configured to the same value without the risk of one of them advancing during configuration. When the TSM bit is written to zero, the PSRASY and PSRSYNC bits are cleared by hardware, and the Timer/Counters start counting simultaneously.

## • Bit 0 – PSRSYNC: Prescaler Reset

When this bit is one, Timer/Counter1 and Timer/Counter0 prescaler will be Reset. This bit is normally cleared immediately by hardware, except if the TSM bit is set. Note that Timer/Counter1 and Timer/Counter0 share the same prescaler and a reset of this prescaler will affect both timers.

nine data bits, then the ninth bit (RXB8n) is used for identifying address and data frames. When the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the frame type bit is zero the frame is a data frame.

The Multi-processor Communication mode enables several slave MCUs to receive data from a master MCU. This is done by first decoding an address frame to find out which MCU has been addressed. If a particular slave MCU has been addressed, it will receive the following data frames as normal, while the other slave MCUs will ignore the received frames until another address frame is received.

#### 17.8.1 Using MPCMn

For an MCU to act as a master MCU, it can use a 9-bit character frame format (UCSZn = 7). The ninth bit (TXB8n) must be set when an address frame (TXB8n = 1) or cleared when a data frame (TXB = 0) is being transmitted. The slave MCUs must in this case be set to use a 9-bit character frame format.

The following procedure should be used to exchange data in Multi-processor Communication mode:

- 1. All Slave MCUs are in Multi-processor Communication mode (MPCMn in UCSRnA is set).

- 2. The Master MCU sends an address frame, and all slaves receive and read this frame. In the Slave MCUs, the RXCn Flag in UCSRnA will be set as normal.

- Each Slave MCU reads the UDRn Register and determines if it has been selected. If so, it clears the MPCMn bit in UCSRnA, otherwise it waits for the next address byte and keeps the MPCMn setting.

- 4. The addressed MCU will receive all data frames until a new address frame is received. The other Slave MCUs, which still have the MPCMn bit set, will ignore the data frames.

- 5. When the last data frame is received by the addressed MCU, the addressed MCU sets the MPCMn bit and waits for a new address frame from master. The process then repeats from 2.

Using any of the 5- to 8-bit character frame formats is possible, but impractical since the Receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult since the Transmitter and Receiver uses the same character size setting. If 5- to 8-bit character frames are used, the Transmitter must be set to use two stop bit (USBSn = 1) since the first stop bit is used for indicating the frame type.

Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCMn bit. The MPCMn bit shares the same I/O location as the TXCn Flag and this might accidentally be cleared when using SBI or CBI instructions.

Writing this bit to one enables the USART Receiver in MSPIM mode. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer. Only enabling the receiver in MSPI mode (i.e. setting RXENn=1 and TXENn=0) has no meaning since it is the transmitter that controls the transfer clock and since only master mode is supported.

## • Bit 3 - TXENn: Transmitter Enable

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn port.

## Bit 2:0 - Reserved Bits in MSPI mode

When in MSPI mode, these bits are reserved for future use. For compatibility with future devices, these bits must be written to zero when UCSRnB is written.

## 18.6.4 USART MSPIM Control and Status Register n C - UCSRnC

| Bit           | 7       | 6       | 5 | 4 | 3 | 2      | 1      | 0      | _      |

|---------------|---------|---------|---|---|---|--------|--------|--------|--------|

|               | UMSELn1 | UMSELn0 | - | - | - | UDORDn | UCPHAn | UCPOLn | UCSRnC |

| Read/Write    | R/W     | R/W     | R | R | R | R/W    | R/W    | R/W    | -      |

| Initial Value | 0       | 0       | 0 | 0 | 0 | 1      | 1      | 0      |        |

## • Bit 7:6 - UMSELn1:0: USART Mode Select

These bits select the mode of operation of the USART as shown in Table 18-3. See "USART Control and Status Register n C – UCSRnC" on page 189 for full description of the normal USART operation. The MSPIM is enabled when both UMSELn bits are set to one. The UDORDn, UCPHAn, and UCPOLn can be set in the same write operation where the MSPIM is enabled.

| Table 18-3. UI | <b>MSELn Bits Settings</b> |

|----------------|----------------------------|

|----------------|----------------------------|

| UMSELn1 | UMSELn0 | Mode               |

|---------|---------|--------------------|

| 0       | 0       | Asynchronous USART |

| 0       | 1       | Synchronous USART  |

| 1       | 0       | (Reserved)         |

| 1       | 1       | Master SPI (MSPIM) |

## • Bit 5:3 - Reserved Bits in MSPI mode

When in MSPI mode, these bits are reserved for future use. For compatibility with future devices, these bits must be written to zero when UCSRnC is written.

## • Bit 2 - UDORDn: Data Order

When set to one the LSB of the data word is transmitted first. When set to zero the MSB of the data word is transmitted first. Refer to the Frame Formats section page 4 for details.

## • Bit 1 - UCPHAn: Clock Phase

The UCPHAn bit setting determine if data is sampled on the leasing edge (first) or tailing (last) edge of XCKn. Refer to the SPI Data Modes and Timing section page 4 for details.

# ATmega48/88/168

able. As long as the TWINT Flag is set, the SCL line is held low. This allows the application software to complete its tasks before allowing the TWI transmission to continue.

The TWINT Flag is set in the following situations:

- After the TWI has transmitted a START/REPEATED START condition.

- After the TWI has transmitted SLA+R/W.

- After the TWI has transmitted an address byte.

- After the TWI has lost arbitration.

- After the TWI has been addressed by own slave address or general call.

- After the TWI has received a data byte.

- After a STOP or REPEATED START has been received while still addressed as a Slave.

- When a bus error has occurred due to an illegal START or STOP condition.

## 19.6 TWI Register Description

## 19.6.1 TWI Bit Rate Register – TWBR

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | TWBR7 | TWBR6 | TWBR5 | TWBR4 | TWBR3 | TWBR2 | TWBR1 | TWBR0 | TWBR |

| Read/Write    | R/W   |      |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

## • Bits 7..0 - TWI Bit Rate Register

TWBR selects the division factor for the bit rate generator. The bit rate generator is a frequency divider which generates the SCL clock frequency in the Master modes. See "Bit Rate Generator Unit" on page 211 for calculating bit rates.

#### 19.6.2 TWI Control Register – TWCR

| Bit           | 7     | 6    | 5     | 4     | 3    | 2    | 1 | 0    | _    |

|---------------|-------|------|-------|-------|------|------|---|------|------|

|               | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE | TWCR |

| Read/Write    | R/W   | R/W  | R/W   | R/W   | R    | R/W  | R | R/W  | -    |

| Initial Value | 0     | 0    | 0     | 0     | 0    | 0    | 0 | 0    |      |

The TWCR is used to control the operation of the TWI. It is used to enable the TWI, to initiate a Master access by applying a START condition to the bus, to generate a Receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the bus are written to the TWDR. It also indicates a write collision if data is attempted written to TWDR while the register is inaccessible.

#### • Bit 7 – TWINT: TWI Interrupt Flag

This bit is set by hardware when the TWI has finished its current job and expects application software response. If the I-bit in SREG and TWIE in TWCR are set, the MCU will jump to the TWI Interrupt Vector. While the TWINT Flag is set, the SCL low period is stretched. The TWINT Flag must be cleared by software by writing a logic one to it. Note that this flag is not automatically cleared by hardware when executing the interrupt routine. Also note that clearing this flag starts the operation of the TWI, so all accesses to the TWI Address Register (TWAR), TWI Status Register (TWSR), and TWI Data Register (TWDR) must be complete before clearing this flag.

## • Bit 6 – TWEA: TWI Enable Acknowledge Bit

The TWEA bit controls the generation of the acknowledge pulse. If the TWEA bit is written to one, the ACK pulse is generated on the TWI bus if the following conditions are met:

- 1. The device's own slave address has been received.

- 2. A general call has been received, while the TWGCE bit in the TWAR is set.

- 3. A data byte has been received in Master Receiver or Slave Receiver mode.

By writing the TWEA bit to zero, the device can be virtually disconnected from the 2-wire Serial Bus temporarily. Address recognition can then be resumed by writing the TWEA bit to one again.

## • Bit 5 – TWSTA: TWI START Condition Bit

The application writes the TWSTA bit to one when it desires to become a Master on the 2-wire Serial Bus. The TWI hardware checks if the bus is available, and generates a START condition on the bus if it is free. However, if the bus is not free, the TWI waits until a STOP condition is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted.

## • Bit 4 – TWSTO: TWI STOP Condition Bit

Writing the TWSTO bit to one in Master mode will generate a STOP condition on the 2-wire Serial Bus. When the STOP condition is executed on the bus, the TWSTO bit is cleared automatically. In Slave mode, setting the TWSTO bit can be used to recover from an error condition. This will not generate a STOP condition, but the TWI returns to a well-defined unaddressed Slave mode and releases the SCL and SDA lines to a high impedance state.

#### Bit 3 – TWWC: TWI Write Collision Flag

The TWWC bit is set when attempting to write to the TWI Data Register – TWDR when TWINT is low. This flag is cleared by writing the TWDR Register when TWINT is high.

#### • Bit 2 – TWEN: TWI Enable Bit

The TWEN bit enables TWI operation and activates the TWI interface. When TWEN is written to one, the TWI takes control over the I/O pins connected to the SCL and SDA pins, enabling the slew-rate limiters and spike filters. If this bit is written to zero, the TWI is switched off and all TWI transmissions are terminated, regardless of any ongoing operation.

#### • Bit 1 - Res: Reserved Bit

This bit is a reserved bit and will always read as zero.

#### • Bit 0 – TWIE: TWI Interrupt Enable

When this bit is written to one, and the I-bit in SREG is set, the TWI interrupt request will be activated for as long as the TWINT Flag is high.

A START condition is sent by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | тwwс | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

TWEN must be set to enable the 2-wire Serial Interface, TWSTA must be written to one to transmit a START condition and TWINT must be written to one to clear the TWINT Flag. The TWI will then test the 2-wire Serial Bus and generate a START condition as soon as the bus becomes free. After a START condition has been transmitted, the TWINT Flag is set by hardware, and the status code in TWSR will be 0x08 (see Table 19-3). In order to enter MT mode, SLA+W must be transmitted. This is done by writing SLA+W to TWDR. Thereafter the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

When SLA+W have been transmitted and an acknowledgement bit has been received, TWINT is set again and a number of status codes in TWSR are possible. Possible status codes in Master mode are 0x18, 0x20, or 0x38. The appropriate action to be taken for each of these status codes is detailed in Table 19-3.

When SLA+W has been successfully transmitted, a data packet should be transmitted. This is done by writing the data byte to TWDR. TWDR must only be written when TWINT is high. If not, the access will be discarded, and the Write Collision bit (TWWC) will be set in the TWCR Register. After updating TWDR, the TWINT bit should be cleared (by writing it to one) to continue the transfer. This is accomplished by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 0     | Х    | 1    | 0 | Х    |

This scheme is repeated until the last byte has been sent and the transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

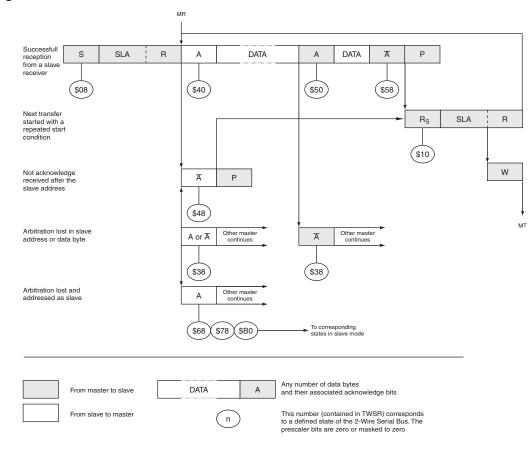

Figure 19-15. Formats and States in the Master Receiver Mode

#### 19.8.3 Slave Receiver Mode

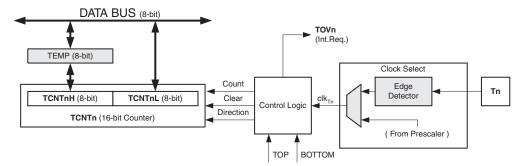

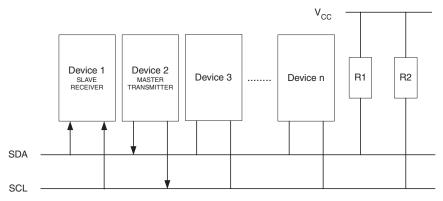

In the Slave Receiver mode, a number of data bytes are received from a Master Transmitter (see Figure 19-16). All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

Figure 19-16. Data transfer in Slave Receiver mode

To initiate the Slave Receiver mode, TWAR and TWCR must be initialized as follows:

| TWAR  | TWA6 | TWA5 | TWA4   | TWA3           | TWA2    | TWA1 | TWA0 | TWGCE |

|-------|------|------|--------|----------------|---------|------|------|-------|

| value |      |      | Device | 's Own Slave A | Address |      |      |       |

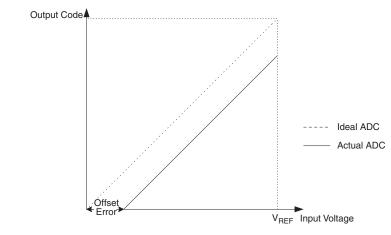

Figure 21-10. Offset Error

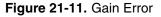

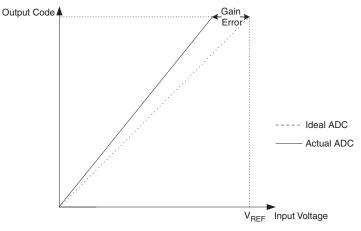

Gain error: After adjusting for offset, the gain error is found as the deviation of the last transition (0x3FE to 0x3FF) compared to the ideal transition (at 1.5 LSB below maximum). Ideal value: 0 LSB

• Integral Non-linearity (INL): After adjusting for offset and gain error, the INL is the maximum deviation of an actual transition compared to an ideal transition for any code. Ideal value: 0 LSB.

| Symbol            | Parameter                                  | Condition                                               | Min. <sup>(5)</sup> | Тур.       | Max. <sup>(5)</sup> | Units |

|-------------------|--------------------------------------------|---------------------------------------------------------|---------------------|------------|---------------------|-------|

| R <sub>RST</sub>  | Reset Pull-up Resistor                     |                                                         | 30                  |            | 60                  | kΩ    |

| R <sub>PU</sub>   | I/O Pin Pull-up Resistor                   |                                                         | 20                  |            | 50                  | kΩ    |

| I <sub>CC</sub>   | Power Supply Current <sup>(6)</sup>        | Active 1MHz, V <sub>CC</sub> = 2V<br>(ATmega48/88/168V) |                     |            | 0.55                | mA    |

|                   |                                            | Active 4MHz, V <sub>CC</sub> = 3V<br>(ATmega48/88/168L) |                     |            | 3.5                 | mA    |

|                   |                                            | Active 8MHz, V <sub>CC</sub> = 5V<br>(ATmega48/88/168)  |                     |            | 12                  | mA    |

|                   |                                            | Idle 1MHz, V <sub>CC</sub> = 2V<br>(ATmega48/88/168V)   |                     | 0.25       | 0.5                 | mA    |

|                   |                                            | Idle 4MHz, V <sub>CC</sub> = 3V<br>(ATmega48/88/168L)   |                     |            | 1.5                 | mA    |

|                   |                                            | Idle 8MHz, V <sub>CC</sub> = 5V<br>(ATmega48/88/168)    |                     |            | 5.5                 | mA    |

|                   | Power-down mode                            | WDT enabled, $V_{CC} = 3V$                              |                     | <8         | 15                  | μA    |

|                   |                                            | WDT disabled, $V_{CC} = 3V$                             |                     | <1         | 2                   | μA    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$                    |                     | <10        | 40                  | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$                    | -50                 |            | 50                  | nA    |

| t <sub>ACID</sub> | Analog Comparator<br>Propagation Delay     | $V_{CC} = 2.7V$ $V_{CC} = 4.0V$                         |                     | 750<br>500 |                     | ns    |

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low

2. "Min" means the lowest value where the pin is guaranteed to be read as high

Although each I/O port can sink more than the test conditions (20mA at V<sub>CC</sub> = 5V, 10mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- ATmega48:

- 1] The sum of all IOL, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOL, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOL, for ports B0 B7, D5 D7, should not exceed 100 mA.

- ATmega88/168:

- 1] The sum of all IOL, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOL, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOL, for ports B0 B7, D5 D7, should not exceed 100 mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

- Although each I/O port can source more than the test conditions (20mA at V<sub>CC</sub> = 5V, 10mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- ATmega48:

- 1] The sum of all IOH, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOH, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOH, for ports B0 B7, D5 D7, should not exceed 100 mA.

- ATmega88/168:

- 1] The sum of all IOH, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOH, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOH, for ports B0 B7, D5 D7, should not exceed 100 mA.

|    | 13.10verview                                             | 106 |

|----|----------------------------------------------------------|-----|

|    | 13.2Accessing 16-bit Registers                           | 108 |

|    | 13.3Timer/Counter Clock Sources                          | 111 |

|    | 13.4Counter Unit                                         | 112 |

|    | 13.5Input Capture Unit                                   | 113 |

|    | 13.6Output Compare Units                                 | 115 |

|    | 13.7Compare Match Output Unit                            | 117 |

|    | 13.8Modes of Operation                                   | 118 |

|    | 13.9Timer/Counter Timing Diagrams                        | 125 |

|    | 13.1016-bit Timer/Counter Register Description           | 128 |

| 14 | Timer/Counter0 and Timer/Counter1 Prescalers             | 135 |

| 15 | 8-bit Timer/Counter2 with PWM and Asynchronous Operation | 138 |

|    | 15.10verview                                             | 138 |

|    | 15.2Timer/Counter Clock Sources                          | 139 |

|    | 15.3Counter Unit                                         | 139 |

|    | 15.4Output Compare Unit                                  | 140 |

|    | 15.5Compare Match Output Unit                            | 142 |

|    | 15.6Modes of Operation                                   | 143 |

|    | 15.7Timer/Counter Timing Diagrams                        | 147 |

|    | 15.88-bit Timer/Counter Register Description             | 149 |

|    | 15.9Asynchronous operation of the Timer/Counter          | 155 |

|    | 15.10Timer/Counter Prescaler                             | 158 |

| 16 | Serial Peripheral Interface – SPI                        | 159 |

|    | 16.1SS Pin Functionality                                 | 164 |

|    | 16.2Data Modes                                           | 166 |

| 17 | USART0                                                   | 168 |

|    | 17.10verview                                             | 168 |

|    | 17.2Clock Generation                                     | 169 |

|    | 17.3Frame Formats                                        | 172 |

|    | 17.4USART Initialization                                 | 174 |

|    | 17.5Data Transmission – The USART Transmitter            | 176 |

|    | 17.6Data Reception – The USART Receiver                  | 178 |

|    | 17.7Asynchronous Data Reception                          | 182 |

|    | 17.8Multi-processor Communication Mode                   | 185 |

|    | 17.9USART Register Description                           | 187 |