#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 28-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48-20pj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.2 SRAM Data Memory

Figure 5-3 shows how the ATmega48/88/168 SRAM Memory is organized.

The ATmega48/88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

The lower 768/1280/1280 data memory locations address both the Register File, the I/O memory, Extended I/O memory, and the internal data SRAM. The first 32 locations address the Register File, the next 64 location the standard I/O memory, then 160 locations of Extended I/O memory, and the next 512/1024/1024 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, 160 Extended I/O Registers, and the 512/1024/1024 bytes of internal data SRAM in the ATmega48/88/168 are all accessible through all these addressing modes. The Register File is described in "General Purpose Register File" on page 10.

## Figure 5-3. Data Memory Map

## **Data Memory**

| 32 Registers<br>64 I/O Registers     | 0x0000 - 0x001F<br>0x0020 - 0x005F |

|--------------------------------------|------------------------------------|

| 160 Ext I/O Reg.                     | 0x0060 - 0x00FF                    |

|                                      | 0x0100                             |

| Internal SRAM<br>(512/1024/1024 x 8) |                                    |

|                                      | 0x02FF/0x04FF/0x04FF               |

## 5.2.1 Data Memory Access Times

This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two  $clk_{CPU}$  cycles as described in Figure 5-4.

When the write access time has elapsed, the EEPE bit is cleared by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEPE has been set, the CPU is halted for two cycles before the next instruction is executed.

# • Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEPE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

The calibrated Oscillator is used to time the EEPROM accesses. Table 5-2 lists the typical programming time for EEPROM access from the CPU.

Table 5-2.

EEPROM Programming Time

| Symbol                     | Number of Calibrated RC Oscillator Cycles | Typ Programming Time |

|----------------------------|-------------------------------------------|----------------------|

| EEPROM write<br>(from CPU) | 26,368                                    | 3.3 ms               |

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

purpose, it is recommended to write the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up.

# 7.1 Idle Mode

When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing the SPI, USART, Analog Comparator, ADC, 2-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts clk<sub>CPU</sub> and clk<sub>FLASH</sub>, while allowing the other clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is enabled, a conversion starts automatically when this mode is entered.

# 7.2 ADC Noise Reduction Mode

When the SM2..0 bits are written to 001, the SLEEP instruction makes the MCU enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external interrupts, the 2-wire Serial Interface address watch, Timer/Counter2, and the Watchdog to continue operating (if enabled). This sleep mode basically halts  $clk_{I/O}$ ,  $clk_{CPU}$ , and  $clk_{FLASH}$ , while allowing the other clocks to run.

This improves the noise environment for the ADC, enabling higher resolution measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered. Apart from the ADC Conversion Complete interrupt, only an External Reset, a Watchdog System Reset, a Watchdog Interrupt, a Brown-out Reset, a 2-wire Serial Interface address match, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt, an external level interrupt on INT0 or INT1 or a pin change interrupt can wake up the MCU from ADC Noise Reduction mode.

# 7.3 Power-down Mode

When the SM2..0 bits are written to 010, the SLEEP instruction makes the MCU enter Powerdown mode. In this mode, the external Oscillator is stopped, while the external interrupts, the 2wire Serial Interface address watch, and the Watchdog continue operating (if enabled). Only an External Reset, a Watchdog System Reset, a Watchdog Interrupt, a Brown-out Reset, a 2-wire Serial Interface address match, an external level interrupt on INT0 or INT1, or a pin change interrupt can wake up the MCU. This sleep mode basically halts all generated clocks, allowing operation of asynchronous modules only.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. Refer to "External Interrupts" on page 83 for details.

When waking up from Power-down mode, there is a delay from the wake-up condition occurs until the wake-up becomes effective. This allows the clock to restart and become stable after having been stopped. The wake-up period is defined by the same CKSEL Fuses that define the Reset Time-out period, as described in "Clock Sources" on page 26.

# 7.4 Power-save Mode

When the SM2..0 bits are written to 011, the SLEEP instruction makes the MCU enter Powersave mode. This mode is identical to Power-down, with one exception:

# 38 ATmega48/88/168

# 9.2 Interrupt Vectors in ATmega88

| Table 9-2. | Reset and Interrupt Vectors in ATmega88 |

|------------|-----------------------------------------|

|            | ricoot and michapt rootoro mirinogaoo   |

| Vector No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                    |

|------------|-----------------------------------|--------------|-------------------------------------------------------------------------|

| 1          | 0x000 <sup>(1)</sup>              | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2          | 0x001                             | INT0         | External Interrupt Request 0                                            |

| 3          | 0x002                             | INT1         | External Interrupt Request 1                                            |

| 4          | 0x003                             | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5          | 0x004                             | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6          | 0x005                             | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7          | 0x006                             | WDT          | Watchdog Time-out Interrupt                                             |

| 8          | 0x007                             | TIMER2 COMPA | Timer/Counter2 Compare Match A                                          |

| 9          | 0x008                             | TIMER2 COMPB | Timer/Counter2 Compare Match B                                          |

| 10         | 0x009                             | TIMER2 OVF   | Timer/Counter2 Overflow                                                 |

| 11         | 0x00A                             | TIMER1 CAPT  | Timer/Counter1 Capture Event                                            |

| 12         | 0x00B                             | TIMER1 COMPA | Timer/Counter1 Compare Match A                                          |

| 13         | 0x00C                             | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                          |

| 14         | 0x00D                             | TIMER1 OVF   | Timer/Counter1 Overflow                                                 |

| 15         | 0x00E                             | TIMER0 COMPA | Timer/Counter0 Compare Match A                                          |

| 16         | 0x00F                             | TIMER0 COMPB | Timer/Counter0 Compare Match B                                          |

| 17         | 0x010                             | TIMER0 OVF   | Timer/Counter0 Overflow                                                 |

| 18         | 0x011                             | SPI, STC     | SPI Serial Transfer Complete                                            |

| 19         | 0x012                             | USART, RX    | USART Rx Complete                                                       |

| 20         | 0x013                             | USART, UDRE  | USART, Data Register Empty                                              |

| 21         | 0x014                             | USART, TX    | USART, Tx Complete                                                      |

| 22         | 0x015                             | ADC          | ADC Conversion Complete                                                 |

| 23         | 0x016                             | EE READY     | EEPROM Ready                                                            |

| 24         | 0x017                             | ANALOG COMP  | Analog Comparator                                                       |

| 25         | 0x018                             | TWI          | 2-wire Serial Interface                                                 |

| 26         | 0x019                             | SPM READY    | Store Program Memory Ready                                              |

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at

reset, see "Boot Loader Support - Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264.

2. When the IVSEL bit in MCUCR is set, Interrupt Vectors will be moved to the start of the Boot Flash Section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash Section.

Table 9-3 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

2. When the IVSEL bit in MCUCR is set, Interrupt Vectors will be moved to the start of the Boot Flash Section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash Section.

Table 9-5 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

| BOOTRST | IVSEL | Reset Address      | Interrupt Vectors Start Address |

|---------|-------|--------------------|---------------------------------|

| 1       | 0     | 0x000              | 0x001                           |

| 1       | 1     | 0x000              | Boot Reset Address + 0x0002     |

| 0       | 0     | Boot Reset Address | 0x001                           |

| 0       | 1     | Boot Reset Address | Boot Reset Address + 0x0002     |

Table 9-5.

Reset and Interrupt Vectors Placement in ATmega168<sup>(1)</sup>

Note: 1. The Boot Reset Address is shown in Table 24-6 on page 276. For the BOOTRST Fuse "1" means unprogrammed while "0" means programmed.

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega168 is:

| Address Label | s Code |            | Comments                             |

|---------------|--------|------------|--------------------------------------|

| 0x0000        | jmp    | RESET      | ; Reset Handler                      |

| 0x0002        | jmp    | EXT_INT0   | ; IRQ0 Handler                       |

| 0x0004        | jmp    | EXT_INT1   | ; IRQ1 Handler                       |

| 0x0006        | jmp    | PCINT0     | ; PCINTO Handler                     |

| 0x0008        | jmp    | PCINT1     | ; PCINT1 Handler                     |

| A000x0        | jmp    | PCINT2     | ; PCINT2 Handler                     |

| 0x000C        | jmp    | WDT        | ; Watchdog Timer Handler             |

| 0x000E        | jmp    | TIM2_COMPA | ; Timer2 Compare A Handler           |

| 0x0010        | jmp    | TIM2_COMPB | ; Timer2 Compare B Handler           |

| 0x0012        | jmp    | TIM2_OVF   | ; Timer2 Overflow Handler            |

| 0x0014        | jmp    | TIM1_CAPT  | ; Timer1 Capture Handler             |

| 0x0016        | jmp    | TIM1_COMPA | ; Timer1 Compare A Handler           |

| 0x0018        | jmp    | TIM1_COMPB | ; Timer1 Compare B Handler           |

| 0x001A        | jmp    | TIM1_OVF   | ; Timer1 Overflow Handler            |

| 0x001C        | jmp    | TIM0_COMPA | ; Timer0 Compare A Handler           |

| 0x001E        | jmp    | TIM0_COMPB | ; Timer0 Compare B Handler           |

| 0x0020        | jmp    | TIM0_OVF   | ; Timer0 Overflow Handler            |

| 0x0022        | jmp    | SPI_STC    | ; SPI Transfer Complete Handler      |

| 0x0024        | jmp    | USART_RXC  | ; USART, RX Complete Handler         |

| 0x0026        | jmp    | USART_UDRE | ; USART, UDR Empty Handler           |

| 0x0028        | jmp    | USART_TXC  | ; USART, TX Complete Handler         |

| 0x002A        | jmp    | ADC        | ; ADC Conversion Complete Handler    |

| 0x002C        | jmp    | EE_RDY     | ; EEPROM Ready Handler               |

| 0x002E        | jmp    | ANA_COMP   | ; Analog Comparator Handler          |

| 0x0030        | jmp    | TWI        | ; 2-wire Serial Interface Handler    |

| 0x0032        | jmp    | SPM_RDY    | ; Store Program Memory Ready Handler |

|               |        |            |                                      |

# 60 ATmega48/88/168

# 10.4.9 The Port D Input Pins Address – PIND

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 | PIND |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R     | -    |

| Initial Value | N/A   |      |

# 11.1.1 External Interrupt Control Register A – EICRA

The External Interrupt Control Register A contains control bits for interrupt sense control.

| Bit           | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     | _     |

|---------------|---|---|---|---|-------|-------|-------|-------|-------|

|               | - | - | - | - | ISC11 | ISC10 | ISC01 | ISC00 | EICRA |

| Read/Write    | R | R | R | R | R/W   | R/W   | R/W   | R/W   | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0     | 0     | 0     | 0     |       |

## • Bit 7..4 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

## • Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 11-1. The value on the INT1 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

Table 11-1.

Interrupt 1 Sense Control

| ISC11 | ISC10 | Description                                                |  |  |  |

|-------|-------|------------------------------------------------------------|--|--|--|

| 0     | 0     | The low level of INT1 generates an interrupt request.      |  |  |  |

| 0     | 1     | Any logical change on INT1 generates an interrupt request. |  |  |  |

| 1     | 0     | The falling edge of INT1 generates an interrupt request.   |  |  |  |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.    |  |  |  |

### • Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 11-2. The value on the INT0 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

|       | •     |                                                            |  |  |  |

|-------|-------|------------------------------------------------------------|--|--|--|

| ISC01 | ISC00 | Description                                                |  |  |  |

| 0     | 0     | The low level of INT0 generates an interrupt request.      |  |  |  |

| 0     | 1     | Any logical change on INT0 generates an interrupt request. |  |  |  |

| 1     | 0     | The falling edge of INT0 generates an interrupt request.   |  |  |  |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.    |  |  |  |

Table 11-2.

Interrupt 0 Sense Control

# ATmega48/88/168

Note: 1. Refer to Figure 1-1 on page 2, Table 10-3 on page 71 and Table 10-9 on page 78 for Timer/Counter1 pin placement and description.

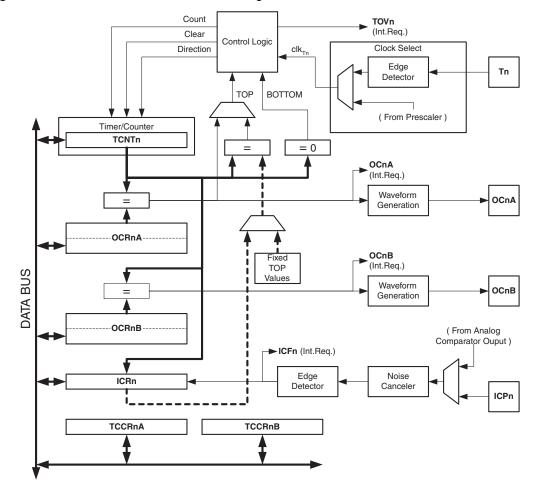

### 13.1.1 Registers

The *Timer/Counter* (TCNT1), *Output Compare Registers* (OCR1A/B), and *Input Capture Register* (ICR1) are all 16-bit registers. Special procedures must be followed when accessing the 16-bit registers. These procedures are described in the section "Accessing 16-bit Registers" on page 108. The *Timer/Counter Control Registers* (TCCR1A/B) are 8-bit registers and have no CPU access restrictions. Interrupt requests (abbreviated to Int.Req. in the figure) signals are all visible in the *Timer Interrupt Flag Register* (TIFR1). All interrupts are individually masked with the *Timer Interrupt Mask Register* (TIMSK1). TIFR1 and TIMSK1 are not shown in the figure.

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on the T1 pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock ( $clk_{T1}$ ).

The double buffered Output Compare Registers (OCR1A/B) are compared with the Timer/Counter value at all time. The result of the compare can be used by the Waveform Generator to generate a PWM or variable frequency output on the Output Compare pin (OC1A/B). See

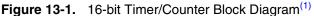

In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 15-6. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

Figure 15-6. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. (See Table 15-3 on page 149). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2x Register at the compare match between OCR2x and TCNT2, and clearing (or setting) the OC2x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clk\_I/O}}}{N \cdot 256}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM2A1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2x to toggle its logical level on each compare match (COM2x1:0 = 1). The waveform

generated will have a maximum frequency of  $f_{oc2} = f_{clk_l/O}/2$  when OCR2A is set to zero. This feature is similar to the OC2A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

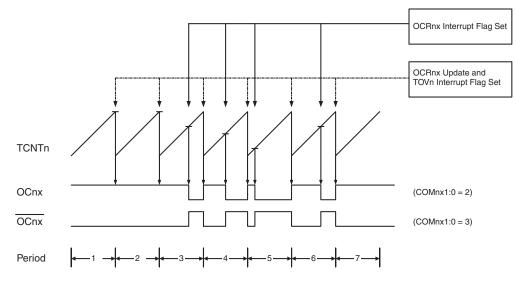

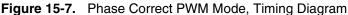

### 15.6.4 Phase Correct PWM Mode

The phase correct PWM mode (WGM22:0 = 1 or 5) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to TOP and then from TOP to BOT-TOM. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. In non-inverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x while upcounting, and set on the compare match while downcount-ing. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

In phase correct PWM mode the counter is incremented until the counter value matches TOP. When the counter reaches TOP, it changes the count direction. The TCNT2 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown on Figure 15-7. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value.

In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM. An inverted PWM

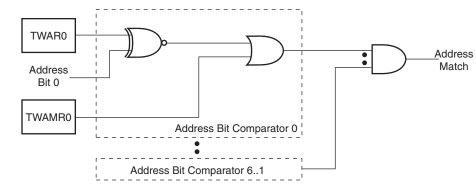

## Figure 19-10. TWI Address Match Logic, Block Diagram

## • Bit 0 - Res: Reserved Bit

This bit is an unused bit in the ATmega48/88/168, and will always read as zero.

# 19.7 Using the TWI

The AVR TWI is byte-oriented and interrupt based. Interrupts are issued after all bus events, like reception of a byte or transmission of a START condition. Because the TWI is interrupt-based, the application software is free to carry on other operations during a TWI byte transfer. Note that the TWI Interrupt Enable (TWIE) bit in TWCR together with the Global Interrupt Enable bit in SREG allow the application to decide whether or not assertion of the TWINT Flag should generate an interrupt request. If the TWIE bit is cleared, the application must poll the TWINT Flag in order to detect actions on the TWI bus.

When the TWINT Flag is asserted, the TWI has finished an operation and awaits application response. In this case, the TWI Status Register (TWSR) contains a value indicating the current state of the TWI bus. The application software can then decide how the TWI should behave in the next TWI bus cycle by manipulating the TWCR and TWDR Registers.

Figure 19-11 is a simple example of how the application can interface to the TWI hardware. In this example, a Master wishes to transmit a single data byte to a Slave. This description is quite abstract, a more detailed explanation follows later in this section. A simple code example implementing the desired behavior is also presented.

## • Bit 5 – ADATE: ADC Auto Trigger Enable

When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a conversion on a positive edge of the selected trigger signal. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in ADCSRB.

## • Bit 4 – ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the Data Registers are updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set. ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify-Write on ADCSRA, a pending interrupt can be disabled. This also applies if the SBI and CBI instructions are used.

## • Bit 3 – ADIE: ADC Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Interrupt is activated.

## • Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

These bits determine the division factor between the system clock frequency and the input clock to the ADC.

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

|-------|-------|-------|-----------------|

| 0     | 0     | 0     | 2               |

| 0     | 0     | 1     | 2               |

| 0     | 1     | 0     | 4               |

| 0     | 1     | 1     | 8               |

| 1     | 0     | 0     | 16              |

| 1     | 0     | 1     | 32              |

| 1     | 1     | 0     | 64              |

| 1     | 1     | 1     | 128             |

Table 21-4. ADC Prescaler Selections

# 22. debugWIRE On-chip Debug System

# 22.1 Features

- Complete Program Flow Control

- Emulates All On-chip Functions, Both Digital and Analog, except RESET Pin

- Real-time Operation

- Symbolic Debugging Support (Both at C and Assembler Source Level, or for Other HLLs)

- Unlimited Number of Program Break Points (Using Software Break Points)

- Non-intrusive Operation

- Electrical Characteristics Identical to Real Device

- Automatic Configuration System

- High-Speed Operation

- Programming of Non-volatile Memories

# 22.2 Overview

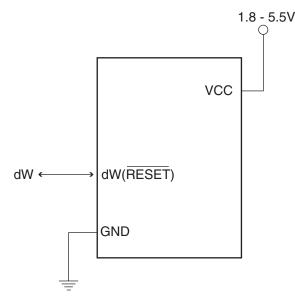

The debugWIRE On-chip debug system uses a One-wire, bi-directional interface to control the program flow, execute AVR instructions in the CPU and to program the different non-volatile memories.

# 22.3 Physical Interface

When the debugWIRE Enable (DWEN) Fuse is programmed and Lock bits are unprogrammed, the debugWIRE system within the target device is activated. The RESET port pin is configured as a wire-AND (open-drain) bi-directional I/O pin with pull-up enabled and becomes the communication gateway between target and emulator.

### Figure 22-1. The debugWIRE Setup

Figure 22-1 shows the schematic of a target MCU, with debugWIRE enabled, and the emulator connector. The system clock is not affected by debugWIRE and will always be the clock source selected by the CKSEL Fuses.

When designing a system where debugWIRE will be used, the following observations must be made for correct operation:

- Pull-up resistors on the dW/(RESET) line must not be smaller than 10kΩ. The pull-up resistor is not required for debugWIRE functionality.

- Connecting the RESET pin directly to V<sub>CC</sub> will not work.

- Capacitors connected to the RESET pin must be disconnected when using debugWire.

- All external reset sources must be disconnected.

## 22.4 Software Break Points

debugWIRE supports Program memory Break Points by the AVR Break instruction. Setting a Break Point in AVR Studio<sup>®</sup> will insert a BREAK instruction in the Program memory. The instruction replaced by the BREAK instruction will be stored. When program execution is continued, the stored instruction will be executed before continuing from the Program memory. A break can be inserted manually by putting the BREAK instruction in the program.

The Flash must be re-programmed each time a Break Point is changed. This is automatically handled by AVR Studio through the debugWIRE interface. The use of Break Points will therefore reduce the Flash Data retention. Devices used for debugging purposes should not be shipped to end customers.

# 22.5 Limitations of debugWIRE

The debugWIRE communication pin (dW) is physically located on the same pin as External Reset (RESET). An External Reset source is therefore not supported when the debugWIRE is enabled.

The debugWIRE system accurately emulates all I/O functions when running at full speed, i.e., when the program in the CPU is running. When the CPU is stopped, care must be taken while accessing some of the I/O Registers via the debugger (AVR Studio).

A programmed DWEN Fuse enables some parts of the clock system to be running in all sleep modes. This will increase the power consumption while in sleep. Thus, the DWEN Fuse should be disabled when debugWire is not used.

## 22.6 debugWIRE Related Register in I/O Memory

The following section describes the registers used with the debugWire.

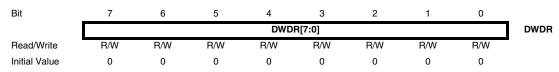

#### 22.6.1 debugWire Data Register – DWDR

The DWDR Register provides a communication channel from the running program in the MCU to the debugger. This register is only accessible by the debugWIRE and can therefore not be used as a general purpose register in the normal operations.

# 23. Self-Programming the Flash, ATmega48

In ATmega48, there is no Read-While-Write support, and no separate Boot Loader Section. The SPM instruction can be executed from the entire Flash.

# <sup>256</sup> **ATmega48/88/168**

## 23.1.1 Store Program Memory Control and Status Register – SPMCSR

The Store Program Memory Control and Status Register contains the control bits needed to control the Program memory operations.

| Bit           | 7     | 6     | 5 | 4      | 3      | 2     | 1     | 0         | _      |

|---------------|-------|-------|---|--------|--------|-------|-------|-----------|--------|

|               | SPMIE | RWWSB | - | RWWSRE | BLBSET | PGWRT | PGERS | SELFPRGEN | SPMCSR |

| Read/Write    | R/W   | R     | R | R/W    | R/W    | R/W   | R/W   | R/W       | •      |

| Initial Value | 0     | 0     | 0 | 0      | 0      | 0     | 0     | 0         |        |

## Bit 7 – SPMIE: SPM Interrupt Enable

When the SPMIE bit is written to one, and the I-bit in the Status Register is set (one), the SPM ready interrupt will be enabled. The SPM ready Interrupt will be executed as long as the SELF-PRGEN bit in the SPMCSR Register is cleared. The interrupt will not be generated during EEPROM write or SPM.

### • Bit 6 - RWWSB: Read-While-Write Section Busy

This bit is for compatibility with devices supporting Read-While-Write. It will always read as zero in ATmega48.

## • Bit 5 - Res: Reserved Bit

This bit is a reserved bit in the ATmega48/88/168 and will always read as zero.

### • Bit 4 – RWWSRE: Read-While-Write Section Read Enable

The functionality of this bit in ATmega48 is a subset of the functionality in ATmega88/168. If the RWWSRE bit is written while filling the temporary page buffer, the temporary page buffer will be cleared and the data will be lost.

## • Bit 3 – BLBSET: Boot Lock Bit Set

The functionality of this bit in ATmega48 is a subset of the functionality in ATmega88/168. An LPM instruction within three cycles after BLBSET and SELFPRGEN are set in the SPMCSR Register, will read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register. See "Reading the Fuse and Lock Bits from Software" on page 260 for details.

### • Bit 2 – PGWRT: Page Write

If this bit is written to one at the same time as SELFPRGEN, the next SPM instruction within four clock cycles executes Page Write, with the data stored in the temporary buffer. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGWRT bit will auto-clear upon completion of a Page Write, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

## • Bit 1 – PGERS: Page Erase

If this bit is written to one at the same time as SELFPRGEN, the next SPM instruction within four clock cycles executes Page Erase. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon completion of a Page Erase, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

shown below. Refer to Table 25-6 on page 282 for detailed description and mapping of the Fuse High byte.

Bit 7 6 5 3 2 0 4 1 Rd FHB7 FHB6 FHB5 FHB4 FHB3 FHB2 FHB1 FHB0

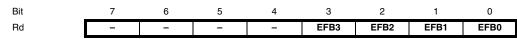

When reading the Extended Fuse byte, load 0x0002 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Extended Fuse byte (EFB) will be loaded in the destination register as shown below. Refer to Table 25-4 on page 281 for detailed description and mapping of the Extended Fuse byte.

Fuse and Lock bits that are programmed, will be read as zero. Fuse and Lock bits that are unprogrammed, will be read as one.

### 24.7.10 Preventing Flash Corruption

During periods of low  $V_{CC}$ , the Flash program can be corrupted because the supply voltage is too low for the CPU and the Flash to operate properly. These issues are the same as for board level systems using the Flash, and the same design solutions should be applied.

A Flash program corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the Flash requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage for executing instructions is too low.

Flash corruption can easily be avoided by following these design recommendations (one is sufficient):

- 1. If there is no need for a Boot Loader update in the system, program the Boot Loader Lock bits to prevent any Boot Loader software updates.

- 2. Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the SPMCSR Register and thus the Flash from unintentional writes.

### 24.7.11 Programming Time for Flash when Using SPM

The calibrated RC Oscillator is used to time Flash accesses. Table 24-5 shows the typical programming time for Flash accesses from the CPU.

#### **Table 24-5.**SPM Programming Time

| Symbol                                                           | Min Programming Time | Max Programming Time |  |  |

|------------------------------------------------------------------|----------------------|----------------------|--|--|

| Flash write (Page Erase, Page Write, and write Lock bits by SPM) | 3.7 ms               | 4.5 ms               |  |  |

Table 25-12. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                                |

|-----|-----|----------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (High or low address byte determined by BS1). |

| 0   | 1   | Load Data (High or Low data byte for Flash determined by BS1).             |

| 1   | 0   | Load Command                                                               |

| 1   | 1   | No Action, Idle                                                            |

Table 25-13. Command Byte Bit Coding

| Command Byte          | Command Executed                          |  |

|-----------------------|-------------------------------------------|--|

| 1000 0000             | Chip Erase                                |  |

| 0100 0000             | Write Fuse bits                           |  |

| 0010 0000             | Write Lock bits                           |  |

| 0001 0000             | Write Flash                               |  |

| 0001 0001             | Write EEPROM                              |  |

| 0000 1000             | Read Signature Bytes and Calibration byte |  |

| 0000 0100             | Read Fuse and Lock bits                   |  |

| 0000 0010             | Read Flash                                |  |

| 0000 0011 Read EEPROM |                                           |  |

# 25.7 Parallel Programming

### 25.7.1 Enter Programming Mode

The following algorithm puts the device in Parallel (High-voltage) Programming mode:

- 1. Set Prog\_enable pins listed in Table 25-11 on page 285 to "0000", RESET pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND.

Ensure that  $V_{CC}$  reaches at least 1.8V within the next 20  $\mu$ s.

- 3. Wait 20 60 µs, and apply 11.5 12.5V to RESET.

- 4. Keep the Prog\_enable pins unchanged for at least 10µs after the High-voltage has been applied to ensure the Prog\_enable Signature has been latched.

- 5. Wait at least 300 µs before giving any parallel programming commands.

- 6. Exit Programming mode by power the device down or by bringing RESET pin to 0V.

If the rise time of the  $V_{CC}$  is unable to fulfill the requirements listed above, the following alternative algorithm can be used.

- 1. Set Prog\_enable pins listed in Table 25-11 on page 285 to "0000", RESET pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND.

- 3. Monitor  $V_{CC}$ , and as soon as  $V_{CC}$  reaches 0.9 1.1V, apply 11.5 12.5V to RESET.

## Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |           | Instructio        | on Format         |                   |                                                                                                                                          |  |

|-------------------------------------------|-----------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction                               | Byte 1    | Byte 2            | Byte 2 Byte 3     |                   | Operation                                                                                                                                |  |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001 | 0000 0000         | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |  |

| Write EEPROM Memory<br>Page (page access) | 1100 0010 | 00xx xx <b>aa</b> | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |  |

| Read Lock bits                            | 0101 1000 | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |  |

| Write Lock bits                           | 1010 1100 | 111x xxxx         | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |  |

| Read Signature Byte                       | 0011 0000 | 000x xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |  |

| Write Fuse bits                           | 1010 1100 | 1010 0000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |  |

| Write Fuse High bits                      | 1010 1100 | 1010 1000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |  |

| Write Extended Fuse Bits                  | 1010 1100 | 1010 0100         | xxxx xxxx         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |  |

| Read Fuse bits                            | 0101 0000 | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |  |

| Read Fuse High bits                       | 0101 1000 | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |  |

| Read Extended Fuse Bits                   | 0101 0000 | 0000 1000         | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |  |

| Read Calibration Byte                     | 0011 1000 | 000x xxxx         | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |  |

| Poll RDY/BSY                              | 1111 0000 | 0000 0000         | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |  |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

## 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

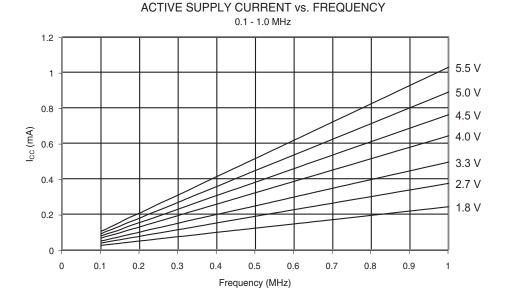

# 27. ATmega48/88/168 Typical Characteristics – Preliminary Data

The following charts show typical behavior. These figures are not tested during manufacturing. All current consumption measurements are performed with all I/O pins configured as inputs and with internal pull-ups enabled. A square wave generator with rail-to-rail output is used as clock source.

All Active- and Idle current consumption measurements are done with all bits in the PRR register set and thus, the corresponding I/O modules are turned off. Also the Analog Comparator is disabled during these measurements. Table 27-1 on page 313 and Table 27-2 on page 314 show the additional current consumption compared to  $I_{CC}$  Active and  $I_{CC}$  Idle for every I/O module controlled by the Power Reduction Register. See "Power Reduction Register" on page 39 for details.

The power consumption in Power-down mode is independent of clock selection.

The current consumption is a function of several factors such as: operating voltage, operating frequency, loading of I/O pins, switching rate of I/O pins, code executed and ambient temperature. The dominating factors are operating voltage and frequency.

The current drawn from capacitive loaded pins may be estimated (for one pin) as  $C_L V_{CC}$  f where  $C_L$  = load capacitance,  $V_{CC}$  = operating voltage and f = average switching frequency of I/O pin.

The parts are characterized at frequencies higher than test limits. Parts are not guaranteed to function properly at frequencies higher than the ordering code indicates.

The difference between current consumption in Power-down mode with Watchdog Timer enabled and Power-down mode with Watchdog Timer disabled represents the differential current drawn by the Watchdog Timer.

# 27.1 Active Supply Current

Figure 27-1. Active Supply Current vs. Frequency (0.1 - 1.0 MHz)

# 33. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

# 33.1 Rev. 2545E-02/05

- 1. MLF-package alternative changed to "Quad Flat No-Lead/Micro Lead Frame Package QFN/MLF".

- 2. Updated "The EEPROM Control Register EECR" on page 19.

- 3. Updated "Calibrated Internal RC Oscillator" on page 31.

- 4. Updated "External Clock" on page 33.

- 5. Updated Table 8-1 on page 44, Table 26-3 on page 304, Table 26-1 on page 301and Table 25-16 on page 297

- 6. Added "Pin Change Interrupt Timing" on page 83

- 7. Updated "8-bit Timer/Counter Block Diagram" on page 88.

- 8. Updated "Store Program Memory Control and Status Register SPMCSR" on page 259.

- 9. Updated "Enter Programming Mode" on page 286.

- 10. Updated "DC Characteristics" on page 299.

- 11. Updated "Ordering Information" on page 341.

- 12. Updated "Errata ATmega88" on page 348 and "Errata ATmega168" on page 349.

# 33.2 Rev. 2545D-07/04

- 1. Updated instructions used with WDTCSR in relevant code examples.

- 2. Updated Table 6-5 on page 29, Table 8-2 on page 46, Table 24-9 on page 278, and Table 24-11 on page 279.

- 3. Updated "System Clock Prescaler" on page 34.

- Moved "Timer/Counter2 Interrupt Mask Register TIMSK2" and "Timer/Counter2 Interrupt Flag Register – TIFR2" to "8-bit Timer/Counter Register Description" on page 149.

- 5. Updated cross-reference in "Electrical Interconnection" on page 206.

- 6. Updated equation in "Bit Rate Generator Unit" on page 211.

- 7. Added "Page Size" on page 284.

- 8. Updated "Serial Programming Algorithm" on page 296.

- 9. Updated Ordering Information for "ATmega168" on page 343.

- 10. Updated "Errata ATmega88" on page 348 and "Errata ATmega168" on page 349.

- 11. Updated equation in "Bit Rate Generator Unit" on page 211.

## 33.3 Rev. 2545C-04/04

- 1. Speed Grades changed: 12MHz to 10MHz and 24MHz to 20MHz

- 2. Updated "Maximum Speed vs. VCC" on page 301.

- 3. Updated "Ordering Information" on page 341.

- 4. Updated "Errata ATmega88" on page 348.

# 350 ATmega48/88/168