Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | AVR                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 10MHz                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 4KB (2K x 16)                                             |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 256 x 8                                                   |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 32-TQFP                                                   |

| Supplier Device Package    | 32-TQFP (7x7)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega48v-10ai |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

purpose, it is recommended to write the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up.

## 7.1 Idle Mode

When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing the SPI, USART, Analog Comparator, ADC, 2-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts clk<sub>CPU</sub> and clk<sub>FLASH</sub>, while allowing the other clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is enabled, a conversion starts automatically when this mode is entered.

## 7.2 ADC Noise Reduction Mode

When the SM2..0 bits are written to 001, the SLEEP instruction makes the MCU enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external interrupts, the 2-wire Serial Interface address watch, Timer/Counter2, and the Watchdog to continue operating (if enabled). This sleep mode basically halts  $clk_{I/O}$ ,  $clk_{CPU}$ , and  $clk_{FLASH}$ , while allowing the other clocks to run.

This improves the noise environment for the ADC, enabling higher resolution measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered. Apart from the ADC Conversion Complete interrupt, only an External Reset, a Watchdog System Reset, a Watchdog Interrupt, a Brown-out Reset, a 2-wire Serial Interface address match, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt, an external level interrupt on INT0 or INT1 or a pin change interrupt can wake up the MCU from ADC Noise Reduction mode.

## 7.3 Power-down Mode

When the SM2..0 bits are written to 010, the SLEEP instruction makes the MCU enter Powerdown mode. In this mode, the external Oscillator is stopped, while the external interrupts, the 2wire Serial Interface address watch, and the Watchdog continue operating (if enabled). Only an External Reset, a Watchdog System Reset, a Watchdog Interrupt, a Brown-out Reset, a 2-wire Serial Interface address match, an external level interrupt on INT0 or INT1, or a pin change interrupt can wake up the MCU. This sleep mode basically halts all generated clocks, allowing operation of asynchronous modules only.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. Refer to "External Interrupts" on page 83 for details.

When waking up from Power-down mode, there is a delay from the wake-up condition occurs until the wake-up becomes effective. This allows the clock to restart and become stable after having been stopped. The wake-up period is defined by the same CKSEL Fuses that define the Reset Time-out period, as described in "Clock Sources" on page 26.

## 7.4 Power-save Mode

When the SM2..0 bits are written to 011, the SLEEP instruction makes the MCU enter Powersave mode. This mode is identical to Power-down, with one exception:

# 38 ATmega48/88/168

Table 10-7 and Table 10-8 relate the alternate functions of Port C to the overriding signals shown in Figure 10-5 on page 69.

| Signal<br>Name | PC6/RESET/PCINT14             | PC5/SCL/ADC5/PCINT13    | PC4/SDA/ADC4/PCINT12    |

|----------------|-------------------------------|-------------------------|-------------------------|

| PUOE           | RSTDISBL                      | TWEN                    | TWEN                    |

| PUOV           | 1                             | PORTC5 • PUD            | PORTC4 • PUD            |

| DDOE           | RSTDISBL                      | TWEN                    | TWEN                    |

| DDOV           | 0                             | SCL_OUT                 | SDA_OUT                 |

| PVOE           | 0                             | TWEN                    | TWEN                    |

| PVOV           | 0                             | 0                       | 0                       |

| DIEOE          | RSTDISBL + PCINT14 •<br>PCIE1 | PCINT13 • PCIE1 + ADC5D | PCINT12 • PCIE1 + ADC4D |

| DIEOV          | RSTDISBL                      | PCINT13 • PCIE1         | PCINT12 • PCIE1         |

| DI             | PCINT14 INPUT                 | PCINT13 INPUT           | PCINT12 INPUT           |

| AIO            | RESET INPUT                   | ADC5 INPUT / SCL INPUT  | ADC4 INPUT / SDA INPUT  |

Table 10-7.

Overriding Signals for Alternate Functions in PC6..PC4<sup>(1)</sup>

Note: 1. When enabled, the 2-wire Serial Interface enables slew-rate controls on the output pins PC4 and PC5. This is not shown in the figure. In addition, spike filters are connected between the AIO outputs shown in the port figure and the digital logic of the TWI module.

| Signal<br>Name | PC3/ADC3/<br>PCINT11       | PC2/ADC2/<br>PCINT10       | PC1/ADC1/<br>PCINT9       | PC0/ADC0/<br>PCINT8       |

|----------------|----------------------------|----------------------------|---------------------------|---------------------------|

| PUOE           | 0                          | 0                          | 0                         | 0                         |

| PUOV           | 0                          | 0                          | 0                         | 0                         |

| DDOE           | 0                          | 0                          | 0                         | 0                         |

| DDOV           | 0                          | 0                          | 0                         | 0                         |

| PVOE           | 0                          | 0                          | 0                         | 0                         |

| PVOV           | 0                          | 0                          | 0                         | 0                         |

| DIEOE          | PCINT11 • PCIE1 +<br>ADC3D | PCINT10 • PCIE1 +<br>ADC2D | PCINT9 • PCIE1 +<br>ADC1D | PCINT8 • PCIE1 +<br>ADC0D |

| DIEOV          | PCINT11 • PCIE1            | PCINT10 • PCIE1            | PCINT9 • PCIE1            | PCINT8 • PCIE1            |

| DI             | PCINT11 INPUT              | PCINT10 INPUT              | PCINT9 INPUT              | PCINT8 INPUT              |

| AIO            | ADC3 INPUT                 | ADC2 INPUT                 | ADC1 INPUT                | ADC0 INPUT                |

#### • T1/OC0B/PCINT21 - Port D, Bit 5

T1, Timer/Counter1 counter source.

OC0B, Output Compare Match output: The PD5 pin can serve as an external output for the Timer/Counter0 Compare Match B. The PD5 pin has to be configured as an output (DDD5 set (one)) to serve this function. The OC0B pin is also the output pin for the PWM mode timer function.

PCINT21: Pin Change Interrupt source 21. The PD5 pin can serve as an external interrupt source.

#### • XCK/T0/PCINT20 - Port D, Bit 4

XCK, USART external clock.

T0, Timer/Counter0 counter source.

PCINT20: Pin Change Interrupt source 20. The PD4 pin can serve as an external interrupt source.

#### • INT1/OC2B/PCINT19 - Port D, Bit 3

INT1, External Interrupt source 1: The PD3 pin can serve as an external interrupt source.

OC2B, Output Compare Match output: The PD3 pin can serve as an external output for the Timer/Counter0 Compare Match B. The PD3 pin has to be configured as an output (DDD3 set (one)) to serve this function. The OC2B pin is also the output pin for the PWM mode timer function.

PCINT19: Pin Change Interrupt source 19. The PD3 pin can serve as an external interrupt source.

#### • INT0/PCINT18 - Port D, Bit 2

INTO, External Interrupt source 0: The PD2 pin can serve as an external interrupt source.

PCINT18: Pin Change Interrupt source 18. The PD2 pin can serve as an external interrupt source.

#### • TXD/PCINT17 – Port D, Bit 1

TXD, Transmit Data (Data output pin for the USART). When the USART Transmitter is enabled, this pin is configured as an output regardless of the value of DDD1.

PCINT17: Pin Change Interrupt source 17. The PD1 pin can serve as an external interrupt source.

#### • RXD/PCINT16 – Port D, Bit 0

RXD, Receive Data (Data input pin for the USART). When the USART Receiver is enabled this pin is configured as an input regardless of the value of DDD0. When the USART forces this pin to be an input, the pull-up can still be controlled by the PORTD0 bit.

PCINT16: Pin Change Interrupt source 16. The PD0 pin can serve as an external interrupt source.

Table 10-10 and Table 10-11 relate the alternate functions of Port D to the overriding signals shown in Figure 10-5 on page 69.

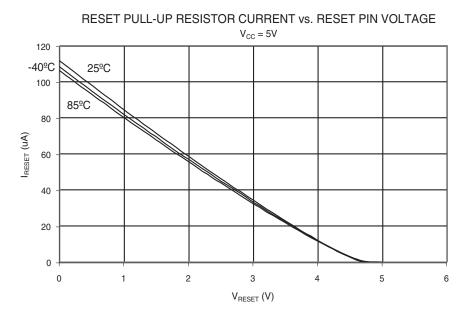

#### Figure 12-2. Counter Unit Block Diagram

Signal description (internal signals):

| count             | Increment or decrement TCNT0 by 1.                               |

|-------------------|------------------------------------------------------------------|

| direction         | Select between increment and decrement.                          |

| clear             | Clear TCNT0 (set all bits to zero).                              |

| clk <sub>Tn</sub> | Timer/Counter clock, referred to as $clk_{T0}$ in the following. |

| top               | Signalize that TCNT0 has reached maximum value.                  |

| bottom            | Signalize that TCNT0 has reached minimum value (zero).           |

Depending of the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T0}$ ).  $clk_{T0}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS02:0). When no clock source is selected (CS02:0 = 0) the timer is stopped. However, the TCNT0 value can be accessed by the CPU, regardless of whether  $clk_{T0}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM01 and WGM00 bits located in the Timer/Counter Control Register (TCCR0A) and the WGM02 bit located in the Timer/Counter Control Register B (TCCR0B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC0A and OC0B. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 93.

The Timer/Counter Overflow Flag (TOV0) is set according to the mode of operation selected by the WGM02:0 bits. TOV0 can be used for generating a CPU interrupt.

## 12.4 Output Compare Unit

The 8-bit comparator continuously compares TCNT0 with the Output Compare Registers (OCR0A and OCR0B). Whenever TCNT0 equals OCR0A or OCR0B, the comparator signals a match. A match will set the Output Compare Flag (OCF0A or OCF0B) at the next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare Flag generates an Output Compare interrupt. The Output Compare Flag is automatically cleared when the interrupt is executed. Alternatively, the flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the WGM02:0 bits and Compare Output mode (COM0x1:0) bits. The max and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation ("Modes of Operation" on page 93).

Figure 12-3 shows a block diagram of the Output Compare unit.

```

Assembly Code Example<sup>(1)</sup>

```

```

TIM16_WriteTCNT1:

; Save global interrupt flag

in r18,SREG

; Disable interrupts

cli

; Set TCNT1 to r17:r16

out TCNT1H,r17

out TCNT1L,r16

; Restore global interrupt flag

out SREG,r18

ret

```

C Code Example<sup>(1)</sup>

```

void TIM16_WriteTCNT1( unsigned int i )

{

unsigned char sreg;

unsigned int i;

/* Save global interrupt flag */

sreg = SREG;

/* Disable interrupts */

_CLI();

/* Set TCNT1 to i */

TCNT1 = i;

/* Restore global interrupt flag */

SREG = sreg;

}

```

See "About Code Examples" on page 6. For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example requires that the r17:r16 register pair contains the value to be written to TCNT1.

## 13.2.1 Reusing the Temporary High Byte Register

Note:

If writing to more than one 16-bit register where the high byte is the same for all registers written, then the high byte only needs to be written once. However, note that the same rule of atomic operation described previously also applies in this case.

## 13.3 Timer/Counter Clock Sources

The Timer/Counter can be clocked by an internal or an external clock source. The clock source is selected by the Clock Select logic which is controlled by the *Clock Select* (CS12:0) bits located in the *Timer/Counter control Register B* (TCCR1B). For details on clock sources and prescaler, see "Timer/Counter0 and Timer/Counter1 Prescalers" on page 135.

When the ICR1 is used as TOP value (see description of the WGM13:0 bits located in the TCCR1A and the TCCR1B Register), the ICP1 is disconnected and consequently the Input Capture function is disabled.

#### • Bit 5 – Reserved Bit

This bit is reserved for future use. For ensuring compatibility with future devices, this bit must be written to zero when TCCR1B is written.

#### • Bit 4:3 – WGM13:2: Waveform Generation Mode

See TCCR1A Register description.

#### • Bit 2:0 - CS12:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter, see Figure 13-10 and Figure 13-11.

| CS12 | CS11 | CS10 | Description                                             |  |  |  |  |

|------|------|------|---------------------------------------------------------|--|--|--|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |  |  |  |  |

| 0    | 0    | 1    | clk <sub>I/O</sub> /1 (No prescaling)                   |  |  |  |  |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |  |  |  |  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |  |  |  |  |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |  |  |  |  |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |  |  |  |  |

| 1    | 1    | 0    | External clock source on T1 pin. Clock on falling edge. |  |  |  |  |

| 1    | 1    | 1    | External clock source on T1 pin. Clock on rising edge.  |  |  |  |  |

Table 13-5. Clock Select Bit Description

If external pin modes are used for the Timer/Counter1, transitions on the T1 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

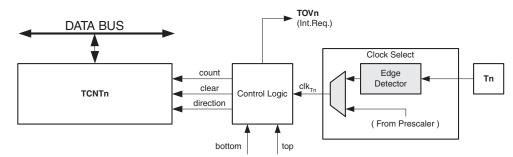

## 13.10.3 Timer/Counter1 Control Register C – TCCR1C

#### • Bit 7 – FOC1A: Force Output Compare for Channel A

## • Bit 6 – FOC1B: Force Output Compare for Channel B

The FOC1A/FOC1B bits are only active when the WGM13:0 bits specifies a non-PWM mode. However, for ensuring compatibility with future devices, these bits must be set to zero when TCCR1A is written when operating in a PWM mode. When writing a logical one to the FOC1A/FOC1B bit, an immediate compare match is forced on the Waveform Generation unit. The OC1A/OC1B output is changed according to its COM1x1:0 bits setting. Note that the FOC1A/FOC1B bits are implemented as strobes. Therefore it is the value present in the COM1x1:0 bits that determine the effect of the forced compare.

# ATmega48/88/168

The following code example shows a simple USART receive function based on polling of the Receive Complete (RXCn) Flag. When using frames with less than eight bits the most significant bits of the data read from the UDRn will be masked to zero. The USART has to be initialized before the function can be used.

```

Assembly Code Example<sup>(1)</sup>

```

```

USART_Receive:

; Wait for data to be received

sbis UCSRNA, RXCn

rjmp USART_Receive

; Get and return received data from buffer

in r16, UDRn

ret

```

C Code Example<sup>(1)</sup>

```

unsigned char USART_Receive( void )

{

/* Wait for data to be received */

while ( !(UCSRnA & (1<<RXCn)) )

;

/* Get and return received data from buffer */

return UDRn;

}</pre>

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The function simply waits for data to be present in the receive buffer by checking the RXCn Flag, before reading the buffer and returning the value.

## 17.6.2 Receiving Frames with 9 Data Bits

If 9-bit characters are used (UCSZn=7) the ninth bit must be read from the RXB8n bit in UCS-RnB **before** reading the low bits from the UDRn. This rule applies to the FEn, DORn and UPEn Status Flags as well. Read status from UCSRnA, then data from UDRn. Reading the UDRn I/O location will change the state of the receive buffer FIFO and consequently the TXB8n, FEn, DORn and UPEn bits, which all are stored in the FIFO, will change.

The following code example shows a simple USART receive function that handles both nine bit characters and the status bits.

UDREn is set after a reset to indicate that the Transmitter is ready.

#### • Bit 4 – FEn: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when received. I.e., when the first stop bit of the next character in the receive buffer is zero. This bit is valid until the receive buffer (UDRn) is read. The FEn bit is zero when the stop bit of received data is one. Always set this bit to zero when writing to UCSRnA.

#### • Bit 3 – DORn: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the Receive Shift Register, and a new start bit is detected. This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

#### • Bit 2 – UPEn: USART Parity Error

This bit is set if the next character in the receive buffer had a Parity Error when received and the Parity Checking was enabled at that point (UPMn1 = 1). This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

#### • Bit 1 – U2Xn: Double the USART Transmission Speed

This bit only has effect for the asynchronous operation. Write this bit to zero when using synchronous operation.

Writing this bit to one will reduce the divisor of the baud rate divider from 16 to 8 effectively doubling the transfer rate for asynchronous communication.

#### • Bit 0 – MPCMn: Multi-processor Communication Mode

This bit enables the Multi-processor Communication mode. When the MPCMn bit is written to one, all the incoming frames received by the USART Receiver that do not contain address information will be ignored. The Transmitter is unaffected by the MPCMn setting. For more detailed information see "Multi-processor Communication Mode" on page 185.

#### 17.9.3 USART Control and Status Register n B – UCSRnB

| Bit           | 7      | 6      | 5      | 4     | 3     | 2      | 1     | 0     | _      |

|---------------|--------|--------|--------|-------|-------|--------|-------|-------|--------|

|               | RXCIEn | TXCIEn | UDRIEn | RXENn | TXENn | UCSZn2 | RXB8n | TXB8n | UCSRnB |

| Read/Write    | R/W    | R/W    | R/W    | R/W   | R/W   | R/W    | R     | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0     | 0     | 0      | 0     | 0     |        |

#### Bit 7 – RXCIEn: RX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the RXCn Flag. A USART Receive Complete interrupt will be generated only if the RXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXCn bit in UCSRnA is set.

#### • Bit 6 – TXCIEn: TX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the TXCn Flag. A USART Transmit Complete interrupt will be generated only if the TXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXCn bit in UCSRnA is set.

|                       | f <sub>osc</sub> = 1.0000 MHz |        |           |          | f <sub>osc</sub> = 1.8432 MHz |          |           |          | f <sub>osc</sub> = 2.0000 MHz |          |           |          |  |

|-----------------------|-------------------------------|--------|-----------|----------|-------------------------------|----------|-----------|----------|-------------------------------|----------|-----------|----------|--|

| Baud<br>Rate<br>(bps) | U2Xn = 0                      |        | U2X       | U2Xn = 1 |                               | U2Xn = 0 |           | U2Xn = 1 |                               | U2Xn = 0 |           | U2Xn = 1 |  |

|                       | UBRR<br>n                     | Error  | UBRR<br>n | Error    | UBRR<br>n                     | Error    | UBRR<br>n | Error    | UBRR<br>n                     | Error    | UBRR<br>n | Error    |  |

| 2400                  | 25                            | 0.2%   | 51        | 0.2%     | 47                            | 0.0%     | 95        | 0.0%     | 51                            | 0.2%     | 103       | 0.2%     |  |

| 4800                  | 12                            | 0.2%   | 25        | 0.2%     | 23                            | 0.0%     | 47        | 0.0%     | 25                            | 0.2%     | 51        | 0.2%     |  |

| 9600                  | 6                             | -7.0%  | 12        | 0.2%     | 11                            | 0.0%     | 23        | 0.0%     | 12                            | 0.2%     | 25        | 0.2%     |  |

| 14.4k                 | 3                             | 8.5%   | 8         | -3.5%    | 7                             | 0.0%     | 15        | 0.0%     | 8                             | -3.5%    | 16        | 2.1%     |  |

| 19.2k                 | 2                             | 8.5%   | 6         | -7.0%    | 5                             | 0.0%     | 11        | 0.0%     | 6                             | -7.0%    | 12        | 0.2%     |  |

| 28.8k                 | 1                             | 8.5%   | 3         | 8.5%     | 3                             | 0.0%     | 7         | 0.0%     | 3                             | 8.5%     | 8         | -3.5%    |  |

| 38.4k                 | 1                             | -18.6% | 2         | 8.5%     | 2                             | 0.0%     | 5         | 0.0%     | 2                             | 8.5%     | 6         | -7.0%    |  |

| 57.6k                 | 0                             | 8.5%   | 1         | 8.5%     | 1                             | 0.0%     | 3         | 0.0%     | 1                             | 8.5%     | 3         | 8.5%     |  |

| 76.8k                 | _                             | _      | 1         | -18.6%   | 1                             | -25.0%   | 2         | 0.0%     | 1                             | -18.6%   | 2         | 8.5%     |  |

| 115.2k                | _                             | _      | 0         | 8.5%     | 0                             | 0.0%     | 1         | 0.0%     | 0                             | 8.5%     | 1         | 8.5%     |  |

| 230.4k                | _                             | _      | _         | _        | -                             | _        | 0         | 0.0%     | _                             | -        | _         | -        |  |

| 250k                  | _                             | _      | _         | -        | -                             | _        | -         | _        | -                             | -        | 0         | 0.0%     |  |

| Max. <sup>(1)</sup>   | 62.5                          | kbps   | 125       | kbps     | 115.2                         | 2 kbps   | 230.4     | l kbps   | 125                           | kbps     | 250       | kbps     |  |

Table 17-9.

Examples of UBRRn Settings for Commonly Used Oscillator Frequencies

Note: 1. UBRRn = 0, Error = 0.0%

# **19. 2-wire Serial Interface**

# 19.1 Features

- Simple Yet Powerful and Flexible Communication Interface, only two Bus Lines Needed

- Both Master and Slave Operation Supported

- Device can Operate as Transmitter or Receiver

- 7-bit Address Space Allows up to 128 Different Slave Addresses

- Multi-master Arbitration Support

- Up to 400 kHz Data Transfer Speed

- Slew-rate Limited Output Drivers

- Noise Suppression Circuitry Rejects Spikes on Bus Lines

- Fully Programmable Slave Address with General Call Support

- Address Recognition Causes Wake-up When AVR is in Sleep Mode

# 19.2 2-wire Serial Interface Bus Definition

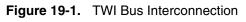

The 2-wire Serial Interface (TWI) is ideally suited for typical microcontroller applications. The TWI protocol allows the systems designer to interconnect up to 128 different devices using only two bi-directional bus lines, one for clock (SCL) and one for data (SDA). The only external hardware needed to implement the bus is a single pull-up resistor for each of the TWI bus lines. All devices connected to the bus have individual addresses, and mechanisms for resolving bus contention are inherent in the TWI protocol.

## 19.2.1 TWI Terminology

The following definitions are frequently encountered in this section.

| Table 19-1. | TWI Terminology                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------|

| Term        | Description                                                                                       |

| Master      | The device that initiates and terminates a transmission. The Master also generates the SCL clock. |

| Slave       | The device addressed by a Master.                                                                 |

| Transmitter | The device placing data on the bus.                                                               |

| Receiver    | The device reading data from the bus.                                                             |

#### 21.4.1 ADC Input Channels

When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:

In Single Conversion mode, always select the channel before starting the conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the conversion to complete before changing the channel selection.

In Free Running mode, always select the channel before starting the first conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the first conversion to complete, and then change the channel selection. Since the next conversion has already started automatically, the next result will reflect the previous channel selection. Subsequent conversions will reflect the new channel selection.

#### 21.4.2 ADC Voltage Reference

The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed  $V_{REF}$  will result in codes close to 0x3FF.  $V_{REF}$  can be selected as either AV<sub>CC</sub>, internal 1.1V reference, or external AREF pin.

$AV_{CC}$  is connected to the ADC through a passive switch. The internal 1.1V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground.  $V_{REF}$  can also be measured at the AREF pin with a high impedant voltmeter. Note that  $V_{REF}$  is a high impedant source, and only a capacitive load should be connected in a system.

If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between  $AV_{CC}$  and 1.1V as reference selection. The first ADC conversion result after switching reference voltage source may be inaccurate, and the user is advised to discard this result.

## 21.5 ADC Noise Canceler

The ADC features a noise canceler that enables conversion during sleep mode to reduce noise induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC Noise Reduction and Idle mode. To make use of this feature, the following procedure should be used:

- a. Make sure that the ADC is enabled and is not busy converting. Single Conversion mode must be selected and the ADC conversion complete interrupt must be enabled.

- b. Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion once the CPU has been halted.

- c. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine. If another interrupt wakes up the CPU before the ADC conversion is complete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed.

Note that the ADC will not be automatically turned off when entering other sleep modes than Idle mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before entering such sleep modes to avoid excessive power consumption.

# ATmega48/88/168

```

; return to RWW section

; verify that RWW section is safe to read

Return:

in

temp1, SPMCSR

sbrs temp1, RWWSB

; If RWWSB is set, the RWW section is not ready yet

ret

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SELFPRGEN)

rcallDo_spm

rjmp Return

Do_spm:

; check for previous SPM complete

Wait_spm:

in temp1, SPMCSR

sbrc temp1, SELFPRGEN

rjmp Wait_spm

; input: spmcrval determines SPM action

; disable interrupts if enabled, store status

in

temp2, SREG

cli

; check that no EEPROM write access is present

Wait_ee:

sbic EECR, EEPE

rjmp Wait_ee

; SPM timed sequence

out SPMCSR, spmcrval

spm

; restore SREG (to enable interrupts if originally enabled)

out SREG, temp2

ret

```

the RWWSB by writing the RWWSRE. See "Simple Assembly Code Example for a Boot Loader" on page 275 for an example.

#### 24.7.7 Setting the Boot Loader Lock Bits by SPM

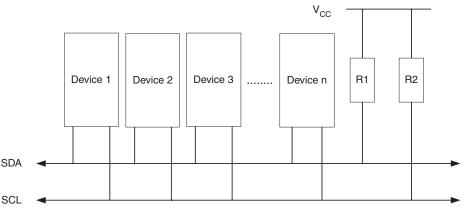

To set the Boot Loader Lock bits, write the desired data to R0, write "X0001001" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The only accessible Lock bits are the Boot Lock bits that may prevent the Application and Boot Loader section from any software update by the MCU.

See Table 24-2 and Table 24-3 for how the different settings of the Boot Loader bits affect the Flash access.

If bits 5..2 in R0 are cleared (zero), the corresponding Boot Lock bit will be programmed if an SPM instruction is executed within four cycles after BLBSET and SELFPRGEN are set in SPMCSR. The Z-pointer is don't care during this operation, but for future compatibility it is recommended to load the Z-pointer with 0x0001 (same as used for reading the  $IO_{ck}$  bits). For future compatibility it is also recommended to set bits 7, 6, 1, and 0 in R0 to "1" when writing the Lock bits. When programming the Lock bits the entire Flash can be read during the operation.

#### 24.7.8 EEPROM Write Prevents Writing to SPMCSR

Note that an EEPROM write operation will block all software programming to Flash. Reading the Fuses and Lock bits from software will also be prevented during the EEPROM write operation. It is recommended that the user checks the status bit (EEPE) in the EECR Register and verifies that the bit is cleared before writing to the SPMCSR Register.

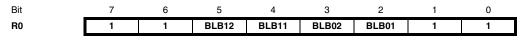

#### 24.7.9 Reading the Fuse and Lock Bits from Software

It is possible to read both the Fuse and Lock bits from software. To read the Lock bits, load the Z-pointer with 0x0001 and set the BLBSET and SELFPRGEN bits in SPMCSR. When an LPM instruction is executed within three CPU cycles after the BLBSET and SELFPRGEN bits are set in SPMCSR, the value of the Lock bits will be loaded in the destination register. The BLBSET and SELFPRGEN bits will auto-clear upon completion of reading the Lock bits or if no LPM instruction is executed within three CPU cycles or no SPM instruction is executed within four CPU cycles. When BLBSET and SELFPRGEN are cleared, LPM will work as described in the Instruction set Manual.

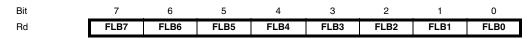

The algorithm for reading the Fuse Low byte is similar to the one described above for reading the Lock bits. To read the Fuse Low byte, load the Z-pointer with 0x0000 and set the BLBSET and SELFPRGEN bits in SPMCSR. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Fuse Low byte (FLB) will be loaded in the destination register as shown below. Refer to Table 25-5 on page 282 for a detailed description and mapping of the Fuse Low byte.

Similarly, when reading the Fuse High byte, load 0x0003 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Fuse High byte (FHB) will be loaded in the destination register as

#### Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |           | Instructio        |                   |                   |                                                                                                                                          |

|-------------------------------------------|-----------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                               | Byte 1    | Byte 2            | Byte 3            | Byte4             | Operation                                                                                                                                |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001 | 0000 0000         | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |

| Write EEPROM Memory<br>Page (page access) | 1100 0010 | 00xx xx <b>aa</b> | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |

| Read Lock bits                            | 0101 1000 | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |

| Write Lock bits                           | 1010 1100 | 111x xxxx         | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |

| Read Signature Byte                       | 0011 0000 | 000x xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |

| Write Fuse bits                           | 1010 1100 | 1010 0000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |

| Write Fuse High bits                      | 1010 1100 | 1010 1000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |

| Write Extended Fuse Bits                  | 1010 1100 | 1010 0100         | xxxx xxxx         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |

| Read Fuse bits                            | 0101 0000 | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |

| Read Fuse High bits                       | 0101 1000 | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |

| Read Extended Fuse Bits                   | 0101 0000 | 0000 1000         | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |

| Read Calibration Byte                     | 0011 1000 | 000x xxxx         | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |

| Poll RDY/BSY                              | 1111 0000 | 0000 0000         | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

#### 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

# 26. Electrical Characteristics

# 26.1 Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                                                                            |

|----------------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                              |

| Voltage on any Pin except $\overrightarrow{\text{RESET}}$ with respect to Ground0.5V to V $_{\text{CC}}$ +0.5V |

| Voltage on $\overline{\text{RESET}}$ with respect to Ground0.5V to +13.0V                                      |

| Maximum Operating Voltage 6.0V                                                                                 |

| DC Current per I/O Pin 40.0 mA                                                                                 |

| DC Current $V_{CC}$ and GND Pins                                                                               |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 26.2 DC Characteristics

$T_A = -40^{\circ}C$  to 85°C,  $V_{CC} = 1.8V$  to 5.5V (unless otherwise noted)

| Symbol           | Parameter                                                | Condition                                                          | Min. <sup>(5)</sup>                                                    | Тур. | Max. <sup>(5)</sup>                                                    | Units |

|------------------|----------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|------|------------------------------------------------------------------------|-------|

| V <sub>IL</sub>  | Input Low Voltage, except<br>XTAL1 and RESET pin         | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | -0.5<br>-0.5                                                           |      | 0.2V <sub>CC</sub> <sup>(1)</sup><br>0.3V <sub>CC</sub> <sup>(1)</sup> | V     |

| V <sub>IH</sub>  | Input High Voltage, except XTAL1 and RESET pins          | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | 0.7V <sub>CC</sub> <sup>(2)</sup><br>0.6V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5<br>V <sub>CC</sub> + 0.5                         | V     |

| V <sub>IL1</sub> | Input Low Voltage,<br>XTAL1 pin                          | V <sub>CC</sub> = 1.8V - 5.5V                                      | -0.5                                                                   |      | 0.1V <sub>CC</sub> <sup>(1)</sup>                                      | V     |

| V <sub>IH1</sub> | Input High Voltage,<br>XTAL1 pin                         | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | 0.8V <sub>CC</sub> <sup>(2)</sup><br>0.7V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5<br>V <sub>CC</sub> + 0.5                         | V     |

| V <sub>IL2</sub> | Input Low Voltage,<br>RESET pin                          | V <sub>CC</sub> = 1.8V - 5.5V                                      | -0.5                                                                   |      | 0.2V <sub>CC</sub> <sup>(1)</sup>                                      | V     |

| V <sub>IH2</sub> | Input High Voltage,<br>RESET pin                         | V <sub>CC</sub> = 1.8V - 5.5V                                      | 0.9V <sub>CC</sub> <sup>(2)</sup>                                      |      | V <sub>CC</sub> + 0.5                                                  | V     |

| V <sub>IL3</sub> | Input Low Voltage,<br>RESET pin as I/O                   | $V_{CC} = 1.8V - 2.4V$<br>$V_{CC} = 2.4V - 5.5V$                   | -0.5<br>-0.5                                                           |      | 0.2V <sub>CC</sub> <sup>(1)</sup><br>0.3V <sub>CC</sub> <sup>(1)</sup> | V     |

| V <sub>IH3</sub> | Input High Voltage,<br>RESET pin as I/O                  | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | 0.7V <sub>CC</sub> <sup>(2)</sup><br>0.6V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5<br>V <sub>CC</sub> + 0.5                         | V     |

| V <sub>OL</sub>  | Output Low Voltage <sup>(3)</sup> ,<br>RESET pin as I/O  | $I_{OL} = 20$ mA, $V_{CC} = 5V$<br>$I_{OL} = 6$ mA, $V_{CC} = 3V$  |                                                                        |      | 0.7<br>0.5                                                             | V     |

| V <sub>OH</sub>  | Output High Voltage <sup>(4)</sup> ,<br>RESET pin as I/O | $I_{OH}$ = -20mA, $V_{CC}$ = 5V<br>$I_{OH}$ = -10mA, $V_{CC}$ = 3V | 4.2<br>2.3                                                             |      |                                                                        | V     |

| V <sub>OL3</sub> | Output Low Voltage <sup>(3)</sup> ,<br>RESET pin as I/O  | TBD                                                                |                                                                        |      | TBD                                                                    | V     |

| V <sub>OH3</sub> | Output High Voltage <sup>(4)</sup> ,<br>RESET pin as I/O | TBD                                                                | TBD                                                                    |      |                                                                        | V     |

| IIL              | Input Leakage<br>Current I/O Pin                         | V <sub>CC</sub> = 5.5V, pin low<br>(absolute value)                |                                                                        |      | 1                                                                      | μΑ    |

| I <sub>IH</sub>  | Input Leakage<br>Current I/O Pin                         | V <sub>CC</sub> = 5.5V, pin high<br>(absolute value)               |                                                                        |      | 1                                                                      | μA    |

| Symbol            | Parameter                                  | Condition                                               | Min. <sup>(5)</sup> | Тур.       | Max. <sup>(5)</sup> | Units |

|-------------------|--------------------------------------------|---------------------------------------------------------|---------------------|------------|---------------------|-------|

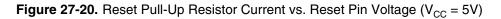

| R <sub>RST</sub>  | Reset Pull-up Resistor                     |                                                         | 30                  |            | 60                  | kΩ    |

| R <sub>PU</sub>   | I/O Pin Pull-up Resistor                   |                                                         | 20                  |            | 50                  | kΩ    |

| I <sub>CC</sub>   | Power Supply Current <sup>(6)</sup>        | Active 1MHz, V <sub>CC</sub> = 2V<br>(ATmega48/88/168V) |                     |            | 0.55                | mA    |

|                   |                                            | Active 4MHz, V <sub>CC</sub> = 3V<br>(ATmega48/88/168L) |                     |            | 3.5                 | mA    |

|                   |                                            | Active 8MHz, V <sub>CC</sub> = 5V<br>(ATmega48/88/168)  |                     |            | 12                  | mA    |

|                   |                                            | Idle 1MHz, V <sub>CC</sub> = 2V<br>(ATmega48/88/168V)   |                     | 0.25       | 0.5                 | mA    |

|                   |                                            | Idle 4MHz, V <sub>CC</sub> = 3V<br>(ATmega48/88/168L)   |                     |            | 1.5                 | mA    |

|                   |                                            | Idle 8MHz, V <sub>CC</sub> = 5V<br>(ATmega48/88/168)    |                     |            | 5.5                 | mA    |

|                   | Power-down mode                            | WDT enabled, $V_{CC} = 3V$                              |                     | <8         | 15                  | μA    |

|                   |                                            | WDT disabled, $V_{CC} = 3V$                             |                     | <1         | 2                   | μA    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$                    |                     | <10        | 40                  | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$                    | -50                 |            | 50                  | nA    |

| t <sub>ACID</sub> | Analog Comparator<br>Propagation Delay     | $V_{CC} = 2.7V$ $V_{CC} = 4.0V$                         |                     | 750<br>500 |                     | ns    |

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low

2. "Min" means the lowest value where the pin is guaranteed to be read as high

Although each I/O port can sink more than the test conditions (20mA at V<sub>CC</sub> = 5V, 10mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- ATmega48:

- 1] The sum of all IOL, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOL, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOL, for ports B0 B7, D5 D7, should not exceed 100 mA.

- ATmega88/168:

- 1] The sum of all IOL, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOL, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOL, for ports B0 B7, D5 D7, should not exceed 100 mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

- Although each I/O port can source more than the test conditions (20mA at V<sub>CC</sub> = 5V, 10mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- ATmega48:

- 1] The sum of all IOH, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOH, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOH, for ports B0 B7, D5 D7, should not exceed 100 mA.

- ATmega88/168:

- 1] The sum of all IOH, for ports C0 C5, should not exceed 100 mA.

- 2] The sum of all IOH, for ports C6, D0 D4, should not exceed 100 mA.

- 3] The sum of all IOH, for ports B0 B7, D5 D7, should not exceed 100 mA.

# 26.8 ADC Characteristics – Preliminary Data

| Symbol                          | Parameter                                                                               | Condition                                                                       | Min                   | Тур  | Max                   | Units |

|---------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

|                                 | Resolution                                                                              |                                                                                 |                       | 10   |                       | Bits  |

|                                 |                                                                                         | $V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                             |                       | 2    | 2.5                   | LSB   |

|                                 | Absolute accuracy (Including<br>INL, DNL, quantization error,<br>gain and offset error) | $V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 1 MHz                               |                       | 4.5  |                       | LSB   |

|                                 |                                                                                         | $V_{REF} = 4V$ , $V_{CC} = 4V$ ,<br>ADC clock = 200 kHz<br>Noise Reduction Mode |                       | 2    |                       | LSB   |

|                                 |                                                                                         | $V_{REF} = 4V$ , $V_{CC} = 4V$ ,<br>ADC clock = 1 MHz<br>Noise Reduction Mode   |                       | 4.5  |                       | LSB   |

|                                 | Integral Non-Linearity (INL)                                                            | $V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                             |                       | 0.5  |                       | LSB   |

|                                 | Differential Non-Linearity<br>(DNL)                                                     | $V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                             |                       | 0.25 |                       | LSB   |

|                                 | Gain Error                                                                              | $V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                             |                       | 2    |                       | LSB   |

|                                 | Offset Error                                                                            | $V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                             |                       | 2    |                       | LSB   |

|                                 | Conversion Time                                                                         | Free Running Conversion                                                         | 13                    |      | 260                   | μs    |

|                                 | Clock Frequency                                                                         |                                                                                 | 50                    |      | 1000                  | kHz   |

| AV <sub>CC</sub> <sup>(1)</sup> | Analog Supply Voltage                                                                   |                                                                                 | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3 | V     |

| V <sub>REF</sub>                | Reference Voltage                                                                       |                                                                                 | 1.0                   |      | AV <sub>CC</sub>      | V     |

| V <sub>IN</sub>                 | Input Voltage                                                                           |                                                                                 | GND                   |      | V <sub>REF</sub>      | V     |

|                                 | Input Bandwidth                                                                         |                                                                                 |                       | 38.5 |                       | kHz   |

| V <sub>INT</sub>                | Internal Voltage Reference                                                              |                                                                                 | 1.0                   | 1.1  | 1.2                   | V     |

| R <sub>REF</sub>                | Reference Input Resistance                                                              |                                                                                 |                       | 32   |                       | kΩ    |

| R <sub>AIN</sub>                | Analog Input Resistance                                                                 |                                                                                 |                       | 100  |                       | MΩ    |

Note: 1.  $AV_{CC}$  absolute min/max: 1.8V/5.5V

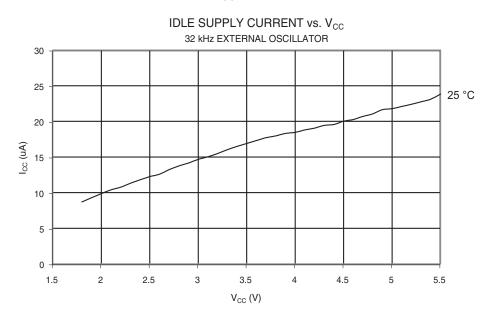

Figure 27-12. Idle Supply Current vs. V<sub>CC</sub> (32 kHz External Oscillator)

# 27.3 Supply Current of I/O modules

The tables and formulas below can be used to calculate the additional current consumption for the different I/O modules in Active and Idle mode. The enabling or disabling of the I/O modules are controlled by the Power Reduction Register. See "Power Reduction Register" on page 39 for details.

| PRR bit  | Typical numbers                |                         |                                |  |  |  |

|----------|--------------------------------|-------------------------|--------------------------------|--|--|--|

|          | V <sub>CC</sub> = 2V, F = 1MHz | $V_{CC} = 3V, F = 4MHz$ | V <sub>CC</sub> = 5V, F = 8MHz |  |  |  |

| PRUSART0 | 8.0 uA                         | 51 uA                   | 220 uA                         |  |  |  |

| PRTWI    | 12 uA                          | 75 uA                   | 315 uA                         |  |  |  |

| PRTIM2   | 11 uA                          | 72 uA                   | 300 uA                         |  |  |  |

| PRTIM1   | 5.0 uA                         | 32 uA                   | 130 uA                         |  |  |  |

| PRTIM0   | 4.0 uA                         | 24 uA                   | 100 uA                         |  |  |  |

| PRSPI    | 15 uA                          | 95 uA                   | 400 uA                         |  |  |  |

| PRADC    | 12 uA                          | 75 uA                   | 315 uA                         |  |  |  |

Table 27-1.

Additional Current Consumption for the different I/O modules (absolute values)

# ATmega48/88/168

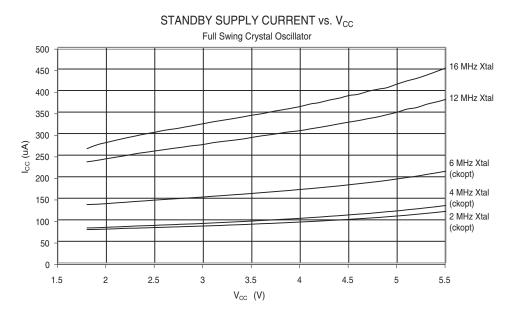

Figure 27-17. Standby Supply Current vs. V<sub>CC</sub> (Full Swing Crystal Oscillator)

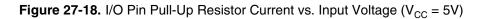

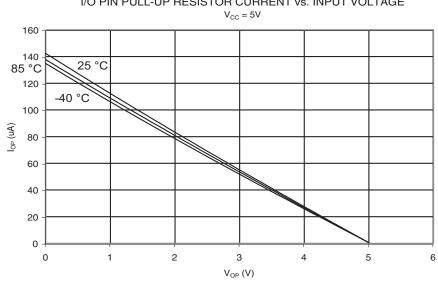

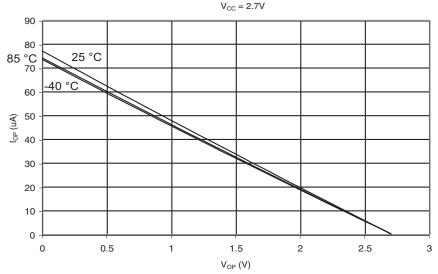

## 27.7 Pin Pull-up

I/O PIN PULL-UP RESISTOR CURRENT vs. INPUT VOLTAGE

Figure 27-19. I/O Pin Pull-Up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 2.7V)

I/O PIN PULL-UP RESISTOR CURRENT vs. INPUT VOLTAGE