Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-TQFP                                                                  |

| Supplier Device Package    | 32-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48v-10aj |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

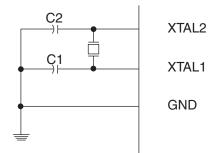

#### Figure 6-3. Crystal Oscillator Connections

Table 6-6.

Start-up Times for the Full Swing Crystal Oscillator Clock Selection

| Oscillator Source /<br>Power Conditions  | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | CKSEL0 | SUT10 |

|------------------------------------------|----------------------------------------------------|------------------------------------------------------------|--------|-------|

| Ceramic resonator, fast rising power     | 258 CK                                             | 14CK + 4.1 ms <sup>(1)</sup>                               | 0      | 00    |

| Ceramic resonator, slowly rising power   | 258 CK                                             | 14CK + 65 ms <sup>(1)</sup>                                | 0      | 01    |

| Ceramic resonator, BOD enabled           | 1K CK                                              | 14CK <sup>(2)</sup>                                        | 0      | 10    |

| Ceramic resonator, fast rising power     | 1K CK                                              | 14CK + 4.1 ms <sup>(2)</sup>                               | 0      | 11    |

| Ceramic resonator, slowly rising power   | 1K CK                                              | 14CK + 65 ms <sup>(2)</sup>                                | 1      | 00    |

| Crystal Oscillator, BOD<br>enabled       | 16K CK                                             | 14CK                                                       | 1      | 01    |

| Crystal Oscillator, fast<br>rising power | 16K CK                                             | 14CK + 4.1 ms                                              | 1      | 10    |

| Crystal Oscillator, slowly rising power  | 16K CK                                             | 14CK + 65 ms                                               | 1      | 11    |

Notes: 1. These options should only be used when not operating close to the maximum frequency of the device, and only if frequency stability at start-up is not important for the application. These options are not suitable for crystals.

2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum frequency of the device, and if frequency stability at start-up is not important for the application.

#### 8.2.1 Watchdog Timer Control Register - WDTCSR

| Bit           | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    | _      |

|---------------|------|------|------|------|-----|------|------|------|--------|

|               | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | -      |

| Initial Value | 0    | 0    | 0    | 0    | х   | 0    | 0    | 0    |        |

#### • Bit 7 - WDIF: Watchdog Interrupt Flag

This bit is set when a time-out occurs in the Watchdog Timer and the Watchdog Timer is configured for interrupt. WDIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, WDIF is cleared by writing a logic one to the flag. When the I-bit in SREG and WDIE are set, the Watchdog Time-out Interrupt is executed.

#### Bit 6 - WDIE: Watchdog Interrupt Enable

When this bit is written to one and the I-bit in the Status Register is set, the Watchdog Interrupt is enabled. If WDE is cleared in combination with this setting, the Watchdog Timer is in Interrupt Mode, and the corresponding interrupt is executed if time-out in the Watchdog Timer occurs.

If WDE is set, the Watchdog Timer is in Interrupt and System Reset Mode. The first time-out in the Watchdog Timer will set WDIF. Executing the corresponding interrupt vector will clear WDIE and WDIF automatically by hardware (the Watchdog goes to System Reset Mode). This is useful for keeping the Watchdog Timer security while using the interrupt. To stay in Interrupt and System Reset Mode, WDIE must be set after each interrupt. This should however not be done within the interrupt service routine itself, as this might compromise the safety-function of the Watchdog System Reset mode. If the interrupt is not executed before the next time-out, a System Reset will be applied.

| WDTON | WDE | WDIE | Mode                               | Action on Time-out                         |

|-------|-----|------|------------------------------------|--------------------------------------------|

| 0     | 0   | 0    | Stopped                            | None                                       |

| 0     | 0   | 1    | Interrupt Mode                     | Interrupt                                  |

| 0     | 1   | 0    | System Reset Mode                  | Reset                                      |

| 0     | 1   | 1    | Interrupt and System Reset<br>Mode | Interrupt, then go to System<br>Reset Mode |

| 1     | х   | x    | System Reset Mode                  | Reset                                      |

Table 8-5.Watchdog Timer Configuration

#### • Bit 4 - WDCE: Watchdog Change Enable

This bit is used in timed sequences for changing WDE and prescaler bits. To clear the WDE bit, and/or change the prescaler bits, WDCE must be set.

Once written to one, hardware will clear WDCE after four clock cycles.

#### Bit 3 - WDE: Watchdog System Reset Enable

WDE is overridden by WDRF in MCUSR. This means that WDE is always set when WDRF is set. To clear WDE, WDRF must be cleared first. This feature ensures multiple resets during conditions causing failure, and a safe start-up after the failure.

#### Assembly Code Example<sup>(1)</sup>

| •••                                    |                                                                                             |  |  |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| ; Define pull-ups and set outputs high |                                                                                             |  |  |  |  |  |  |  |

| ; De                                   | fine directions for port pins                                                               |  |  |  |  |  |  |  |

| ldi                                    | r16,(1< <pb7) (1<<pb6) (1<<pb1) (1<<pb0)< th=""></pb7) (1<<pb6) (1<<pb1) (1<<pb0)<>         |  |  |  |  |  |  |  |

| ldi                                    | r17,(1< <ddb3) (1<<ddb2) (1<<ddb1) (1<<ddb0)< th=""></ddb3) (1<<ddb2) (1<<ddb1) (1<<ddb0)<> |  |  |  |  |  |  |  |

| out                                    | PORTB,r16                                                                                   |  |  |  |  |  |  |  |

| out                                    | DDRB,r17                                                                                    |  |  |  |  |  |  |  |

| ; In                                   | sert nop for synchronization                                                                |  |  |  |  |  |  |  |

| nop                                    |                                                                                             |  |  |  |  |  |  |  |

| ; Re                                   | ad port pins                                                                                |  |  |  |  |  |  |  |

| in                                     | r16,PINB                                                                                    |  |  |  |  |  |  |  |

| •••                                    |                                                                                             |  |  |  |  |  |  |  |

#### C Code Example

```

unsigned char i;

...

/* Define pull-ups and set outputs high */

/* Define directions for port pins */

PORTB = (1<<PB7) | (1<<PB6) | (1<<PB1) | (1<<PB0);

DDRB = (1<<DDB3) | (1<<DDB2) | (1<<DDB1) | (1<<DDB0);

/* Insert nop for synchronization*/

___no_operation();

/* Read port pins */

i = PINB;

...

```

Note: 1. For the assembly program, two temporary registers are used to minimize the time from pullups are set on pins 0, 1, 6, and 7, until the direction bits are correctly set, defining bit 2 and 3 as low and redefining bits 0 and 1 as strong high drivers.

#### 10.2.5 Digital Input Enable and Sleep Modes

As shown in Figure 10-2, the digital input signal can be clamped to ground at the input of the Schmitt Trigger. The signal denoted SLEEP in the figure, is set by the MCU Sleep Controller in Power-down mode, Power-save mode, and Standby mode to avoid high power consumption if some input signals are left floating, or have an analog signal level close to  $V_{CC}/2$ .

SLEEP is overridden for port pins enabled as external interrupt pins. If the external interrupt request is not enabled, SLEEP is active also for these pins. SLEEP is also overridden by various other alternate functions as described in "Alternate Port Functions" on page 69.

If a logic high level ("one") is present on an asynchronous external interrupt pin configured as "Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin" while the external interrupt is *not* enabled, the corresponding External Interrupt Flag will be set when resuming from the above mentioned Sleep mode, as the clamping in these sleep mode produces the requested logic change.

#### 10.2.6 Unconnected Pins

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, float-

#### 10.3.1 MCU Control Register – MCUCR

| Bit           | 7 | 6 | 5 | 4   | 3 | 2 | 1     | 0    | _     |

|---------------|---|---|---|-----|---|---|-------|------|-------|

|               | - | - | - | PUD | - | - | IVSEL | IVCE | MCUCR |

| Read/Write    | R | R | R | R/W | R | R | R/W   | R/W  | •     |

| Initial Value | 0 | 0 | 0 | 0   | 0 | 0 | 0     | 0    |       |

#### • Bit 4 – PUD: Pull-up Disable

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01). See "Configuring the Pin" on page 65 for more details about this feature.

#### 10.3.2 Alternate Functions of Port B

The Port B pins with alternate functions are shown in Table 10-3.

Port Pin **Alternate Functions** XTAL2 (Chip Clock Oscillator pin 2) PB7 TOSC2 (Timer Oscillator pin 2) PCINT7 (Pin Change Interrupt 7) XTAL1 (Chip Clock Oscillator pin 1 or External clock input) PB6 TOSC1 (Timer Oscillator pin 1) PCINT6 (Pin Change Interrupt 6) SCK (SPI Bus Master clock Input) PB5 PCINT5 (Pin Change Interrupt 5) MISO (SPI Bus Master Input/Slave Output) PB4 PCINT4 (Pin Change Interrupt 4) MOSI (SPI Bus Master Output/Slave Input) PB3 OC2A (Timer/Counter2 Output Compare Match A Output) PCINT3 (Pin Change Interrupt 3) SS (SPI Bus Master Slave select) PB2 OC1B (Timer/Counter1 Output Compare Match B Output) PCINT2 (Pin Change Interrupt 2) OC1A (Timer/Counter1 Output Compare Match A Output) PB1 PCINT1 (Pin Change Interrupt 1) ICP1 (Timer/Counter1 Input Capture Input) PB0 CLKO (Divided System Clock Output) PCINT0 (Pin Change Interrupt 0)

Table 10-3. Port B Pins Alternate Functions

The alternate pin configuration is as follows:

#### • XTAL2/TOSC2/PCINT7 - Port B, Bit 7

XTAL2: Chip clock Oscillator pin 2. Used as clock pin for crystal Oscillator or Low-frequency crystal Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

TOSC2: Timer Oscillator pin 2. Used only if internal calibrated RC Oscillator is selected as chip clock source, and the asynchronous timer is enabled by the correct setting in ASSR. When the AS2 bit in ASSR is set (one) and the EXCLK bit is cleared (zero) to enable asynchronous clock-ing of Timer/Counter2 using the Crystal Oscillator, pin PB7 is disconnected from the port, and

the 2-wire Serial Interface. In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal, and the pin is driven by an open drain driver with slew-rate limitation.

PC4 can also be used as ADC input Channel 4. Note that ADC input channel 4 uses digital power.

PCINT12: Pin Change Interrupt source 12. The PC4 pin can serve as an external interrupt source.

#### • ADC3/PCINT11 – Port C, Bit 3

PC3 can also be used as ADC input Channel 3. Note that ADC input channel 3 uses analog power.

PCINT11: Pin Change Interrupt source 11. The PC3 pin can serve as an external interrupt source.

#### • ADC2/PCINT10 – Port C, Bit 2

PC2 can also be used as ADC input Channel 2. Note that ADC input channel 2 uses analog power.

PCINT10: Pin Change Interrupt source 10. The PC2 pin can serve as an external interrupt source.

#### • ADC1/PCINT9 – Port C, Bit 1

PC1 can also be used as ADC input Channel 1. Note that ADC input channel 1 uses analog power.

PCINT9: Pin Change Interrupt source 9. The PC1 pin can serve as an external interrupt source.

#### ADC0/PCINT8 – Port C, Bit 0

PC0 can also be used as ADC input Channel 0. Note that ADC input channel 0 uses analog power.

PCINT8: Pin Change Interrupt source 8. The PC0 pin can serve as an external interrupt source.

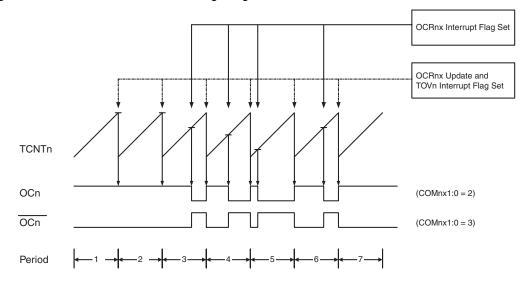

PWM mode is shown in Figure 12-6. The TCNT0 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT0 slopes represent compare matches between OCR0x and TCNT0.

The Timer/Counter Overflow Flag (TOV0) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC0x pins. Setting the COM0x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM0x1:0 to three: Setting the COM0A1:0 bits to one allows the OC0A pin to toggle on Compare Matches if the WGM02 bit is set. This option is not available for the OC0B pin (see Table 12-6 on page 100). The actual OC0x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC0x Register at the compare match between OCR0x and TCNT0, and clearing (or setting) the OC0x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clk}\_I/O}}{N \cdot 256}$$

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

The extreme values for the OCR0A Register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR0A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR0A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM0A1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC0x to toggle its logical level on each compare match (COM0x1:0 = 1). The waveform generated will have a maximum frequency of  $f_{OC0} = f_{clk}$   $_{1/O}/2$  when OCR0A is set to zero. This

# ATmega48/88/168

one allows the OC0A pin to toggle on Compare Matches if the WGM02 bit is set. This option is not available for the OC0B pin (see Table 12-7 on page 101). The actual OC0x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by clearing (or setting) the OC0x Register at the compare match between OCR0x and TCNT0 when the counter increments, and setting (or clearing) the OC0x Register at compare match between OCR0x and TCNT0 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{OCnxPCPWM} = \frac{f_{\text{clk\_I/O}}}{N \cdot 510}$$

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

The extreme values for the OCR0A Register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR0A is set equal to BOTTOM, the output will be continuously low and if set equal to MAX the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values.

At the very start of period 2 in Figure 12-7 OCnx has a transition from high to low even though there is no Compare Match. The point of this transition is to guarantee symmetry around BOT-TOM. There are two cases that give a transition without Compare Match.

- OCRnx changes its value from MAX, like in Figure 12-7. When the OCR0A value is MAX the OCn pin value is the same as the result of a down-counting Compare Match. To ensure symmetry around BOTTOM the OCnx value at MAX must correspond to the result of an up-counting Compare Match.

- The timer starts counting from a value higher than the one in OCRnx, and for that reason misses the Compare Match and hence the OCnx change that would have happened on the way up.

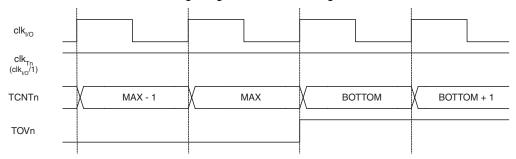

# 12.7 Timer/Counter Timing Diagrams

The Timer/Counter is a synchronous design and the timer clock  $(clk_{T0})$  is therefore shown as a clock enable signal in the following figures. The figures include information on when interrupt flags are set. Figure 12-8 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other than phase correct PWM mode.

Figure 12-8. Timer/Counter Timing Diagram, no Prescaling

Figure 12-9 shows the same timing data, but with the prescaler enabled.

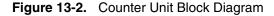

# 13.4 Counter Unit

The main part of the 16-bit Timer/Counter is the programmable 16-bit bi-directional counter unit. Figure 13-2 shows a block diagram of the counter and its surroundings.

Signal description (internal signals):

| Count             | Increment or decrement TCNT1 by 1.                     |

|-------------------|--------------------------------------------------------|

| Direction         | Select between increment and decrement.                |

| Clear             | Clear TCNT1 (set all bits to zero).                    |

| clk <sub>T1</sub> | Timer/Counter clock.                                   |

| ТОР               | Signalize that TCNT1 has reached maximum value.        |

| воттом            | Signalize that TCNT1 has reached minimum value (zero). |

The 16-bit counter is mapped into two 8-bit I/O memory locations: *Counter High* (TCNT1H) containing the upper eight bits of the counter, and *Counter Low* (TCNT1L) containing the lower eight bits. The TCNT1H Register can only be indirectly accessed by the CPU. When the CPU does an access to the TCNT1H I/O location, the CPU accesses the high byte temporary register (TEMP). The temporary register is updated with the TCNT1H value when the TCNT1L is read, and TCNT1H is updated with the temporary register value when TCNT1L is written. This allows the CPU to read or write the entire 16-bit counter value within one clock cycle via the 8-bit data bus. It is important to notice that there are special cases of writing to the TCNT1 Register when the counter is counting that will give unpredictable results. The special cases are described in the sections where they are of importance.

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each *timer clock* ( $clk_{T1}$ ). The  $clk_{T1}$  can be generated from an external or internal clock source, selected by the *Clock Select* bits (CS12:0). When no clock source is selected (CS12:0 = 0) the timer is stopped. However, the TCNT1 value can be accessed by the CPU, independent of whether  $clk_{T1}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the *Waveform Generation mode* bits (WGM13:0) located in the *Timer/Counter Control Registers* A and B (TCCR1A and TCCR1B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC1x. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 118.

The PWM resolution for fast PWM can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution in bits can be calculated by using the following equation:

$$R_{FPWM} = \frac{\log(TOP + 1)}{\log(2)}$$

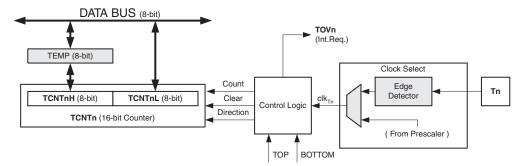

In fast PWM mode the counter is incremented until the counter value matches either one of the fixed values 0x00FF, 0x01FF, or 0x03FF (WGM13:0 = 5, 6, or 7), the value in ICR1 (WGM13:0 = 14), or the value in OCR1A (WGM13:0 = 15). The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 13-7. The figure shows fast PWM mode when OCR1A or ICR1 is used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

Figure 13-7. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches TOP. In addition the OC1A or ICF1 Flag is set at the same timer clock cycle as TOV1 is set when either OCR1A or ICR1 is used for defining the TOP value. If one of the interrupts are enabled, the interrupt handler routine can be used for updating the TOP and compare values.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNT1 and the OCR1x. Note that when using fixed TOP values the unused bits are masked to zero when any of the OCR1x Registers are written.

The procedure for updating ICR1 differs from updating OCR1A when used for defining the TOP value. The ICR1 Register is not double buffered. This means that if ICR1 is changed to a low value when the counter is running with none or a low prescaler value, there is a risk that the new ICR1 value written is lower than the current value of TCNT1. The result will then be that the counter will miss the compare match at the TOP value. The counter will then have to count to the MAX value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. The OCR1A Register however, is double buffered. This feature allows the OCR1A I/O location

- Description of wake up from Power-save or ADC Noise Reduction mode when the timer is clocked asynchronously: When the interrupt condition is met, the wake up process is started on the following cycle of the timer clock, that is, the timer is always advanced by at least one before the processor can read the counter value. After wake-up, the MCU is halted for four cycles, it executes the interrupt routine, and resumes execution from the instruction following SLEEP.

- Reading of the TCNT2 Register shortly after wake-up from Power-save may give an incorrect result. Since TCNT2 is clocked on the asynchronous TOSC clock, reading TCNT2 must be done through a register synchronized to the internal I/O clock domain. Synchronization takes place for every rising TOSC1 edge. When waking up from Power-save mode, and the I/O clock (clk<sub>I/O</sub>) again becomes active, TCNT2 will read as the previous value (before entering sleep) until the next rising TOSC1 edge. The phase of the TOSC clock after waking up from Power-save mode is essentially unpredictable, as it depends on the wake-up time. The recommended procedure for reading TCNT2 is thus as follows:

- a. Write any value to either of the registers OCR2x or TCCR2x.

- b. Wait for the corresponding Update Busy Flag to be cleared.

- c. Read TCNT2.

During asynchronous operation, the synchronization of the Interrupt Flags for the asynchronous timer takes 3 processor cycles plus one timer cycle. The timer is therefore advanced by at least one before the processor can read the timer value causing the setting of the Interrupt Flag. The Output Compare pin is changed on the timer clock and is not synchronized to the processor clock.

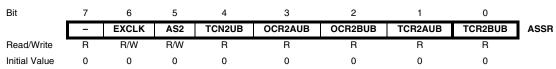

#### 15.9.2 Asynchronous Status Register – ASSR

#### • Bit 7 – RES: Reserved bit

This bit is reserved and will always read as zero.

#### • Bit 6 – EXCLK: Enable External Clock Input

When EXCLK is written to one, and asynchronous clock is selected, the external clock input buffer is enabled and an external clock can be input on Timer Oscillator 1 (TOSC1) pin instead of a 32 kHz crystal. Writing to EXCLK should be done before asynchronous operation is selected. Note that the crystal Oscillator will only run when this bit is zero.

#### • Bit 5 – AS2: Asynchronous Timer/Counter2

When AS2 is written to zero, Timer/Counter2 is clocked from the I/O clock,  $clk_{I/O}$ . When AS2 is written to one, Timer/Counter2 is clocked from a crystal Oscillator connected to the Timer Oscillator 1 (TOSC1) pin. When the value of AS2 is changed, the contents of TCNT2, OCR2A, OCR2B, TCCR2A and TCCR2B might be corrupted.

#### Bit 4 – TCN2UB: Timer/Counter2 Update Busy

When Timer/Counter2 operates asynchronously and TCNT2 is written, this bit becomes set. When TCNT2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCNT2 is ready to be updated with a new value.

#### 17.2.3 External Clock

External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 17-2 for details.

External clock input from the XCKn pin is sampled by a synchronization register to minimize the chance of meta-stability. The output from the synchronization register must then pass through an edge detector before it can be used by the Transmitter and Receiver. This process introduces a two CPU clock period delay and therefore the maximum external XCKn clock frequency is limited by the following equation:

$$f_{XCK} < \frac{f_{OSC}}{4}$$

Note that f<sub>osc</sub> depends on the stability of the system clock source. It is therefore recommended to add some margin to avoid possible loss of data due to frequency variations.

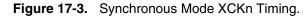

#### 17.2.4 Synchronous Clock Operation

When synchronous mode is used (UMSELn = 1), the XCKn pin will be used as either clock input (Slave) or clock output (Master). The dependency between the clock edges and data sampling or data change is the same. The basic principle is that data input (on RxDn) is sampled at the opposite XCKn clock edge of the edge the data output (TxDn) is changed.

The UCPOLn bit UCRSC selects which XCKn clock edge is used for data sampling and which is used for data change. As Figure 17-3 shows, when UCPOLn is zero the data will be changed at rising XCKn edge and sampled at falling XCKn edge. If UCPOLn is set, the data will be changed at falling XCKn edge and sampled at rising XCKn edge.

#### 17.3 Frame Formats

A serial frame is defined to be one character of data bits with synchronization bits (start and stop bits), and optionally a parity bit for error checking. The USART accepts all 30 combinations of the following as valid frame formats:

- 1 start bit

- 5, 6, 7, 8, or 9 data bits

- no, even or odd parity bit

- 1 or 2 stop bits

# 172 **ATmega48/88/168**

# ATmega48/88/168

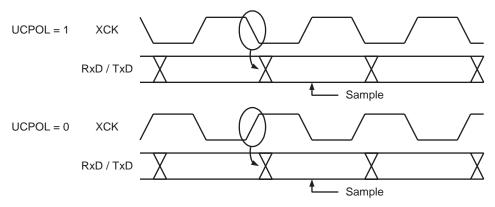

Figure 24-2. Memory Sections

Note: 1. The parameters in the figure above are given in Table 24-6 on page 276.

# 24.4 Boot Loader Lock Bits

If no Boot Loader capability is needed, the entire Flash is available for application code. The Boot Loader has two separate sets of Boot Lock bits which can be set independently. This gives the user a unique flexibility to select different levels of protection.

The user can select:

- To protect the entire Flash from a software update by the MCU.

- To protect only the Boot Loader Flash section from a software update by the MCU.

- To protect only the Application Flash section from a software update by the MCU.

- Allow software update in the entire Flash.

See Table 24-2 and Table 24-3 for further details. The Boot Lock bits can be set in software and in Serial or Parallel Programming mode, but they can be cleared by a Chip Erase command only. The general Write Lock (Lock Bit mode 2) does not control the programming of the Flash memory by SPM instruction. Similarly, the general Read/Write Lock (Lock Bit mode 1) does not control reading nor writing by LPM/SPM, if it is attempted.

| BLB0 Mode | BLB02 | BLB01 | Protection                                                                                                                                                                                                                                                                                    |  |  |  |

|-----------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1         | 1     | 1     | No restrictions for SPM or LPM accessing the Application section.                                                                                                                                                                                                                             |  |  |  |

| 2         | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                       |  |  |  |

| 3         | 0     | 0     | SPM is not allowed to write to the Application section, and LPM executing from the Boot Loader section is not allowed to read from the Application section. If Interrupt Vectors are placed in the Boot Loader section, interrupts are disabled while executing from the Application section. |  |  |  |

| 4         | 0     | 1     | LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section.                                                    |  |  |  |

Table 24-2.

Boot Lock Bit0 Protection Modes (Application Section)<sup>(1)</sup>

Note: 1. "1" means unprogrammed, "0" means programmed

| Table 24-3. | Boot Lock Bit1 Protection Modes | (Boot Loader Section) <sup>(1)</sup> |

|-------------|---------------------------------|--------------------------------------|

|-------------|---------------------------------|--------------------------------------|

| BLB1 Mode | BLB12 | BLB11 | Protection                                                                                                                                                                                                                                                                                    |  |

|-----------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1         | 1     | 1     | No restrictions for SPM or LPM accessing the Boot Loader section.                                                                                                                                                                                                                             |  |

| 2         | 1     | 0     | SPM is not allowed to write to the Boot Loader section.                                                                                                                                                                                                                                       |  |

| 3         | 0     | 0     | SPM is not allowed to write to the Boot Loader section, and LPM executing from the Application section is not allowed to read from the Boot Loader section. If Interrupt Vectors are placed in the Application section, interrupts are disabled while executing from the Boot Loader section. |  |

| 4         | 0     | 1     | LPM executing from the Application section is not allowed to<br>read from the Boot Loader section. If Interrupt Vectors are<br>placed in the Application section, interrupts are disabled while<br>executing from the Boot Loader section.                                                    |  |

Note: 1. "1" means unprogrammed, "0" means programmed

# 24.5 Entering the Boot Loader Program

Entering the Boot Loader takes place by a jump or call from the application program. This may be initiated by a trigger such as a command received via USART, or SPI interface. Alternatively, the Boot Reset Fuse can be programmed so that the Reset Vector is pointing to the Boot Flash start address after a reset. In this case, the Boot Loader is started after a reset. After the application code is loaded, the program can start executing the application code. Note that the fuses cannot be changed by the MCU itself. This means that once the Boot Reset Fuse is programmed, the Reset Vector will always point to the Boot Loader Reset and the fuse can only be changed through the serial or parallel programming interface.

Table 24-4.Boot Reset Fuse(1)

| BOOTRST | Reset Address                                                 |

|---------|---------------------------------------------------------------|

| 1       | Reset Vector = Application Reset (address 0x0000)             |

| 0       | Reset Vector = Boot Loader Reset (see Table 24-6 on page 276) |

- 1. A: Load Command "0010 0000".

- C: Load Data Low Byte. Bit n = "0" programs the Lock bit. If LB mode 3 is programmed (LB1 and LB2 is programmed), it is not possible to program the Boot Lock bits by any External Programming mode.

- 3. Give  $\overline{WR}$  a negative pulse and wait for RDY/ $\overline{BSY}$  to go high.

The Lock bits can only be cleared by executing Chip Erase.

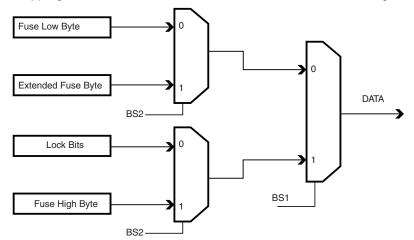

# 25.7.12 Reading the Fuse and Lock Bits

The algorithm for reading the Fuse and Lock bits is as follows (refer to "Programming the Flash" on page 287 for details on Command loading):

- 1. A: Load Command "0000 0100".

- 2. Set  $\overline{\text{OE}}$  to "0", BS2 to "0" and BS1 to "0". The status of the Fuse Low bits can now be read at DATA ("0" means programmed).

- 3. Set  $\overline{\text{OE}}$  to "0", BS2 to "1" and BS1 to "1". The status of the Fuse High bits can now be read at DATA ("0" means programmed).

- 4. Set OE to "0", BS2 to "1", and BS1 to "0". The status of the Extended Fuse bits can now be read at DATA ("0" means programmed).

- 5. Set  $\overline{\text{OE}}$  to "0", BS2 to "0" and BS1 to "1". The status of the Lock bits can now be read at DATA ("0" means programmed).

- 6. Set OE to "1".

### Figure 25-6. Mapping Between BS1, BS2 and the Fuse and Lock Bits During Read

#### 25.7.13 Reading the Signature Bytes

The algorithm for reading the Signature bytes is as follows (refer to "Programming the Flash" on page 287 for details on Command and Address loading):

- 1. A: Load Command "0000 1000".

- 2. B: Load Address Low Byte (0x00 0x02).

- 3. Set  $\overline{OE}$  to "0", and BS1 to "0". The selected Signature byte can now be read at DATA.

- 4. Set OE to "1".

#### Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |           | Instructio        |                   |                   |                                                                                                                                          |

|-------------------------------------------|-----------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                               | Byte 1    | Byte 2            | Byte 3            | Byte4             | Operation                                                                                                                                |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001 | 0000 0000         | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |

| Write EEPROM Memory<br>Page (page access) | 1100 0010 | 00xx xx <b>aa</b> | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |

| Read Lock bits                            | 0101 1000 | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |

| Write Lock bits                           | 1010 1100 | 111x xxxx         | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |

| Read Signature Byte                       | 0011 0000 | 000x xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |

| Write Fuse bits                           | 1010 1100 | 1010 0000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |

| Write Fuse High bits                      | 1010 1100 | 1010 1000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |

| Write Extended Fuse Bits                  | 1010 1100 | 1010 0100         | xxxx xxxx         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |

| Read Fuse bits                            | 0101 0000 | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |

| Read Fuse High bits                       | 0101 1000 | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |

| Read Extended Fuse Bits                   | 0101 0000 | 0000 1000         | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |

| Read Calibration Byte                     | 0011 1000 | 000x xxxx         | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |

| Poll RDY/BSY                              | 1111 0000 | 0000 0000         | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

#### 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

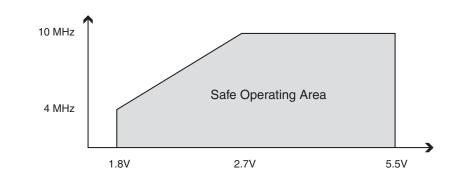

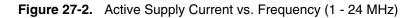

Figure 26-2. Maximum Frequency vs. V<sub>CC</sub>, ATmega48V/88V/168V

# 26.6 2-wire Serial Interface Characteristics

Table 26-2 describes the requirements for devices connected to the 2-wire Serial Bus. The ATmega48/88/168 2-wire Serial Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 26-4.

Table 26-2. 2-wire Serial Bus Requirements

| Symbol             | Parameter                                        | Condition                                      | Min                                      | Мах                   | Units |

|--------------------|--------------------------------------------------|------------------------------------------------|------------------------------------------|-----------------------|-------|

| VIL                | Input Low-voltage                                |                                                | -0.5                                     | 0.3 V <sub>CC</sub>   | V     |

| VIH                | Input High-voltage                               |                                                | 0.7 V <sub>CC</sub>                      | V <sub>CC</sub> + 0.5 | V     |

| (1)<br>Vhys        | Hysteresis of Schmitt Trigger Inputs             |                                                | 0.05 V <sub>CC</sub> <sup>(2)</sup>      | _                     | V     |

| VOL <sup>(1)</sup> | Output Low-voltage                               | 3 mA sink current                              | 0                                        | 0.4                   | V     |

| tr <sup>(1)</sup>  | Rise Time for both SDA and SCL                   |                                                | 20 + 0.1C <sub>b</sub> <sup>(3)(2)</sup> | 300                   | ns    |

| (1)<br>tof         | Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ | 10 pF < C <sub>b</sub> < 400 pF <sup>(3)</sup> | 20 + 0.1C <sub>b</sub> <sup>(3)(2)</sup> | 250                   | ns    |

| tSP <sup>(1)</sup> | Spikes Suppressed by Input Filter                |                                                | 0                                        | 50 <sup>(2)</sup>     | ns    |

| l <sub>i</sub>     | Input Current each I/O Pin                       | $0.1V_{\rm CC} < V_{\rm i} < 0.9V_{\rm CC}$    | -10                                      | 10                    | μA    |

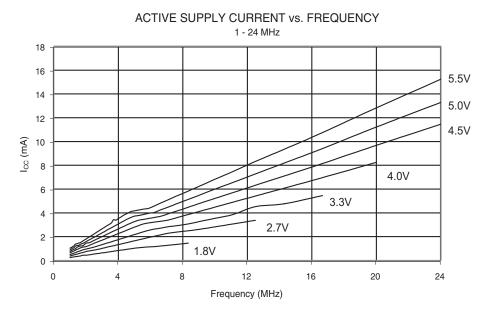

Figure 27-3. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 128 kHz)

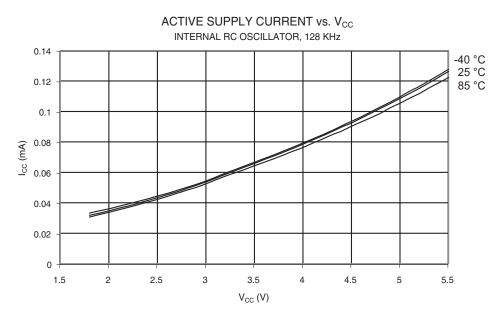

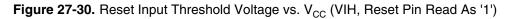

Figure 27-29. I/O Pin Input Threshold Voltage vs. V<sub>CC</sub> (VIL, I/O Pin Read As '0')

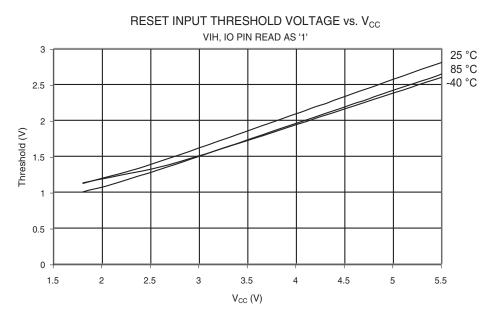

# 31. Packaging Information

# 31.1 32A

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

## **Atmel Operations**

*Memory* 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2005. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, AVR<sup>®</sup>, and AVR Studio<sup>®</sup> are registered trademarks, and Everywhere You Are<sup>SM</sup> are the trademarks of Atmel Corporation or its subsidiaries. Microsoft<sup>®</sup>, Windows<sup>®</sup>, Windows NT<sup>®</sup>, and Windows XP<sup>®</sup> are the registered trademarks of Microsoft Corporation. Other terms and product names may be trademarks of others.