Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48v-10pj |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Low Power Consumption

- Active Mode:

- 1 MHz, 1.8V: 240µA

- 32 kHz, 1.8V: 15µA (including Oscillator)

- Power-down Mode:

- 0.1µA at 1.8V

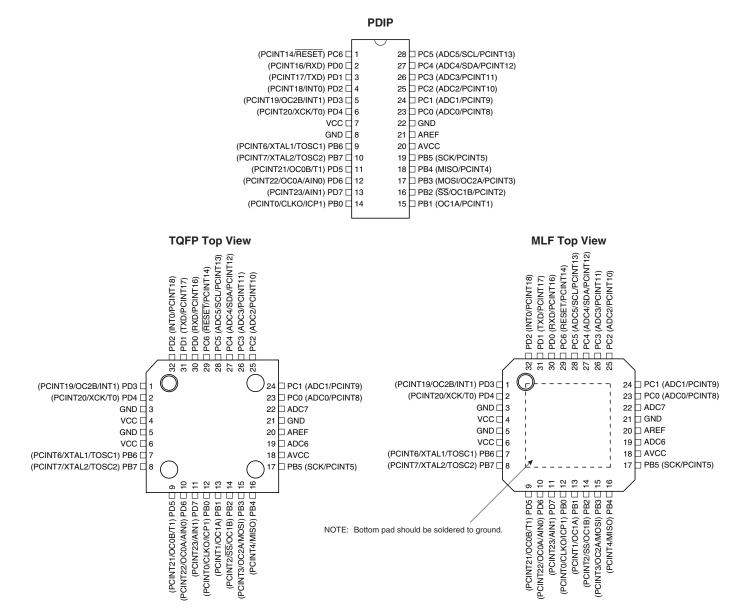

## 1. Pin Configurations

Figure 1-1. Pinout ATmega48/88/168

# 6. System Clock and Clock Options

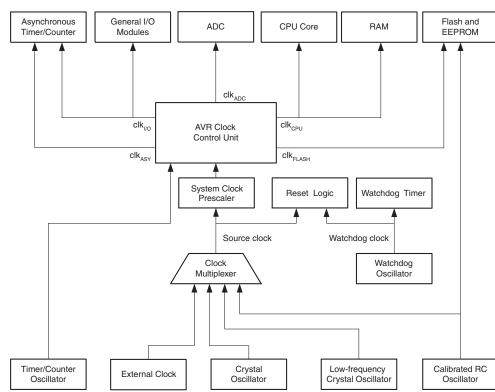

## 6.1 Clock Systems and their Distribution

Figure 6-1 presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the clocks to modules not being used can be halted by using different sleep modes, as described in "Power Management and Sleep Modes" on page 37. The clock systems are detailed below.

#### Figure 6-1. Clock Distribution

#### 6.1.1 CPU Clock – clk<sub>CPU</sub>

The CPU clock is routed to parts of the system concerned with operation of the AVR core. Examples of such modules are the General Purpose Register File, the Status Register and the data memory holding the Stack Pointer. Halting the CPU clock inhibits the core from performing general operations and calculations.

#### 6.1.2 I/O Clock - clk<sub>I/O</sub>

The I/O clock is used by the majority of the I/O modules, like Timer/Counters, SPI, and USART. The I/O clock is also used by the External Interrupt module, but note that some external interrupts are detected by asynchronous logic, allowing such interrupts to be detected even if the I/O clock is halted. Also note that start condition detection in the USI module is carried out asynchronously when clk<sub>I/O</sub> is halted, TWI address recognition in all sleep modes.

### 6.1.3 Flash Clock – clk<sub>FLASH</sub>

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simultaneously with the CPU clock.

## 9. Interrupts

This section describes the specifics of the interrupt handling as performed in ATmega48/88/168. For a general explanation of the AVR interrupt handling, refer to "Reset and Interrupt Handling" on page 12.

The interrupt vectors in ATmega48, ATmega88 and ATmega168 are generally the same, with the following differences:

- Each Interrupt Vector occupies two instruction words in ATmega168, and one instruction word in ATmega48 and ATmega88.

- ATmega48 does not have a separate Boot Loader Section. In ATmega88 and ATmega168, the Reset Vector is affected by the BOOTRST fuse, and the Interrupt Vector start address is affected by the IVSEL bit in MCUCR.

### 9.1 Interrupt Vectors in ATmega48

Table 9-1.

Reset and Interrupt Vectors in ATmega48

| Vector No. | Program Address | Source       | Interrupt Definition                                                    |

|------------|-----------------|--------------|-------------------------------------------------------------------------|

| 1          | 0x000           | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2          | 0x001           | INT0         | External Interrupt Request 0                                            |

| 3          | 0x002           | INT1         | External Interrupt Request 1                                            |

| 4          | 0x003           | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5          | 0x004           | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6          | 0x005           | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7          | 0x006           | WDT          | Watchdog Time-out Interrupt                                             |

| 8          | 0x007           | TIMER2 COMPA | Timer/Counter2 Compare Match A                                          |

| 9          | 0x008           | TIMER2 COMPB | Timer/Counter2 Compare Match B                                          |

| 10         | 0x009           | TIMER2 OVF   | Timer/Counter2 Overflow                                                 |

| 11         | 0x00A           | TIMER1 CAPT  | Timer/Counter1 Capture Event                                            |

| 12         | 0x00B           | TIMER1 COMPA | Timer/Counter1 Compare Match A                                          |

| 13         | 0x00C           | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                          |

| 14         | 0x00D           | TIMER1 OVF   | Timer/Counter1 Overflow                                                 |

| 15         | 0x00E           | TIMER0 COMPA | Timer/Counter0 Compare Match A                                          |

| 16         | 0x00F           | TIMER0 COMPB | Timer/Counter0 Compare Match B                                          |

| 17         | 0x010           | TIMER0 OVF   | Timer/Counter0 Overflow                                                 |

| 18         | 0x011           | SPI, STC     | SPI Serial Transfer Complete                                            |

| 19         | 0x012           | USART, RX    | USART Rx Complete                                                       |

| 20         | 0x013           | USART, UDRE  | USART, Data Register Empty                                              |

| 21         | 0x014           | USART, TX    | USART, Tx Complete                                                      |

| 22         | 0x015           | ADC          | ADC Conversion Complete                                                 |

| 23         | 0x016           | EE READY     | EEPROM Ready                                                            |

## 12. 8-bit Timer/Counter0 with PWM

Timer/Counter0 is a general purpose 8-bit Timer/Counter module, with two independent Output Compare Units, and with PWM support. It allows accurate program execution timing (event management) and wave generation. The main features are:

- Two Independent Output Compare Units

- Double Buffered Output Compare Registers

- Clear Timer on Compare Match (Auto Reload)

- Glitch Free, Phase Correct Pulse Width Modulator (PWM)

- Variable PWM Period

- Frequency Generator

- Three Independent Interrupt Sources (TOV0, OCF0A, and OCF0B)

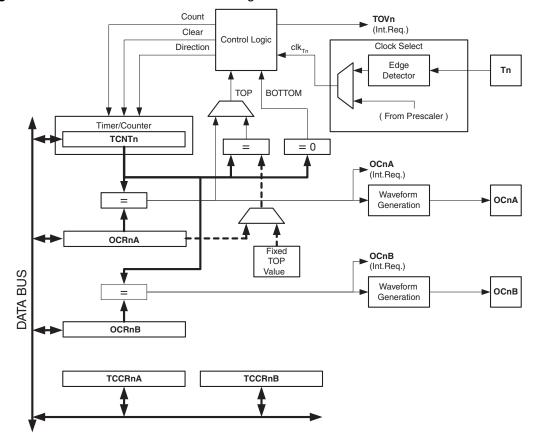

#### 12.1 Overview

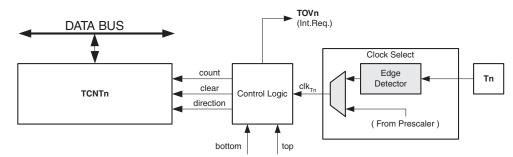

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 12-1. For the actual placement of I/O pins, refer to "Pinout ATmega48/88/168" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "8-bit Timer/Counter Register Description" on page 99.

The PRTIM0 bit in "Power Reduction Register - PRR" on page 40 must be written to zero to enable Timer/Counter0 module.

#### Figure 12-1. 8-bit Timer/Counter Block Diagram

#### Figure 12-2. Counter Unit Block Diagram

Signal description (internal signals):

| count             | Increment or decrement TCNT0 by 1.                               |

|-------------------|------------------------------------------------------------------|

| direction         | Select between increment and decrement.                          |

| clear             | Clear TCNT0 (set all bits to zero).                              |

| clk <sub>Tn</sub> | Timer/Counter clock, referred to as $clk_{T0}$ in the following. |

| top               | Signalize that TCNT0 has reached maximum value.                  |

| bottom            | Signalize that TCNT0 has reached minimum value (zero).           |

Depending of the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T0}$ ).  $clk_{T0}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS02:0). When no clock source is selected (CS02:0 = 0) the timer is stopped. However, the TCNT0 value can be accessed by the CPU, regardless of whether  $clk_{T0}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM01 and WGM00 bits located in the Timer/Counter Control Register (TCCR0A) and the WGM02 bit located in the Timer/Counter Control Register B (TCCR0B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC0A and OC0B. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 93.

The Timer/Counter Overflow Flag (TOV0) is set according to the mode of operation selected by the WGM02:0 bits. TOV0 can be used for generating a CPU interrupt.

#### 12.4 Output Compare Unit

The 8-bit comparator continuously compares TCNT0 with the Output Compare Registers (OCR0A and OCR0B). Whenever TCNT0 equals OCR0A or OCR0B, the comparator signals a match. A match will set the Output Compare Flag (OCF0A or OCF0B) at the next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare Flag generates an Output Compare interrupt. The Output Compare Flag is automatically cleared when the interrupt is executed. Alternatively, the flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the WGM02:0 bits and Compare Output mode (COM0x1:0) bits. The max and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation ("Modes of Operation" on page 93).

Figure 12-3 shows a block diagram of the Output Compare unit.

# ATmega48/88/168

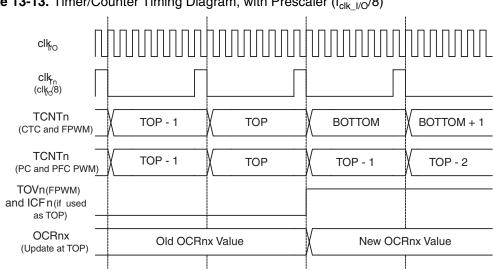

Figure 13-13. Timer/Counter Timing Diagram, with Prescaler ( ${\rm f}_{\rm clk\_I/O}/8)$

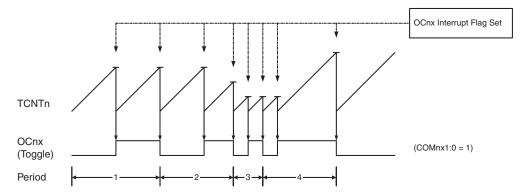

Figure 15-5. CTC Mode, Timing Diagram

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF2A Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR2A is lower than the current value of TCNT2, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur.

For generating a waveform output in CTC mode, the OC2A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM2A1:0 = 1). The OC2A value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC2A} = f_{clk\_l/O}/2$  when OCR2A is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCnx} = \frac{f_{clk\_I/O}}{2 \cdot N \cdot (1 + OCRnx)}$$

The *N* variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

As for the Normal mode of operation, the TOV2 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

#### 15.6.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM22:0 = 3 or 7) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOT-TOM. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. In noninverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x, and set at BOTTOM. In inverting Compare Output mode, the output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that uses dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

#### • Bit 3 – OCR2AUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2A is written, this bit becomes set. When OCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2A is ready to be updated with a new value.

#### • Bit 2 – OCR2BUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2B is written, this bit becomes set. When OCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2B is ready to be updated with a new value.

#### • Bit 1 – TCR2AUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2A is written, this bit becomes set. When TCCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2A is ready to be updated with a new value.

#### • Bit 0 – TCR2BUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2B is written, this bit becomes set. When TCCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2B is ready to be updated with a new value.

If a write is performed to any of the five Timer/Counter2 Registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur.

The mechanisms for reading TCNT2, OCR2A, OCR2B, TCCR2A and TCCR2B are different. When reading TCNT2, the actual timer value is read. When reading OCR2A, OCR2B, TCCR2A and TCCR2B the value in the temporary storage register is read.

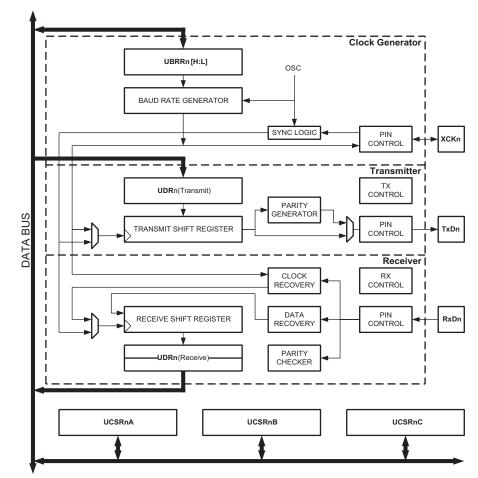

Figure 17-1. USART Block Diagram<sup>(1)</sup>

Note: 1. Refer to Figure 1-1 on page 2 and Table 10-9 on page 78 for USART0 pin placement.

#### 17.2 Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: Normal asynchronous, Double Speed asynchronous, Master synchronous and Slave synchronous mode. The UMSELn bit in USART Control and Status Register C (UCSRnC) selects between asynchronous and synchronous operation. Double Speed (asynchronous mode only) is controlled by the U2Xn found in the UCSRnA Register. When using synchronous mode (UMSELn = 1), the Data Direction Register for the XCKn pin (DDR\_XCKn) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCKn pin is only active when using synchronous mode.

Figure 17-2 shows a block diagram of the clock generation logic.

Writing this bit to one enables the USART Receiver in MSPIM mode. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer. Only enabling the receiver in MSPI mode (i.e. setting RXENn=1 and TXENn=0) has no meaning since it is the transmitter that controls the transfer clock and since only master mode is supported.

#### • Bit 3 - TXENn: Transmitter Enable

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn port.

#### Bit 2:0 - Reserved Bits in MSPI mode

When in MSPI mode, these bits are reserved for future use. For compatibility with future devices, these bits must be written to zero when UCSRnB is written.

#### 18.6.4 USART MSPIM Control and Status Register n C - UCSRnC

| Bit           | 7       | 6       | 5 | 4 | 3 | 2      | 1      | 0      | _      |

|---------------|---------|---------|---|---|---|--------|--------|--------|--------|

|               | UMSELn1 | UMSELn0 | - | - | - | UDORDn | UCPHAn | UCPOLn | UCSRnC |

| Read/Write    | R/W     | R/W     | R | R | R | R/W    | R/W    | R/W    | -      |

| Initial Value | 0       | 0       | 0 | 0 | 0 | 1      | 1      | 0      |        |

#### • Bit 7:6 - UMSELn1:0: USART Mode Select

These bits select the mode of operation of the USART as shown in Table 18-3. See "USART Control and Status Register n C – UCSRnC" on page 189 for full description of the normal USART operation. The MSPIM is enabled when both UMSELn bits are set to one. The UDORDn, UCPHAn, and UCPOLn can be set in the same write operation where the MSPIM is enabled.

| Table 18-3. UI | <b>MSELn Bits Settings</b> |

|----------------|----------------------------|

|----------------|----------------------------|

| UMSELn1 | UMSELn0 | Mode               |

|---------|---------|--------------------|

| 0       | 0       | Asynchronous USART |

| 0       | 1       | Synchronous USART  |

| 1       | 0       | (Reserved)         |

| 1       | 1       | Master SPI (MSPIM) |

#### • Bit 5:3 - Reserved Bits in MSPI mode

When in MSPI mode, these bits are reserved for future use. For compatibility with future devices, these bits must be written to zero when UCSRnC is written.

#### • Bit 2 - UDORDn: Data Order

When set to one the LSB of the data word is transmitted first. When set to zero the MSB of the data word is transmitted first. Refer to the Frame Formats section page 4 for details.

#### • Bit 1 - UCPHAn: Clock Phase

The UCPHAn bit setting determine if data is sampled on the leasing edge (first) or tailing (last) edge of XCKn. Refer to the SPI Data Modes and Timing section page 4 for details.

# ATmega48/88/168

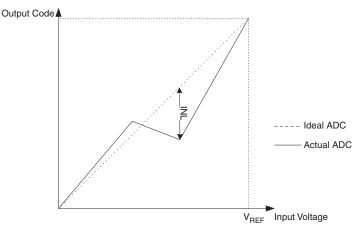

Figure 21-12. Integral Non-linearity (INL)

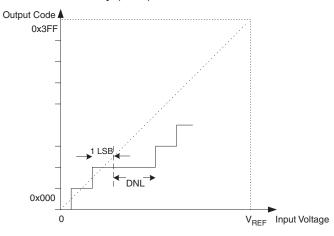

• Differential Non-linearity (DNL): The maximum deviation of the actual code width (the interval between two adjacent transitions) from the ideal code width (1 LSB). Ideal value: 0 LSB.

Figure 21-13. Differential Non-linearity (DNL)

- Quantization Error: Due to the quantization of the input voltage into a finite number of codes, a range of input voltages (1 LSB wide) will code to the same value. Always ±0.5 LSB.

- Absolute accuracy: The maximum deviation of an actual (unadjusted) transition compared to an ideal transition for any code. This is the compound effect of offset, gain error, differential error, non-linearity, and quantization error. Ideal value: ±0.5 LSB.

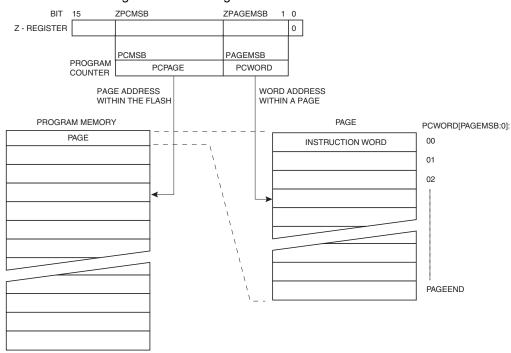

#### 23.0.3 Performing a Page Write

To execute Page Write, set up the address in the Z-pointer, write "00000101" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored. The page address must be written to PCPAGE. Other bits in the Z-pointer must be written to zero during this operation.

• The CPU is halted during the Page Write operation.

#### 23.1 Addressing the Flash During Self-Programming

The Z-pointer is used to address the SPM commands.

| Bit      | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| ZH (R31) | Z15 | Z14 | Z13 | Z12 | Z11 | Z10 | Z9 | Z8 |

| ZL (R30) | Z7  | Z6  | Z5  | Z4  | Z3  | Z2  | Z1 | Z0 |

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

Since the Flash is organized in pages (see Table 25-8 on page 284), the Program Counter can be treated as having two different sections. One section, consisting of the least significant bits, is addressing the words within a page, while the most significant bits are addressing the pages. This is shown in Figure 24-3. Note that the Page Erase and Page Write operations are addressed independently. Therefore it is of major importance that the software addresses the same page in both the Page Erase and Page Write operation.

The LPM instruction uses the Z-pointer to store the address. Since this instruction addresses the Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used.

#### Figure 23-1. Addressing the Flash During SPM<sup>(1)</sup>

Note: 1. The different variables used in Figure 24-3 are listed in Table 25-8 on page 284.

Table 25-12. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                                |

|-----|-----|----------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (High or low address byte determined by BS1). |

| 0   | 1   | Load Data (High or Low data byte for Flash determined by BS1).             |

| 1   | 0   | Load Command                                                               |

| 1   | 1   | No Action, Idle                                                            |

Table 25-13. Command Byte Bit Coding

| Command Byte | Command Executed                          |

|--------------|-------------------------------------------|

| 1000 0000    | Chip Erase                                |

| 0100 0000    | Write Fuse bits                           |

| 0010 0000    | Write Lock bits                           |

| 0001 0000    | Write Flash                               |

| 0001 0001    | Write EEPROM                              |

| 0000 1000    | Read Signature Bytes and Calibration byte |

| 0000 0100    | Read Fuse and Lock bits                   |

| 0000 0010    | Read Flash                                |

| 0000 0011    | Read EEPROM                               |

#### 25.7 Parallel Programming

#### 25.7.1 Enter Programming Mode

The following algorithm puts the device in Parallel (High-voltage) Programming mode:

- 1. Set Prog\_enable pins listed in Table 25-11 on page 285 to "0000", RESET pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND.

Ensure that  $V_{CC}$  reaches at least 1.8V within the next 20  $\mu$ s.

- 3. Wait 20 60 µs, and apply 11.5 12.5V to RESET.

- 4. Keep the Prog\_enable pins unchanged for at least 10µs after the High-voltage has been applied to ensure the Prog\_enable Signature has been latched.

- 5. Wait at least 300 µs before giving any parallel programming commands.

- 6. Exit Programming mode by power the device down or by bringing RESET pin to 0V.

If the rise time of the  $V_{CC}$  is unable to fulfill the requirements listed above, the following alternative algorithm can be used.

- 1. Set Prog\_enable pins listed in Table 25-11 on page 285 to "0000", RESET pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND.

- 3. Monitor  $V_{CC}$ , and as soon as  $V_{CC}$  reaches 0.9 1.1V, apply 11.5 12.5V to RESET.

### 25.9 Serial Programming Pin Mapping

|        | -1F 5 | 3   |                 |

|--------|-------|-----|-----------------|

| Symbol | Pins  | I/O | Description     |

| MOSI   | PB3   | I   | Serial Data in  |

| MISO   | PB4   | 0   | Serial Data out |

| SCK    | PB5   | I   | Serial Clock    |

#### Table 25-15. Pin Mapping Serial Programming

#### 25.9.1 Serial Programming Algorithm

When writing serial data to the ATmega48/88/168, data is clocked on the rising edge of SCK.

When reading data from the ATmega48/88/168, data is clocked on the falling edge of SCK. See Figure 25-11 for timing details.

To program and verify the ATmega48/88/168 in the serial programming mode, the following sequence is recommended (See four byte instruction formats in Table 25-17):

1. Power-up sequence:

Apply power between  $V_{CC}$  and GND while RESET and SCK are set to "0". In some systems, the programmer can not guarantee that SCK is held low during power-up. In this case, RESET must be given a positive pulse of at least two CPU clock cycles duration after SCK has been set to "0".

- 2. Wait for at least 20 ms and enable serial programming by sending the Programming Enable serial instruction to pin MOSI.

- 3. The serial programming instructions will not work if the communication is out of synchronization. When in sync. the second byte (0x53), will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all four bytes of the instruction must be transmitted. If the 0x53 did not echo back, give RESET a positive pulse and issue a new Programming Enable command.

- 4. The Flash is programmed one page at a time. The memory page is loaded one byte at a time by supplying the 6 LSB of the address and data together with the Load Program Memory Page instruction. To ensure correct loading of the page, the data low byte must be loaded before data high byte is applied for a given address. The Program Memory Page is stored by loading the Write Program Memory Page instruction with the 7 MSB of the address. If polling (RDY/BSY) is not used, the user must wait at least t<sub>WD\_FLASH</sub> before issuing the next page (See Table 25-16). Accessing the serial programming interface before the Flash write operation completes can result in incorrect programming.

- 5. A: The EEPROM array is programmed one byte at a time by supplying the address and data together with the appropriate Write instruction. An EEPROM memory location is first automatically erased before new data is written. If polling (RDY/BSY) is not used, the user must wait at least t<sub>WD\_EEPROM</sub> before issuing the next byte (See Table 25-16). In a chip erased device, no 0xFFs in the data file(s) need to be programmed.

**B**: The EEPROM array is programmed one page at a time. The Memory page is loaded one byte at a time by supplying the 6 LSB of the address and data together with the Load EEPROM Memory Page instruction. The EEPROM Memory Page is stored by loading the Write EEPROM Memory Page Instruction with the 7 MSB of the address. When using EEPROM page access only byte locations loaded with the Load EEPROM Memory Page instruction is altered. The remaining locations remain unchanged. If polling (RDY/BSY) is not used, the used must wait at least  $t_{WD\_EEPROM}$  before issuing the next byte (See Table 25-16). In a chip erased device, no 0xFF in the data file(s) need to be programmed.

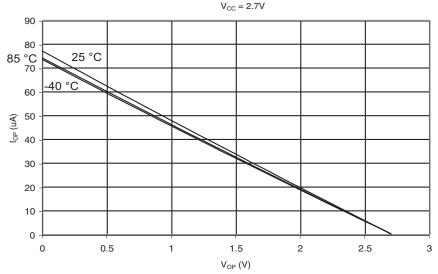

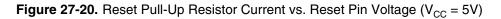

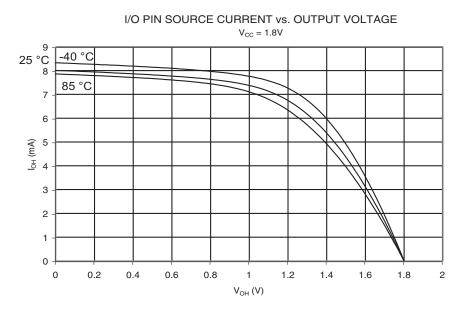

Figure 27-19. I/O Pin Pull-Up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 2.7V)

I/O PIN PULL-UP RESISTOR CURRENT vs. INPUT VOLTAGE

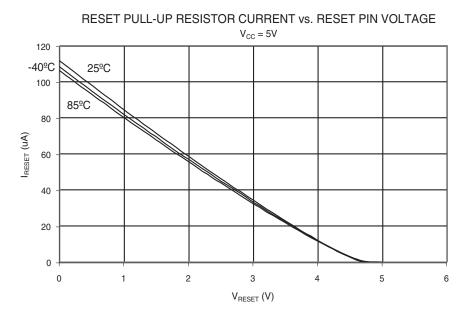

Figure 27-23. I/O Pin Source Current vs. Output Voltage (V<sub>CC</sub> = 2.7V)

I/O PIN SOURCE CURRENT vs. OUTPUT VOLTAGE  $V_{\rm CC}$  = 2.7V

# 336 ATmega48/88/168

| Address                                                                                                                                                                                                           | Name                                                                                                                           | Bit 7                               | Bit 6                       | Bit 5                                             | Bit 4                                                                                                                                                                     | Bit 3                                                                                                                                                                                             | Bit 2                                                               | Bit 1                                | Bit 0                                 | Page                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------|---------------------------------------|-----------------------------------------------------------------|

| (0x7D)                                                                                                                                                                                                            | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x7C)                                                                                                                                                                                                            | ADMUX                                                                                                                          | REFS1                               | REFS0                       | ADLAR                                             | -                                                                                                                                                                         | MUX3                                                                                                                                                                                              | MUX2                                                                | MUX1                                 | MUX0                                  | 250                                                             |

| (0x7B)                                                                                                                                                                                                            | ADCSRB                                                                                                                         | -                                   | ACME                        | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | ADTS2                                                               | ADTS1                                | ADTS0                                 | 253                                                             |

| (0x7A)                                                                                                                                                                                                            | ADCSRA                                                                                                                         | ADEN                                | ADSC                        | ADATE                                             | ADIF                                                                                                                                                                      | ADIE                                                                                                                                                                                              | ADPS2                                                               | ADPS1                                | ADPS0                                 | 251                                                             |

| (0x79)                                                                                                                                                                                                            | ADCH                                                                                                                           |                                     |                             |                                                   | ,                                                                                                                                                                         | gister High byte                                                                                                                                                                                  |                                                                     |                                      |                                       | 253                                                             |

| (0x78)                                                                                                                                                                                                            | ADCL                                                                                                                           |                                     |                             |                                                   | ,                                                                                                                                                                         | gister Low byte                                                                                                                                                                                   |                                                                     |                                      |                                       | 253                                                             |

| (0x77)                                                                                                                                                                                                            | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x76)                                                                                                                                                                                                            | Reserved<br>Reserved                                                                                                           | -                                   | -                           |                                                   | -                                                                                                                                                                         | -                                                                                                                                                                                                 |                                                                     | _                                    | -                                     |                                                                 |

| (0x75)<br>(0x74)                                                                                                                                                                                                  | Reserved                                                                                                                       | _                                   | -                           |                                                   | -                                                                                                                                                                         | -                                                                                                                                                                                                 |                                                                     | -                                    | -                                     |                                                                 |

| (0x74)<br>(0x73)                                                                                                                                                                                                  | Reserved                                                                                                                       | _                                   | _                           |                                                   | _                                                                                                                                                                         | _                                                                                                                                                                                                 | _                                                                   | _                                    |                                       |                                                                 |

| (0x73)<br>(0x72)                                                                                                                                                                                                  | Reserved                                                                                                                       |                                     | _                           |                                                   | _                                                                                                                                                                         | _                                                                                                                                                                                                 |                                                                     | _                                    | _                                     |                                                                 |

| (0x71)                                                                                                                                                                                                            | Reserved                                                                                                                       | _                                   | _                           | _                                                 | _                                                                                                                                                                         | _                                                                                                                                                                                                 | _                                                                   | _                                    | _                                     |                                                                 |

| (0x70)                                                                                                                                                                                                            | TIMSK2                                                                                                                         | _                                   | _                           | _                                                 | _                                                                                                                                                                         | _                                                                                                                                                                                                 | OCIE2B                                                              | OCIE2A                               | TOIE2                                 | 154                                                             |

| (0x6F)                                                                                                                                                                                                            | TIMSK1                                                                                                                         | _                                   | -                           | ICIE1                                             | -                                                                                                                                                                         | -                                                                                                                                                                                                 | OCIE1B                                                              | OCIE1A                               | TOIE1                                 | 133                                                             |

| (0x6E)                                                                                                                                                                                                            | TIMSK0                                                                                                                         | -                                   | _                           | -                                                 | _                                                                                                                                                                         | -                                                                                                                                                                                                 | OCIE0B                                                              | OCIE0A                               | TOIE0                                 | 104                                                             |

| (0x6D)                                                                                                                                                                                                            | PCMSK2                                                                                                                         | PCINT23                             | PCINT22                     | PCINT21                                           | PCINT20                                                                                                                                                                   | PCINT19                                                                                                                                                                                           | PCINT18                                                             | PCINT17                              | PCINT16                               | 87                                                              |

| (0x6C)                                                                                                                                                                                                            | PCMSK1                                                                                                                         | -                                   | PCINT14                     | PCINT13                                           | PCINT12                                                                                                                                                                   | PCINT11                                                                                                                                                                                           | PCINT10                                                             | PCINT9                               | PCINT8                                | 87                                                              |

| (0x6B)                                                                                                                                                                                                            | PCMSK0                                                                                                                         | PCINT7                              | PCINT6                      | PCINT5                                            | PCINT4                                                                                                                                                                    | PCINT3                                                                                                                                                                                            | PCINT2                                                              | PCINT1                               | PCINT0                                | 87                                                              |

| (0x6A)                                                                                                                                                                                                            | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x69)                                                                                                                                                                                                            | EICRA                                                                                                                          | -                                   | -                           | -                                                 | -                                                                                                                                                                         | ISC11                                                                                                                                                                                             | ISC10                                                               | ISC01                                | ISC00                                 | 84                                                              |

| (0x68)                                                                                                                                                                                                            | PCICR                                                                                                                          | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | PCIE2                                                               | PCIE1                                | PCIE0                                 |                                                                 |

| (0x67)                                                                                                                                                                                                            | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x66)                                                                                                                                                                                                            | OSCCAL                                                                                                                         |                                     |                             |                                                   |                                                                                                                                                                           | oration Register                                                                                                                                                                                  |                                                                     |                                      |                                       | 32                                                              |

| (0x65)                                                                                                                                                                                                            | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x64)                                                                                                                                                                                                            | PRR                                                                                                                            | PRTWI                               | PRTIM2                      | PRTIM0                                            | -                                                                                                                                                                         | PRTIM1                                                                                                                                                                                            | PRSPI                                                               | PRUSART0                             | PRADC                                 | 40                                                              |

| (0x63)                                                                                                                                                                                                            | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x62)                                                                                                                                                                                                            | Reserved                                                                                                                       | _                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| (0x61)                                                                                                                                                                                                            | CLKPR                                                                                                                          | CLKPCE                              | -                           | -                                                 | -                                                                                                                                                                         | CLKPS3                                                                                                                                                                                            | CLKPS2                                                              | CLKPS1                               | CLKPS0                                | 35                                                              |

| (0x60)                                                                                                                                                                                                            | WDTCSR                                                                                                                         | WDIF                                | WDIE                        | WDP3                                              | WDCE                                                                                                                                                                      | WDE                                                                                                                                                                                               | WDP2                                                                | WDP1<br>Z                            | WDP0                                  | 52                                                              |

| 0x3F (0x5F)<br>0x3E (0x5E)                                                                                                                                                                                        | SREG<br>SPH                                                                                                                    | -                                   | т<br>–                      | H<br>_                                            | S<br>_                                                                                                                                                                    | V _                                                                                                                                                                                               | N<br>(SP10) <sup>5.</sup>                                           | SP9                                  | C<br>SP8                              | 9 11                                                            |

| 0x3E (0x5E)<br>0x3D (0x5D)                                                                                                                                                                                        | SPH                                                                                                                            | SP7                                 | SP6                         | SP5                                               | <br>SP4                                                                                                                                                                   | SP3                                                                                                                                                                                               | SP2                                                                 | SP9<br>SP1                           | SP0                                   | 11                                                              |

| 0x3C (0x5C)                                                                                                                                                                                                       | Reserved                                                                                                                       | -                                   | _                           | -                                                 | -                                                                                                                                                                         | _                                                                                                                                                                                                 | -                                                                   | _                                    | -                                     |                                                                 |

| 0x3B (0x5B)                                                                                                                                                                                                       | Reserved                                                                                                                       | _                                   | _                           | _                                                 | _                                                                                                                                                                         | _                                                                                                                                                                                                 | _                                                                   | _                                    | _                                     |                                                                 |

| 0x3A (0x5A)                                                                                                                                                                                                       | Reserved                                                                                                                       | _                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| 0x39 (0x59)                                                                                                                                                                                                       | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| 0x38 (0x58)                                                                                                                                                                                                       | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| 0x37 (0x57)                                                                                                                                                                                                       | SPMCSR                                                                                                                         | SPMIE                               | (RWWSB) <sup>5.</sup>       | -                                                 | (RWWSRE) <sup>5.</sup>                                                                                                                                                    | BLBSET                                                                                                                                                                                            | PGWRT                                                               | PGERS                                | SELFPRGEN                             | 269                                                             |

| 0x36 (0x56)                                                                                                                                                                                                       | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| 0x35 (0x55)                                                                                                                                                                                                       | MCUCR                                                                                                                          | -                                   | -                           | -                                                 | PUD                                                                                                                                                                       | -                                                                                                                                                                                                 | -                                                                   | IVSEL                                | IVCE                                  |                                                                 |

| 0x34 (0x54)                                                                                                                                                                                                       | MCUSR                                                                                                                          | -                                   | -                           | -                                                 | -                                                                                                                                                                         | WDRF                                                                                                                                                                                              | BORF                                                                | EXTRF                                | PORF                                  |                                                                 |

| 0x33 (0x53)                                                                                                                                                                                                       | SMCR                                                                                                                           | _                                   | -                           | -                                                 | -                                                                                                                                                                         | SM2                                                                                                                                                                                               | SM1                                                                 | SM0                                  | SE                                    | 37                                                              |

| 0x32 (0x52)                                                                                                                                                                                                       | Reserved                                                                                                                       | -                                   | -                           | _                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| 0x31 (0x51)                                                                                                                                                                                                       | Reserved                                                                                                                       | -                                   | -                           | -                                                 | -                                                                                                                                                                         | -                                                                                                                                                                                                 | -                                                                   | -                                    | -                                     |                                                                 |

| 0x30 (0x50)                                                                                                                                                                                                       | ACSR                                                                                                                           | ACD                                 | ACBG                        | ACO                                               | ACI                                                                                                                                                                       | ACIE                                                                                                                                                                                              | ACIC                                                                | ACIS1                                | ACIS0                                 | 236                                                             |