Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48v-10pu |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Oscillator Source /<br>Power Conditions | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | CKSEL0 | SUT10 |

|-----------------------------------------|----------------------------------------------------|------------------------------------------------------------|--------|-------|

| Crystal Oscillator, BOD enabled         | 16K CK                                             | 14CK                                                       | 1      | 01    |

| Crystal Oscillator, fast rising power   | 16K CK                                             | 14CK + 4.1 ms                                              | 1      | 10    |

| Crystal Oscillator, slowly rising power | 16K CK                                             | 14CK + 65 ms                                               | 1      | 11    |

Table 6-4.

Start-up Times for the Low Power Crystal Oscillator Clock Selection (Continued)

Notes: 1. These options should only be used when not operating close to the maximum frequency of the device, and only if frequency stability at start-up is not important for the application. These options are not suitable for crystals.

2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum frequency of the device, and if frequency stability at start-up is not important for the application.

# 6.4 Full Swing Crystal Oscillator

Pins XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in Figure 6-2. Either a quartz crystal or a ceramic resonator may be used.

This Crystal Oscillator is a full swing oscillator, with rail-to-rail swing on the XTAL2 output. This is useful for driving other clock inputs and in noisy environments. The current consumption is higher than the "Low Power Crystal Oscillator" on page 27. Note that the Full Swing Crystal Oscillator will only operate for  $V_{CC} = 2.7 - 5.5$  volts.

C1 and C2 should always be equal for both crystals and resonators. The optimal value of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for choosing capacitors for use with crystals are given in Table 6-6. For ceramic resonators, the capacitor values given by the manufacturer should be used.

The operating mode is selected by the fuses CKSEL3..1 as shown in Table 6-5.

Table 6-5.

Full Swing Crystal Oscillator operating modes<sup>(2)</sup>

| Frequency Range <sup>(1)</sup><br>(MHz) | Recommended Range for<br>Capacitors C1 and C2 (pF) | CKSEL31 |

|-----------------------------------------|----------------------------------------------------|---------|

| 0.4 - 20                                | 12 - 22                                            | 011     |

Notes: 1. The frequency ranges are preliminary values. Actual values are TBD.

If 8 MHz frequency exceeds the specification of the device (depends on V<sub>CC</sub>), the CKDIV8 Fuse can be programmed in order to divide the internal frequency by 8. It must be ensured that the resulting divided clock meets the frequency specification of the device.

# 8. System Control and Reset

#### 8.0.1 Resetting the AVR

During reset, all I/O Registers are set to their initial values, and the program starts execution from the Reset Vector. For the ATmega168, the instruction placed at the Reset Vector must be a JMP – Absolute Jump – instruction to the reset handling routine. For the ATmega48 and ATmega88, the instruction placed at the Reset Vector must be an RJMP – Relative Jump – instruction to the reset handling routine. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa (ATmega88/168 only). The circuit diagram in Figure 8-1 shows the reset logic. Table 8-1 defines the electrical parameters of the reset circuitry.

The I/O ports of the AVR are immediately reset to their initial state when a reset source goes active. This does not require any clock source to be running.

After all reset sources have gone inactive, a delay counter is invoked, stretching the internal reset. This allows the power to reach a stable level before normal operation starts. The time-out period of the delay counter is defined by the user through the SUT and CKSEL Fuses. The different selections for the delay period are presented in "Clock Sources" on page 26.

#### 8.0.2 Reset Sources

The ATmega48/88/168 has four sources of reset:

- Power-on Reset. The MCU is reset when the supply voltage is below the Power-on Reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for longer than the minimum pulse length.

- Watchdog System Reset. The MCU is reset when the Watchdog Timer period expires and the Watchdog System Reset mode is enabled.

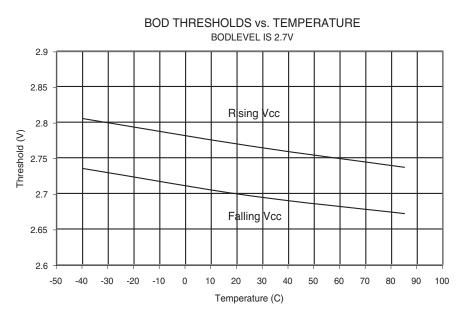

- Brown-out Reset. The MCU is reset when the supply voltage  $V_{CC}$  is below the Brown-out Reset threshold ( $V_{BOT}$ ) and the Brown-out Detector is enabled.

# ATmega48/88/168

Note: If the Watchdog is accidentally enabled, for example by a runaway pointer or brown-out condition, the device will be reset and the Watchdog Timer will stay enabled. If the code is not set up to handle the Watchdog, this might lead to an eternal loop of time-out resets. To avoid this situation, the application software should always clear the Watchdog System Reset Flag (WDRF) and the WDE control bit in the initialisation routine, even if the Watchdog is not in use.

The following code example shows one assembly and one C function for changing the time-out value of the Watchdog Timer.

```

Assembly Code Example<sup>(1)</sup>

WDT_Prescaler_Change:

; Turn off global interrupt

cli

; Reset Watchdog Timer

wdr

; Start timed sequence

lds r16, WDTCSR

ori

r16, (1<<WDCE) | (1<<WDE)

sts WDTCSR, r16

; -- Got four cycles to set the new values from here -

; Set new prescaler(time-out) value = 64K cycles (~0.5 s)

r16, (1<<WDE) | (1<<WDP2) | (1<<WDP0)

ldi

sts WDTCSR, r16

; -- Finished setting new values, used 2 cycles -

; Turn on global interrupt

sei

ret

C Code Example<sup>(1)</sup>

void WDT_Prescaler_Change(void)

{

__disable_interrupt();

__watchdog_reset();

/* Start timed equence */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* Set new prescaler(time-out) value = 64K cycles (~0.5 s) */

WDTCSR = (1<<WDE) | (1<<WDP2) | (1<<WDP0);

_enable_interrupt();

}

```

Note: 1. See "About Code Examples" on page 6.

Note: The Watchdog Timer should be reset before any change of the WDP bits, since a change in the WDP bits can result in a time-out when switching to a shorter time-out period.

#### • Bit 0 – IVCE: Interrupt Vector Change Enable

The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts, as explained in the IVSEL description above. See Code Example below.

```

Assembly Code Example

```

```

Move_interrupts:

; Enable change of Interrupt Vectors

ldi r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ldi r16, (1<<IVSEL)

out MCUCR, r16

ret

```

C Code Example

```

void Move_interrupts(void)

```

```

{

/* Enable change of Interrupt Vectors */

MCUCR = (1<<IVCE);

/* Move interrupts to Boot Flash section */

MCUCR = (1<<IVSEL);

}</pre>

```

This bit is not available in ATmega48.

#### Assembly Code Example<sup>(1)</sup>

| TIM16_ReadTCNT1:                  |

|-----------------------------------|

| ; Save global interrupt flag      |

| in r18,SREG                       |

| ; Disable interrupts              |

| cli                               |

| ; Read TCNT <b>1</b> into r17:r16 |

| in r16,TCNT1L                     |

| in r17, TCNT1H                    |

| ; Restore global interrupt flag   |

| out SREG, r18                     |

| ret                               |

C Code Example<sup>(1)</sup>

```

unsigned int TIM16_ReadTCNT1( void )

{

unsigned char sreg;

unsigned int i;

/* Save global interrupt flag */

sreg = SREG;

/* Disable interrupts */

_CLI();

/* Read TCNT1 into i */

i = TCNT1;

/* Restore global interrupt flag */

SREG = sreg;

return i;

}

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNT1 value in the r17:r16 register pair.

The following code examples show how to do an atomic write of the TCNT1 Register contents. Writing any of the OCR1A/B or ICR1 Registers can be done by using the same principle.

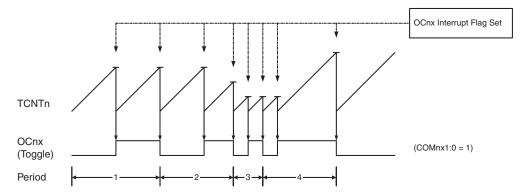

Figure 15-5. CTC Mode, Timing Diagram

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF2A Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR2A is lower than the current value of TCNT2, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur.

For generating a waveform output in CTC mode, the OC2A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM2A1:0 = 1). The OC2A value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC2A} = f_{clk\_l/O}/2$  when OCR2A is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCnx} = \frac{f_{clk\_I/O}}{2 \cdot N \cdot (1 + OCRnx)}$$

The *N* variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

As for the Normal mode of operation, the TOV2 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

#### 15.6.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM22:0 = 3 or 7) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOT-TOM. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. In noninverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x, and set at BOTTOM. In inverting Compare Output mode, the output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that uses dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

nine data bits, then the ninth bit (RXB8n) is used for identifying address and data frames. When the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the frame type bit is zero the frame is a data frame.

The Multi-processor Communication mode enables several slave MCUs to receive data from a master MCU. This is done by first decoding an address frame to find out which MCU has been addressed. If a particular slave MCU has been addressed, it will receive the following data frames as normal, while the other slave MCUs will ignore the received frames until another address frame is received.

#### 17.8.1 Using MPCMn

For an MCU to act as a master MCU, it can use a 9-bit character frame format (UCSZn = 7). The ninth bit (TXB8n) must be set when an address frame (TXB8n = 1) or cleared when a data frame (TXB = 0) is being transmitted. The slave MCUs must in this case be set to use a 9-bit character frame format.

The following procedure should be used to exchange data in Multi-processor Communication mode:

- 1. All Slave MCUs are in Multi-processor Communication mode (MPCMn in UCSRnA is set).

- 2. The Master MCU sends an address frame, and all slaves receive and read this frame. In the Slave MCUs, the RXCn Flag in UCSRnA will be set as normal.

- 3. Each Slave MCU reads the UDRn Register and determines if it has been selected. If so, it clears the MPCMn bit in UCSRnA, otherwise it waits for the next address byte and keeps the MPCMn setting.

- 4. The addressed MCU will receive all data frames until a new address frame is received. The other Slave MCUs, which still have the MPCMn bit set, will ignore the data frames.

- 5. When the last data frame is received by the addressed MCU, the addressed MCU sets the MPCMn bit and waits for a new address frame from master. The process then repeats from 2.

Using any of the 5- to 8-bit character frame formats is possible, but impractical since the Receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult since the Transmitter and Receiver uses the same character size setting. If 5- to 8-bit character frames are used, the Transmitter must be set to use two stop bit (USBSn = 1) since the first stop bit is used for indicating the frame type.

Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCMn bit. The MPCMn bit shares the same I/O location as the TXCn Flag and this might accidentally be cleared when using SBI or CBI instructions.

|                     | f <sub>osc</sub> = 1.0000 MHz |               |           |                | f <sub>osc</sub> = 1.8432 MHz |          |           |          | f <sub>osc</sub> = 2.0000 MHz |          |           |       |

|---------------------|-------------------------------|---------------|-----------|----------------|-------------------------------|----------|-----------|----------|-------------------------------|----------|-----------|-------|

| Baud                | U2X                           | U2Xn = 0 U2Xr |           | n = 1 U2Xn = 0 |                               | U2Xn = 1 |           | U2Xn = 0 |                               | U2Xn = 1 |           |       |

| Rate<br>(bps)       | UBRR<br>n                     | Error         | UBRR<br>n | Error          | UBRR<br>n                     | Error    | UBRR<br>n | Error    | UBRR<br>n                     | Error    | UBRR<br>n | Error |

| 2400                | 25                            | 0.2%          | 51        | 0.2%           | 47                            | 0.0%     | 95        | 0.0%     | 51                            | 0.2%     | 103       | 0.2%  |

| 4800                | 12                            | 0.2%          | 25        | 0.2%           | 23                            | 0.0%     | 47        | 0.0%     | 25                            | 0.2%     | 51        | 0.2%  |

| 9600                | 6                             | -7.0%         | 12        | 0.2%           | 11                            | 0.0%     | 23        | 0.0%     | 12                            | 0.2%     | 25        | 0.2%  |

| 14.4k               | 3                             | 8.5%          | 8         | -3.5%          | 7                             | 0.0%     | 15        | 0.0%     | 8                             | -3.5%    | 16        | 2.1%  |

| 19.2k               | 2                             | 8.5%          | 6         | -7.0%          | 5                             | 0.0%     | 11        | 0.0%     | 6                             | -7.0%    | 12        | 0.2%  |

| 28.8k               | 1                             | 8.5%          | 3         | 8.5%           | 3                             | 0.0%     | 7         | 0.0%     | 3                             | 8.5%     | 8         | -3.5% |

| 38.4k               | 1                             | -18.6%        | 2         | 8.5%           | 2                             | 0.0%     | 5         | 0.0%     | 2                             | 8.5%     | 6         | -7.0% |

| 57.6k               | 0                             | 8.5%          | 1         | 8.5%           | 1                             | 0.0%     | 3         | 0.0%     | 1                             | 8.5%     | 3         | 8.5%  |

| 76.8k               | _                             | _             | 1         | -18.6%         | 1                             | -25.0%   | 2         | 0.0%     | 1                             | -18.6%   | 2         | 8.5%  |

| 115.2k              | _                             | _             | 0         | 8.5%           | 0                             | 0.0%     | 1         | 0.0%     | 0                             | 8.5%     | 1         | 8.5%  |

| 230.4k              | _                             | _             | _         | _              | -                             | _        | 0         | 0.0%     | _                             | -        | _         | -     |

| 250k                | _                             | _             | _         | -              | -                             | _        | -         | _        | -                             | -        | 0         | 0.0%  |

| Max. <sup>(1)</sup> | 62.5                          | kbps          | 125       | kbps           | 115.2                         | 2 kbps   | 230.4     | l kbps   | 125                           | kbps     | 250       | kbps  |

Table 17-9.

Examples of UBRRn Settings for Commonly Used Oscillator Frequencies

Note: 1. UBRRn = 0, Error = 0.0%

The PRTWI bit in "Power Reduction Register - PRR" on page 40 must be written to zero to enable the 2-wire Serial Interface.

#### 19.2.2 Electrical Interconnection

As depicted in Figure 19-1, both bus lines are connected to the positive supply voltage through pull-up resistors. The bus drivers of all TWI-compliant devices are open-drain or open-collector. This implements a wired-AND function which is essential to the operation of the interface. A low level on a TWI bus line is generated when one or more TWI devices output a zero. A high level is output when all TWI devices tri-state their outputs, allowing the pull-up resistors to pull the line high. Note that all AVR devices connected to the TWI bus must be powered in order to allow any bus operation.

The number of devices that can be connected to the bus is only limited by the bus capacitance limit of 400 pF and the 7-bit slave address space. A detailed specification of the electrical characteristics of the TWI is given in "2-wire Serial Interface Characteristics" on page 302. Two different sets of specifications are presented there, one relevant for bus speeds below 100 kHz, and one valid for bus speeds up to 400 kHz.

# 19.3 Data Transfer and Frame Format

#### 19.3.1 Transferring Bits

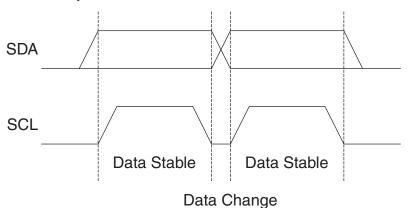

Each data bit transferred on the TWI bus is accompanied by a pulse on the clock line. The level of the data line must be stable when the clock line is high. The only exception to this rule is for generating start and stop conditions.

#### Figure 19-2. Data Validity

#### 19.3.2 START and STOP Conditions

The Master initiates and terminates a data transmission. The transmission is initiated when the Master issues a START condition on the bus, and it is terminated when the Master issues a STOP condition. Between a START and a STOP condition, the bus is considered busy, and no other master should try to seize control of the bus. A special case occurs when a new START condition is issued between a START and STOP condition. This is referred to as a REPEATED START condition, and is used when the Master wishes to initiate a new transfer without relinquishing control of the bus. After a REPEATED START, the bus is considered busy until the next STOP. This is identical to the START behavior, and therefore START is used to describe both START and REPEATED START for the remainder of this datasheet, unless otherwise noted. As

#### • Bit 6 – TWEA: TWI Enable Acknowledge Bit

The TWEA bit controls the generation of the acknowledge pulse. If the TWEA bit is written to one, the ACK pulse is generated on the TWI bus if the following conditions are met:

- 1. The device's own slave address has been received.

- 2. A general call has been received, while the TWGCE bit in the TWAR is set.

- 3. A data byte has been received in Master Receiver or Slave Receiver mode.

By writing the TWEA bit to zero, the device can be virtually disconnected from the 2-wire Serial Bus temporarily. Address recognition can then be resumed by writing the TWEA bit to one again.

#### • Bit 5 – TWSTA: TWI START Condition Bit

The application writes the TWSTA bit to one when it desires to become a Master on the 2-wire Serial Bus. The TWI hardware checks if the bus is available, and generates a START condition on the bus if it is free. However, if the bus is not free, the TWI waits until a STOP condition is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted.

#### Bit 4 – TWSTO: TWI STOP Condition Bit

Writing the TWSTO bit to one in Master mode will generate a STOP condition on the 2-wire Serial Bus. When the STOP condition is executed on the bus, the TWSTO bit is cleared automatically. In Slave mode, setting the TWSTO bit can be used to recover from an error condition. This will not generate a STOP condition, but the TWI returns to a well-defined unaddressed Slave mode and releases the SCL and SDA lines to a high impedance state.

#### Bit 3 – TWWC: TWI Write Collision Flag

The TWWC bit is set when attempting to write to the TWI Data Register – TWDR when TWINT is low. This flag is cleared by writing the TWDR Register when TWINT is high.

#### • Bit 2 – TWEN: TWI Enable Bit

The TWEN bit enables TWI operation and activates the TWI interface. When TWEN is written to one, the TWI takes control over the I/O pins connected to the SCL and SDA pins, enabling the slew-rate limiters and spike filters. If this bit is written to zero, the TWI is switched off and all TWI transmissions are terminated, regardless of any ongoing operation.

#### • Bit 1 - Res: Reserved Bit

This bit is a reserved bit and will always read as zero.

#### • Bit 0 – TWIE: TWI Interrupt Enable

When this bit is written to one, and the I-bit in SREG is set, the TWI interrupt request will be activated for as long as the TWINT Flag is high.

#### 19.6.3 TWI Status Register – TWSR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2 | 1     | 0     | _    |

|---------------|------|------|------|------|------|---|-------|-------|------|

|               | TWS7 | TWS6 | TWS5 | TWS4 | TWS3 | - | TWPS1 | TWPS0 | TWSR |

| Read/Write    | R    | R    | R    | R    | R    | R | R/W   | R/W   |      |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 0 | 0     | 0     |      |

#### • Bits 7..3 - TWS: TWI Status

These 5 bits reflect the status of the TWI logic and the 2-wire Serial Bus. The different status codes are described later in this section. Note that the value read from TWSR contains both the 5-bit status value and the 2-bit prescaler value. The application designer should mask the prescaler bits to zero when checking the Status bits. This makes status checking independent of prescaler setting. This approach is used in this datasheet, unless otherwise noted.

#### Bit 2 – Res: Reserved Bit

This bit is reserved and will always read as zero.

#### • Bits 1..0 - TWPS: TWI Prescaler Bits

These bits can be read and written, and control the bit rate prescaler.

| TWPS1 | TWPS0 | Prescaler Value |

|-------|-------|-----------------|

| 0     | 0     | 1               |

| 0     | 1     | 4               |

| 1     | 0     | 16              |

| 1     | 1     | 64              |

Table 19-2.

TWI Bit Rate Prescaler

To calculate bit rates, see "Bit Rate Generator Unit" on page 211. The value of TWPS1..0 is used in the equation.

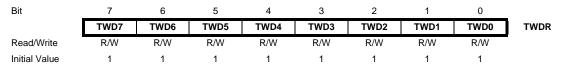

#### 19.6.4 TWI Data Register – TWDR

In Transmit mode, TWDR contains the next byte to be transmitted. In Receive mode, the TWDR contains the last byte received. It is writable while the TWI is not in the process of shifting a byte. This occurs when the TWI Interrupt Flag (TWINT) is set by hardware. Note that the Data Register cannot be initialized by the user before the first interrupt occurs. The data in TWDR remains stable as long as TWINT is set. While data is shifted out, data on the bus is simultaneously shifted in. TWDR always contains the last byte present on the bus, except after a wake up from a sleep mode by the TWI interrupt. In this case, the contents of TWDR is undefined. In the case of a lost bus arbitration, no data is lost in the transition from Master to Slave. Handling of the ACK bit is controlled automatically by the TWI logic, the CPU cannot access the ACK bit directly.

|   | Assembly Code Example                                                                                                                                        | C Example                                                                                            | Comments                                                      |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|   | <b>ldi</b> r16,                                                                                                                                              | TWCR = $(1 < TWINT)   (1 < TWSTA)  $                                                                 |                                                               |

| 1 | (1 << TWINT)   (1 << TWSTA)                                                                                                                                  | (1< <twen)< td=""><td>Send START condition</td></twen)<>                                             | Send START condition                                          |

|   | (1< <twen)< td=""><td></td><td>Sena STATT condition</td></twen)<>                                                                                            |                                                                                                      | Sena STATT condition                                          |

|   | out TWCR, r16                                                                                                                                                |                                                                                                      |                                                               |

|   | wait1:                                                                                                                                                       | <pre>while (!(TWCR &amp; (1&lt;<twint)))< pre=""></twint)))<></pre>                                  |                                                               |

| 2 | in r16,TWCR                                                                                                                                                  | ;                                                                                                    | Wait for TWINT Flag set. This<br>indicates that the START     |

| 2 | <b>sbrs</b> r16,TWINT                                                                                                                                        |                                                                                                      | condition has been transmitted                                |

|   | <b>rjmp</b> wait1                                                                                                                                            |                                                                                                      |                                                               |

|   | in r16,TWSR                                                                                                                                                  | <b>if</b> ((TWSR & 0xF8) != START)                                                                   | Check value of TWI Status                                     |

|   | <b>andi</b> r16, 0xF8                                                                                                                                        | ERROR();                                                                                             | Register. Mask prescaler bits. If                             |

|   | <b>cpi</b> r16, START                                                                                                                                        |                                                                                                      | status different from START go to                             |

|   | brne ERROR                                                                                                                                                   |                                                                                                      | ERROR                                                         |

| 3 | ldi r16, SLA_W                                                                                                                                               | TWDR = SLA_W;                                                                                        |                                                               |

|   | out TWDR, r16                                                                                                                                                | TWCR = (1< <twint)< td=""><td>Load SLA_W into TWDR</td></twint)<>                                    | Load SLA_W into TWDR                                          |

|   | <b>ldi</b> r16, (1< <twint)< td=""><td>(1&lt;<twen);< td=""><td>Register. Clear TWINT bit in<br/>TWCR to start transmission of</td></twen);<></td></twint)<> | (1< <twen);< td=""><td>Register. Clear TWINT bit in<br/>TWCR to start transmission of</td></twen);<> | Register. Clear TWINT bit in<br>TWCR to start transmission of |

|   | (1< <twen)< td=""><td></td><td>address</td></twen)<>                                                                                                         |                                                                                                      | address                                                       |

|   | out TWCR, r16                                                                                                                                                |                                                                                                      |                                                               |

|   | wait2:                                                                                                                                                       | <pre>while (!(TWCR &amp; (1&lt;<twint)))< pre=""></twint)))<></pre>                                  | Wait for TWINT Flag set. This                                 |

| 4 | in r16,TWCR                                                                                                                                                  | ;                                                                                                    | indicates that the SLA+W has                                  |

| 4 | <b>sbrs</b> r16,TWINT                                                                                                                                        |                                                                                                      | been transmitted, and                                         |

|   | <b>rjmp</b> wait2                                                                                                                                            |                                                                                                      | ACK/NACK has been received.                                   |

|   | in r16,TWSR                                                                                                                                                  | <b>if</b> ((TWSR & 0xF8) !=                                                                          | Check value of TWI Status                                     |

|   | <b>andi</b> r16, 0xF8                                                                                                                                        | MT_SLA_ACK)                                                                                          | Register. Mask prescaler bits. If                             |

|   | <b>cpi</b> r16, MT_SLA_ACK                                                                                                                                   | ERROR();                                                                                             | status different from                                         |

|   | brne ERROR                                                                                                                                                   |                                                                                                      | MT_SLA_ACK go to ERROR                                        |

| 5 | ldi r16, DATA                                                                                                                                                | TWDR = DATA;                                                                                         |                                                               |

|   | out TWDR, r16                                                                                                                                                | TWCR = (1< <twint)< td=""><td>Load DATA into TWDR Register.</td></twint)<>                           | Load DATA into TWDR Register.                                 |

|   | <b>ldi</b> r16, (1< <twint)< td=""><td>(1&lt;<twen);< td=""><td>Clear TWINT bit in TWCR to</td></twen);<></td></twint)<>                                     | (1< <twen);< td=""><td>Clear TWINT bit in TWCR to</td></twen);<>                                     | Clear TWINT bit in TWCR to                                    |

|   | (1< <twen)< td=""><td></td><td>start transmission of data</td></twen)<>                                                                                      |                                                                                                      | start transmission of data                                    |

|   | out TWCR, r16                                                                                                                                                |                                                                                                      |                                                               |

|   | wait3:                                                                                                                                                       | while (!(TWCR & (1< <twint)))< td=""><td>Wait for TWINT Flag set. This</td></twint)))<>              | Wait for TWINT Flag set. This                                 |

| 6 | in r16,TWCR                                                                                                                                                  | ;                                                                                                    | indicates that the DATA has been                              |

| 6 | <b>sbrs</b> r16, TWINT                                                                                                                                       |                                                                                                      | transmitted, and ACK/NACK has                                 |

|   | <b>rjmp</b> wait3                                                                                                                                            |                                                                                                      | been received.                                                |

|   | in r16,TWSR                                                                                                                                                  | <b>if</b> ((TWSR & 0xF8) !=                                                                          | Check value of TWI Status                                     |

|   | <b>andi</b> r16, 0xF8                                                                                                                                        | MT_DATA_ACK)                                                                                         | Register. Mask prescaler bits. If                             |

|   | <b>cpi</b> r16, MT_DATA_ACK                                                                                                                                  | ERROR();                                                                                             | status different from                                         |

| 7 | brne ERROR                                                                                                                                                   |                                                                                                      | MT_DATA_ACK go to ERROR                                       |

| 7 | <b>ldi</b> r16,                                                                                                                                              | TWCR = (1< <twint) (1<<twen)="" td=""  =""  <=""><td></td></twint)>                                  |                                                               |

|   | (1< <twint) (1<<twen)="" td=""  =""  <=""><td>(1&lt;<twsto);< td=""><td></td></twsto);<></td></twint)>                                                       | (1< <twsto);< td=""><td></td></twsto);<>                                                             |                                                               |

|   | (1< <twsto)< td=""><td></td><td>Transmit STOP condition</td></twsto)<>                                                                                       |                                                                                                      | Transmit STOP condition                                       |

|   | out TWCR, r16                                                                                                                                                |                                                                                                      |                                                               |

Notes:

#### : 1. See Table 20-2 on page 238.

2. Refer to Figure 1-1 on page 2 and Table 10-9 on page 78 for Analog Comparator pin placement.

#### 20.0.1 ADC Control and Status Register B – ADCSRB

| Bit           | 7 | 6    | 5 | 4 | 3 | 2     | 1     | 0     | _      |

|---------------|---|------|---|---|---|-------|-------|-------|--------|

|               | - | ACME | - | - | - | ADTS2 | ADTS1 | ADTS0 | ADCSRB |

| Read/Write    | R | R/W  | R | R | R | R/W   | R/W   | R/W   |        |

| Initial Value | 0 | 0    | 0 | 0 | 0 | 0     | 0     | 0     |        |

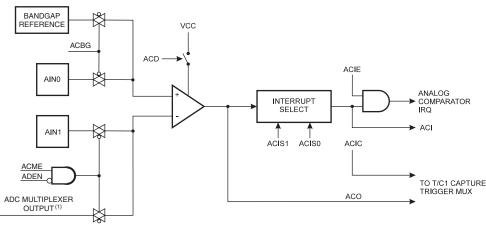

#### Bit 6 – ACME: Analog Comparator Multiplexer Enable

When this bit is written logic one and the ADC is switched off (ADEN in ADCSRA is zero), the ADC multiplexer selects the negative input to the Analog Comparator. When this bit is written logic zero, AIN1 is applied to the negative input of the Analog Comparator. For a detailed description of this bit, see "Analog Comparator Multiplexed Input" on page 237.

#### 20.0.2 Analog Comparator Control and Status Register – ACSR

| Bit           | 7   | 6    | 5   | 4   | 3    | 2    | 1     | 0     | _    |

|---------------|-----|------|-----|-----|------|------|-------|-------|------|

|               | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR |

| Read/Write    | R/W | R/W  | R   | R/W | R/W  | R/W  | R/W   | R/W   | -    |

| Initial Value | 0   | 0    | N/A | 0   | 0    | 0    | 0     | 0     |      |

#### • Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

#### Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AINO is applied to the positive input of the Analog Comparator. See Section "8.1" on page 48.

# 22. debugWIRE On-chip Debug System

# 22.1 Features

- Complete Program Flow Control

- Emulates All On-chip Functions, Both Digital and Analog, except RESET Pin

- Real-time Operation

- Symbolic Debugging Support (Both at C and Assembler Source Level, or for Other HLLs)

- Unlimited Number of Program Break Points (Using Software Break Points)

- Non-intrusive Operation

- Electrical Characteristics Identical to Real Device

- Automatic Configuration System

- High-Speed Operation

- Programming of Non-volatile Memories

# 22.2 Overview

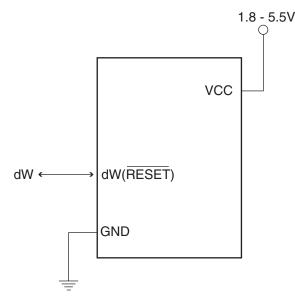

The debugWIRE On-chip debug system uses a One-wire, bi-directional interface to control the program flow, execute AVR instructions in the CPU and to program the different non-volatile memories.

### 22.3 Physical Interface

When the debugWIRE Enable (DWEN) Fuse is programmed and Lock bits are unprogrammed, the debugWIRE system within the target device is activated. The RESET port pin is configured as a wire-AND (open-drain) bi-directional I/O pin with pull-up enabled and becomes the communication gateway between target and emulator.

#### Figure 22-1. The debugWIRE Setup

Figure 22-1 shows the schematic of a target MCU, with debugWIRE enabled, and the emulator connector. The system clock is not affected by debugWIRE and will always be the clock source selected by the CKSEL Fuses.

#### Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |           | Instructio        | on Format         |                   |                                                                                                                                          |

|-------------------------------------------|-----------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                               | Byte 1    | Byte 2            | Byte 3            | Byte4             | Operation                                                                                                                                |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001 | 0000 0000         | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |

| Write EEPROM Memory<br>Page (page access) | 1100 0010 | 00xx xx <b>aa</b> | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |

| Read Lock bits                            | 0101 1000 | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |

| Write Lock bits                           | 1010 1100 | 111x xxxx         | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |

| Read Signature Byte                       | 0011 0000 | 000x xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |

| Write Fuse bits                           | 1010 1100 | 1010 0000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |

| Write Fuse High bits                      | 1010 1100 | 1010 1000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |

| Write Extended Fuse Bits                  | 1010 1100 | 1010 0100         | xxxx xxxx         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |

| Read Fuse bits                            | 0101 0000 | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |

| Read Fuse High bits                       | 0101 1000 | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |

| Read Extended Fuse Bits                   | 0101 0000 | 0000 1000         | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |

| Read Calibration Byte                     | 0011 1000 | 000x xxxx         | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |

| Poll RDY/BSY                              | 1111 0000 | 0000 0000         | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

#### 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

ATmega48/88/168

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

- All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon

- 6. Values with "Power Reduction Register PRR" disabled (0x00).

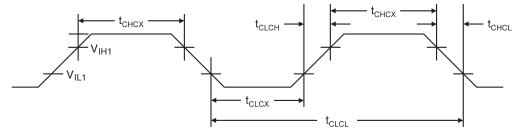

# 26.3 External Clock Drive Waveforms

#### Figure 26-1. External Clock Drive Waveforms

### 26.4 External Clock Drive

|                     |                                                         | V <sub>CC</sub> =1.8-5.5V |      | V <sub>CC</sub> =2.7-5.5V |      | V <sub>CC</sub> =4.5-5.5V |      |       |  |

|---------------------|---------------------------------------------------------|---------------------------|------|---------------------------|------|---------------------------|------|-------|--|

| Symbol              | Parameter                                               | Min.                      | Max. | Min.                      | Max. | Min.                      | Max. | Units |  |

| 1/t <sub>CLCL</sub> | Oscillator<br>Frequency                                 | 0                         | 4    | 0                         | 10   | 0                         | 20   | MHz   |  |

| t <sub>CLCL</sub>   | Clock Period                                            | 250                       |      | 100                       |      | 50                        |      | ns    |  |

| t <sub>CHCX</sub>   | High Time                                               | 100                       |      | 40                        |      | 20                        |      | ns    |  |

| t <sub>CLCX</sub>   | Low Time                                                | 100                       |      | 40                        |      | 20                        |      | ns    |  |

| t <sub>CLCH</sub>   | Rise Time                                               |                           | 2.0  |                           | 1.6  |                           | 0.5  | μs    |  |

| t <sub>CHCL</sub>   | Fall Time                                               |                           | 2.0  |                           | 1.6  |                           | 0.5  | μS    |  |

| $\Delta t_{CLCL}$   | Change in period<br>from one clock<br>cycle to the next |                           | 2    |                           | 2    |                           | 2    | %     |  |

Table 26-1.External Clock Drive

Note: All DC Characteristics contained in this datasheet are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are preliminary values representing design targets, and will be updated after characterization of actual silicon.

# 26.5 Maximum Speed vs. V<sub>CC</sub>

Maximum frequency is dependent on V<sub>CC.</sub> As shown in Figure 26-2 and Figure 26-3, the Maximum Frequency vs. V<sub>CC</sub> curve is linear between  $1.8V < V_{CC} < 2.7V$  and between  $2.7V < V_{CC} < 4.5V$ .

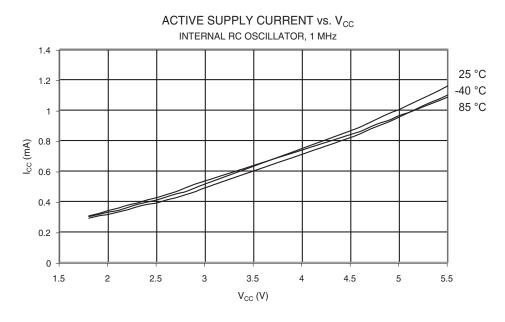

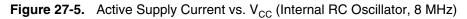

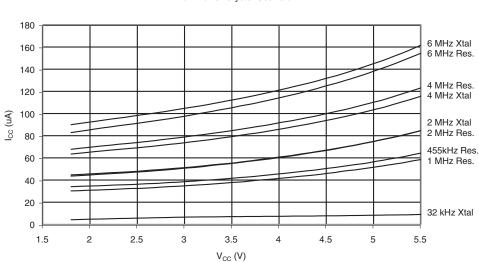

Figure 27-4. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 1 MHz)

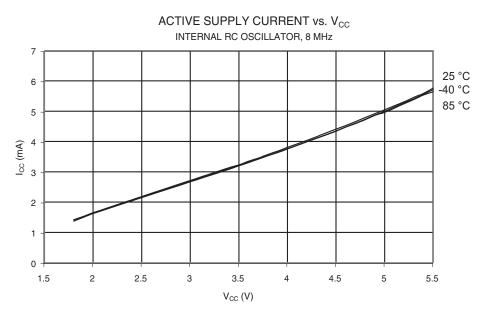

# 27.5 Power-Save Supply Current

Figure 27-15. Power-Save Supply Current vs. V<sub>CC</sub> (Watchdog Timer Disabled)

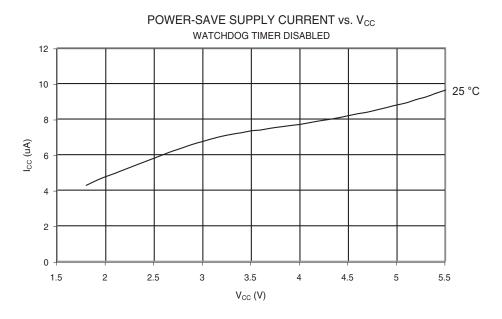

# 27.6 Standby Supply Current

STANDBY SUPPLY CURRENT vs. V<sub>CC</sub> Low Power Crystal Oscillator

# 27.10 BOD Thresholds and Analog Comparator Offset

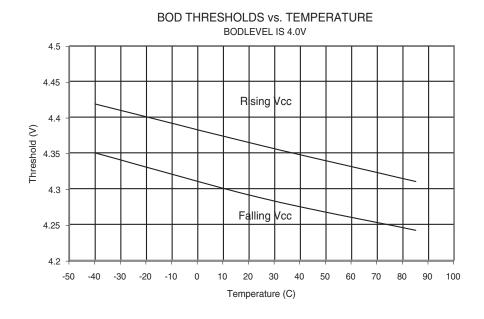

Figure 27-33. BOD Thresholds vs. Temperature (BODLEVEL Is 4.0V)

|    | 17.10Examples of Baud Rate Setting                            | 191 |

|----|---------------------------------------------------------------|-----|

| 18 | USART in SPI Mode                                             | 196 |

|    | 18.1Overview                                                  | 196 |

|    | 18.2Clock Generation                                          | 196 |

|    | 18.3SPI Data Modes and Timing                                 | 197 |

|    | 18.4Frame Formats                                             | 198 |

|    | 18.5Data Transfer                                             | 199 |

|    | 18.6USART MSPIM Register Description                          | 201 |

|    | 18.7AVR USART MSPIM vs. AVR SPI                               | 204 |

| 19 | 2-wire Serial Interface                                       | 205 |

|    | 19.1Features                                                  | 205 |

|    | 19.22-wire Serial Interface Bus Definition                    | 205 |

|    | 19.3Data Transfer and Frame Format                            | 206 |

|    | 19.4Multi-master Bus Systems, Arbitration and Synchronization | 209 |

|    | 19.5Overview of the TWI Module                                | 211 |

|    | 19.6TWI Register Description                                  | 213 |

|    | 19.7Using the TWI                                             | 217 |

|    | 19.8Transmission Modes                                        | 221 |

|    | 19.9Multi-master Systems and Arbitration                      | 234 |

| 20 | Analog Comparator                                             | 235 |

|    | 20.1Analog Comparator Multiplexed Input                       | 237 |

| 21 | Analog-to-Digital Converter                                   | 239 |

|    | 21.1Features                                                  | 239 |

|    | 21.2Starting a Conversion                                     | 241 |

|    | 21.3Prescaling and Conversion Timing                          | 242 |

|    | 21.4Changing Channel or Reference Selection                   | 244 |

|    | 21.5ADC Noise Canceler                                        | 245 |

|    | 21.6ADC Conversion Result                                     | 250 |

| 22 | debugWIRE On-chip Debug System                                | 255 |

|    | 22.1Features                                                  | 255 |

|    | 22.20verview                                                  | 255 |

|    | 22.3Physical Interface                                        | 255 |

|    | 22.4Software Break Points                                     | 256 |

|    | 22.5Limitations of debugWIRE                                  | 256 |