# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega88-20aj |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In ATmega48, there is no Read-While-Write support and no separate Boot Loader Section. The SPM instruction can execute from the entire Flash.

# 2.3 Pin Descriptions

| 2.3. | 1 | VCC |

|------|---|-----|

|      |   |     |

- Digital supply voltage.

- 2.3.2 GND

Ground.

# 2.3.3 Port B (PB7..0) XTAL1/XTAL2/TOSC1/TOSC2

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.

If the Internal Calibrated RC Oscillator is used as chip clock source, PB7..6 is used as TOSC2..1 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.

The various special features of Port B are elaborated in "Alternate Functions of Port B" on page 71 and "System Clock and Clock Options" on page 25.

# 2.3.4 Port C (PC5..0)

Port C is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The PC5..0 output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

# 2.3.5 PC6/RESET

If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electrical characteristics of PC6 differ from those of the other pins of Port C.

If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. The minimum pulse length is given in Table 8-1 on page 44. Shorter pulses are not guaranteed to generate a Reset.

The various special features of Port C are elaborated in "Alternate Functions of Port C" on page 75.

#### 2.3.6 Port D (PD7..0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up

# 4.7 Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock  $clk_{CPU}$ , directly generated from the selected clock source for the chip. No internal clock division is used.

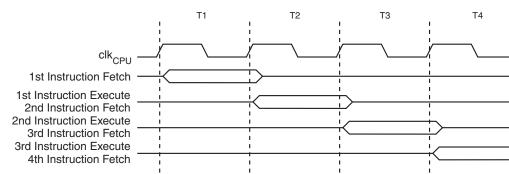

Figure 4-4 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

Figure 4-4. The Parallel Instruction Fetches and Instruction Executions

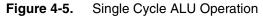

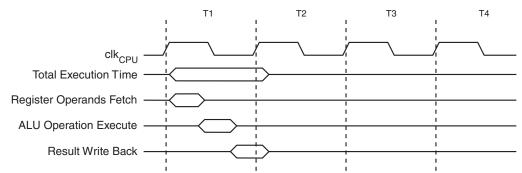

Figure 4-5 shows the internal timing concept for the Register File. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

# 4.8 Reset and Interrupt Handling

The AVR provides several different interrupt sources. These interrupts and the separate Reset Vector each have a separate program vector in the program memory space. All interrupts are assigned individual enable bits which must be written logic one together with the Global Interrupt Enable bit in the Status Register in order to enable the interrupt. Depending on the Program Counter value, interrupts may be automatically disabled when Boot Lock bits BLB02 or BLB12 are programmed. This feature improves software security. See the section "Memory Programming" on page 280 for details.

The lowest addresses in the program memory space are by default defined as the Reset and Interrupt Vectors. The complete list of vectors is shown in "Interrupts" on page 54. The list also determines the priority levels of the different interrupts. The lower the address the higher is the

# 12 ATmega48/88/168

### 6.1.4 Asynchronous Timer Clock – clk<sub>ASY</sub>

The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly from an external clock or an external 32 kHz clock crystal. The dedicated clock domain allows using this Timer/Counter as a real-time counter even when the device is in sleep mode.

# 6.1.5 ADC Clock – clk<sub>ADC</sub>

The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry. This gives more accurate ADC conversion results.

#### 6.2 Clock Sources

The device has the following clock source options, selectable by Flash Fuse bits as shown below. The clock from the selected source is input to the AVR clock generator, and routed to the appropriate modules.

| Device Clocking Option            | CKSEL30     |

|-----------------------------------|-------------|

| Low Power Crystal Oscillator      | 1111 - 1000 |

| Full Swing Crystal Oscillator     | 0111 - 0110 |

| Low Frequency Crystal Oscillator  | 0101 - 0100 |

| Internal 128 kHz RC Oscillator    | 0011        |

| Calibrated Internal RC Oscillator | 0010        |

| External Clock                    | 0000        |

| Reserved                          | 0001        |

Table 6-1.

Device Clocking Options Select<sup>(1)</sup>

Note: 1. For all fuses "1" means unprogrammed while "0" means programmed.

#### 6.2.1 Default Clock Source

The device is shipped with internal RC oscillator at 8.0MHz and with the fuse CKDIV8 programmed, resulting in 1.0MHz system clock. The startup time is set to maximum and time-out period enabled. (CKSEL = "0010", SUT = "10", CKDIV8 = "0"). The default setting ensures that all users can make their desired clock source setting using any available programming interface.

#### 6.2.2 Clock Startup Sequence

Any clock source needs a sufficient  $V_{CC}$  to start oscillating and a minimum number of oscillating cycles before it can be considered stable.

To ensure sufficient  $V_{CC}$ , the device issues an internal reset with a time-out delay ( $t_{TOUT}$ ) after the device reset is released by all other reset sources. "System Control and Reset" on page 43 describes the start conditions for the internal reset. The delay ( $t_{TOUT}$ ) is timed from the Watchdog Oscillator and the number of cycles in the delay is set by the SUTx and CKSELx fuse bits. The selectable delays are shown in Table 6-2. The frequency of the Watchdog Oscillator is voltage

# 6.5 Low Frequency Crystal Oscillator

The device can utilize a 32.768 kHz watch crystal as clock source by a dedicated Low Frequency Crystal Oscillator. The crystal should be connected as shown in Figure 6-2. When this Oscillator is selected, start-up times are determined by the SUT Fuses and CKSEL0 as shown in Table 6-7.

| Power Conditions    | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | CKSEL0 | SUT10 |

|---------------------|----------------------------------------------------|------------------------------------------------------------|--------|-------|

| BOD enabled         | 1K CK                                              | 14CK <sup>(1)</sup>                                        | 0      | 00    |

| Fast rising power   | 1K CK                                              | 14CK + 4.1 ms <sup>(1)</sup>                               | 0      | 01    |

| Slowly rising power | 1K CK                                              | 14CK + 65 ms <sup>(1)</sup>                                | 0      | 10    |

|                     | 0                                                  | 11                                                         |        |       |

| BOD enabled         | 32K CK                                             | 14CK                                                       | 1      | 00    |

| Fast rising power   | 32K CK                                             | 14CK + 4.1 ms                                              | 1      | 01    |

| Slowly rising power | 32K CK                                             | 14CK + 65 ms                                               | 1      | 10    |

|                     | Reserved                                           |                                                            | 1      | 11    |

Table 6-7.

Start-up Times for the Low Frequency Crystal Oscillator Clock Selection

Note: 1. These options should only be used if frequency stability at start-up is not important for the application.

# 6.6 Calibrated Internal RC Oscillator

The calibrated internal RC Oscillator by default provides a 8.0 MHz clock. The frequency is nominal value at 3V and 25°C. The device is shipped with the CKDIV8 Fuse programmed. See "System Clock Prescaler" on page 34 for more details. This clock may be selected as the system clock by programming the CKSEL Fuses as shown in Table 6-8. If selected, it will operate with no external components. During reset, hardware loads the calibration byte into the OSCCAL Register and thereby automatically calibrates the RC Oscillator. At 3V and 25°C, this calibration gives a frequency of 8 MHz  $\pm 10\%$ . The oscillator can be calibrated to any frequency in the range 7.3 - 8.1 MHz within  $\pm 2\%$  accuracy, by changing the OSCCAL register. When this Oscillator is used as the chip clock, the Watchdog Oscillator will still be used for the Watchdog Timer and for the Reset Time-out. For more information on the pre-programmed calibration value, see the section "Calibration Byte" on page 284.

| Table 6-8. | Internal Calibrated RC Oscillator Operating Modes <sup>(1)(3)</sup> |

|------------|---------------------------------------------------------------------|

|------------|---------------------------------------------------------------------|

| Frequency Range <sup>(2)</sup> (MHz) | CKSEL30 |

|--------------------------------------|---------|

| 7.3 - 8.1                            | 0010    |

Notes: 1. The device is shipped with this option selected.

2. The frequency ranges are preliminary values. Actual values are TBD.

If 8 MHz frequency exceeds the specification of the device (depends on V<sub>CC</sub>), the CKDIV8 Fuse can be programmed in order to divide the internal frequency by 8.

| - |         |       |                    | 5                               |

|---|---------|-------|--------------------|---------------------------------|

|   | BOOTRST | IVSEL | Reset Address      | Interrupt Vectors Start Address |

| ſ | 1       | 0     | 0x000              | 0x001                           |

|   | 1       | 1     | 0x000              | Boot Reset Address + 0x001      |

|   | 0       | 0     | Boot Reset Address | 0x001                           |

|   | 0       | 1     | Boot Reset Address | Boot Reset Address + 0x001      |

Table 9-3.

Reset and Interrupt Vectors Placement in ATmega88<sup>(1)</sup>

Note: 1. The Boot Reset Address is shown in Table 24-6 on page 276. For the BOOTRST Fuse "1" means unprogrammed while "0" means programmed.

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Label | s Code                                                    |                | С   | omments                            |

|---------------|-----------------------------------------------------------|----------------|-----|------------------------------------|

| 0x000         | rjmp                                                      | RESET          | ;   | Reset Handler                      |

| 0x001         | rjmp                                                      | EXT_INT0       | ;   | IRQ0 Handler                       |

| 0x002         | rjmp                                                      | EXT_INT1       | ;   | IRQ1 Handler                       |

| 0x003         | rjmp                                                      | PCINT0         | ;   | PCINTO Handler                     |

| 0x004         | rjmp                                                      | PCINT1         | ;   | PCINT1 Handler                     |

| 0x005         | rjmp                                                      | PCINT2         | ;   | PCINT2 Handler                     |

| 0x006         | rjmp                                                      | WDT            | ;   | Watchdog Timer Handler             |

| 0x007         | rjmp                                                      | TIM2_COMPA     | ;   | Timer2 Compare A Handler           |

| 0X008         | rjmp                                                      | TIM2_COMPB     | ;   | Timer2 Compare B Handler           |

| 0x009         | rjmp                                                      | TIM2_OVF       | ;   | Timer2 Overflow Handler            |

| 0x00A         | rjmp                                                      | TIM1_CAPT      | ;   | Timer1 Capture Handler             |

| 0x00B         | rjmp                                                      | TIM1_COMPA     | ;   | Timer1 Compare A Handler           |

| 0x00C         | rjmp                                                      | TIM1_COMPB     | ;   | Timer1 Compare B Handler           |

| 0x00D         | rjmp                                                      | TIM1_OVF       | ;   | Timer1 Overflow Handler            |

| 0x00E         | rjmp                                                      | TIM0_COMPA     | ;   | Timer0 Compare A Handler           |

| 0x00F         | rjmp                                                      | TIM0_COMPB     | ;   | Timer0 Compare B Handler           |

| 0x010         | rjmp                                                      | TIM0_OVF       | ;   | Timer0 Overflow Handler            |

| 0x011         | rjmp                                                      | SPI_STC        | ;   | SPI Transfer Complete Handler      |

| 0x012         | rjmp                                                      | USART_RXC      | ;   | USART, RX Complete Handler         |

| 0x013         | rjmp                                                      | USART_UDRE     | ;   | USART, UDR Empty Handler           |

| 0x014         | rjmp                                                      | USART_TXC      | ;   | USART, TX Complete Handler         |

| 0x015         | rjmp                                                      | ADC            | ;   | ADC Conversion Complete Handler    |

| 0x016         | rjmp                                                      | EE_RDY         | ;   | EEPROM Ready Handler               |

| 0x017         | rjmp                                                      | ANA_COMP       | ;   | Analog Comparator Handler          |

| 0x018         | rjmp                                                      | TWI            | ;   | 2-wire Serial Interface Handler    |

| 0x019         | rjmp                                                      | SPM_RDY        | ;   | Store Program Memory Ready Handler |

| ;             |                                                           |                |     |                                    |

| 0x01ARESET:   | ldi                                                       | r16, high(RAME | IND | ); Main program start              |

| 0x01B         | out                                                       | SPH,r16        | ;   | Set Stack Pointer to top of RAM    |

| 0x01C         | ldi                                                       | r16, low(RAMEN | ID) |                                    |

| 0x01D         | out                                                       | SPL,r16        |     |                                    |

| 0x01E         | sei                                                       |                | ;   | Enable interrupts                  |

| 0x01F         | <inst< td=""><td>r&gt; xxx</td><td></td><td></td></inst<> | r> xxx         |     |                                    |

When the BOOTRST Fuse is unprogrammed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address   | Labels | Code                                                       |                 | Co | omments                            |

|-----------|--------|------------------------------------------------------------|-----------------|----|------------------------------------|

| 0x000     | RESET: | ldi                                                        | r16,high(RAMENI | ); | ; Main program start               |

| 0x001     |        | out                                                        | SPH,r16         | ;  | Set Stack Pointer to top of RAM    |

| 0x002     |        | ldi                                                        | r16,low(RAMEND) |    |                                    |

| 0x003     |        | out                                                        | SPL,r16         |    |                                    |

| 0x004     |        | sei                                                        |                 | ;  | Enable interrupts                  |

| 0x005     |        | <instr< td=""><td>&gt; xxx</td><td></td><td></td></instr<> | > xxx           |    |                                    |

| ;         |        |                                                            |                 |    |                                    |

| .org 0xC0 | )1     |                                                            |                 |    |                                    |

| 0xC01     |        | rjmp                                                       | EXT_INT0        | ;  | IRQ0 Handler                       |

| 0xC02     |        | rjmp                                                       | EXT_INT1        | ;  | IRQ1 Handler                       |

| •••       |        |                                                            |                 | ;  |                                    |

| 0xC19     |        | rjmp                                                       | SPM_RDY         | ;  | Store Program Memory Ready Handler |

|           |        |                                                            |                 |    |                                    |

When the BOOTRST Fuse is programmed and the Boot section size set to 2K bytes, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Label | s Code                                           | Com           | Comments                             |  |  |  |  |

|---------------|--------------------------------------------------|---------------|--------------------------------------|--|--|--|--|

| .org 0x001    |                                                  |               |                                      |  |  |  |  |

| 0x001         | rjmp                                             | EXT_INT0      | ; IRQ0 Handler                       |  |  |  |  |

| 0x002         | rjmp                                             | EXT_INT1      | ; IRQ1 Handler                       |  |  |  |  |

|               |                                                  |               | ;                                    |  |  |  |  |

| 0x019         | rjmp                                             | SPM_RDY       | ; Store Program Memory Ready Handler |  |  |  |  |

| ;             |                                                  |               |                                      |  |  |  |  |

| .org 0xC00    |                                                  |               |                                      |  |  |  |  |

| 0xC00 RESET   | : ldi                                            | r16,high(RAME | ND); Main program start              |  |  |  |  |

| 0xC01         | out                                              | SPH,r16       | ; Set Stack Pointer to top of RAM    |  |  |  |  |

| 0xC02         | ldi                                              | r16,low(RAMEN | ם)                                   |  |  |  |  |

| 0xC03         | out                                              | SPL,r16       |                                      |  |  |  |  |

| 0xC04         | sei                                              |               | ; Enable interrupts                  |  |  |  |  |

| 0xC05         | <inst< td=""><td>r&gt; xxx</td><td></td></inst<> | r> xxx        |                                      |  |  |  |  |

When the BOOTRST Fuse is programmed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Labels Code |                | Comments                             |  |  |  |  |

|---------------------|----------------|--------------------------------------|--|--|--|--|

| ;                   |                |                                      |  |  |  |  |

| .org 0xC00          |                |                                      |  |  |  |  |

| 0xC00 rjmp          | RESET          | ; Reset handler                      |  |  |  |  |

| 0xC01 rjmp          | EXT_INT0       | ; IRQ0 Handler                       |  |  |  |  |

| 0xC02 rjmp          | EXT_INT1       | ; IRQ1 Handler                       |  |  |  |  |

|                     |                | ;                                    |  |  |  |  |

| 0xC19 rjmp          | SPM_RDY        | ; Store Program Memory Ready Handler |  |  |  |  |

| ;                   |                |                                      |  |  |  |  |

| 0xC1A RESET: ldi    | r16,high(RAMEN | ND); Main program start              |  |  |  |  |

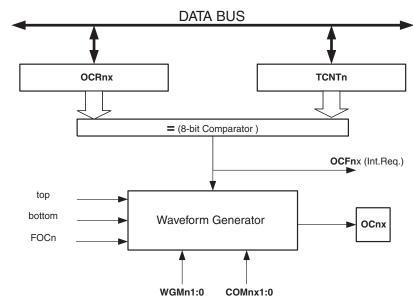

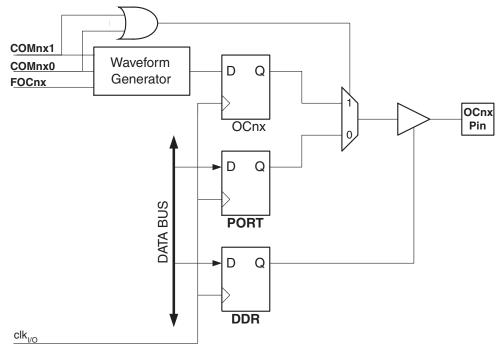

Figure 12-3. Output Compare Unit, Block Diagram

The OCR0x Registers are double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR0x Compare Registers to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCR0x Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR0x Buffer Register, and if double buffering is disabled the CPU will access the OCR0x directly.

# 12.4.1 Force Output Compare

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0x) bit. Forcing compare match will not set the OCF0x Flag or reload/clear the timer, but the OC0x pin will be updated as if a real compare match had occurred (the COM0x1:0 bits settings define whether the OC0x pin is set, cleared or toggled).

# 12.4.2 Compare Match Blocking by TCNT0 Write

All CPU write operations to the TCNT0 Register will block any compare match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0x to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.

# 12.4.3 Using the Output Compare Unit

Since writing TCNT0 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the Output Compare Unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0x value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is downcounting.

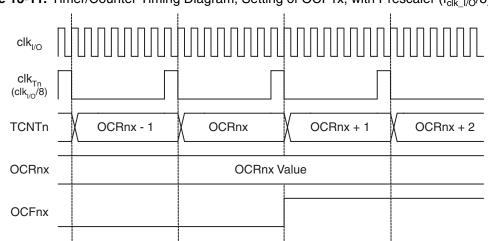

Figure 13-11. Timer/Counter Timing Diagram, Setting of OCF1x, with Prescaler (f<sub>clk I/O</sub>/8)

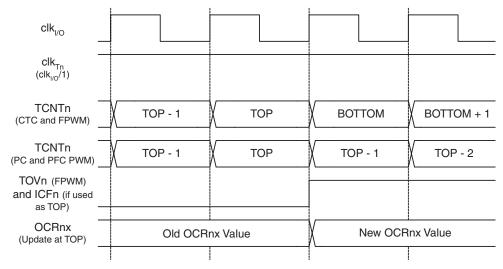

Figure 13-12 shows the count sequence close to TOP in various modes. When using phase and frequency correct PWM mode the OCR1x Register is updated at BOTTOM. The timing diagrams will be the same, but TOP should be replaced by BOTTOM, TOP-1 by BOTTOM+1 and so on. The same renaming applies for modes that set the TOV1 Flag at BOTTOM.

Figure 13-12. Timer/Counter Timing Diagram, no Prescaling

Figure 13-13 shows the same timing data, but with the prescaler enabled.

The setup of the OC2x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC2x value is to use the Force Output Compare (FOC2x) strobe bit in Normal mode. The OC2x Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COM2x1:0 bits are not double buffered together with the compare value. Changing the COM2x1:0 bits will take effect immediately.

# 15.5 Compare Match Output Unit

The Compare Output mode (COM2x1:0) bits have two functions. The Waveform Generator uses the COM2x1:0 bits for defining the Output Compare (OC2x) state at the next compare match. Also, the COM2x1:0 bits control the OC2x pin output source. Figure 15-4 shows a simplified schematic of the logic affected by the COM2x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM2x1:0 bits are shown. When referring to the OC2x state, the reference is for the internal OC2x Register, not the OC2x pin.

The general I/O port function is overridden by the Output Compare (OC2x) from the Waveform Generator if either of the COM2x1:0 bits are set. However, the OC2x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC2x pin (DDR\_OC2x) must be set as output before the OC2x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC2x state before the output is enabled. Note that some COM2x1:0 bit settings are reserved for certain modes of operation. See Section "15.8" on page 149.

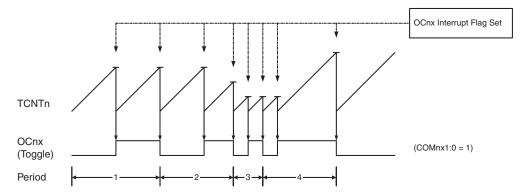

Figure 15-5. CTC Mode, Timing Diagram

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF2A Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR2A is lower than the current value of TCNT2, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur.

For generating a waveform output in CTC mode, the OC2A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM2A1:0 = 1). The OC2A value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC2A} = f_{clk\_l/O}/2$  when OCR2A is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCnx} = \frac{f_{clk\_I/O}}{2 \cdot N \cdot (1 + OCRnx)}$$

The *N* variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

As for the Normal mode of operation, the TOV2 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

#### 15.6.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM22:0 = 3 or 7) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOT-TOM. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7. In noninverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x, and set at BOTTOM. In inverting Compare Output mode, the output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that uses dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

# ATmega48/88/168

output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7 (See Table 15-4 on page 150). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by clearing (or setting) the OC2x Register at the compare match between OCR2x and TCNT2 when the counter increments, and setting (or clearing) the OC2x Register at compare match between OCR2x and TCNT2 when the counter increments, and setting (or clearing) the OC2x Register at compare match between OCR2x and TCNT2 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{OCnxPCPWM} = \frac{f_{\text{clk}\_I/O}}{N \cdot 510}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR2A is set equal to BOTTOM, the output will be continuously low and if set equal to MAX the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values.

At the very start of period 2 in Figure 15-7 OCnx has a transition from high to low even though there is no Compare Match. The point of this transition is to guarantee symmetry around BOT-TOM. There are two cases that give a transition without Compare Match.

- OCR2A changes its value from MAX, like in Figure 15-7. When the OCR2A value is MAX the OCn pin value is the same as the result of a down-counting compare match. To ensure symmetry around BOTTOM the OCn value at MAX must correspond to the result of an up-counting Compare Match.

- The timer starts counting from a value higher than the one in OCR2A, and for that reason misses the Compare Match and hence the OCn change that would have happened on the way up.

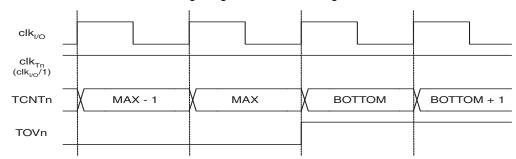

# 15.7 Timer/Counter Timing Diagrams

The following figures show the Timer/Counter in synchronous mode, and the timer clock ( $clk_{T2}$ ) is therefore shown as a clock enable signal. In asynchronous mode,  $clk_{I/O}$  should be replaced by the Timer/Counter Oscillator clock. The figures include information on when Interrupt Flags are set. Figure 15-8 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other than phase correct PWM mode.

Figure 15-8. Timer/Counter Timing Diagram, no Prescaling

Figure 15-9 shows the same timing data, but with the prescaler enabled.

### 15.8.6 Timer/Counter2 Interrupt Mask Register – TIMSK2

| Bit           | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0     | _      |

|---------------|---|---|---|---|---|--------|--------|-------|--------|

|               | - | - | - | - | - | OCIE2B | OCIE2A | TOIE2 | TIMSK2 |

| Read/Write    | R | R | R | R | R | R/W    | R/W    | R/W   | -      |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0      | 0      | 0     |        |

### • Bit 2 – OCIE2B: Timer/Counter2 Output Compare Match B Interrupt Enable

When the OCIE2B bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match B interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, i.e., when the OCF2B bit is set in the Timer/Counter 2 Interrupt Flag Register – TIFR2.

### • Bit 1 – OCIE2A: Timer/Counter2 Output Compare Match A Interrupt Enable

When the OCIE2A bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match A interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, i.e., when the OCF2A bit is set in the Timer/Counter 2 Interrupt Flag Register – TIFR2.

#### • Bit 0 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, i.e., when the TOV2 bit is set in the Timer/Counter2 Interrupt Flag Register – TIFR2.

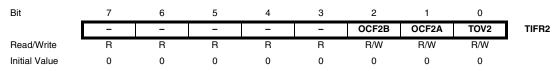

### 15.8.7 Timer/Counter2 Interrupt Flag Register – TIFR2

# • Bit 2 – OCF2B: Output Compare Flag 2 B

The OCF2B bit is set (one) when a compare match occurs between the Timer/Counter2 and the data in OCR2B – Output Compare Register2. OCF2B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF2B is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE2B (Timer/Counter2 Compare match Interrupt Enable), and OCF2B are set (one), the Timer/Counter2 Compare match Interrupt is executed.

# • Bit 1 – OCF2A: Output Compare Flag 2 A

The OCF2A bit is set (one) when a compare match occurs between the Timer/Counter2 and the data in OCR2A – Output Compare Register2. OCF2A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF2A is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE2A (Timer/Counter2 Compare match Interrupt Enable), and OCF2A are set (one), the Timer/Counter2 Compare match Interrupt is executed.

# Bit 0 – TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE2A (Timer/Counter2 Overflow Interrupt Enable), and TOV2 are set (one), the Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 changes counting direction at 0x00.

### 16.1.4 SPI Status Register – SPSR

| Bit           | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0     | _    |

|---------------|------|------|---|---|---|---|---|-------|------|

|               | SPIF | WCOL | - | - | - | - | - | SPI2X | SPSR |

| Read/Write    | R    | R    | R | R | R | R | R | R/W   |      |

| Initial Value | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0     |      |

### • Bit 7 – SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF Flag is set. An interrupt is generated if SPIE in SPCR is set and global interrupts are enabled. If  $\overline{SS}$  is an input and is driven low when the SPI is in Master mode, this will also set the SPIF Flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI Status Register with SPIF set, then accessing the SPI Data Register (SPDR).

#### Bit 6 – WCOL: Write COLlision Flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared by first reading the SPI Status Register with WCOL set, and then accessing the SPI Data Register.

#### • Bit 5..1 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### Bit 0 – SPI2X: Double SPI Speed Bit

When this bit is written logic one the SPI speed (SCK Frequency) will be doubled when the SPI is in Master mode (see Table 16-4). This means that the minimum SCK period will be two CPU clock periods. When the SPI is configured as Slave, the SPI is only guaranteed to work at  $f_{osc}/4$  or lower.

The SPI interface on the ATmega48/88/168 is also used for program memory and EEPROM downloading or uploading. See page 295 for serial programming and verification.

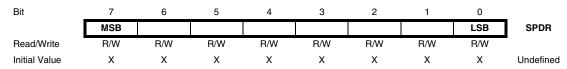

#### 16.1.5 SPI Data Register – SPDR

The SPI Data Register is a read/write register used for data transfer between the Register File and the SPI Shift Register. Writing to the register initiates data transmission. Reading the register causes the Shift Register Receive buffer to be read.

### 16.2 Data Modes

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 16-3 and Figure 16-4. Data bits are shifted out and latched in on opposite edges of the SCK signal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing Table 16-2 and Table 16-3, as done below.

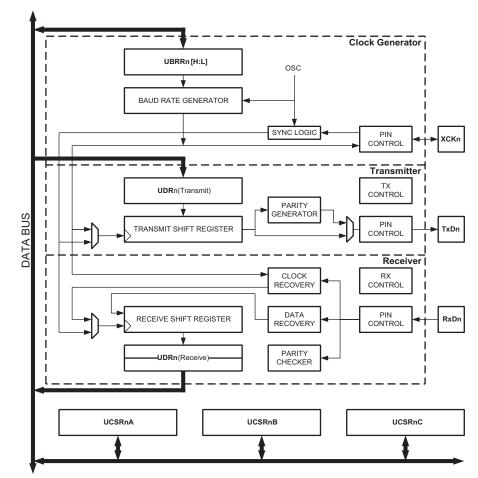

Figure 17-1. USART Block Diagram<sup>(1)</sup>

Note: 1. Refer to Figure 1-1 on page 2 and Table 10-9 on page 78 for USART0 pin placement.

# 17.2 Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: Normal asynchronous, Double Speed asynchronous, Master synchronous and Slave synchronous mode. The UMSELn bit in USART Control and Status Register C (UCSRnC) selects between asynchronous and synchronous operation. Double Speed (asynchronous mode only) is controlled by the U2Xn found in the UCSRnA Register. When using synchronous mode (UMSELn = 1), the Data Direction Register for the XCKn pin (DDR\_XCKn) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCKn pin is only active when using synchronous mode.

Figure 17-2 shows a block diagram of the clock generation logic.

# 17.2.3 External Clock

External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 17-2 for details.

External clock input from the XCKn pin is sampled by a synchronization register to minimize the chance of meta-stability. The output from the synchronization register must then pass through an edge detector before it can be used by the Transmitter and Receiver. This process introduces a two CPU clock period delay and therefore the maximum external XCKn clock frequency is limited by the following equation:

$$f_{XCK} < \frac{f_{OSC}}{4}$$

Note that f<sub>osc</sub> depends on the stability of the system clock source. It is therefore recommended to add some margin to avoid possible loss of data due to frequency variations.

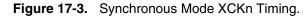

### 17.2.4 Synchronous Clock Operation

When synchronous mode is used (UMSELn = 1), the XCKn pin will be used as either clock input (Slave) or clock output (Master). The dependency between the clock edges and data sampling or data change is the same. The basic principle is that data input (on RxDn) is sampled at the opposite XCKn clock edge of the edge the data output (TxDn) is changed.

The UCPOLn bit UCRSC selects which XCKn clock edge is used for data sampling and which is used for data change. As Figure 17-3 shows, when UCPOLn is zero the data will be changed at rising XCKn edge and sampled at falling XCKn edge. If UCPOLn is set, the data will be changed at falling XCKn edge and sampled at rising XCKn edge.

### 17.3 Frame Formats

A serial frame is defined to be one character of data bits with synchronization bits (start and stop bits), and optionally a parity bit for error checking. The USART accepts all 30 combinations of the following as valid frame formats:

- 1 start bit

- 5, 6, 7, 8, or 9 data bits

- no, even or odd parity bit

- 1 or 2 stop bits

# 172 **ATmega48/88/168**

UDREn is set after a reset to indicate that the Transmitter is ready.

# • Bit 4 – FEn: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when received. I.e., when the first stop bit of the next character in the receive buffer is zero. This bit is valid until the receive buffer (UDRn) is read. The FEn bit is zero when the stop bit of received data is one. Always set this bit to zero when writing to UCSRnA.

# • Bit 3 – DORn: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the Receive Shift Register, and a new start bit is detected. This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

# • Bit 2 – UPEn: USART Parity Error

This bit is set if the next character in the receive buffer had a Parity Error when received and the Parity Checking was enabled at that point (UPMn1 = 1). This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

### • Bit 1 – U2Xn: Double the USART Transmission Speed

This bit only has effect for the asynchronous operation. Write this bit to zero when using synchronous operation.

Writing this bit to one will reduce the divisor of the baud rate divider from 16 to 8 effectively doubling the transfer rate for asynchronous communication.

# • Bit 0 – MPCMn: Multi-processor Communication Mode

This bit enables the Multi-processor Communication mode. When the MPCMn bit is written to one, all the incoming frames received by the USART Receiver that do not contain address information will be ignored. The Transmitter is unaffected by the MPCMn setting. For more detailed information see "Multi-processor Communication Mode" on page 185.

# 17.9.3 USART Control and Status Register n B – UCSRnB

| Bit           | 7      | 6      | 5      | 4     | 3     | 2      | 1     | 0     | _      |

|---------------|--------|--------|--------|-------|-------|--------|-------|-------|--------|

|               | RXCIEn | TXCIEn | UDRIEn | RXENn | TXENn | UCSZn2 | RXB8n | TXB8n | UCSRnB |

| Read/Write    | R/W    | R/W    | R/W    | R/W   | R/W   | R/W    | R     | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0     | 0     | 0      | 0     | 0     |        |

# Bit 7 – RXCIEn: RX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the RXCn Flag. A USART Receive Complete interrupt will be generated only if the RXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXCn bit in UCSRnA is set.

# • Bit 6 – TXCIEn: TX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the TXCn Flag. A USART Transmit Complete interrupt will be generated only if the TXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXCn bit in UCSRnA is set.

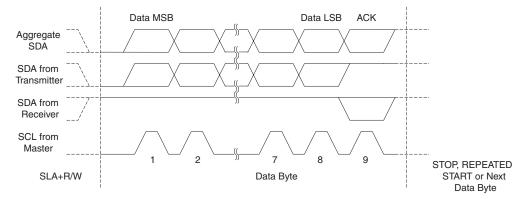

#### 19.3.4 Data Packet Format

All data packets transmitted on the TWI bus are nine bits long, consisting of one data byte and an acknowledge bit. During a data transfer, the Master generates the clock and the START and STOP conditions, while the Receiver is responsible for acknowledging the reception. An Acknowledge (ACK) is signalled by the Receiver pulling the SDA line low during the ninth SCL cycle. If the Receiver leaves the SDA line high, a NACK is signalled. When the Receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the Transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first.

#### Figure 19-5. Data Packet Format

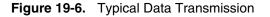

### 19.3.5 Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the Wired-ANDing of the SCL line can be used to implement handshaking between the Master and the Slave. The Slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the Master is too fast for the Slave, or the Slave needs extra time for processing between the data transmissions. The Slave extending the SCL low period will not affect the SCL high period, which is determined by the Master. As a consequence, the Slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

Figure 19-6 shows a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

# ATmega48/88/168

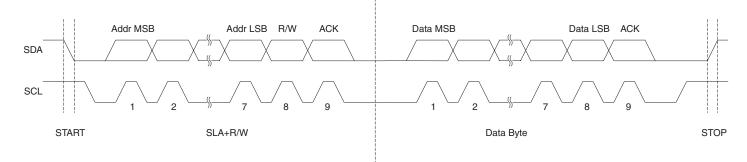

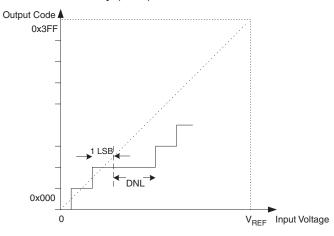

Figure 21-12. Integral Non-linearity (INL)

• Differential Non-linearity (DNL): The maximum deviation of the actual code width (the interval between two adjacent transitions) from the ideal code width (1 LSB). Ideal value: 0 LSB.

Figure 21-13. Differential Non-linearity (DNL)

- Quantization Error: Due to the quantization of the input voltage into a finite number of codes, a range of input voltages (1 LSB wide) will code to the same value. Always ±0.5 LSB.

- Absolute accuracy: The maximum deviation of an actual (unadjusted) transition compared to an ideal transition for any code. This is the compound effect of offset, gain error, differential error, non-linearity, and quantization error. Ideal value: ±0.5 LSB.

shown below. Refer to Table 25-6 on page 282 for detailed description and mapping of the Fuse High byte.

Bit 7 6 5 3 2 0 4 1 Rd FHB7 FHB6 FHB5 FHB4 FHB3 FHB2 FHB1 FHB0

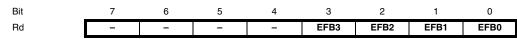

When reading the Extended Fuse byte, load 0x0002 in the Z-pointer. When an LPM instruction is executed within three cycles after the BLBSET and SELFPRGEN bits are set in the SPMCSR, the value of the Extended Fuse byte (EFB) will be loaded in the destination register as shown below. Refer to Table 25-4 on page 281 for detailed description and mapping of the Extended Fuse byte.

Fuse and Lock bits that are programmed, will be read as zero. Fuse and Lock bits that are unprogrammed, will be read as one.

#### 24.7.10 Preventing Flash Corruption

During periods of low  $V_{CC}$ , the Flash program can be corrupted because the supply voltage is too low for the CPU and the Flash to operate properly. These issues are the same as for board level systems using the Flash, and the same design solutions should be applied.

A Flash program corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the Flash requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage for executing instructions is too low.

Flash corruption can easily be avoided by following these design recommendations (one is sufficient):

- 1. If there is no need for a Boot Loader update in the system, program the Boot Loader Lock bits to prevent any Boot Loader software updates.

- 2. Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the SPMCSR Register and thus the Flash from unintentional writes.

#### 24.7.11 Programming Time for Flash when Using SPM

The calibrated RC Oscillator is used to time Flash accesses. Table 24-5 shows the typical programming time for Flash accesses from the CPU.

#### **Table 24-5.**SPM Programming Time

| Symbol                                                           | Min Programming Time | Max Programming Time |

|------------------------------------------------------------------|----------------------|----------------------|

| Flash write (Page Erase, Page Write, and write Lock bits by SPM) | 3.7 ms               | 4.5 ms               |

ATmega48/88/168

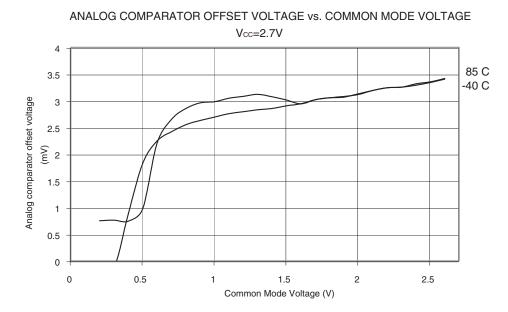

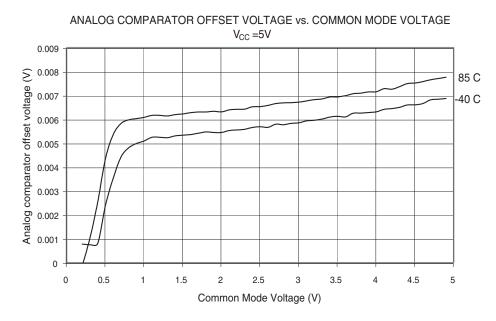

Figure 27-38. Analog Comparator Offset Voltage vs. Common Mode Voltage (V<sub>CC</sub>=2.7V)