# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega88-20au |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In ATmega48, there is no Read-While-Write support and no separate Boot Loader Section. The SPM instruction can execute from the entire Flash.

# 2.3 Pin Descriptions

| 2.3. | 1 | VCC |

|------|---|-----|

|      |   |     |

- Digital supply voltage.

- 2.3.2 GND

Ground.

#### 2.3.3 Port B (PB7..0) XTAL1/XTAL2/TOSC1/TOSC2

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.

If the Internal Calibrated RC Oscillator is used as chip clock source, PB7..6 is used as TOSC2..1 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.

The various special features of Port B are elaborated in "Alternate Functions of Port B" on page 71 and "System Clock and Clock Options" on page 25.

#### 2.3.4 Port C (PC5..0)

Port C is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The PC5..0 output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### 2.3.5 PC6/RESET

If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electrical characteristics of PC6 differ from those of the other pins of Port C.

If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. The minimum pulse length is given in Table 8-1 on page 44. Shorter pulses are not guaranteed to generate a Reset.

The various special features of Port C are elaborated in "Alternate Functions of Port C" on page 75.

#### 2.3.6 Port D (PD7..0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up

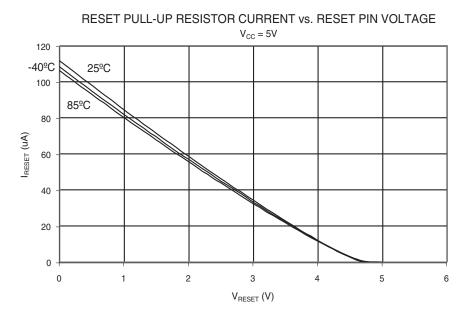

The fast-access Register File contains  $32 \times 8$ -bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the Reset routine (before subroutines or interrupts are executed). The Stack Pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F. In addition, the ATmega48/88/168 has Extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# 4.3 ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

Assembly Code Example

| <b>in</b> r16, S | SREG    | ; store SREG value               |

|------------------|---------|----------------------------------|

| cli ;            | disable | interrupts during timed sequence |

| <b>sbi</b> EECR, | EEMPE   | ; start EEPROM write             |

| <b>sbi</b> EECR, | EEPE    |                                  |

| out SREG,        | r16     | ; restore SREG value (I-bit)     |

C Code Example

```

char cSREG;

cSREG = SREG; /* store SREG value */

/* disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMPE); /* start EEPROM write */

EECR |= (1<<EEPE);

SREG = cSREG; /* restore SREG value (I-bit) */

```

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in this example.

| Assembly  | Code Example                                                  |

|-----------|---------------------------------------------------------------|

| sei       | set Global Interrupt Enable                                   |

| sleep     | enter sleep, waiting for interrupt                            |

| ; note    | e: will enter sleep before any pending interrupt(s)           |

| C Code Ex | ample                                                         |

| enal      | <pre>ole_interrupt(); /* set Global Interrupt Enable */</pre> |

| slee      | ep(); /* enter sleep, waiting for interrupt */                |

| /* not    | te: will enter sleep before any pending interrupt(s) */       |

#### 4.8.1 Interrupt Response Time

The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. After four clock cycles the program vector address for the actual interrupt handling routine is executed. During this four clock cycle period, the Program Counter is pushed onto the Stack. The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the Program Counter (two bytes) is popped back from the Stack, the Stack Pointer is incremented by two, and the I-bit in SREG is set.

## 5.3 EEPROM Data Memory

The ATmega48/88/168 contains 256/512/512 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM Data Register, and the EEPROM Control Register.

"Memory Programming" on page 280 contains a detailed description on EEPROM Programming in SPI or Parallel Programming mode.

#### 5.3.1 EEPROM Read/Write Access

The EEPROM Access Registers are accessible in the I/O space.

The write access time for the EEPROM is given in Table 5-2. A self-timing function, however, lets the user software detect when the next byte can be written. If the user code contains instructions that write the EEPROM, some precautions must be taken. In heavily filtered power supplies,  $V_{CC}$  is likely to rise or fall slowly on power-up/down. This causes the device for some period of time to run at a voltage lower than specified as minimum for the clock frequency used. See "Preventing EEPROM Corruption" on page 23 for details on how to avoid problems in these situations.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

When the BOOTRST Fuse is unprogrammed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address   | Labels | Code                                                       |                 | Co | omments                            |

|-----------|--------|------------------------------------------------------------|-----------------|----|------------------------------------|

| 0x000     | RESET: | ldi                                                        | r16,high(RAMENI | ); | ; Main program start               |

| 0x001     |        | out                                                        | SPH,r16         | ;  | Set Stack Pointer to top of RAM    |

| 0x002     |        | ldi                                                        | r16,low(RAMEND) |    |                                    |

| 0x003     |        | out                                                        | SPL,r16         |    |                                    |

| 0x004     |        | sei                                                        |                 | ;  | Enable interrupts                  |

| 0x005     |        | <instr< td=""><td>&gt; xxx</td><td></td><td></td></instr<> | > xxx           |    |                                    |

| ;         |        |                                                            |                 |    |                                    |

| .org 0xC0 | )1     |                                                            |                 |    |                                    |

| 0xC01     |        | rjmp                                                       | EXT_INT0        | ;  | IRQ0 Handler                       |

| 0xC02     |        | rjmp                                                       | EXT_INT1        | ;  | IRQ1 Handler                       |

| •••       |        |                                                            |                 | ;  |                                    |

| 0xC19     |        | rjmp                                                       | SPM_RDY         | ;  | Store Program Memory Ready Handler |

|           |        |                                                            |                 |    |                                    |

When the BOOTRST Fuse is programmed and the Boot section size set to 2K bytes, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Label | s Code                                           | Com           | ments                                |

|---------------|--------------------------------------------------|---------------|--------------------------------------|

| .org 0x001    |                                                  |               |                                      |

| 0x001         | rjmp                                             | EXT_INT0      | ; IRQ0 Handler                       |

| 0x002         | rjmp                                             | EXT_INT1      | ; IRQ1 Handler                       |

|               |                                                  |               | ;                                    |

| 0x019         | rjmp                                             | SPM_RDY       | ; Store Program Memory Ready Handler |

| ;             |                                                  |               |                                      |

| .org 0xC00    |                                                  |               |                                      |

| 0xC00 RESET   | : ldi                                            | r16,high(RAME | ND); Main program start              |

| 0xC01         | out                                              | SPH,r16       | ; Set Stack Pointer to top of RAM    |

| 0xC02         | ldi                                              | r16,low(RAMEN | ם)                                   |

| 0xC03         | out                                              | SPL,r16       |                                      |

| 0xC04         | sei                                              |               | ; Enable interrupts                  |

| 0xC05         | <inst< td=""><td>r&gt; xxx</td><td></td></inst<> | r> xxx        |                                      |

When the BOOTRST Fuse is programmed, the Boot section size set to 2K bytes and the IVSEL bit in the MCUCR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Labels Code |                | Comments                             |

|---------------------|----------------|--------------------------------------|

| ;                   |                |                                      |

| .org 0xC00          |                |                                      |

| 0xC00 rjmp          | RESET          | ; Reset handler                      |

| 0xC01 rjmp          | EXT_INT0       | ; IRQ0 Handler                       |

| 0xC02 rjmp          | EXT_INT1       | ; IRQ1 Handler                       |

|                     |                | ;                                    |

| 0xC19 rjmp          | SPM_RDY        | ; Store Program Memory Ready Handler |

| ;                   |                |                                      |

| 0xC1A RESET: ldi    | r16,high(RAMEN | ND); Main program start              |

# ATmega48/88/168

#### 11.1.2 External Interrupt Mask Register – EIMSK

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    | _     |

|---------------|---|---|---|---|---|---|------|------|-------|

|               | - | - | - | - | - | - | INT1 | INT0 | EIMSK |

| Read/Write    | R | R | R | R | R | R | R/W  | R/W  | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |       |

#### • Bit 7..2 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 1 – INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the External Interrupt Control Register A (EICRA) define whether the external interrupt is activated on rising and/or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from the INT1 Interrupt Vector.

#### • Bit 0 – INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the External Interrupt Control Register A (EICRA) define whether the external interrupt is activated on rising and/or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from the INT0 Interrupt Vector.

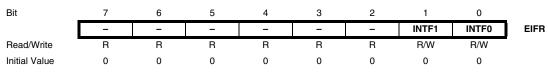

#### 11.1.3 External Interrupt Flag Register – EIFR

#### • Bit 7..2 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 1 – INTF1: External Interrupt Flag 1

When an edge or logic change on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in EIMSK are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT1 is configured as a level interrupt.

#### • Bit 0 – INTF0: External Interrupt Flag 0

When an edge or logic change on the INT0 pin triggers an interrupt request, INTF0 becomes set (one). If the I-bit in SREG and the INT0 bit in EIMSK are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT0 is configured as a level interrupt.

non-PWM modes refer to Table 13-1 on page 128. For fast PWM mode refer to Table 13-2 on page 128, and for phase correct and phase and frequency correct PWM refer to Table 13-3 on page 129.

A change of the COM1x1:0 bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC1x strobe bits.

#### 13.8 Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the combination of the *Waveform Generation mode* (WGM13:0) and *Compare Output mode* (COM1x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM1x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM1x1:0 bits control whether the output should be set, cleared or toggle at a compare match (See Section "13.7" on page 117.)

For detailed timing information refer to "Timer/Counter Timing Diagrams" on page 125.

#### 13.8.1 Normal Mode

The simplest mode of operation is the *Normal mode* (WGM13:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 16-bit value (MAX = 0xFFFF) and then restarts from the BOTTOM (0x0000). In normal operation the *Timer/Counter Overflow Flag* (TOV1) will be set in the same timer clock cycle as the TCNT1 becomes zero. The TOV1 Flag in this case behaves like a 17th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV1 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Input Capture unit is easy to use in Normal mode. However, observe that the maximum interval between the external events must not exceed the resolution of the counter. If the interval between events are too long, the timer overflow interrupt or the prescaler must be used to extend the resolution for the capture unit.

The Output Compare units can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

#### 13.8.2 Clear Timer on Compare Match (CTC) Mode

In *Clear Timer on Compare* or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 Register are used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 = 12). The OCR1A or ICR1 define the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 13-6. The counter value (TCNT1) increases until a compare match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared.

# ATmega48/88/168

to be written anytime. When the OCR1A I/O location is written the value written will be put into the OCR1A Buffer Register. The OCR1A Compare Register will then be updated with the value in the Buffer Register at the next timer clock cycle the TCNT1 matches TOP. The update is done at the same timer clock cycle as the TCNT1 is cleared and the TOV1 Flag is set.

Using the ICR1 Register for defining TOP works well when using fixed TOP values. By using ICR1, the OCR1A Register is free to be used for generating a PWM output on OC1A. However, if the base PWM frequency is actively changed (by changing the TOP value), using the OCR1A as TOP is clearly a better choice due to its double buffer feature.

In fast PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to three (see Table on page 128). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1, and clearing (or setting) the OC1x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clk}\_I/O}}{N \cdot (1 + TOP)}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x Register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR1x is set equal to BOTTOM (0x0000) the output will be a narrow spike for each TOP+1 timer clock cycle. Setting the OCR1x equal to TOP will result in a constant high or low output (depending on the polarity of the output set by the COM1x1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC1A to toggle its logical level on each compare match (COM1A1:0 = 1). This applies only if OCR1A is used to define the TOP value (WGM13:0 = 15). The waveform generated will have a maximum frequency of  $f_{OC1A} = f_{clk\_l/O}/2$  when OCR1A is set to zero (0x0000). This feature is similar to the OC1A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

#### 13.8.4 Phase Correct PWM Mode

The *phase correct Pulse Width Modulation* or phase correct PWM mode (WGM13:0 = 1, 2, 3, 10, or 11) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is, like the phase and frequency correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared on the compare match between TCNT1 and OCR1x while upcounting, and set on the compare match while downcounting. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The PWM resolution for the phase correct PWM mode can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to

Using the ICR1 Register for defining TOP works well when using fixed TOP values. By using ICR1, the OCR1A Register is free to be used for generating a PWM output on OC1A. However, if the base PWM frequency is actively changed by changing the TOP value, using the OCR1A as TOP is clearly a better choice due to its double buffer feature.

In phase and frequency correct PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to three (See Table on page 129). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1 when the counter increments, and clearing (or setting) the OC1x Register at compare match between OCR1x and TCNT1 when the counter decrements. The PWM frequency for the output when using phase and frequency correct PWM can be calculated by the following equation:

$$f_{OCnxPFCPWM} = \frac{f_{clk\_I/O}}{2 \cdot N \cdot TOP}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x Register represents special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCR1x is set equal to BOTTOM the output will be continuously low and if set equal to TOP the output will be set to high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values. If OCR1A is used to define the TOP value (WGM13:0 = 9) and COM1A1:0 = 1, the OC1A output will toggle with a 50% duty cycle.

# 13.9 Timer/Counter Timing Diagrams

**TCNT**n

**OCRnx**

**OCFnx**

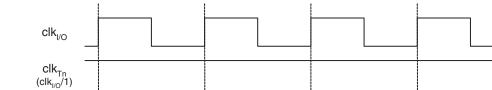

The Timer/Counter is a synchronous design and the timer clock ( $clk_{T1}$ ) is therefore shown as a clock enable signal in the following figures. The figures include information on when Interrupt Flags are set, and when the OCR1x Register is updated with the OCR1x buffer value (only for modes utilizing double buffering). Figure 13-10 shows a timing diagram for the setting of OCF1x.

**OCRnx**

**OCRnx Value**

OCRnx + 1

OCRnx + 2

Figure 13-10. Timer/Counter Timing Diagram, Setting of OCF1x, no Prescaling

OCRnx - 1

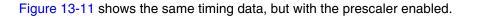

Figure 17-1. USART Block Diagram<sup>(1)</sup>

Note: 1. Refer to Figure 1-1 on page 2 and Table 10-9 on page 78 for USART0 pin placement.

# 17.2 Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: Normal asynchronous, Double Speed asynchronous, Master synchronous and Slave synchronous mode. The UMSELn bit in USART Control and Status Register C (UCSRnC) selects between asynchronous and synchronous operation. Double Speed (asynchronous mode only) is controlled by the U2Xn found in the UCSRnA Register. When using synchronous mode (UMSELn = 1), the Data Direction Register for the XCKn pin (DDR\_XCKn) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCKn pin is only active when using synchronous mode.

Figure 17-2 shows a block diagram of the clock generation logic.

# 17.9 USART Register Description

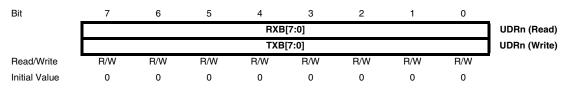

# 17.9.1 USART I/O Data Register n- UDRn

The USART Transmit Data Buffer Register and USART Receive Data Buffer Registers share the same I/O address referred to as USART Data Register or UDRn. The Transmit Data Buffer Register (TXB) will be the destination for data written to the UDRn Register location. Reading the UDRn Register location will return the contents of the Receive Data Buffer Register (RXB).

For 5-, 6-, or 7-bit characters the upper unused bits will be ignored by the Transmitter and set to zero by the Receiver.

The transmit buffer can only be written when the UDREn Flag in the UCSRnA Register is set. Data written to UDRn when the UDREn Flag is not set, will be ignored by the USART Transmitter. When data is written to the transmit buffer, and the Transmitter is enabled, the Transmitter will load the data into the Transmit Shift Register when the Shift Register is empty. Then the data will be serially transmitted on the TxDn pin.

The receive buffer consists of a two level FIFO. The FIFO will change its state whenever the receive buffer is accessed. Due to this behavior of the receive buffer, do not use Read-Modify-Write instructions (SBI and CBI) on this location. Be careful when using bit test instructions (SBIC and SBIS), since these also will change the state of the FIFO.

# 17.9.2 USART Control and Status Register n A – UCSRnA

| Bit           | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0     | -      |

|---------------|------|------|-------|-----|------|------|------|-------|--------|

|               | RXCn | TXCn | UDREn | FEn | DORn | UPEn | U2Xn | MPCMn | UCSRnA |

| Read/Write    | R    | R/W  | R     | R   | R    | R    | R/W  | R/W   | •      |

| Initial Value | 0    | 0    | 1     | 0   | 0    | 0    | 0    | 0     |        |

# • Bit 7 – RXCn: USART Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when the receive buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled, the receive buffer will be flushed and consequently the RXCn bit will become zero. The RXCn Flag can be used to generate a Receive Complete interrupt (see description of the RXCIEn bit).

#### • Bit 6 – TXCn: USART Transmit Complete

This flag bit is set when the entire frame in the Transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer (UDRn). The TXCn Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXCn Flag can generate a Transmit Complete interrupt (see description of the TXCIEn bit).

# Bit 5 – UDREn: USART Data Register Empty

The UDREn Flag indicates if the transmit buffer (UDRn) is ready to receive new data. If UDREn is one, the buffer is empty, and therefore ready to be written. The UDREn Flag can generate a Data Register Empty interrupt (see description of the UDRIEn bit).

|                     |           | $f_{osc} = 1.0$ | 000 MHz   |        |           | $f_{osc} = 1.8$ | 432 MHz   |          | f <sub>osc</sub> = 2.0000 MHz |          |           |          |  |

|---------------------|-----------|-----------------|-----------|--------|-----------|-----------------|-----------|----------|-------------------------------|----------|-----------|----------|--|

| Baud                | U2X       | n = 0           | U2Xn = 1  |        | U2X       | U2Xn = 0        |           | U2Xn = 1 |                               | U2Xn = 0 |           | U2Xn = 1 |  |

| Rate<br>(bps)       | UBRR<br>n | Error           | UBRR<br>n | Error  | UBRR<br>n | Error           | UBRR<br>n | Error    | UBRR<br>n                     | Error    | UBRR<br>n | Error    |  |

| 2400                | 25        | 0.2%            | 51        | 0.2%   | 47        | 0.0%            | 95        | 0.0%     | 51                            | 0.2%     | 103       | 0.2%     |  |

| 4800                | 12        | 0.2%            | 25        | 0.2%   | 23        | 0.0%            | 47        | 0.0%     | 25                            | 0.2%     | 51        | 0.2%     |  |

| 9600                | 6         | -7.0%           | 12        | 0.2%   | 11        | 0.0%            | 23        | 0.0%     | 12                            | 0.2%     | 25        | 0.2%     |  |

| 14.4k               | 3         | 8.5%            | 8         | -3.5%  | 7         | 0.0%            | 15        | 0.0%     | 8                             | -3.5%    | 16        | 2.1%     |  |

| 19.2k               | 2         | 8.5%            | 6         | -7.0%  | 5         | 0.0%            | 11        | 0.0%     | 6                             | -7.0%    | 12        | 0.2%     |  |

| 28.8k               | 1         | 8.5%            | 3         | 8.5%   | 3         | 0.0%            | 7         | 0.0%     | 3                             | 8.5%     | 8         | -3.5%    |  |

| 38.4k               | 1         | -18.6%          | 2         | 8.5%   | 2         | 0.0%            | 5         | 0.0%     | 2                             | 8.5%     | 6         | -7.0%    |  |

| 57.6k               | 0         | 8.5%            | 1         | 8.5%   | 1         | 0.0%            | 3         | 0.0%     | 1                             | 8.5%     | 3         | 8.5%     |  |

| 76.8k               | _         | _               | 1         | -18.6% | 1         | -25.0%          | 2         | 0.0%     | 1                             | -18.6%   | 2         | 8.5%     |  |

| 115.2k              | _         | _               | 0         | 8.5%   | 0         | 0.0%            | 1         | 0.0%     | 0                             | 8.5%     | 1         | 8.5%     |  |

| 230.4k              | _         | _               | _         | _      | -         | _               | 0         | 0.0%     | _                             | -        | _         | -        |  |

| 250k                | _         | _               | _         | -      | -         | _               | -         | _        | -                             | -        | 0         | 0.0%     |  |

| Max. <sup>(1)</sup> | 62.5      | kbps            | 125       | kbps   | 115.2     | 2 kbps          | 230.4     | l kbps   | 125                           | kbps     | 250       | kbps     |  |

Table 17-9.

Examples of UBRRn Settings for Commonly Used Oscillator Frequencies

Note: 1. UBRRn = 0, Error = 0.0%

|                     |           | f <sub>osc</sub> = 16. | 0000 MHz  |       |           | f <sub>osc</sub> = 18. | <sub>sc</sub> = 18.4320 MHz f <sub>osc</sub> = 20.0000 MHz |       |           |       |           |       |

|---------------------|-----------|------------------------|-----------|-------|-----------|------------------------|------------------------------------------------------------|-------|-----------|-------|-----------|-------|

| Baud                | U2Xn = 0  |                        | U2Xn = 1  |       | U2Xn = 0  |                        | U2Xn = 1                                                   |       | U2Xn = 0  |       | U2Xn = 1  |       |

| Rate<br>(bps)       | UBRR<br>n | Error                  | UBRR<br>n | Error | UBRR<br>n | Error                  | UBRR<br>n                                                  | Error | UBRR<br>n | Error | UBRR<br>n | Error |

| 2400                | 416       | -0.1%                  | 832       | 0.0%  | 479       | 0.0%                   | 959                                                        | 0.0%  | 520       | 0.0%  | 1041      | 0.0%  |

| 4800                | 207       | 0.2%                   | 416       | -0.1% | 239       | 0.0%                   | 479                                                        | 0.0%  | 259       | 0.2%  | 520       | 0.0%  |

| 9600                | 103       | 0.2%                   | 207       | 0.2%  | 119       | 0.0%                   | 239                                                        | 0.0%  | 129       | 0.2%  | 259       | 0.2%  |

| 14.4k               | 68        | 0.6%                   | 138       | -0.1% | 79        | 0.0%                   | 159                                                        | 0.0%  | 86        | -0.2% | 173       | -0.2% |

| 19.2k               | 51        | 0.2%                   | 103       | 0.2%  | 59        | 0.0%                   | 119                                                        | 0.0%  | 64        | 0.2%  | 129       | 0.2%  |

| 28.8k               | 34        | -0.8%                  | 68        | 0.6%  | 39        | 0.0%                   | 79                                                         | 0.0%  | 42        | 0.9%  | 86        | -0.2% |

| 38.4k               | 25        | 0.2%                   | 51        | 0.2%  | 29        | 0.0%                   | 59                                                         | 0.0%  | 32        | -1.4% | 64        | 0.2%  |

| 57.6k               | 16        | 2.1%                   | 34        | -0.8% | 19        | 0.0%                   | 39                                                         | 0.0%  | 21        | -1.4% | 42        | 0.9%  |

| 76.8k               | 12        | 0.2%                   | 25        | 0.2%  | 14        | 0.0%                   | 29                                                         | 0.0%  | 15        | 1.7%  | 32        | -1.4% |

| 115.2k              | 8         | -3.5%                  | 16        | 2.1%  | 9         | 0.0%                   | 19                                                         | 0.0%  | 10        | -1.4% | 21        | -1.4% |

| 230.4k              | 3         | 8.5%                   | 8         | -3.5% | 4         | 0.0%                   | 9                                                          | 0.0%  | 4         | 8.5%  | 10        | -1.4% |

| 250k                | 3         | 0.0%                   | 7         | 0.0%  | 4         | -7.8%                  | 8                                                          | 2.4%  | 4         | 0.0%  | 9         | 0.0%  |

| 0.5M                | 1         | 0.0%                   | 3         | 0.0%  | _         | _                      | 4                                                          | -7.8% | _         | _     | 4         | 0.0%  |

| 1M                  | 0         | 0.0%                   | 1         | 0.0%  | _         | _                      | _                                                          | -     | _         | _     | _         | -     |

| Max. <sup>(1)</sup> | 1 M       | lbps                   | 2 N       | lbps  | 1.152     | Mbps                   | 2.304                                                      | Mbps  | 1.25      | Mbps  | 2.5       | Vbps  |

| Table 17-12. | Examples of UBRRn Settings for Commonly Use  | ed Oscillator Frequencies ( | Continued)  |

|--------------|----------------------------------------------|-----------------------------|-------------|

|              | Examples of Serie ange for Serie and the Sec |                             | contantaca) |

1. UBRRn = 0, Error = 0.0%

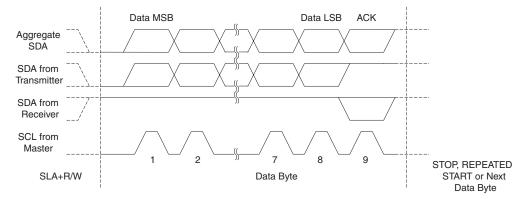

#### 19.3.4 Data Packet Format

All data packets transmitted on the TWI bus are nine bits long, consisting of one data byte and an acknowledge bit. During a data transfer, the Master generates the clock and the START and STOP conditions, while the Receiver is responsible for acknowledging the reception. An Acknowledge (ACK) is signalled by the Receiver pulling the SDA line low during the ninth SCL cycle. If the Receiver leaves the SDA line high, a NACK is signalled. When the Receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the Transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first.

#### Figure 19-5. Data Packet Format

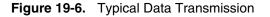

#### 19.3.5 Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the Wired-ANDing of the SCL line can be used to implement handshaking between the Master and the Slave. The Slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the Master is too fast for the Slave, or the Slave needs extra time for processing between the data transmissions. The Slave extending the SCL low period will not affect the SCL high period, which is determined by the Master. As a consequence, the Slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

Figure 19-6 shows a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

# 19.5 Overview of the TWI Module

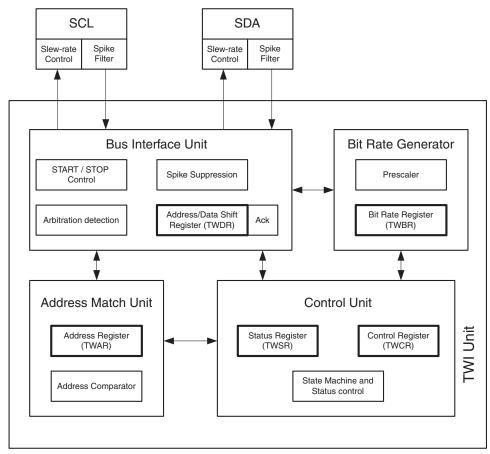

The TWI module is comprised of several submodules, as shown in Figure 19-9. All registers drawn in a thick line are accessible through the AVR data bus.

### 19.5.1 SCL and SDA Pins

These pins interface the AVR TWI with the rest of the MCU system. The output drivers contain a slew-rate limiter in order to conform to the TWI specification. The input stages contain a spike suppression unit removing spikes shorter than 50 ns. Note that the internal pull-ups in the AVR pads can be enabled by setting the PORT bits corresponding to the SCL and SDA pins, as explained in the I/O Port section. The internal pull-ups can in some systems eliminate the need for external ones.

## 19.5.2 Bit Rate Generator Unit

This unit controls the period of SCL when operating in a Master mode. The SCL period is controlled by settings in the TWI Bit Rate Register (TWBR) and the Prescaler bits in the TWI Status Register (TWSR). Slave operation does not depend on Bit Rate or Prescaler settings, but the CPU clock frequency in the Slave must be at least 16 times higher than the SCL frequency. Note

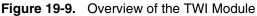

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multi master system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The following figure shows the flow in this transfer.

# 19.9 Multi-master Systems and Arbitration

If multiple masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two masters are trying to transmit data to a Slave Receiver.

#### Figure 19-21. An Arbitration Example

Several different scenarios may arise during arbitration, as described below:

- Two or more masters are performing identical communication with the same Slave. In this case, neither the Slave nor any of the masters will know about the bus contention.

- Two or more masters are accessing the same Slave with different data or direction bit. In this case, arbitration will occur, either in the READ/WRITE bit or in the data bits. The masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Losing masters will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

| Extended Fuse Byte | Bit No | Description                                     | Default Value                 |  |

|--------------------|--------|-------------------------------------------------|-------------------------------|--|

| -                  | 7      | -                                               | 1                             |  |

| -                  | 6      | -                                               | 1                             |  |

| -                  | 5      | -                                               | 1                             |  |

| -                  | 4      | -                                               | 1                             |  |

| -                  | 3      | -                                               | 1                             |  |

| BOOTSZ1            | 2      | Select Boot Size<br>(see Table 113 for details) | 0 (programmed) <sup>(1)</sup> |  |

| BOOTSZ0            | 1      | Select Boot Size<br>(see Table 113 for details) | 0 (programmed) <sup>(1)</sup> |  |

| BOOTRST            | 0      | Select Reset Vector                             | 1 (unprogrammed)              |  |

Table 25-5.

Extended Fuse Byte for mega88/168

Note: 1. The default value of BOOTSZ1..0 results in maximum Boot Size. See Table 25-10 on page 285 for details.

| Table 25-6. | Fuse High Byte |

|-------------|----------------|

|-------------|----------------|

| High Fuse Byte           | Bit No | Description                                             | Default Value                              |  |

|--------------------------|--------|---------------------------------------------------------|--------------------------------------------|--|

| RSTDISBL <sup>(1)</sup>  | 7      | External Reset Disable                                  | 1 (unprogrammed)                           |  |

| DWEN                     | 6      | debugWIRE Enable                                        | 1 (unprogrammed)                           |  |

| SPIEN <sup>(2)</sup>     | 5      | Enable Serial Program and<br>Data Downloading           | 0 (programmed, SPI<br>programming enabled) |  |

| WDTON <sup>(3)</sup>     | 4      | Watchdog Timer Always On                                | 1 (unprogrammed)                           |  |

| EESAVE                   | 3      | EEPROM memory is<br>preserved through the Chip<br>Erase | 1 (unprogrammed), EEPROM not reserved      |  |

| BODLEVEL2 <sup>(4)</sup> | 2      | Brown-out Detector trigger level                        | 1 (unprogrammed)                           |  |

| BODLEVEL1 <sup>(4)</sup> | 1      | Brown-out Detector trigger level                        | 1 (unprogrammed)                           |  |

| BODLEVEL0 <sup>(4)</sup> | 0      | Brown-out Detector trigger level                        | 1 (unprogrammed)                           |  |

Notes: 1. See "Alternate Functions of Port C" on page 75 for description of RSTDISBL Fuse.

2. The SPIEN Fuse is not accessible in serial programming mode.

3. See "Watchdog Timer Control Register - WDTCSR" on page 52 for details.

4. See Table 8-2 on page 46 for BODLEVEL Fuse decoding.

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data low byte (0x00 0xFF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- 2. Give PAGEL a positive pulse. This latches the data bytes. (See Figure 25-3 for signal waveforms)

F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 25-2 on page 289. Note that if less than eight bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address low byte are used to address the page when performing a Page Write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- H. Program Page

- 1. Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- 2. Wait until RDY/BSY goes high (See Figure 25-3 for signal waveforms).

I. Repeat B through H until the entire Flash is programmed or until all data has been programmed.

J. End Page Programming

- 1. 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set DATA to "0000 0000". This is the command for No Operation.

- 3. Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

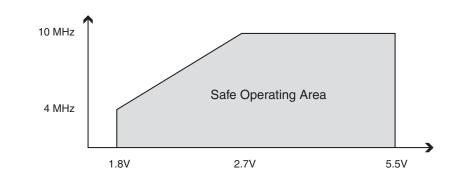

Figure 26-2. Maximum Frequency vs. V<sub>CC</sub>, ATmega48V/88V/168V

# 26.6 2-wire Serial Interface Characteristics

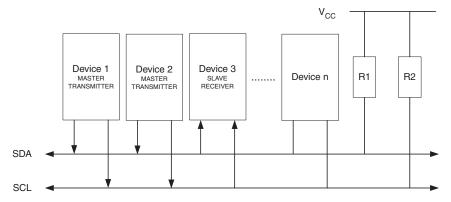

Table 26-2 describes the requirements for devices connected to the 2-wire Serial Bus. The ATmega48/88/168 2-wire Serial Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 26-4.

Table 26-2. 2-wire Serial Bus Requirements

| Symbol             | Parameter                                        | Condition                                      | Min                                      | Мах                   | Units |

|--------------------|--------------------------------------------------|------------------------------------------------|------------------------------------------|-----------------------|-------|

| VIL                | Input Low-voltage                                |                                                | -0.5                                     | 0.3 V <sub>CC</sub>   | V     |

| VIH                | Input High-voltage                               |                                                | 0.7 V <sub>CC</sub>                      | V <sub>CC</sub> + 0.5 | V     |

| (1)<br>Vhys        | Hysteresis of Schmitt Trigger Inputs             |                                                | 0.05 V <sub>CC</sub> <sup>(2)</sup>      | _                     | V     |

| VOL <sup>(1)</sup> | Output Low-voltage                               | 3 mA sink current                              | 0                                        | 0.4                   | V     |

| tr <sup>(1)</sup>  | Rise Time for both SDA and SCL                   |                                                | 20 + 0.1C <sub>b</sub> <sup>(3)(2)</sup> | 300                   | ns    |

| (1)<br>tof         | Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ | 10 pF < C <sub>b</sub> < 400 pF <sup>(3)</sup> | 20 + 0.1C <sub>b</sub> <sup>(3)(2)</sup> | 250                   | ns    |

| tSP <sup>(1)</sup> | Spikes Suppressed by Input Filter                |                                                | 0                                        | 50 <sup>(2)</sup>     | ns    |

| l <sub>i</sub>     | Input Current each I/O Pin                       | $0.1V_{\rm CC} < V_{\rm i} < 0.9V_{\rm CC}$    | -10                                      | 10                    | μA    |

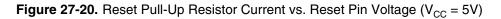

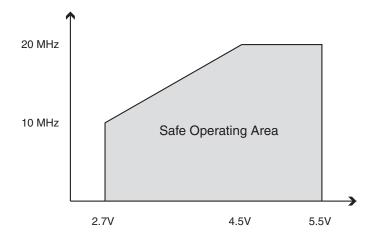

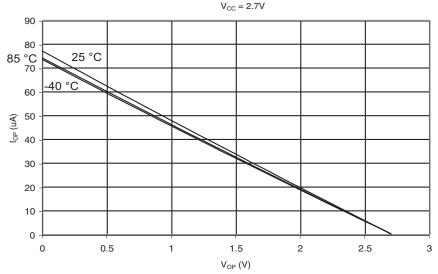

Figure 27-19. I/O Pin Pull-Up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 2.7V)

I/O PIN PULL-UP RESISTOR CURRENT vs. INPUT VOLTAGE