#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-TQFP                                                                  |

| Supplier Device Package    | 32-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega88v-10ai |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The fast-access Register File contains  $32 \times 8$ -bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the Reset routine (before subroutines or interrupts are executed). The Stack Pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F. In addition, the ATmega48/88/168 has Extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

## 4.3 ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

# 5. AVR ATmega48/88/168 Memories

This section describes the different memories in the ATmega48/88/168. The AVR architecture has two main memory spaces, the Data Memory and the Program Memory space. In addition, the ATmega48/88/168 features an EEPROM Memory for data storage. All three memory spaces are linear and regular.

## 5.1 In-System Reprogrammable Flash Program Memory

The ATmega48/88/168 contains 4/8/16K bytes On-chip In-System Reprogrammable Flash memory for program storage. Since all AVR instructions are 16 or 32 bits wide, the Flash is organized as 2/4/8K x 16. For software security, the Flash Program memory space is divided into two sections, Boot Loader Section and Application Program Section in ATmega88 and ATmega168. ATmega48 does not have separate Boot Loader and Application Program sections, and the SPM instruction can be executed from the entire Flash. See SELFPRGEN description in section "Store Program Memory Control and Status Register – SPMCSR" on page 259 and page 269for more details.

The Flash memory has an endurance of at least 10,000 write/erase cycles. The ATmega48/88/168 Program Counter (PC) is 11/12/13 bits wide, thus addressing the 2/4/8K program memory locations. The operation of Boot Program section and associated Boot Lock bits for software protection are described in detail in "Self-Programming the Flash, ATmega48" on page 256 and "Boot Loader Support – Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264. "Memory Programming" on page 280 contains a detailed description on Flash Programming in SPI- or Parallel Programming mode.

Constant tables can be allocated within the entire program memory address space (see the LPM – Load Program Memory instruction description).

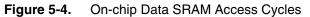

Timing diagrams for instruction fetch and execution are presented in "Instruction Execution Timing" on page 12.

### 5.3 EEPROM Data Memory

The ATmega48/88/168 contains 256/512/512 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM Data Register, and the EEPROM Control Register.

"Memory Programming" on page 280 contains a detailed description on EEPROM Programming in SPI or Parallel Programming mode.

#### 5.3.1 EEPROM Read/Write Access

The EEPROM Access Registers are accessible in the I/O space.

The write access time for the EEPROM is given in Table 5-2. A self-timing function, however, lets the user software detect when the next byte can be written. If the user code contains instructions that write the EEPROM, some precautions must be taken. In heavily filtered power supplies,  $V_{CC}$  is likely to rise or fall slowly on power-up/down. This causes the device for some period of time to run at a voltage lower than specified as minimum for the clock frequency used. See "Preventing EEPROM Corruption" on page 23 for details on how to avoid problems in these situations.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

# ATmega48/88/168

Note: If the Watchdog is accidentally enabled, for example by a runaway pointer or brown-out condition, the device will be reset and the Watchdog Timer will stay enabled. If the code is not set up to handle the Watchdog, this might lead to an eternal loop of time-out resets. To avoid this situation, the application software should always clear the Watchdog System Reset Flag (WDRF) and the WDE control bit in the initialisation routine, even if the Watchdog is not in use.

The following code example shows one assembly and one C function for changing the time-out value of the Watchdog Timer.

```

Assembly Code Example<sup>(1)</sup>

WDT_Prescaler_Change:

; Turn off global interrupt

cli

; Reset Watchdog Timer

wdr

; Start timed sequence

lds r16, WDTCSR

ori

r16, (1<<WDCE) | (1<<WDE)

sts WDTCSR, r16

; -- Got four cycles to set the new values from here -

; Set new prescaler(time-out) value = 64K cycles (~0.5 s)

r16, (1<<WDE) | (1<<WDP2) | (1<<WDP0)

ldi

sts WDTCSR, r16

; -- Finished setting new values, used 2 cycles -

; Turn on global interrupt

sei

ret

C Code Example<sup>(1)</sup>

void WDT_Prescaler_Change(void)

{

__disable_interrupt();

__watchdog_reset();

/* Start timed equence */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* Set new prescaler(time-out) value = 64K cycles (~0.5 s) */

WDTCSR = (1<<WDE) | (1<<WDP2) | (1<<WDP0);

_enable_interrupt();

}

```

Note: 1. See "About Code Examples" on page 6.

Note: The Watchdog Timer should be reset before any change of the WDP bits, since a change in the WDP bits can result in a time-out when switching to a shorter time-out period.

```

Assembly Code Examples<sup>(1)</sup>

```

```

...

; Set TCNT1 to 0x01FF

ldi r17,0x01

ldi r16,0xFF

out TCNT1H,r17

out TCNT1L,r16

; Read TCNT1 into r17:r16

in r16,TCNT1L

in r17,TCNT1H

....

```

C Code Examples<sup>(1)</sup>

```

unsigned int i;

...

/* Set TCNT1 to 0x01FF */

TCNT1 = 0x1FF;

/* Read TCNT1 into i */

i = TCNT1;

...

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNT1 value in the r17:r16 register pair.

It is important to notice that accessing 16-bit registers are atomic operations. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit Timer Registers, then the result of the access outside the interrupt will be corrupted. Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access.

The following code examples show how to do an atomic read of the TCNT1 Register contents. Reading any of the OCR1A/B or ICR1 Registers can be done by using the same principle.

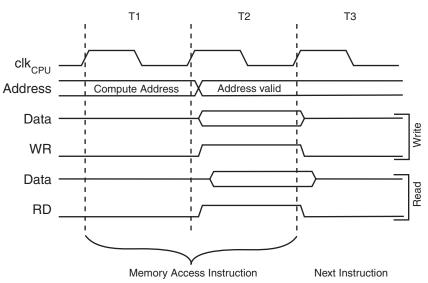

## 13.4 Counter Unit

The main part of the 16-bit Timer/Counter is the programmable 16-bit bi-directional counter unit. Figure 13-2 shows a block diagram of the counter and its surroundings.

Signal description (internal signals):

| Count             | Increment or decrement TCNT1 by 1.                     |

|-------------------|--------------------------------------------------------|

| Direction         | Select between increment and decrement.                |

| Clear             | Clear TCNT1 (set all bits to zero).                    |

| clk <sub>T1</sub> | Timer/Counter clock.                                   |

| ТОР               | Signalize that TCNT1 has reached maximum value.        |

| воттом            | Signalize that TCNT1 has reached minimum value (zero). |

The 16-bit counter is mapped into two 8-bit I/O memory locations: *Counter High* (TCNT1H) containing the upper eight bits of the counter, and *Counter Low* (TCNT1L) containing the lower eight bits. The TCNT1H Register can only be indirectly accessed by the CPU. When the CPU does an access to the TCNT1H I/O location, the CPU accesses the high byte temporary register (TEMP). The temporary register is updated with the TCNT1H value when the TCNT1L is read, and TCNT1H is updated with the temporary register value when TCNT1L is written. This allows the CPU to read or write the entire 16-bit counter value within one clock cycle via the 8-bit data bus. It is important to notice that there are special cases of writing to the TCNT1 Register when the counter is counting that will give unpredictable results. The special cases are described in the sections where they are of importance.

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each *timer clock* ( $clk_{T1}$ ). The  $clk_{T1}$  can be generated from an external or internal clock source, selected by the *Clock Select* bits (CS12:0). When no clock source is selected (CS12:0 = 0) the timer is stopped. However, the TCNT1 value can be accessed by the CPU, independent of whether  $clk_{T1}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the *Waveform Generation mode* bits (WGM13:0) located in the *Timer/Counter Control Registers* A and B (TCCR1A and TCCR1B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC1x. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 118.

the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution in bits can be calculated using the following equation:

$$R_{PFCPWM} = \frac{\log(TOP + 1)}{\log(2)}$$

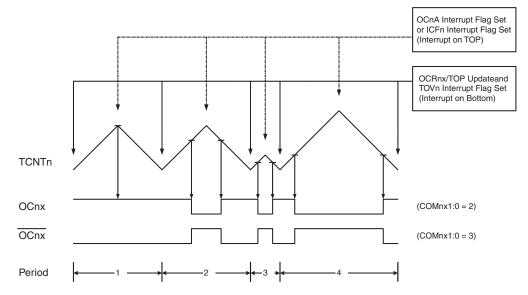

In phase and frequency correct PWM mode the counter is incremented until the counter value matches either the value in ICR1 (WGM13:0 = 8), or the value in OCR1A (WGM13:0 = 9). The counter has then reached the TOP and changes the count direction. The TCNT1 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct and frequency correct PWM mode is shown on Figure 13-9. The figure shows phase and frequency correct PWM mode when OCR1A or ICR1 is used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

Figure 13-9. Phase and Frequency Correct PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV1) is set at the same timer clock cycle as the OCR1x Registers are updated with the double buffer value (at BOTTOM). When either OCR1A or ICR1 is used for defining the TOP value, the OC1A or ICF1 Flag set when TCNT1 has reached TOP. The Interrupt Flags can then be used to generate an interrupt each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNT1 and the OCR1x.

As Figure 13-9 shows the output generated is, in contrast to the phase correct mode, symmetrical in all periods. Since the OCR1x Registers are updated at BOTTOM, the length of the rising and the falling slopes will always be equal. This gives symmetrical output pulses and is therefore frequency correct.

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of<br>Operation  | ТОР    | Update of<br>OCR1x at | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|-------------------------------------|--------|-----------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                              | 0xFFFF | Immediate             | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit           | 0x00FF | TOP                   | BOTTOM              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit           | 0x01FF | TOP                   | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit          | 0x03FF | TOP                   | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | CTC                                 | OCR1A  | Immediate             | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                     | 0x00FF | TOP                   | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                     | 0x01FF | TOP                   | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                    | 0x03FF | TOP                   | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct | ICR1   | BOTTOM                | BOTTOM              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct | OCR1A  | BOTTOM                | BOTTOM              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                  | ICR1   | TOP                   | BOTTOM              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                  | OCR1A  | TOP                   | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                                 | ICR1   | Immediate             | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                          | _      | _                     | _                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                            | ICR1   | TOP                   | TOP                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                            | OCR1A  | TOP                   | TOP                 |

Table 13-4.

Waveform Generation Mode Bit Description<sup>(1)</sup>

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

#### 13.10.2 Timer/Counter1 Control Register B – TCCR1B

| Bit           | 7     | 6     | 5 | 4     | 3     | 2    | 1    | 0    | _      |

|---------------|-------|-------|---|-------|-------|------|------|------|--------|

|               | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  | -      |

| Initial Value | 0     | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

#### • Bit 7 – ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the noise canceler is activated, the input from the Input Capture pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four Oscillator cycles when the noise canceler is enabled.

#### • Bit 6 – ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture pin (ICP1) that is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

A FOC1A/FOC1B strobe will not generate any interrupt nor will it clear the timer in Clear Timer on Compare match (CTC) mode using OCR1A as TOP.

The FOC1A/FOC1B bits are always read as zero.

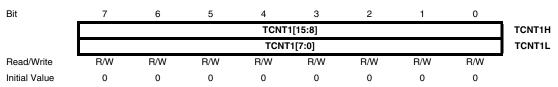

#### 13.10.4 Timer/Counter1 – TCNT1H and TCNT1L

The two *Timer/Counter* I/O locations (TCNT1H and TCNT1L, combined TCNT1) give direct access, both for read and for write operations, to the Timer/Counter unit 16-bit counter. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See Section "13.2" on page 108.

Modifying the counter (TCNT1) while the counter is running introduces a risk of missing a compare match between TCNT1 and one of the OCR1x Registers.

Writing to the TCNT1 Register blocks (removes) the compare match on the following timer clock for all compare units.

#### 13.10.5 Output Compare Register 1 A – OCR1AH and OCR1AL

| Bit           | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   | _      |

|---------------|-----|-----|-----|------|---------|-----|-----|-----|--------|

|               |     |     |     | OCR1 | A[15:8] |     |     |     | OCR1AH |

|               |     |     |     | OCR1 | A[7:0]  |     |     |     | OCR1AL |

| Read/Write    | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |        |

| Initial Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |        |

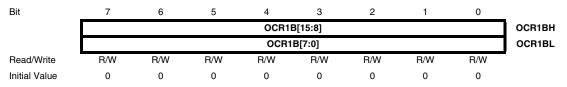

#### 13.10.6 Output Compare Register 1 B – OCR1BH and OCR1BL

The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNT1). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC1x pin.

The Output Compare Registers are 16-bit in size. To ensure that both the high and low bytes are written simultaneously when the CPU writes to these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See Section "13.2" on page 108.

# 14. Timer/Counter0 and Timer/Counter1 Prescalers

"8-bit Timer/Counter0 with PWM" on page 88 and "16-bit Timer/Counter1 with PWM" on page 106 share the same prescaler module, but the Timer/Counters can have different prescaler settings. The description below applies to both Timer/Counter1 and Timer/Counter0.

#### 14.0.1 Internal Clock Source

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system clock frequency ( $f_{CLK_{-}I/O}$ ). Alternatively, one of four taps from the prescaler can be used as a clock source. The prescaled clock has a frequency of either  $f_{CLK_{-}I/O}/8$ ,  $f_{CLK_{-}I/O}/64$ ,  $f_{CLK_{-}I/O}/256$ , or  $f_{CLK_{-}I/O}/1024$ .

#### 14.0.2 Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of the Timer/Counter, and it is shared by Timer/Counter1 and Timer/Counter0. Since the prescaler is not affected by the Timer/Counter's clock select, the state of the prescaler will have implications for situations where a prescaled clock is used. One example of prescaling artifacts occurs when the timer is enabled and clocked by the prescaler (6 > CSn2:0 > 1). The number of system clock cycles from when the timer is enabled to the first count occurs can be from 1 to N+1 system clock cycles, where N equals the prescaler divisor (8, 64, 256, or 1024).

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program execution. However, care must be taken if the other Timer/Counter that shares the same prescaler also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is connected to.

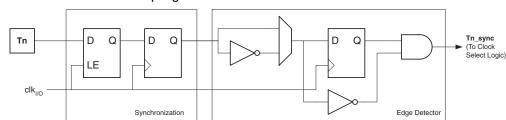

#### 14.0.3 External Clock Source

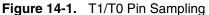

An external clock source applied to the T1/T0 pin can be used as Timer/Counter clock  $(clk_{T1}/clk_{T0})$ . The T1/T0 pin is sampled once every system clock cycle by the pin synchronization logic. The synchronized (sampled) signal is then passed through the edge detector. Figure 14-1 shows a functional equivalent block diagram of the T1/T0 synchronization and edge detector logic. The registers are clocked at the positive edge of the internal system clock ( $clk_{I/O}$ ). The latch is transparent in the high period of the internal system clock.

The edge detector generates one  $clk_{T1}/clk_{T0}$  pulse for each positive (CSn2:0 = 7) or negative (CSn2:0 = 6) edge it detects.

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles from an edge has been applied to the T1/T0 pin to the counter is updated.

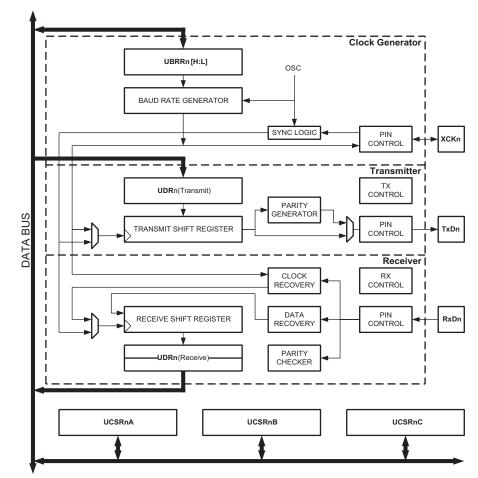

Figure 17-1. USART Block Diagram<sup>(1)</sup>

Note: 1. Refer to Figure 1-1 on page 2 and Table 10-9 on page 78 for USART0 pin placement.

## 17.2 Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: Normal asynchronous, Double Speed asynchronous, Master synchronous and Slave synchronous mode. The UMSELn bit in USART Control and Status Register C (UCSRnC) selects between asynchronous and synchronous operation. Double Speed (asynchronous mode only) is controlled by the U2Xn found in the UCSRnA Register. When using synchronous mode (UMSELn = 1), the Data Direction Register for the XCKn pin (DDR\_XCKn) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCKn pin is only active when using synchronous mode.

Figure 17-2 shows a block diagram of the clock generation logic.

## 17.5 Data Transmission – The USART Transmitter

The USART Transmitter is enabled by setting the *Transmit Enable* (TXEN) bit in the UCSRnB Register. When the Transmitter is enabled, the normal port operation of the TxDn pin is overridden by the USART and given the function as the Transmitter's serial output. The baud rate, mode of operation and frame format must be set up once before doing any transmissions. If synchronous operation is used, the clock on the XCKn pin will be overridden and used as transmission clock.

#### 17.5.1 Sending Frames with 5 to 8 Data Bit

A data transmission is initiated by loading the transmit buffer with the data to be transmitted. The CPU can load the transmit buffer by writing to the UDRn I/O location. The buffered data in the transmit buffer will be moved to the Shift Register when the Shift Register is ready to send a new frame. The Shift Register is loaded with new data if it is in idle state (no ongoing transmission) or immediately after the last stop bit of the previous frame is transmitted. When the Shift Register is loaded with new data, it will transfer one complete frame at the rate given by the Baud Register, U2Xn bit or by XCKn depending on mode of operation.

The following code examples show a simple USART transmit function based on polling of the *Data Register Empty* (UDREn) Flag. When using frames with less than eight bits, the most significant bits written to the UDRn are ignored. The USART has to be initialized before the function can be used. For the assembly code, the data to be sent is assumed to be stored in Register R16

```

Assembly Code Example<sup>(1)</sup>

```

```

USART_Transmit:

; Wait for empty transmit buffer

sbis UCSRnA,UDREn

rjmp USART_Transmit

; Put data (r16) into buffer, sends the data

out UDRn,r16

ret

```

C Code Example<sup>(1)</sup>

```

void USART_Transmit( unsigned char data )

{

/* Wait for empty transmit buffer */

while ( !( UCSRnA & (1<<UDREn)) )

;

/* Put data into buffer, sends the data */

UDRn = data;

}</pre>

```

Note: 1. See "About Code Examples" on page 6.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The function simply waits for the transmit buffer to be empty by checking the UDREn Flag, before loading it with new data to be transmitted. If the Data Register Empty interrupt is utilized, the interrupt routine writes the data into the buffer.

|               | $f_{osc} = 3.6$ | 864 MHz |           |       | $f_{osc} = 4.0$ | 0000 MHz          |           |       | f <sub>osc</sub> = 7.3 | 8728 MHz |           |        |

|---------------|-----------------|---------|-----------|-------|-----------------|-------------------|-----------|-------|------------------------|----------|-----------|--------|

| Baud          | U2Xn = 0        | ט       | U2Xn =    | 1     | U2Xn =          | U2Xn = 0 U2Xn = 1 |           |       | U2Xn = 0               |          | U2Xn = 1  |        |

| Rate<br>(bps) | UBRR<br>n       | Error   | UBRR<br>n | Error | UBRR<br>n       | Error             | UBRR<br>n | Error | UBRR<br>n              | Error    | UBRR<br>n | Error  |

| 2400          | 95              | 0.0%    | 191       | 0.0%  | 103             | 0.2%              | 207       | 0.2%  | 191                    | 0.0%     | 383       | 0.0%   |

| 4800          | 47              | 0.0%    | 95        | 0.0%  | 51              | 0.2%              | 103       | 0.2%  | 95                     | 0.0%     | 191       | 0.0%   |

| 9600          | 23              | 0.0%    | 47        | 0.0%  | 25              | 0.2%              | 51        | 0.2%  | 47                     | 0.0%     | 95        | 0.0%   |

| 14.4k         | 15              | 0.0%    | 31        | 0.0%  | 16              | 2.1%              | 34        | -0.8% | 31                     | 0.0%     | 63        | 0.0%   |

| 19.2k         | 11              | 0.0%    | 23        | 0.0%  | 12              | 0.2%              | 25        | 0.2%  | 23                     | 0.0%     | 47        | 0.0%   |

| 28.8k         | 7               | 0.0%    | 15        | 0.0%  | 8               | -3.5%             | 16        | 2.1%  | 15                     | 0.0%     | 31        | 0.0%   |

| 38.4k         | 5               | 0.0%    | 11        | 0.0%  | 6               | -7.0%             | 12        | 0.2%  | 11                     | 0.0%     | 23        | 0.0%   |

| 57.6k         | 3               | 0.0%    | 7         | 0.0%  | 3               | 8.5%              | 8         | -3.5% | 7                      | 0.0%     | 15        | 0.0%   |

| 76.8k         | 2               | 0.0%    | 5         | 0.0%  | 2               | 8.5%              | 6         | -7.0% | 5                      | 0.0%     | 11        | 0.0%   |

| 115.2k        | 1               | 0.0%    | 3         | 0.0%  | 1               | 8.5%              | 3         | 8.5%  | 3                      | 0.0%     | 7         | 0.0%   |

| 230.4k        | 0               | 0.0%    | 1         | 0.0%  | 0               | 8.5%              | 1         | 8.5%  | 1                      | 0.0%     | 3         | 0.0%   |

| 250k          | 0               | -7.8%   | 1         | -7.8% | 0               | 0.0%              | 1         | 0.0%  | 1                      | -7.8%    | 3         | -7.8%  |

| 0.5M          | -               | _       | 0         | -7.8% | -               | _                 | 0         | 0.0%  | 0                      | -7.8%    | 1         | -7.8%  |

| 1M            | -               | _       | -         | -     | -               | _                 | -         | _     | _                      | _        | 0         | -7.8%  |

| Max. (1)      | 230.4           | kbps    | 460.8     | kbps  | 250             | kbps              | 0.5 N     | Лbps  | 460.8                  | kbps     | 921.6     | 6 kbps |

| Table 17-10. | Examples of UBRRn Set | ettings for Commonly I | Used Oscillator Frequencies | (Continued)    |

|--------------|-----------------------|------------------------|-----------------------------|----------------|

|              |                       |                        |                             | (000.000.000.) |

1. UBRRn = 0, Error = 0.0%

shown below. See Table 25-5 on page 282 for detailed description and mapping of the Extended Fuse byte.

Bit 7 6 5 3 2 0 4 1 Rd FHB7 FHB6 FHB5 FHB4 FHB3 FHB2 FHB1 FHB0

Fuse and Lock bits that are programmed, will be read as zero. Fuse and Lock bits that are unprogrammed, will be read as one.

#### 23.1.4 Preventing Flash Corruption

During periods of low  $V_{CC}$ , the Flash program can be corrupted because the supply voltage is too low for the CPU and the Flash to operate properly. These issues are the same as for board level systems using the Flash, and the same design solutions should be applied.

A Flash program corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the Flash requires a minimum voltage to operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the supply voltage for executing instructions is too low.

Flash corruption can easily be avoided by following these design recommendations (one is sufficient):

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the SPMCSR Register and thus the Flash from unintentional writes.

#### 23.1.5 Programming Time for Flash when Using SPM

The calibrated RC Oscillator is used to time Flash accesses. Table 24-5 shows the typical programming time for Flash accesses from the CPU.

#### Table 23-1. SPM Programming Time

| Symbol                                                           | Min Programming Time | Max Programming Time |

|------------------------------------------------------------------|----------------------|----------------------|

| Flash write (Page Erase, Page Write, and write Lock bits by SPM) | 3.7 ms               | 4.5 ms               |

#### 23.1.6 Simple Assembly Code Example for a Boot Loader

Note that the RWWSB bit will always be read as zero in ATmega48. Nevertheless, it is recommended to check this bit as shown in the code example, to ensure compatibility with devices supporting Read-While-Write.

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data low byte (0x00 0xFF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- 2. Give PAGEL a positive pulse. This latches the data bytes. (See Figure 25-3 for signal waveforms)

F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 25-2 on page 289. Note that if less than eight bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address low byte are used to address the page when performing a Page Write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- H. Program Page

- 1. Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- 2. Wait until RDY/BSY goes high (See Figure 25-3 for signal waveforms).

I. Repeat B through H until the entire Flash is programmed or until all data has been programmed.

J. End Page Programming

- 1. 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set DATA to "0000 0000". This is the command for No Operation.

- 3. Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

#### Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |           | Instructio        | on Format         |                   |                                                                                                                                          |

|-------------------------------------------|-----------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                               | Byte 1    | Byte 2            | Byte 3            | Byte4             | Operation                                                                                                                                |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001 | 0000 0000         | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |

| Write EEPROM Memory<br>Page (page access) | 1100 0010 | 00xx xx <b>aa</b> | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |

| Read Lock bits                            | 0101 1000 | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |

| Write Lock bits                           | 1010 1100 | 111x xxxx         | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |

| Read Signature Byte                       | 0011 0000 | 000x xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |

| Write Fuse bits                           | 1010 1100 | 1010 0000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |

| Write Fuse High bits                      | 1010 1100 | 1010 1000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |

| Write Extended Fuse Bits                  | 1010 1100 | 1010 0100         | XXXX XXXX         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |

| Read Fuse bits                            | 0101 0000 | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |

| Read Fuse High bits                       | 0101 1000 | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |

| Read Extended Fuse Bits                   | 0101 0000 | 0000 1000         | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |

| Read Calibration Byte                     | 0011 1000 | 000x xxxx         | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |

| Poll RDY/BSY                              | 1111 0000 | 0000 0000         | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

#### 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

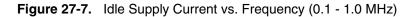

# 27.2 Idle Supply Current

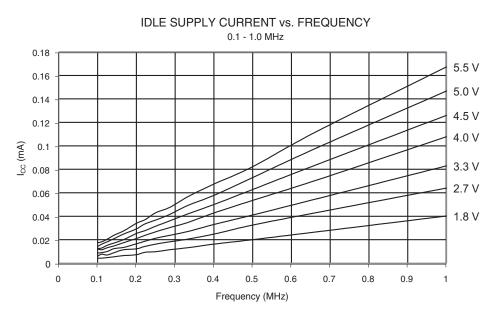

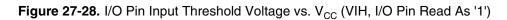

27.9 Pin Thresholds and Hysteresis

# 30.3 ATmega168

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code                  | Package <sup>(1)</sup> | Operational Range |

|----------------------------|--------------|--------------------------------|------------------------|-------------------|

|                            |              | ATmega168V-10AI                | 32A                    |                   |

|                            |              | ATmega168V-10PI                | 28P3                   |                   |

| 10                         |              | ATmega168V-10MI                | 32M1-A                 | Industrial        |

| 10                         | 1.8 - 5.5    | ATmega168V-10AU <sup>(2)</sup> | 32A                    | (-40°C to 85°C)   |

|                            |              | ATmega168V-10PU <sup>(2)</sup> | 28P3                   |                   |

|                            |              | ATmega168V-10MU <sup>(2)</sup> | 32M1-A                 |                   |

|                            |              | ATmega168-20AI                 | 32A                    |                   |

|                            |              | ATmega168-20PI                 | 28P3                   |                   |

| 00                         |              | ATmega168-20MI                 | 32M1-A                 | Industrial        |

| 20                         | 2.7 - 5.5    | ATmega168-20AU <sup>(2)</sup>  | 32A                    | (-40°C to 85°C)   |

|                            |              | ATmega168-20PU <sup>(2)</sup>  | 28P3                   |                   |

|                            |              | ATmega168-20MU <sup>(2)</sup>  | 32M1-A                 |                   |

Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. See Figure 26-2 on page 302 and Figure 26-3 on page 302.

|        | Package Type                                                                                      |

|--------|---------------------------------------------------------------------------------------------------|

| 32A    | 32-lead, Thin (1.0 mm) Plastic Quad Flat Package (TQFP)                                           |

| 28P3   | 28-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                          |

| 32M1-A | 32-pad, 5 x 5 x 1.0 body, Lead Pitch 0.50 mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF) |

# 32. Errata

## 32.1 Errata ATmega48

The revision letter in this section refers to the revision of the ATmega48 device.

#### 32.1.1 Rev A

- Wrong values read after Erase Only operation

- Watchdog Timer Interrupt disabled

- Start-up time with Crystal Oscillator is higher than expected

- High Power Consumption in Power-down with External Clock

- Asynchronous Oscillator does not stop in Power-down

#### 1. Wrong values read after Erase Only operation

At supply voltages below 2.7 V, an EEPROM location that is erased by the Erase Only operation may read as programmed (0x00).

#### **Problem Fix/Workaround**

If it is necessary to read an EEPROM location after Erase Only, use an Atomic Write operation with 0xFF as data in order to erase a location. In any case, the Write Only operation can be used as intended. Thus no special considerations are needed as long as the erased location is not read before it is programmed.

#### 2. Watchdog Timer Interrupt disabled

If the watchdog timer interrupt flag is not cleared before a new timeout occurs, the watchdog will be disabled, and the interrupt flag will automatically be cleared. This is only applicable in interrupt only mode. If the Watchdog is configured to reset the device in the watchdog time-out following an interrupt, the device works correctly.

#### Problem fix / Workaround

Make sure there is enough time to always service the first timeout event before a new watchdog timeout occurs. This is done by selecting a long enough time-out period.

#### 3. Start-up time with Crystal Oscillator is higher than expected

The clock counting part of the start-up time is about 2 times higher than expected for all start-up periods when running on an external Crystal. This applies only when waking up by reset. Wake-up from power down is not affected. For most settings, the clock counting parts is a small fraction of the overall start-up time, and thus, the problem can be ignored. The exception is when using a very low frequency crystal like for instance a 32 kHz clock crystal.

#### Problem fix / Workaround

No known workaround.

#### 4. High Power Consumption in Power-down with External Clock

The power consumption in power down with an active external clock is about 10 times higher than when using internal RC or external oscillators.

#### Problem fix / Workaround

Stop the external clock when the device is in power down.

#### 5. Asynchronous Oscillator does not stop in Power-down