Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega88v-10pi |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The fast-access Register File contains  $32 \times 8$ -bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the Reset routine (before subroutines or interrupts are executed). The Stack Pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F. In addition, the ATmega48/88/168 has Extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# 4.3 ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

# 5.3.2 The EEPROM Address Register – EEARH and EEARL

| Bit           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | _     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

|               | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

|               | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | Х     |       |

|               | Х     | х     | х     | х     | х     | х     | х     | Х     |       |

# • Bits 15..9 – Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

# • Bits 8..0 – EEAR8..0: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL specify the EEPROM address in the 256/512/512 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 255/511/511. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

EEAR8 is an unused bit in ATmega48 and must always be written to zero.

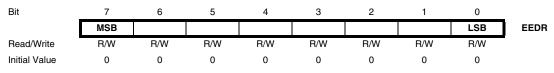

# 5.3.3 The EEPROM Data Register – EEDR

# Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR Register contains the data to be written to the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

# 5.3.4 The EEPROM Control Register – EECR

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|---------------|---|---|-------|-------|-------|-------|------|------|------|

|               | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write    | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | •    |

| Initial Value | 0 | 0 | Х     | х     | 0     | 0     | х    | 0    |      |

# • Bits 7..6 - Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

# • Bits 5, 4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits

The EEPROM Programming mode bit setting defines which programming action that will be triggered when writing EEPE. It is possible to program data in one atomic operation (erase the old value and program the new value) or to split the Erase and Write operations in two different operations. The Programming times for the different modes are shown in Table 5-1. While EEPE

| - |         |       |                    | 5                               |

|---|---------|-------|--------------------|---------------------------------|

|   | BOOTRST | IVSEL | Reset Address      | Interrupt Vectors Start Address |

| ſ | 1       | 0     | 0x000              | 0x001                           |

|   | 1       | 1     | 0x000              | Boot Reset Address + 0x001      |

|   | 0       | 0     | Boot Reset Address | 0x001                           |

|   | 0       | 1     | Boot Reset Address | Boot Reset Address + 0x001      |

Table 9-3.

Reset and Interrupt Vectors Placement in ATmega88<sup>(1)</sup>

Note: 1. The Boot Reset Address is shown in Table 24-6 on page 276. For the BOOTRST Fuse "1" means unprogrammed while "0" means programmed.

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Label | s Code                                                    |                | С   | omments                            |

|---------------|-----------------------------------------------------------|----------------|-----|------------------------------------|

| 0x000         | rjmp                                                      | RESET          | ;   | Reset Handler                      |

| 0x001         | rjmp                                                      | EXT_INT0       | ;   | IRQ0 Handler                       |

| 0x002         | rjmp                                                      | EXT_INT1       | ;   | IRQ1 Handler                       |

| 0x003         | rjmp                                                      | PCINT0         | ;   | PCINTO Handler                     |

| 0x004         | rjmp                                                      | PCINT1         | ;   | PCINT1 Handler                     |

| 0x005         | rjmp                                                      | PCINT2         | ;   | PCINT2 Handler                     |

| 0x006         | rjmp                                                      | WDT            | ;   | Watchdog Timer Handler             |

| 0x007         | rjmp                                                      | TIM2_COMPA     | ;   | Timer2 Compare A Handler           |

| 0X008         | rjmp                                                      | TIM2_COMPB     | ;   | Timer2 Compare B Handler           |

| 0x009         | rjmp                                                      | TIM2_OVF       | ;   | Timer2 Overflow Handler            |

| 0x00A         | rjmp                                                      | TIM1_CAPT      | ;   | Timer1 Capture Handler             |

| 0x00B         | rjmp                                                      | TIM1_COMPA     | ;   | Timer1 Compare A Handler           |

| 0x00C         | rjmp                                                      | TIM1_COMPB     | ;   | Timer1 Compare B Handler           |

| 0x00D         | rjmp                                                      | TIM1_OVF       | ;   | Timer1 Overflow Handler            |

| 0x00E         | rjmp                                                      | TIM0_COMPA     | ;   | Timer0 Compare A Handler           |

| 0x00F         | rjmp                                                      | TIM0_COMPB     | ;   | Timer0 Compare B Handler           |

| 0x010         | rjmp                                                      | TIM0_OVF       | ;   | Timer0 Overflow Handler            |

| 0x011         | rjmp                                                      | SPI_STC        | ;   | SPI Transfer Complete Handler      |

| 0x012         | rjmp                                                      | USART_RXC      | ;   | USART, RX Complete Handler         |

| 0x013         | rjmp                                                      | USART_UDRE     | ;   | USART, UDR Empty Handler           |

| 0x014         | rjmp                                                      | USART_TXC      | ;   | USART, TX Complete Handler         |

| 0x015         | rjmp                                                      | ADC            | ;   | ADC Conversion Complete Handler    |

| 0x016         | rjmp                                                      | EE_RDY         | ;   | EEPROM Ready Handler               |

| 0x017         | rjmp                                                      | ANA_COMP       | ;   | Analog Comparator Handler          |

| 0x018         | rjmp                                                      | TWI            | ;   | 2-wire Serial Interface Handler    |

| 0x019         | rjmp                                                      | SPM_RDY        | ;   | Store Program Memory Ready Handler |

| ;             |                                                           |                |     |                                    |

| 0x01ARESET:   | ldi                                                       | r16, high(RAME | IND | ); Main program start              |

| 0x01B         | out                                                       | SPH,r16        | ;   | Set Stack Pointer to top of RAM    |

| 0x01C         | ldi                                                       | r16, low(RAMEN | ID) |                                    |

| 0x01D         | out                                                       | SPL,r16        |     |                                    |

| 0x01E         | sei                                                       |                | ;   | Enable interrupts                  |

| 0x01F         | <inst< td=""><td>r&gt; xxx</td><td></td><td></td></inst<> | r> xxx         |     |                                    |

# • T1/OC0B/PCINT21 - Port D, Bit 5

T1, Timer/Counter1 counter source.

OC0B, Output Compare Match output: The PD5 pin can serve as an external output for the Timer/Counter0 Compare Match B. The PD5 pin has to be configured as an output (DDD5 set (one)) to serve this function. The OC0B pin is also the output pin for the PWM mode timer function.

PCINT21: Pin Change Interrupt source 21. The PD5 pin can serve as an external interrupt source.

## • XCK/T0/PCINT20 - Port D, Bit 4

XCK, USART external clock.

T0, Timer/Counter0 counter source.

PCINT20: Pin Change Interrupt source 20. The PD4 pin can serve as an external interrupt source.

## • INT1/OC2B/PCINT19 - Port D, Bit 3

INT1, External Interrupt source 1: The PD3 pin can serve as an external interrupt source.

OC2B, Output Compare Match output: The PD3 pin can serve as an external output for the Timer/Counter0 Compare Match B. The PD3 pin has to be configured as an output (DDD3 set (one)) to serve this function. The OC2B pin is also the output pin for the PWM mode timer function.

PCINT19: Pin Change Interrupt source 19. The PD3 pin can serve as an external interrupt source.

#### • INT0/PCINT18 - Port D, Bit 2

INTO, External Interrupt source 0: The PD2 pin can serve as an external interrupt source.

PCINT18: Pin Change Interrupt source 18. The PD2 pin can serve as an external interrupt source.

#### • TXD/PCINT17 – Port D, Bit 1

TXD, Transmit Data (Data output pin for the USART). When the USART Transmitter is enabled, this pin is configured as an output regardless of the value of DDD1.

PCINT17: Pin Change Interrupt source 17. The PD1 pin can serve as an external interrupt source.

# • RXD/PCINT16 – Port D, Bit 0

RXD, Receive Data (Data input pin for the USART). When the USART Receiver is enabled this pin is configured as an input regardless of the value of DDD0. When the USART forces this pin to be an input, the pull-up can still be controlled by the PORTD0 bit.

PCINT16: Pin Change Interrupt source 16. The PD0 pin can serve as an external interrupt source.

Table 10-10 and Table 10-11 relate the alternate functions of Port D to the overriding signals shown in Figure 10-5 on page 69.

The Timer/Counter Overflow Flag (TOV1) is set according to the mode of operation selected by the WGM13:0 bits. TOV1 can be used for generating a CPU interrupt.

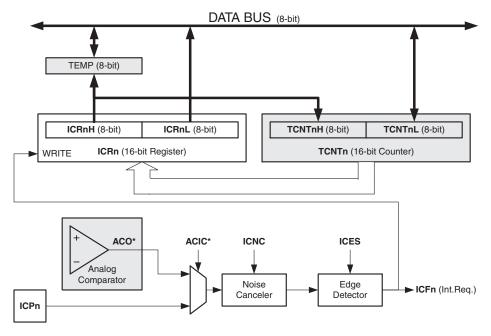

# 13.5 Input Capture Unit

The Timer/Counter incorporates an Input Capture unit that can capture external events and give them a time-stamp indicating time of occurrence. The external signal indicating an event, or multiple events, can be applied via the ICP1 pin or alternatively, via the analog-comparator unit. The time-stamps can then be used to calculate frequency, duty-cycle, and other features of the signal applied. Alternatively the time-stamps can be used for creating a log of the events.

The Input Capture unit is illustrated by the block diagram shown in Figure 13-3. The elements of the block diagram that are not directly a part of the Input Capture unit are gray shaded. The small "n" in register and bit names indicates the Timer/Counter number.

Figure 13-3. Input Capture Unit Block Diagram

When a change of the logic level (an event) occurs on the *Input Capture pin* (ICP1), alternatively on the *Analog Comparator output* (ACO), and this change confirms to the setting of the edge detector, a capture will be triggered. When a capture is triggered, the 16-bit value of the counter (TCNT1) is written to the *Input Capture Register* (ICR1). The *Input Capture Flag* (ICF1) is set at the same system clock as the TCNT1 value is copied into ICR1 Register. If enabled (ICIE1 = 1), the Input Capture Flag generates an Input Capture interrupt. The ICF1 Flag is automatically cleared when the interrupt is executed. Alternatively the ICF1 Flag can be cleared by software by writing a logical one to its I/O bit location.

Reading the 16-bit value in the *Input Capture Register* (ICR1) is done by first reading the low byte (ICR1L) and then the high byte (ICR1H). When the low byte is read the high byte is copied into the high byte temporary register (TEMP). When the CPU reads the ICR1H I/O location it will access the TEMP Register.

The ICR1 Register can only be written when using a Waveform Generation mode that utilizes the ICR1 Register for defining the counter's TOP value. In these cases the *Waveform Genera*-

When the ICR1 is used as TOP value (see description of the WGM13:0 bits located in the TCCR1A and the TCCR1B Register), the ICP1 is disconnected and consequently the Input Capture function is disabled.

# • Bit 5 – Reserved Bit

This bit is reserved for future use. For ensuring compatibility with future devices, this bit must be written to zero when TCCR1B is written.

# • Bit 4:3 – WGM13:2: Waveform Generation Mode

See TCCR1A Register description.

# • Bit 2:0 - CS12:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter, see Figure 13-10 and Figure 13-11.

| CS12 | CS11 | CS10 | Description                                             |  |  |  |  |

|------|------|------|---------------------------------------------------------|--|--|--|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |  |  |  |  |

| 0    | 0    | 1    | clk <sub>I/O</sub> /1 (No prescaling)                   |  |  |  |  |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |  |  |  |  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |  |  |  |  |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |  |  |  |  |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |  |  |  |  |

| 1    | 1    | 0    | External clock source on T1 pin. Clock on falling edge. |  |  |  |  |

| 1    | 1    | 1    | External clock source on T1 pin. Clock on rising edge.  |  |  |  |  |

Table 13-5. Clock Select Bit Description

If external pin modes are used for the Timer/Counter1, transitions on the T1 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

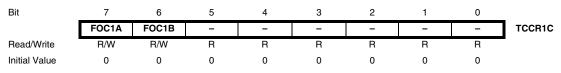

# 13.10.3 Timer/Counter1 Control Register C – TCCR1C

# • Bit 7 – FOC1A: Force Output Compare for Channel A

# • Bit 6 – FOC1B: Force Output Compare for Channel B

The FOC1A/FOC1B bits are only active when the WGM13:0 bits specifies a non-PWM mode. However, for ensuring compatibility with future devices, these bits must be set to zero when TCCR1A is written when operating in a PWM mode. When writing a logical one to the FOC1A/FOC1B bit, an immediate compare match is forced on the Waveform Generation unit. The OC1A/OC1B output is changed according to its COM1x1:0 bits setting. Note that the FOC1A/FOC1B bits are implemented as strobes. Therefore it is the value present in the COM1x1:0 bits that determine the effect of the forced compare.

A FOC1A/FOC1B strobe will not generate any interrupt nor will it clear the timer in Clear Timer on Compare match (CTC) mode using OCR1A as TOP.

The FOC1A/FOC1B bits are always read as zero.

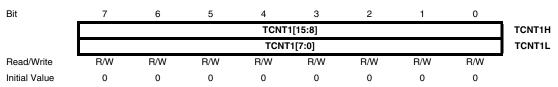

## 13.10.4 Timer/Counter1 – TCNT1H and TCNT1L

The two *Timer/Counter* I/O locations (TCNT1H and TCNT1L, combined TCNT1) give direct access, both for read and for write operations, to the Timer/Counter unit 16-bit counter. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See Section "13.2" on page 108.

Modifying the counter (TCNT1) while the counter is running introduces a risk of missing a compare match between TCNT1 and one of the OCR1x Registers.

Writing to the TCNT1 Register blocks (removes) the compare match on the following timer clock for all compare units.

#### 13.10.5 Output Compare Register 1 A – OCR1AH and OCR1AL

| Bit           | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   | _      |

|---------------|-----|-----|-----|------|---------|-----|-----|-----|--------|

|               |     |     |     | OCR1 | A[15:8] |     |     |     | OCR1AH |

|               |     |     |     | OCR1 | A[7:0]  |     |     |     | OCR1AL |

| Read/Write    | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |        |

| Initial Value | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |        |

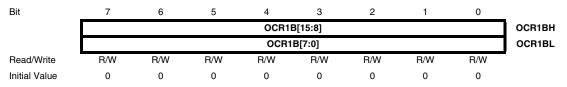

#### 13.10.6 Output Compare Register 1 B – OCR1BH and OCR1BL

The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNT1). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC1x pin.

The Output Compare Registers are 16-bit in size. To ensure that both the high and low bytes are written simultaneously when the CPU writes to these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. See Section "13.2" on page 108.

# 13.10.9 Timer/Counter1 Interrupt Flag Register – TIFR1

| Bit           | 7 | 6 | 5    | 4 | 3 | 2     | 1     | 0    | _     |

|---------------|---|---|------|---|---|-------|-------|------|-------|

|               | - | - | ICF1 | - | - | OCF1B | OCF1A | TOV1 | TIFR1 |

| Read/Write    | R | R | R/W  | R | R | R/W   | R/W   | R/W  | -     |

| Initial Value | 0 | 0 | 0    | 0 | 0 | 0     | 0     | 0    |       |

#### • Bit 7, 6 - Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### • Bit 5 – ICF1: Timer/Counter1, Input Capture Flag

This flag is set when a capture event occurs on the ICP1 pin. When the Input Capture Register (ICR1) is set by the WGM13:0 to be used as the TOP value, the ICF1 Flag is set when the counter reaches the TOP value.

ICF1 is automatically cleared when the Input Capture Interrupt Vector is executed. Alternatively, ICF1 can be cleared by writing a logic one to its bit location.

#### Bit 4, 3 – Res: Reserved Bits

These bits are unused bits in the ATmega48/88/168, and will always read as zero.

#### Bit 2 – OCF1B: Timer/Counter1, Output Compare B Match Flag

This flag is set in the timer clock cycle after the counter (TCNT1) value matches the Output Compare Register B (OCR1B).

Note that a Forced Output Compare (FOC1B) strobe will not set the OCF1B Flag.

OCF1B is automatically cleared when the Output Compare Match B Interrupt Vector is executed. Alternatively, OCF1B can be cleared by writing a logic one to its bit location.

#### • Bit 1 – OCF1A: Timer/Counter1, Output Compare A Match Flag

This flag is set in the timer clock cycle after the counter (TCNT1) value matches the Output Compare Register A (OCR1A).

Note that a Forced Output Compare (FOC1A) strobe will not set the OCF1A Flag.

OCF1A is automatically cleared when the Output Compare Match A Interrupt Vector is executed. Alternatively, OCF1A can be cleared by writing a logic one to its bit location.

#### Bit 0 – TOV1: Timer/Counter1, Overflow Flag

The setting of this flag is dependent of the WGM13:0 bits setting. In Normal and CTC modes, the TOV1 Flag is set when the timer overflows. Refer to Table 13-4 on page 130 for the TOV1 Flag behavior when using another WGM13:0 bit setting.

TOV1 is automatically cleared when the Timer/Counter1 Overflow Interrupt Vector is executed. Alternatively, TOV1 can be cleared by writing a logic one to its bit location.

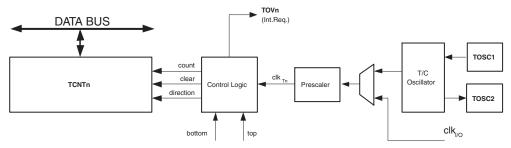

Signal description (internal signals):

| count             | Increment or decrement TCNT2 by 1.                               |

|-------------------|------------------------------------------------------------------|

| direction         | Selects between increment and decrement.                         |

| clear             | Clear TCNT2 (set all bits to zero).                              |

| clk <sub>Tn</sub> | Timer/Counter clock, referred to as $clk_{T2}$ in the following. |

| top               | Signalizes that TCNT2 has reached maximum value.                 |

| bottom            | Signalizes that TCNT2 has reached minimum value (zero).          |

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T2}$ ).  $clk_{T2}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS22:0). When no clock source is selected (CS22:0 = 0) the timer is stopped. However, the TCNT2 value can be accessed by the CPU, regardless of whether  $clk_{T2}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM21 and WGM20 bits located in the Timer/Counter Control Register (TCCR2A) and the WGM22 located in the Timer/Counter Control Register B (TCCR2B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC2A and OC2B. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 143.

The Timer/Counter Overflow Flag (TOV2) is set according to the mode of operation selected by the WGM22:0 bits. TOV2 can be used for generating a CPU interrupt.

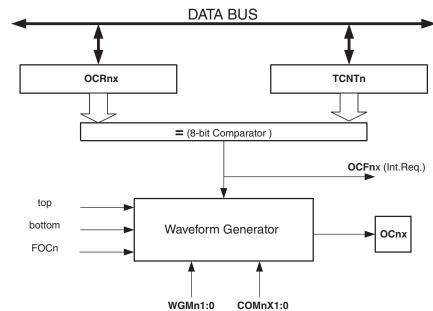

# 15.4 Output Compare Unit

The 8-bit comparator continuously compares TCNT2 with the Output Compare Register (OCR2A and OCR2B). Whenever TCNT2 equals OCR2A or OCR2B, the comparator signals a match. A match will set the Output Compare Flag (OCF2A or OCF2B) at the next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare Flag generates an Output Compare interrupt. The Output Compare Flag is automatically cleared when the interrupt is executed. Alternatively, the Output Compare Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the WGM22:0 bits and Compare Output mode (COM2x1:0) bits. The max and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation ("Modes of Operation" on page 143).

Figure 15-3 shows a block diagram of the Output Compare unit.

Figure 15-3. Output Compare Unit, Block Diagram

The OCR2x Register is double buffered when using any of the Pulse Width Modulation (PWM) modes. For the Normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR2x Compare Register to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCR2x Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR2x Buffer Register, and if double buffering is disabled the CPU will access the OCR2x directly.

# 15.4.1 Force Output Compare

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC2x) bit. Forcing compare match will not set the OCF2x Flag or reload/clear the timer, but the OC2x pin will be updated as if a real compare match had occurred (the COM2x1:0 bits settings define whether the OC2x pin is set, cleared or toggled).

# 15.4.2 Compare Match Blocking by TCNT2 Write

All CPU write operations to the TCNT2 Register will block any compare match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCR2x to be initialized to the same value as TCNT2 without triggering an interrupt when the Timer/Counter clock is enabled.

#### 15.4.3 Using the Output Compare Unit

Since writing TCNT2 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT2 when using the Output Compare channel, independently of whether the Timer/Counter is running or not. If the value written to TCNT2 equals the OCR2x value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT2 value equal to BOTTOM when the counter is downcounting.

## 15.8.2 Timer/Counter Control Register B – TCCR2B

| Bit           | 7     | 6     | 5 | 4 | 3     | 2    | 1    | 0    | _      |

|---------------|-------|-------|---|---|-------|------|------|------|--------|

|               | FOC2A | FOC2B | - | - | WGM22 | CS22 | CS21 | CS20 | TCCR2B |

| Read/Write    | W     | W     | R | R | R     | R    | R/W  | R/W  | -      |

| Initial Value | 0     | 0     | 0 | 0 | 0     | 0    | 0    | 0    |        |

#### • Bit 7 – FOC2A: Force Output Compare A

The FOC2A bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR2B is written when operating in PWM mode. When writing a logical one to the FOC2A bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC2A output is changed according to its COM2A1:0 bits setting. Note that the FOC2A bit is implemented as a strobe. Therefore it is the value present in the COM2A1:0 bits that determines the effect of the forced compare.

A FOC2A strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR2A as TOP.

The FOC2A bit is always read as zero.

#### Bit 6 – FOC2B: Force Output Compare B

The FOC2B bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR2B is written when operating in PWM mode. When writing a logical one to the FOC2B bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC2B output is changed according to its COM2B1:0 bits setting. Note that the FOC2B bit is implemented as a strobe. Therefore it is the value present in the COM2B1:0 bits that determines the effect of the forced compare.

A FOC2B strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR2B as TOP.

The FOC2B bit is always read as zero.

#### Bits 5:4 – Res: Reserved Bits

These bits are reserved bits in the ATmega48/88/168 and will always read as zero.

#### Bit 3 – WGM22: Waveform Generation Mode

See the description in the "Timer/Counter Control Register A – TCCR2A" on page 149.

#### Bit 2:0 – CS22:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter, see Table 15-9.

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|---------------------|---------------------------------------|

| 5                        | 93.20                 | 106.67                | +6.67/-6.8          | ± 3.0                                 |

| 6                        | 94.12                 | 105.79                | +5.79/-5.88         | ± 2.5                                 |

| 7                        | 94.81                 | 105.11                | +5.11/-5.19         | ± 2.0                                 |

| 8                        | 95.36                 | 104.58                | +4.58/-4.54         | ± 2.0                                 |

| 9                        | 95.81                 | 104.14                | +4.14/-4.19         | ± 1.5                                 |

| 10                       | 96.17                 | 103.78                | +3.78/-3.83         | ± 1.5                                 |

Table 17-2.

Recommended Maximum Receiver Baud Rate Error for Normal Speed Mode (U2Xn = 0)

Table 17-3.Recommended Maximum Receiver Baud Rate Error for Double Speed Mode<br/>(U2Xn = 1)

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|---------------------|---------------------------------------|

| 5                        | 94.12                 | 105.66                | +5.66/-5.88         | ± 2.5                                 |

| 6                        | 94.92                 | 104.92                | +4.92/-5.08         | ± 2.0                                 |

| 7                        | 95.52                 | 104,35                | +4.35/-4.48         | ± 1.5                                 |

| 8                        | 96.00                 | 103.90                | +3.90/-4.00         | ± 1.5                                 |

| 9                        | 96.39                 | 103.53                | +3.53/-3.61         | ± 1.5                                 |

| 10                       | 96.70                 | 103.23                | +3.23/-3.30         | ± 1.0                                 |

The recommendations of the maximum receiver baud rate error was made under the assumption that the Receiver and Transmitter equally divides the maximum total error.

There are two possible sources for the receivers baud rate error. The Receiver's system clock (XTAL) will always have some minor instability over the supply voltage range and the temperature range. When using a crystal to generate the system clock, this is rarely a problem, but for a resonator the system clock may differ more than 2% depending of the resonators tolerance. The second source for the error is more controllable. The baud rate generator can not always do an exact division of the system frequency to get the baud rate wanted. In this case an UBRRn value that gives an acceptable low error can be used if possible.

# 17.8 Multi-processor Communication Mode

Setting the Multi-processor Communication mode (MPCMn) bit in UCSRnA enables a filtering function of incoming frames received by the USART Receiver. Frames that do not contain address information will be ignored and not put into the receive buffer. This effectively reduces the number of incoming frames that has to be handled by the CPU, in a system with multiple MCUs that communicate via the same serial bus. The Transmitter is unaffected by the MPCMn setting, but has to be used differently when it is a part of a system utilizing the Multi-processor Communication mode.

If the Receiver is set up to receive frames that contain 5 to 8 data bits, then the first stop bit indicates if the frame contains data or address information. If the Receiver is set up for frames with

UDREn is set after a reset to indicate that the Transmitter is ready.

# • Bit 4 – FEn: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when received. I.e., when the first stop bit of the next character in the receive buffer is zero. This bit is valid until the receive buffer (UDRn) is read. The FEn bit is zero when the stop bit of received data is one. Always set this bit to zero when writing to UCSRnA.

# • Bit 3 – DORn: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the Receive Shift Register, and a new start bit is detected. This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

# • Bit 2 – UPEn: USART Parity Error

This bit is set if the next character in the receive buffer had a Parity Error when received and the Parity Checking was enabled at that point (UPMn1 = 1). This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

## • Bit 1 – U2Xn: Double the USART Transmission Speed

This bit only has effect for the asynchronous operation. Write this bit to zero when using synchronous operation.

Writing this bit to one will reduce the divisor of the baud rate divider from 16 to 8 effectively doubling the transfer rate for asynchronous communication.

# • Bit 0 – MPCMn: Multi-processor Communication Mode

This bit enables the Multi-processor Communication mode. When the MPCMn bit is written to one, all the incoming frames received by the USART Receiver that do not contain address information will be ignored. The Transmitter is unaffected by the MPCMn setting. For more detailed information see "Multi-processor Communication Mode" on page 185.

# 17.9.3 USART Control and Status Register n B – UCSRnB

| Bit           | 7      | 6      | 5      | 4     | 3     | 2      | 1     | 0     | _      |

|---------------|--------|--------|--------|-------|-------|--------|-------|-------|--------|

|               | RXCIEn | TXCIEn | UDRIEn | RXENn | TXENn | UCSZn2 | RXB8n | TXB8n | UCSRnB |

| Read/Write    | R/W    | R/W    | R/W    | R/W   | R/W   | R/W    | R     | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0     | 0     | 0      | 0     | 0     |        |

# Bit 7 – RXCIEn: RX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the RXCn Flag. A USART Receive Complete interrupt will be generated only if the RXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXCn bit in UCSRnA is set.

# • Bit 6 – TXCIEn: TX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the TXCn Flag. A USART Transmit Complete interrupt will be generated only if the TXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXCn bit in UCSRnA is set.

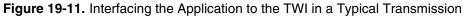

- 1. The first step in a TWI transmission is to transmit a START condition. This is done by writing a specific value into TWCR, instructing the TWI hardware to transmit a START condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the START condition.

- 2. When the START condition has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the START condition has successfully been sent.

- 3. The application software should now examine the value of TWSR, to make sure that the START condition was successfully transmitted. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load SLA+W into TWDR. Remember that TWDR is used both for address and data. After TWDR has been loaded with the desired SLA+W, a specific value must be written to TWCR, instructing the TWI hardware to transmit the SLA+W present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the address packet.

- 4. When the address packet has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the address packet has successfully been sent. The status code will also reflect whether a Slave acknowledged the packet or not.

- 5. The application software should now examine the value of TWSR, to make sure that the address packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load a data packet into TWDR. Subsequently, a specific value must be written to TWCR, instructing the TWI hardware to transmit the data packet present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will

The upper 7 bits are the address to which the 2-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (0x00), otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | тимс | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "0" (write), the TWI will operate in SR mode, otherwise ST mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 19-5. The Slave Receiver mode may also be entered if arbitration is lost while the TWI is in the Master mode (see states 0x68 and 0x78).

If the TWEA bit is reset during a transfer, the TWI will return a "Not Acknowledge" ("1") to SDA after the next received data byte. This can be used to indicate that the Slave is not able to receive any more bytes. While TWEA is zero, the TWI does not acknowledge its own slave address. However, the 2-wire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the 2-wire Serial Bus.

In all sleep modes other than Idle mode, the clock system to the TWI is turned off. If the TWEA bit is set, the interface can still acknowledge its own slave address or the general call address by using the 2-wire Serial Bus clock as a clock source. The part will then wake up from sleep and the TWI will hold the SCL clock low during the wake up and until the TWINT Flag is cleared (by writing it to one). Further data reception will be carried out as normal, with the AVR clocks running as normal. Observe that if the AVR is set up with a long start-up time, the SCL line may be held low for a long time, blocking other data transmissions.

Note that the 2-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these Sleep modes.

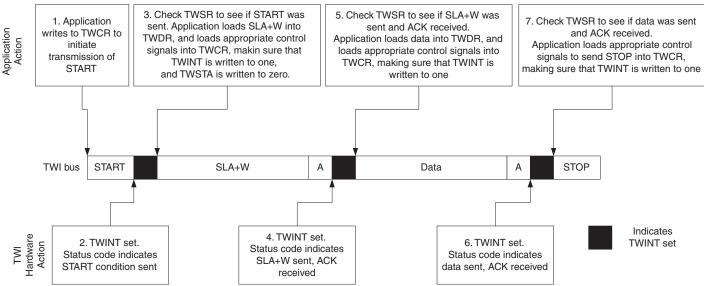

# ATmega48/88/168

**Figure 24-3.** Addressing the Flash During SPM<sup>(1)</sup>

# 24.7 Self-Programming the Flash

The program memory is updated in a page by page fashion. Before programming a page with the data stored in the temporary page buffer, the page must be erased. The temporary page buffer is filled one word at a time using SPM and the buffer can be filled either before the Page Erase command or between a Page Erase and a Page Write operation:

Alternative 1, fill the buffer before a Page Erase

- Fill temporary page buffer

- Perform a Page Erase

- Perform a Page Write

Alternative 2, fill the buffer after Page Erase

- Perform a Page Erase

- Fill temporary page buffer

- Perform a Page Write

If only a part of the page needs to be changed, the rest of the page must be stored (for example in the temporary page buffer) before the erase, and then be rewritten. When using alternative 1, the Boot Loader provides an effective Read-Modify-Write feature which allows the user software to first read the page, do the necessary changes, and then write back the modified data. If alternative 2 is used, it is not possible to read the old data while loading since the page is already erased. The temporary page buffer can be accessed in a random sequence. It is essential that the page address used in both the Page Erase and Page Write operation is addressing the same page. See "Simple Assembly Code Example for a Boot Loader" on page 275 for an assembly code example.

| Variable |          | Corresponding<br>Z-value <sup>(1)</sup> | Description                                                                                                                 |

|----------|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PCMSB    | 12       |                                         | Most significant bit in the Program Counter. (The Program Counter is 12 bits PC[11:0])                                      |

| PAGEMSB  | 5        |                                         | Most significant bit which is used to address<br>the words within one page (64 words in a page<br>requires 6 bits PC [5:0]) |

| ZPCMSB   |          | Z13                                     | Bit in Z-register that is mapped to PCMSB. Because Z0 is not used, the ZPCMSB equals PCMSB + 1.                             |

| ZPAGEMSB |          | Z6                                      | Bit in Z-register that is mapped to PAGEMSB.<br>Because Z0 is not used, the ZPAGEMSB equals<br>PAGEMSB + 1.                 |

| PCPAGE   | PC[12:6] | Z13:Z7                                  | Program counter page address: Page select, for page erase and page write                                                    |

| PCWORD   | PC[5:0]  | Z6:Z1                                   | Program counter word address: Word select, for filling temporary buffer (must be zero during page write operation)          |

Table 24-11.

Explanation of Different Variables used in Figure 24-3 and the Mapping to the Z-pointer, ATmega168

Note: 1. Z15:Z14: always ignored

Z0: should be zero for all SPM commands, byte select for the LPM instruction. See "Addressing the Flash During Self-Programming" on page 270 for details about the use of Z-pointer during Self-Programming.

## Table 25-17. Serial Programming Instruction Set (Continued)

|                                           |                 | Instructio        | on Format         |                   |                                                                                                                                          |  |

|-------------------------------------------|-----------------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction                               | Byte 1 Byte 2 B |                   | Byte 3            | Byte4             | Operation                                                                                                                                |  |

| Load EEPROM Memory<br>Page (page access)  | 1100 0001       | 0000 0000         | <b>dd</b> 00 0000 | iiii iiii         | Load data i to EEPROM memory page<br>buffer. After data is loaded, program<br>EEPROM page.                                               |  |

| Write EEPROM Memory<br>Page (page access) | 1100 0010       | 00xx xx <b>aa</b> | bbbb bb00         | xxxx xxxx         | Write EEPROM page at address <b>a</b> : <b>b</b> .                                                                                       |  |

| Read Lock bits                            | 0101 1000       | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed, "1"<br>= unprogrammed. See Table 25-1 on<br>page 280 for details.                                      |  |

| Write Lock bits                           | 1010 1100       | 111x xxxx         | XXXX XXXX         | 11 <b>ii iiii</b> | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 25-1 on<br>page 280 for details.                                      |  |

| Read Signature Byte                       | 0011 0000       | 000x xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                       |  |

| Write Fuse bits                           | 1010 1100       | 1010 0000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See <b>Table XXX on page</b><br><b>XXX</b> for details.                                  |  |

| Write Fuse High bits                      | 1010 1100       | 1010 1000         | XXXX XXXX         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 21-1 on page<br>244 for details.                                               |  |

| Write Extended Fuse Bits                  | 1010 1100       | 1010 0100         | xxxx xxxx         | xxxx xxii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 25-4 on page<br>281 for details.                                               |  |

| Read Fuse bits                            | 0101 0000       | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed, "1"<br>= unprogrammed. See <b>Table XXX on</b><br><b>page XXX</b> for details.                         |  |

| Read Fuse High bits                       | 0101 1000       | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse High bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 21-1 on page 244 for details.                               |  |

| Read Extended Fuse Bits                   | 0101 0000       | 0000 1000         | xxxx xxxx         | 0000 0000         | Read Extended Fuse bits. "0" = pro-<br>grammed, "1" = unprogrammed. See<br>Table 25-4 on page 281 for details.                           |  |

| Read Calibration Byte                     | 0011 1000       | 000x xxxx         | 0000 0000         | 0000 0000         | Read Calibration Byte                                                                                                                    |  |

| Poll RDY/BSY                              | 1111 0000       | 0000 0000         | XXXX XXXX         | xxxx xxx <b>o</b> | If $\mathbf{o} = "1"$ , a programming operation is<br>still busy. Wait until this bit returns to<br>"0" before applying another command. |  |

Note: **a** = address high bits, **b** = address low bits, **H** = 0 - Low byte, 1 - High Byte, **o** = data out, **i** = data in, x = don't care

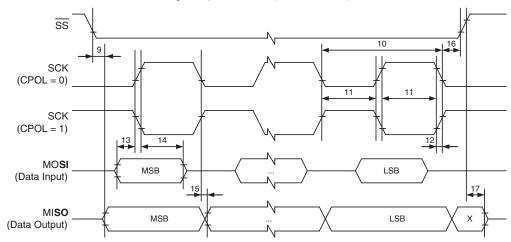

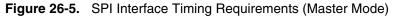

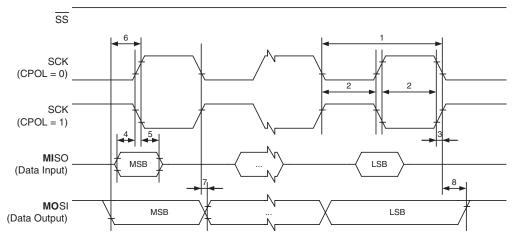

# 25.9.2 SPI Serial Programming Characteristics

For characteristics of the SPI module see "SPI Timing Characteristics" on page 304.

# 26. Electrical Characteristics

# 26.1 Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                                                                      |

|----------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                        |

| Voltage on any Pin except $\overline{\text{RESET}}$ with respect to Ground0.5V to V $_{\text{CC}}$ +0.5V |

| Voltage on $\overrightarrow{\text{RESET}}$ with respect to Ground0.5V to +13.0V                          |

| Maximum Operating Voltage 6.0V                                                                           |

| DC Current per I/O Pin 40.0 mA                                                                           |

| DC Current $V_{CC}$ and GND Pins                                                                         |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 26.2 DC Characteristics

$T_A = -40^{\circ}C$  to 85°C,  $V_{CC} = 1.8V$  to 5.5V (unless otherwise noted)

| Symbol           | Parameter                                                | Condition                                                          | Min. <sup>(5)</sup>                                                    | Тур. | Max. <sup>(5)</sup>                                                    | Units |

|------------------|----------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|------|------------------------------------------------------------------------|-------|

| V <sub>IL</sub>  | Input Low Voltage, except<br>XTAL1 and RESET pin         | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | -0.5<br>-0.5                                                           |      | 0.2V <sub>CC</sub> <sup>(1)</sup><br>0.3V <sub>CC</sub> <sup>(1)</sup> | V     |

| V <sub>IH</sub>  | Input High Voltage, except XTAL1 and RESET pins          | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | 0.7V <sub>CC</sub> <sup>(2)</sup><br>0.6V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5<br>V <sub>CC</sub> + 0.5                         | V     |

| V <sub>IL1</sub> | Input Low Voltage,<br>XTAL1 pin                          | V <sub>CC</sub> = 1.8V - 5.5V                                      | -0.5                                                                   |      | 0.1V <sub>CC</sub> <sup>(1)</sup>                                      | V     |

| V <sub>IH1</sub> | Input High Voltage,<br>XTAL1 pin                         | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | 0.8V <sub>CC</sub> <sup>(2)</sup><br>0.7V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5<br>V <sub>CC</sub> + 0.5                         | V     |

| V <sub>IL2</sub> | Input Low Voltage,<br>RESET pin                          | V <sub>CC</sub> = 1.8V - 5.5V                                      | -0.5                                                                   |      | 0.2V <sub>CC</sub> <sup>(1)</sup>                                      | V     |

| V <sub>IH2</sub> | Input High Voltage,<br>RESET pin                         | V <sub>CC</sub> = 1.8V - 5.5V                                      | 0.9V <sub>CC</sub> <sup>(2)</sup>                                      |      | V <sub>CC</sub> + 0.5                                                  | V     |

| V <sub>IL3</sub> | Input Low Voltage,<br>RESET pin as I/O                   | $V_{CC} = 1.8V - 2.4V$<br>$V_{CC} = 2.4V - 5.5V$                   | -0.5<br>-0.5                                                           |      | 0.2V <sub>CC</sub> <sup>(1)</sup><br>0.3V <sub>CC</sub> <sup>(1)</sup> | V     |

| V <sub>IH3</sub> | Input High Voltage,<br>RESET pin as I/O                  | V <sub>CC</sub> = 1.8V - 2.4V<br>V <sub>CC</sub> = 2.4V - 5.5V     | 0.7V <sub>CC</sub> <sup>(2)</sup><br>0.6V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5<br>V <sub>CC</sub> + 0.5                         | V     |

| V <sub>OL</sub>  | Output Low Voltage <sup>(3)</sup> ,<br>RESET pin as I/O  | $I_{OL} = 20$ mA, $V_{CC} = 5V$<br>$I_{OL} = 6$ mA, $V_{CC} = 3V$  |                                                                        |      | 0.7<br>0.5                                                             | V     |

| V <sub>OH</sub>  | Output High Voltage <sup>(4)</sup> ,<br>RESET pin as I/O | $I_{OH}$ = -20mA, $V_{CC}$ = 5V<br>$I_{OH}$ = -10mA, $V_{CC}$ = 3V | 4.2<br>2.3                                                             |      |                                                                        | V     |

| V <sub>OL3</sub> | Output Low Voltage <sup>(3)</sup> ,<br>RESET pin as I/O  | TBD                                                                |                                                                        |      | TBD                                                                    | V     |

| V <sub>OH3</sub> | Output High Voltage <sup>(4)</sup> ,<br>RESET pin as I/O | TBD                                                                | TBD                                                                    |      |                                                                        | V     |

| I <sub>IL</sub>  | Input Leakage<br>Current I/O Pin                         | V <sub>CC</sub> = 5.5V, pin low<br>(absolute value)                |                                                                        |      | 1                                                                      | μA    |

| I <sub>IH</sub>  | Input Leakage<br>Current I/O Pin                         | V <sub>CC</sub> = 5.5V, pin high<br>(absolute value)               |                                                                        |      | 1                                                                      | μA    |

Figure 26-6. SPI Interface Timing Requirements (Slave Mode)