#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 65                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                  |

| Data Converters            | A/D - 12b SAR                                                                |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 125-VFBGA                                                                    |

| Supplier Device Package    | 125-BGA (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32pg12b500f1024il125-cr |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2 Power

The EFM32PG12 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. An optional integrated DC-DC buck regulator can be utilized to further reduce the current consumption. The DC-DC regulator requires one external inductor and one external capacitor.

The EFM32PG12 device family includes support for internal supply voltage scaling, as well as two different power domains groups for peripherals. These enhancements allow for further supply current reductions and lower overall power consumption.

AVDD and VREGVDD need to be 1.8 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the DC-DC to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

### 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

### 3.2.3 Power Domains

The EFM32PG12 has two peripheral power domains for operation in EM2 and lower. If all of the peripherals in a peripheral power domain are configured as unused, the power domain for that group will be powered off in the low-power mode, reducing the overall current consumption of the device.

| Peripheral Power Domain 1 | Peripheral Power Domain 2 |

|---------------------------|---------------------------|

| ACMP0                     | ACMP1                     |

| PCNT0                     | PCNT1                     |

| ADC0                      | PCNT2                     |

| LETIMER0                  | CSEN                      |

| LESENSE                   | DAC0                      |

| APORT                     | LEUART0                   |

| -                         | 12C0                      |

| -                         | I2C1                      |

| -                         | IDAC                      |

#### Table 3.1. Peripheral Power Subdomains

### 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

### 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling so-phisticated operations to be implemented.

## 4.1.3 Thermal Characteristics

| Parameter          | Symbol              | Test Condition                                       | Min | Тур  | Мах | Unit |

|--------------------|---------------------|------------------------------------------------------|-----|------|-----|------|

| Thermal Resistance | THETA <sub>JA</sub> | QFN48 Package, 2-Layer PCB,<br>Air velocity = 0 m/s  | —   | 75.7 | _   | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 1 m/s  | —   | 61.5 | _   | °C/W |

|                    |                     | QFN48 Package, 2-Layer PCB,<br>Air velocity = 2 m/s  | _   | 55.4 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 0 m/s  | _   | 30.2 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 1 m/s  |     | 26.3 | _   | °C/W |

|                    |                     | QFN48 Package, 4-Layer PCB,<br>Air velocity = 2 m/s  |     | 24.9 | _   | °C/W |

|                    |                     | BGA125 Package, 2-Layer PCB,<br>Air velocity = 0 m/s |     | 90.7 |     | °C/W |

|                    |                     | BGA125 Package, 2-Layer PCB,<br>Air velocity = 1 m/s |     | 73.7 | _   | °C/W |

|                    |                     | BGA125 Package, 2-Layer PCB,<br>Air velocity = 2 m/s |     | 66.4 | _   | °C/W |

|                    |                     | BGA125 Package, 4-Layer PCB,<br>Air velocity = 0 m/s | _   | 45   | _   | °C/W |

|                    |                     | BGA125 Package, 4-Layer PCB,<br>Air velocity = 1 m/s |     | 39.6 | _   | °C/W |

|                    |                     | BGA125 Package, 4-Layer PCB,<br>Air velocity = 2 m/s |     | 37.6 | _   | °C/W |

### Table 4.3. Thermal Characteristics

### 4.1.5.3 Current Consumption 1.8 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 1.8 V.  $T_{OP}$  = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at  $T_{OP}$  = 25 °C.

| Table 4.7. | Current Consumption 1.8 V without DC-DC Converter |  |

|------------|---------------------------------------------------|--|

| Parameter                                                              | Symbol                 | Test Condition                                                        | Min | Тур  | Max | Unit   |

|------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals disabled          | I <sub>ACTIVE</sub>    | 38.4 MHz crystal, CPU running while loop from flash <sup>1</sup>      | _   | 126  | _   | µA/MHz |

| ableu                                                                  |                        | 38 MHz HFRCO, CPU running<br>Prime from flash                         | _   | 99   | —   | µA/MHz |

|                                                                        |                        | 38 MHz HFRCO, CPU running while loop from flash                       | _   | 99   | _   | µA/MHz |

|                                                                        |                        | 38 MHz HFRCO, CPU running<br>CoreMark from flash                      | _   | 124  | _   | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO, CPU running while loop from flash                       | _   | 102  |     | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO, CPU running while loop from flash                        | _   | 277  | _   | µA/MHz |

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE_VS</sub> | 19 MHz HFRCO, CPU running while loop from flash                       | _   | 87   | _   | µA/MHz |

| abled and voltage scaling enabled                                      |                        | 1 MHz HFRCO, CPU running while loop from flash                        | _   | 231  | _   | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1</sub>       | 38.4 MHz crystal <sup>1</sup>                                         | _   | 76   | _   | µA/MHz |

| mode with all peripherals disabled                                     |                        | 38 MHz HFRCO                                                          | _   | 50   |     | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO                                                          | _   | 52   |     | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO                                                           | _   | 227  | _   | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub>    | 19 MHz HFRCO                                                          | _   | 47   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                        | 1 MHz HFRCO                                                           | _   | 190  | _   | µA/MHz |

| Current consumption in EM2 mode, with votage scaling                   | IEM2_VS                | Full 256 kB RAM retention and RTCC running from LFXO                  | _   | 2.8  | _   | μΑ     |

| enabled.                                                               |                        | Full 256 kB RAM retention and RTCC running from LFRCO                 | _   | 3.0  | _   | μA     |

|                                                                        |                        | 16 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup> | _   | 1.9  | —   | μA     |

| Current consumption in EM3 mode, with voltage scaling enabled.         | I <sub>EM3_VS</sub>    | Full 256 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   | _   | 2.47 | _   | μA     |

| Current consumption in<br>EM4H mode, with voltage                      | I <sub>EM4H_VS</sub>   | 128 byte RAM retention, RTCC running from LFXO                        | —   | 0.91 | _   | μA     |

| scaling enabled.                                                       |                        | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO            | —   | 0.35 |     | μA     |

|                                                                        |                        | 128 byte RAM retention, no RTCC                                       | _   | 0.35 |     | μA     |

| Current consumption in EM4S mode                                       | I <sub>EM4S</sub>      | no RAM retention, no RTCC                                             |     | 0.04 |     | μA     |

# 4.1.9 Flash Memory Characteristics<sup>3</sup>

| Parameter                                   | Symbol               | Test Condition            | Min   | Тур  | Мах | Unit   |

|---------------------------------------------|----------------------|---------------------------|-------|------|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                           | 10000 | _    | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T <sub>AMB</sub> ≤ 85 °C  | 10    |      | _   | years  |

|                                             |                      | T <sub>AMB</sub> ≤ 125 °C | 10    |      | _   | years  |

| Word (32-bit) programming time              | tw_prog              |                           | 20    | 24.4 | 30  | μs     |

| Page erase time                             | t <sub>PERASE</sub>  |                           | 20    | 26.4 | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                           | 20    | 26.5 | 35  | ms     |

| Device erase time <sup>2</sup>              | t <sub>DERASE</sub>  | T <sub>AMB</sub> ≤ 85 °C  | -     | 69   | 100 | ms     |

|                                             |                      | T <sub>AMB</sub> ≤ 125 °C | _     | 69   | 110 | ms     |

| Page erase current <sup>4</sup>             | I <sub>ERASE</sub>   |                           | _     | _    | 1.6 | mA     |

| Write current <sup>4</sup>                  | I <sub>WRITE</sub>   |                           | —     |      | 3.8 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                           | 1.62  |      | TBD | V      |

## Table 4.16. Flash Memory Characteristics<sup>3</sup>

## Note:

1. Mass erase is issued by the CPU and erases all flash.

2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

3. Flash data retention information is published in the Quarterly Quality and Reliability Report.

4. Measured at 25 °C.

| Parameter                  | Symbol            | Test Condition                       | Min | Тур | Мах | Unit |

|----------------------------|-------------------|--------------------------------------|-----|-----|-----|------|

| Output fall time, From 70% | t <sub>IOOF</sub> | C <sub>L</sub> = 50 pF,              | —   | 1.8 | _   | ns   |

| to 30% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              |     | 4.5 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Output rise time, From 30% | t <sub>ioor</sub> | C <sub>L</sub> = 50 pF,              |     | 2.2 | _   | ns   |

| to 70% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE = 0x6 <sup>1</sup>          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              |     | 7.4 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Note:                      |                   |                                      |     |     |     |      |

## 4.1.16 Capacitive Sense (CSEN)

| Parameter                                                               | Symbol                | Test Condition                                                                                                                         | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Single conversion time (1x                                              | t <sub>CNV</sub>      | 12-bit SAR Conversions                                                                                                                 | _   | 20.2 | _   | μs   |

| accumulation)                                                           |                       | 16-bit SAR Conversions                                                                                                                 | _   | 26.4 | _   | μs   |

|                                                                         |                       | Delta Modulation Conversion (sin-<br>gle comparison)                                                                                   | _   | 1.55 | _   | μs   |

| Maximum external capactive load                                         | C <sub>EXTMAX</sub>   | CS0CG=7 (Gain = 1x), including routing parasitics                                                                                      | _   | 68   | _   | pF   |

|                                                                         |                       | CS0CG=0 (Gain = 10x), including routing parasitics                                                                                     | _   | 680  | -   | pF   |

| Maximum external series impedance                                       | R <sub>EXTMAX</sub>   |                                                                                                                                        | —   | 1    | _   | kΩ   |

| Supply current, EM2 scan<br>conversions, WARMUP-                        | I <sub>CSEN_EM2</sub> | 12-bit SAR conversions, 20 ms scan rate, 8 samples per scan <sup>1</sup>                                                               | _   | 800  | _   | nA   |

| MODE=NORMAL, WAR-<br>MUPCNT=0                                           |                       | Delta Modulation conversions, 20<br>ms scan rate, 8 comparisons per<br>sample (DMCR = 1, DMR = 2), 8<br>samples per scan <sup>1</sup>  | _   | 590  | _   | nA   |

|                                                                         |                       | 12-bit SAR conversions, 200 ms scan rate, 8 samples per scan <sup>1</sup>                                                              | _   | 80   | _   | nA   |

|                                                                         |                       | Delta Modulation conversions,<br>200 ms scan rate, 8 comparisons<br>per sample (DMCR = 1, DMR =<br>2), 8 samples per scan <sup>1</sup> | _   | 59   | _   | nA   |

| Supply current, continuous<br>conversions, WARMUP-<br>MODE=KEEPCSENWARM | ICSEN_ACTIVE          | SAR or Delta Modulation conver-<br>sions of 33 pF capacitor, always<br>on                                                              | _   | 90.5 | -   | μA   |

### Table 4.23. Capacitive Sense (CSEN)

### Note:

1. Current is specified with a total external capacitance of 33 pF. Average current is dependent on how long the module is actively sampling channels within the scan period, and will scale linearly with the number of samples acquired. Supply current for a specific application can be caclulated by multiplying the current per sample by the total number of samples per period (total\_current = single\_sample\_current \* (number\_of\_channels \* accumulation)).

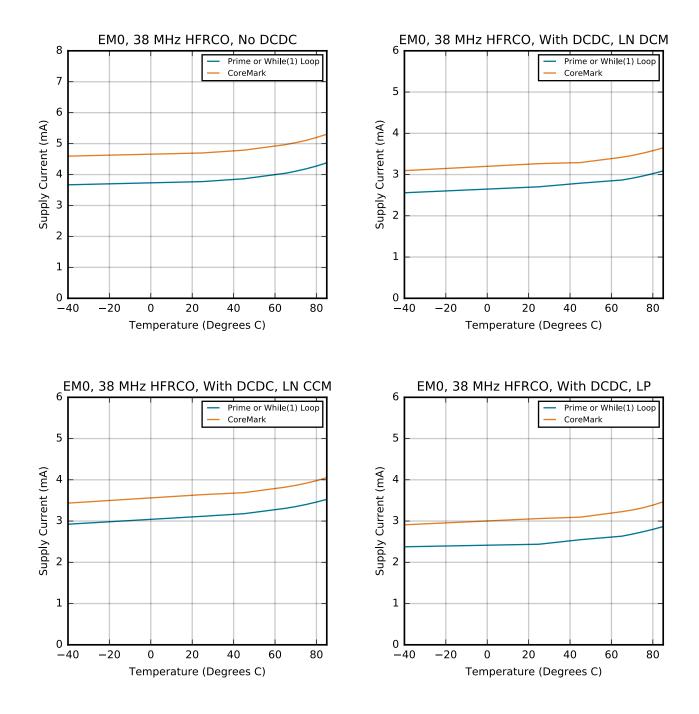

Figure 4.3. EM0 Active Mode Typical Supply Current vs. Temperature

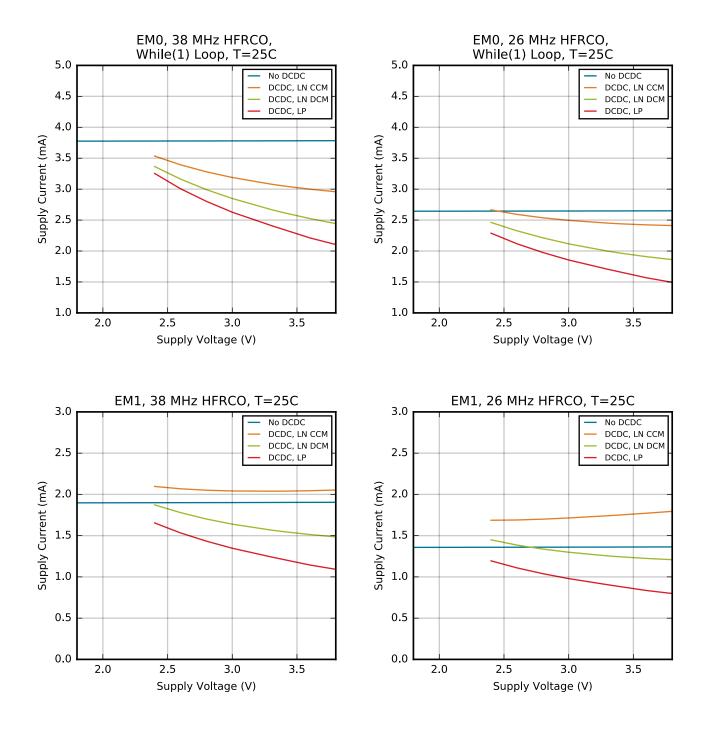

Figure 4.6. EM0 and EM1 Mode Typical Supply Current vs. Supply

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

|       | Pin      |                           | Pin Alternate Funct                                                                                                                                   | ionality / Description                                                                                                                                                                         |                            |

|-------|----------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Pin # | Pin Name | Analog                    | Timers                                                                                                                                                | Communication                                                                                                                                                                                  | Other                      |

| E13   | PB7      | BUSCY BUSDX               | WTIM0_CC0 #11<br>WTIM0_CC1 #9<br>WTIM0_CC2 #7<br>WTIM0_CDTI0 #3<br>WTIM0_CDT11 #1<br>PCNT1_S0IN #7<br>PCNT1_S1IN #6<br>PCNT2_S0IN #7<br>PCNT2_S1IN #6 | US2_TX #10 US2_RX<br>#9 US2_CLK #8<br>US2_CS #7 US2_CTS<br>#6 US2_RTS #5<br>US3_TX #11 US3_RX<br>#10 US3_CLK #9<br>US3_CS #8 US3_CTS<br>#7 US3_RTS #6<br>I2C1_SDA #7<br>I2C1_SCL #6            | ETM_TD2 #2                 |

| F1    | PK2      |                           | PCNT1_S0IN #31<br>PCNT1_S1IN #30<br>PCNT2_S0IN #31<br>PCNT2_S1IN #30                                                                                  | US2_TX #31 US2_RX<br>#30 US2_CLK #29<br>US2_CS #28 US2_CTS<br>#27 US2_RTS #26<br>US3_TX #31 US3_RX<br>#30 US3_CLK #29<br>US3_CS #28 US3_CTS<br>#27 US3_RTS #26<br>I2C1_SDA #31<br>I2C1_SCL #30 |                            |

| F2    | IOVDD    | Digital IO power supply . |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F5    | VSS      | Ground                    |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F6    | VSS      | Ground                    |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F7    | VSS      | Ground                    |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F8    | VSS      | Ground                    |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F9    | VSS      | Ground                    |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F11   | IOVDD    | Digital IO power supply . |                                                                                                                                                       |                                                                                                                                                                                                |                            |

| F12   | PB6      | BUSDY BUSCX               | WTIM0_CC0 #10<br>WTIM0_CC1 #8<br>WTIM0_CC2 #6<br>WTIM0_CDTI0 #2<br>WTIM0_CDT11 #0<br>PCNT1_S0IN #6<br>PCNT1_S1IN #5<br>PCNT2_S0IN #6<br>PCNT2_S1IN #5 | US2_TX #9 US2_RX #8<br>US2_CLK #7 US2_CS<br>#6 US2_CTS #5<br>US2_RTS #4 US3_TX<br>#10 US3_RX #9<br>US3_CLK #8 US3_CS<br>#7 US3_CTS #6<br>US3_RTS #5 I2C1_SDA<br>#6 I2C1_SCL #5                 | CMU_CLKI0 #3<br>ETM_TD1 #2 |

| F13   | PI3      | BUSADC0Y BU-<br>SADC0X    | PCNT1_S0IN #5<br>PCNT1_S1IN #4<br>PCNT2_S0IN #5<br>PCNT2_S1IN #4                                                                                      | US2_TX #8 US2_RX #7<br>US2_CLK #6 US2_CS<br>#5 US2_CTS #4<br>US2_RTS #3 US3_TX<br>#9 US3_RX #8<br>US3_CLK #7 US3_CS<br>#6 US3_CTS #5<br>US3_RTS #4 I2C1_SDA<br>#5 I2C1_SCL #4                  | LES_ALTEX7<br>ETM_TD0 #2   |

|       | Pin      |             | Pin Alternate Functi                                                                                                                                                                                                                                                                                                                                                                                                                                     | onality / Description                                                                                                                                                                                                                                                                                      |                                                                                                            |

|-------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog      | Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Communication                                                                                                                                                                                                                                                                                              | Other                                                                                                      |

| 19    | PD10     | BUSDY BUSCX | TIM0_CC0 #18<br>TIM0_CC1 #17<br>TIM0_CC2 #16<br>TIM0_CDTI0 #15<br>TIM0_CDTI0 #15<br>TIM0_CDTI2 #13<br>TIM1_CC0 #18<br>TIM1_CC1 #17<br>TIM1_CC2 #16<br>TIM1_CC2 #16<br>TIM1_CC3 #15<br>WTIM0_CDTI0 #26<br>WTIM0_CDTI0 #26<br>WTIM0_CDTI1 #24<br>WTIM0_CDTI1 #24<br>WTIM0_CDT12 #22<br>WTIM1_CC0 #18<br>WTIM1_CC1 #16<br>WTIM1_CC2 #14<br>WTIM1_CC3 #12 LE-<br>TIM0_OUT0 #18 LE-<br>TIM0_OUT0 #18 LE-<br>TIM0_OUT1 #17<br>PCNT0_S0IN #18<br>PCNT0_S1IN #17 | US0_TX #18 US0_RX<br>#17 US0_CLK #16<br>US0_CS #15 US0_CTS<br>#14 US0_RTS #13<br>US1_TX #18 US1_RX<br>#17 US1_CLK #16<br>US1_CS #15 US1_CTS<br>#14 US1_RTS #13<br>US3_TX #2 US3_RX #1<br>US3_CLK #0 US3_CS<br>#31 US3_CTS #30<br>US3_RTS #29<br>LEU0_TX #18<br>LEU0_RX #17<br>I2C0_SDA #18<br>I2C0_SCL #17 | CMU_CLK1 #4<br>PRS_CH3 #9 PRS_CH4<br>#1 PRS_CH5 #0<br>PRS_CH6 #12<br>ACMP0_O #18<br>ACMP1_O #18<br>LES_CH2 |

| 20    | PD11     | BUSCY BUSDX | TIM0_CC0 #19<br>TIM0_CC1 #18<br>TIM0_CC2 #17<br>TIM0_CDTI0 #16<br>TIM0_CDTI1 #15<br>TIM0_CDTI2 #14<br>TIM1_CC0 #19<br>TIM1_CC1 #18<br>TIM1_CC2 #17<br>TIM1_CC3 #16<br>WTIM0_CDTI0 #27<br>WTIM0_CDTI0 #27<br>WTIM0_CDTI1 #25<br>WTIM0_CDTI1 #25<br>WTIM0_CDTI2 #23<br>WTIM1_CC0 #19<br>WTIM1_CC1 #17<br>WTIM1_CC2 #15<br>WTIM1_CC3 #13 LE-<br>TIM0_OUT0 #19 LE-<br>TIM0_OUT1 #18<br>PCNT0_S0IN #19<br>PCNT0_S1IN #18                                      | US0_TX #19 US0_RX<br>#18 US0_CLK #17<br>US0_CS #16 US0_CTS<br>#15 US0_RTS #14<br>US1_TX #19 US1_RX<br>#18 US1_CLK #17<br>US1_CS #16 US1_CTS<br>#15 US1_RTS #14<br>US3_TX #3 US3_RX #2<br>US3_CLK #1 US3_CS<br>#0 US3_CTS #31<br>US3_RTS #30<br>LEU0_TX #19<br>LEU0_RX #18<br>I2C0_SDA #19<br>I2C0_SCL #18  | PRS_CH3 #10<br>PRS_CH4 #2 PRS_CH5<br>#1 PRS_CH6 #13<br>ACMP0_O #19<br>ACMP1_O #19<br>LES_CH3               |

|       | Pin      |                                                            | Pin Alternate Functi                                                                                                                                                                                                                                                                       | onality / Description                                                                                                                                                                                             |                                                                                                          |

|-------|----------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog                                                     | Timers                                                                                                                                                                                                                                                                                     | Communication                                                                                                                                                                                                     | Other                                                                                                    |

| 26    | PA1      | BUSCY BUSDX<br>ADC0_EXTP<br>VDAC0_EXT                      | TIM0_CC0 #1<br>TIM0_CC1 #0<br>TIM0_CC2 #31<br>TIM0_CDTI0 #30<br>TIM0_CDTI1 #29<br>TIM0_CDTI2 #28<br>TIM1_CC0 #1<br>TIM1_CC1 #0<br>TIM1_CC2 #31<br>TIM1_CC3 #30<br>WTIM0_CC0 #1 LE-<br>TIM0_OUT0 #1 LE-<br>TIM0_OUT0 #1 LE-<br>TIM0_OUT1 #0<br>PCNT0_S0IN #1<br>PCNT0_S1IN #0               | US0_TX #1 US0_RX #0<br>US0_CLK #31 US0_CS<br>#30 US0_CTS #29<br>US0_RTS #28 US1_TX<br>#1 US1_RX #0<br>US1_CLK #31 US1_CS<br>#30 US1_CTS #29<br>US1_RTS #28<br>LEU0_TX #1 LEU0_RX<br>#0 I2C0_SDA #1<br>I2C0_SCL #0 | CMU_CLK0 #0<br>PRS_CH6 #1 PRS_CH7<br>#0 PRS_CH8 #10<br>PRS_CH9 #9<br>ACMP0_O #1<br>ACMP1_O #1 LES_CH9    |

| 27    | PA2      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1<br>BUSDY BUSCX<br>OPA0_P | TIM0_CC0 #2<br>TIM0_CC1 #1<br>TIM0_CC2 #0<br>TIM0_CDTI0 #31<br>TIM0_CDTI1 #30<br>TIM0_CDTI2 #29<br>TIM1_CC0 #2<br>TIM1_CC1 #1<br>TIM1_CC2 #0<br>TIM1_CC3 #31<br>WTIM0_CC0 #2<br>WTIM0_CC1 #0 LE-<br>TIM0_OUT0 #2 LE-<br>TIM0_OUT0 #2 LE-<br>TIM0_OUT1 #1<br>PCNT0_S0IN #2<br>PCNT0_S1IN #1 | US0_TX #2 US0_RX #1<br>US0_CLK #0 US0_CS<br>#31 US0_CTS #30<br>US0_RTS #29 US1_TX<br>#2 US1_RX #1<br>US1_CLK #0 US1_CS<br>#31 US1_CTS #30<br>US1_RTS #29<br>LEU0_TX #2 LEU0_RX<br>#1 I2C0_SDA #2<br>I2C0_SCL #1   | PRS_CH6 #2 PRS_CH7<br>#1 PRS_CH8 #0<br>PRS_CH9 #10<br>ACMP0_O #2<br>ACMP1_O #2<br>LES_CH10               |

| 28    | PA3      | BUSCY BUSDX<br>VDAC0_OUT0 /<br>OPA0_OUT                    | TIM0_CC0 #3<br>TIM0_CC1 #2<br>TIM0_CC2 #1<br>TIM0_CDTI0 #0<br>TIM0_CDTI1 #31<br>TIM0_CDTI2 #30<br>TIM1_CC0 #3<br>TIM1_CC1 #2<br>TIM1_CC3 #0<br>WTIM0_CC0 #3<br>WTIM0_CC0 #3<br>WTIM0_CC1 #1 LE-<br>TIM0_OUT0 #3 LE-<br>TIM0_OUT1 #2<br>PCNT0_S0IN #3<br>PCNT0_S1IN #2                      | US0_TX #3 US0_RX #2<br>US0_CLK #1 US0_CS<br>#0 US0_CTS #31<br>US0_RTS #30 US1_TX<br>#3 US1_RX #2<br>US1_CLK #1 US1_CS<br>#0 US1_CTS #31<br>US1_RTS #30<br>LEU0_TX #3 LEU0_RX<br>#2 I2C0_SDA #3<br>I2C0_SCL #2     | PRS_CH6 #3 PRS_CH7<br>#2 PRS_CH8 #1<br>PRS_CH9 #0<br>ACMP0_O #3<br>ACMP1_O #3<br>LES_CH11<br>GPIO_EM4WU8 |

## EFM32PG12 Family Data Sheet Pin Definitions

|       | Pin      |                                                            | Pin Alternate Functi                                                                                                                                                                                                                                                                                                                     | onality / Description                                                                                                                                                                                                                                                                      |                                                                                                                          |

|-------|----------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Pin # | Pin Name | Analog                                                     | Timers                                                                                                                                                                                                                                                                                                                                   | Communication                                                                                                                                                                                                                                                                              | Other                                                                                                                    |

| 29    | PA4      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2<br>BUSDY BUSCX<br>OPA0_N | TIM0_CC0 #4<br>TIM0_CC1 #3<br>TIM0_CC2 #2<br>TIM0_CDTI0 #1<br>TIM0_CDTI1 #0<br>TIM0_CDTI2 #31<br>TIM1_CC0 #4<br>TIM1_CC1 #3<br>TIM1_CC2 #2<br>TIM1_CC3 #1<br>WTIM0_CC0 #4<br>WTIM0_CC1 #2<br>WTIM0_CC2 #0 LE-<br>TIM0_OUT0 #4 LE-<br>TIM0_OUT1 #3<br>PCNT0_S0IN #4<br>PCNT0_S1IN #3                                                      | US0_TX #4 US0_RX #3<br>US0_CLK #2 US0_CS<br>#1 US0_CTS #0<br>US0_RTS #31 US1_TX<br>#4 US1_RX #3<br>US1_CLK #2 US1_CS<br>#1 US1_CTS #0<br>US1_RTS #31<br>LEU0_TX #4 LEU0_RX<br>#3 I2C0_SDA #4<br>I2C0_SCL #3                                                                                | PRS_CH6 #4 PRS_CH7<br>#3 PRS_CH8 #2<br>PRS_CH9 #1<br>ACMP0_O #4<br>ACMP1_O #4<br>LES_CH12                                |

| 30    | PA5      | VDAC0_OUT0ALT /<br>OPA0_OUTALT #0<br>BUSCY BUSDX           | TIM0_CC0 #5<br>TIM0_CC1 #4<br>TIM0_CC2 #3<br>TIM0_CDTI0 #2<br>TIM0_CDTI1 #1<br>TIM0_CDTI2 #0<br>TIM1_CC0 #5<br>TIM1_CC1 #4<br>TIM1_CC2 #3<br>TIM1_CC3 #2<br>WTIM0_CC0 #5<br>WTIM0_CC1 #3<br>WTIM0_CC2 #1 LE-<br>TIM0_OUT0 #5 LE-<br>TIM0_OUT1 #4<br>PCNT0_SOIN #5<br>PCNT0_S1IN #4                                                       | US0_TX #5 US0_RX #4<br>US0_CLK #3 US0_CS<br>#2 US0_CTS #1<br>US0_RTS #0 US1_TX<br>#5 US1_RX #4<br>US1_CLK #3 US1_CS<br>#2 US1_CTS #1<br>US1_RTS #0 US2_TX<br>#0 US2_RX #31<br>US2_CLK #30 US2_CS<br>#29 US2_CTS #28<br>US2_RTS #27<br>LEU0_TX #5 LEU0_RX<br>#4 I2C0_SDA #5<br>I2C0_SCL #4  | CMU_CLKI0 #4<br>PRS_CH6 #5 PRS_CH7<br>#4 PRS_CH8 #3<br>PRS_CH9 #2<br>ACMP0_O #5<br>ACMP1_O #5<br>LES_CH13 ETM_TCLK<br>#1 |

| 31    | PB11     | BUSCY BUSDX<br>OPA2_P                                      | TIM0_CC0 #6<br>TIM0_CC1 #5<br>TIM0_CC2 #4<br>TIM0_CDTI0 #3<br>TIM0_CDTI1 #2<br>TIM0_CDTI2 #1<br>TIM1_CC0 #6<br>TIM1_CC1 #5<br>TIM1_CC2 #4<br>TIM1_CC3 #3<br>WTIM0_CC0 #15<br>WTIM0_CC1 #13<br>WTIM0_CC1 #13<br>WTIM0_CC1 #13<br>WTIM0_CDT10 #7<br>WTIM0_CDT10 #7<br>WTIM0_CDT12 #3 LE-<br>TIM0_OUT1 #5<br>PCNT0_S0IN #6<br>PCNT0_S0IN #5 | US0_TX #6 US0_RX #5<br>US0_CLK #4 US0_CS<br>#3 US0_CTS #2<br>US0_RTS #1 US1_TX<br>#6 US1_RX #5<br>US1_CLK #4 US1_CS<br>#3 US1_CTS #2<br>US1_RTS #1 US3_TX<br>#15 US3_RX #14<br>US3_CLK #13 US3_CS<br>#12 US3_CTS #11<br>US3_RTS #10<br>LEU0_TX #6 LEU0_RX<br>#5 I2C0_SDA #6<br>I2C0_SCL #5 | PRS_CH6 #6 PRS_CH7<br>#5 PRS_CH8 #4<br>PRS_CH9 #3<br>ACMP0_O #6<br>ACMP1_O #6                                            |

| Alternate     |         |       |        |         |         |         |         |         |                                    |

|---------------|---------|-------|--------|---------|---------|---------|---------|---------|------------------------------------|

| Functionality | 0 - 3   | 4 - 7 | 8 - 11 | 12 - 15 | 16 - 19 | 20 - 23 | 24 - 27 | 28 - 31 | Description                        |

| LES_ALTEX0    | 0: PA8  |       |        |         |         |         |         |         | LESENSE alternate excite output 0. |

| LES_ALTEX1    | 0: PA9  |       |        |         |         |         |         |         | LESENSE alternate excite output 1. |

| LES_ALTEX2    | 0: PJ14 |       |        |         |         |         |         |         | LESENSE alternate excite output 2. |

| LES_ALTEX3    | 0: PJ15 |       |        |         |         |         |         |         | LESENSE alternate excite output 3. |

| LES_ALTEX4    | 0: PI0  |       |        |         |         |         |         |         | LESENSE alternate excite output 4. |

| LES_ALTEX5    | 0: PI1  |       |        |         |         |         |         |         | LESENSE alternate excite output 5. |

| LES_ALTEX6    | 0: PI2  |       |        |         |         |         |         |         | LESENSE alternate excite output 6. |

| LES_ALTEX7    | 0: PI3  |       |        |         |         |         |         |         | LESENSE alternate excite output 7. |

| LES_CH0       | 0: PD8  |       |        |         |         |         |         |         | LESENSE channel<br>0.              |

| LES_CH1       | 0: PD9  |       |        |         |         |         |         |         | LESENSE channel<br>1.              |

| LES_CH2       | 0: PD10 |       |        |         |         |         |         |         | LESENSE channel<br>2.              |

| LES_CH3       | 0: PD11 |       |        |         |         |         |         |         | LESENSE channel<br>3.              |

| LES_CH4       | 0: PD12 |       |        |         |         |         |         |         | LESENSE channel<br>4.              |

| Alternate     |                                      |                                         |                                           | LOC                                        | ATION                                       |                                              |                                          |                                          |                                                                                                                                     |

|---------------|--------------------------------------|-----------------------------------------|-------------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                | 4 - 7                                   | 8 - 11                                    | 12 - 15                                    | 16 - 19                                     | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                                                                                         |

| LEU0_RX       | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | LEUART0 Receive input.                                                                                                              |

| LEU0_TX       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | LEUART0 Transmit<br>output. Also used<br>as receive input in<br>half duplex commu-<br>nication.                                     |

| LFXTAL_N      | 0: PB14                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Low Frequency<br>Crystal (typically<br>32.768 kHz) nega-<br>tive pin. Also used<br>as an optional ex-<br>ternal clock input<br>pin. |

| LFXTAL_P      | 0: PB15                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Low Frequency<br>Crystal (typically<br>32.768 kHz) posi-<br>tive pin.                                                               |

| OPA0_N        | 0: PA4                               |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 0 external nega-<br>tive input.                                                                          |

| OPA0_P        | 0: PA2                               |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 0 external posi-<br>tive input.                                                                          |

| OPA1_N        | 0: PD15                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 1 external nega-<br>tive input.                                                                          |

| OPA1_P        | 0: PD13                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 1 external posi-<br>tive input.                                                                          |

| OPA2_N        | 0: PB13                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 2 external nega-<br>tive input.                                                                          |

| OPA2_OUT      | 0: PB12                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifier 2 output.                                                                                                     |

| OPA2_OUTALT   | 0: PB9<br>1: PB10                    |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 2 alternative out-<br>put.                                                                               |

| OPA2_P        | 0: PB11                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Operational Amplifi-<br>er 2 external posi-<br>tive input.                                                                          |

| Alternate     |                                                    |                                         |                                           |                                              |                                             |                                                                |                                              |                                           |                                                  |

|---------------|----------------------------------------------------|-----------------------------------------|-------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------------------------|----------------------------------------------|-------------------------------------------|--------------------------------------------------|

| Functionality | 0 - 3                                              | 4 - 7                                   | 8 - 11                                    | 12 - 15                                      | 16 - 19                                     | 20 - 23                                                        | 24 - 27                                      | 28 - 31                                   | Description                                      |

| PCNT0_S0IN    | 0: PA04: PA41: PA15: PA52: PA26: PB113: PA37: PB12 |                                         | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10    | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15                   | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3     | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7  | Pulse Counter<br>PCNT0 input num-<br>ber 0.      |

| PCNT0_S1IN    | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4               | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11   | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0                    | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4     | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0  | Pulse Counter<br>PCNT0 input num-<br>ber 1.      |

| PCNT1_S0IN    | 0: PA6<br>1: PA7<br>2: PA8<br>3: PA9               | 4: PI2<br>5: PI3<br>6: PB6<br>7: PB7    | 8: PB8<br>9: PB9<br>10: PB10<br>11: PJ14  | 12: PJ15<br>13: PC0<br>14: PC1<br>15: PC2    | 16: PC3<br>17: PC4<br>18: PC5<br>19: PF6    | 20: PF7<br>21: PF8<br>22: PF9<br>23: PF10                      | 24: PF11<br>25: PF12<br>26: PF13<br>27: PF14 | 28: PF15<br>29: PK0<br>30: PK1<br>31: PK2 | Pulse Counter<br>PCNT1 input num-<br>ber 0.      |

| PCNT1_S1IN    | 0: PA7<br>1: PA8<br>2: PA9<br>3: Pl2               | 4: PI3<br>5: PB6<br>6: PB7<br>7: PB8    | 8: PB9<br>9: PB10<br>10: PJ14<br>11: PJ15 | 12: PC0<br>13: PC1<br>14: PC2<br>15: PC3     | 16: PC4<br>17: PC5<br>18: PF6<br>19: PF7    | 20: PF8<br>21: PF9<br>22: PF10<br>23: PF11                     | 24: PF12<br>25: PF13<br>26: PF14<br>27: PF15 | 28: PK0<br>29: PK1<br>30: PK2<br>31: PA6  | Pulse Counter<br>PCNT1 input num-<br>ber 1.      |

| PCNT2_S0IN    | 0: PA6<br>1: PA7<br>2: PA8<br>3: PA9               | 4: PI2<br>5: PI3<br>6: PB6<br>7: PB7    | 8: PB8<br>9: PB9<br>10: PB10<br>11: PJ14  | 12: PJ15<br>13: PC0<br>14: PC1<br>15: PC2    | 16: PC3<br>17: PC4<br>18: PC5<br>19: PC10   | 20: PC11<br>21: PF8<br>22: PF9<br>23: PF10                     | 24: PF11<br>25: PF12<br>26: PF13<br>27: PF14 | 28: PF15<br>29: PK0<br>30: PK1<br>31: PK2 | Pulse Counter<br>PCNT2 input num-<br>ber 0.      |

| PCNT2_S1IN    | 0: PA7<br>1: PA8<br>2: PA9<br>3: Pl2               | 4: PI3<br>5: PB6<br>6: PB7<br>7: PB8    | 8: PB9<br>9: PB10<br>10: PJ14<br>11: PJ15 | 12: PC0<br>13: PC1<br>14: PC2<br>15: PC3     | 16: PC4<br>17: PC5<br>18: PC10<br>19: PC11  | 20: PF824: PF1221: PF925: PF1322: PF1026: PF1423: PF1127: PF15 |                                              | 28: PK0<br>29: PK1<br>30: PK2<br>31: PA6  | Pulse Counter<br>PCNT2 input num-<br>ber 1.      |

| PRS_CH0       | 0: PF0<br>1: PF1<br>2: PF2<br>3: PF3               | 4: PF4<br>5: PF5<br>6: PF6<br>7: PF7    | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11                         |                                             |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 0. |

| PRS_CH1       | 0: PF1<br>1: PF2<br>2: PF3<br>3: PF4               | 4: PF5<br>5: PF6<br>6: PF7<br>7: PF0    |                                           |                                              |                                             |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 1. |

| PRS_CH2       | 0: PF2<br>1: PF3<br>2: PF4<br>3: PF5               | 4: PF6<br>5: PF7<br>6: PF0<br>7: PF1    |                                           |                                              |                                             |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 2. |

| PRS_CH3       | 0: PF3<br>1: PF4<br>2: PF5<br>3: PF6               | 4: PF7<br>5: PF0<br>6: PF1<br>7: PF2    | 8: PD9<br>9: PD10<br>10: PD11<br>11: PD12 | 12: PD13<br>13: PD14<br>14: PD15             |                                             |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 3. |

| PRS_CH4       | 0: PD9<br>1: PD10<br>2: PD11<br>3: PD12            | 4: PD13<br>5: PD14<br>6: PD15           |                                           |                                              |                                             |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 4. |

| PRS_CH5       | 0: PD10<br>1: PD11<br>2: PD12<br>3: PD13           | 4: PD14<br>5: PD15<br>6: PD9            |                                           |                                              |                                             |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 5. |

| PRS_CH6       | 0: PA0 4: PA4<br>1: PA1 5: PA5<br>2: PA2 6: PB11   |                                         | 8: PB13<br>9: PB14<br>10: PB15<br>11: PD9 | 12: PD10<br>13: PD11<br>14: PD12<br>15: PD13 | 16: PD14<br>17: PD15                        |                                                                |                                              |                                           | Peripheral Reflex<br>System PRS, chan-<br>nel 6. |

| Alternate     |                                         |                                                     |                                           |                                             |                                              |                                              |                                          |                                          |                                                                                                                                                                                    |

|---------------|-----------------------------------------|-----------------------------------------------------|-------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                   | 4 - 7                                               | 8 - 11                                    | 12 - 15                                     | 16 - 19                                      | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                                                                                                                                        |

| TIM1_CC2      | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14            | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | Timer 1 Capture<br>Compare input /<br>output channel 2.                                                                                                                            |

| TIM1_CC3      | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15            | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | Timer 1 Capture<br>Compare input /<br>output channel 3.                                                                                                                            |

| US0_CLK       | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14            | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | USART0 clock in-<br>put / output.                                                                                                                                                  |

| US0_CS        | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15            | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | USART0 chip se-<br>lect input / output.                                                                                                                                            |

| US0_CTS       | 0: PA4<br>1: PA5<br>2: PB11<br>3: PB12  | 4: PB13<br>5: PB14<br>6: PB15<br>7: PC6             | 8: PC7<br>9: PC8<br>10: PC9<br>11: PC10   | 12: PC11<br>13: PD9<br>14: PD10<br>15: PD11 | 16: PD12<br>17: PD13<br>18: PD14<br>19: PD15 | 20: PF0<br>21: PF1<br>22: PF2<br>23: PF3     | 24: PF4<br>25: PF5<br>26: PF6<br>27: PF7 | 28: PA0<br>29: PA1<br>30: PA2<br>31: PA3 | USART0 Clear To<br>Send hardware<br>flow control input.                                                                                                                            |

| US0_RTS       | 0: PA5<br>1: PB11<br>2: PB12<br>3: PB13 | 0: PA5 4: PB14<br>1: PB11 5: PB15<br>2: PB12 6: PC6 |                                           | 12: PD9<br>13: PD10<br>14: PD11<br>15: PD12 | 16: PD13<br>17: PD14<br>18: PD15<br>19: PF0  | 20: PF1<br>21: PF2<br>22: PF3<br>23: PF4     | 24: PF5<br>25: PF6<br>26: PF7<br>27: PA0 | 28: PA1<br>29: PA2<br>30: PA3<br>31: PA4 | USART0 Request<br>To Send hardware<br>flow control output.                                                                                                                         |

| US0_RX        | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4    | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13             | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11  | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12  | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | USART0 Asynchro-<br>nous Receive.<br>USART0 Synchro-<br>nous mode Master<br>Input / Slave Out-<br>put (MISO).                                                                      |

| US0_TX        | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3    | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12              | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10   | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11  | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | USART0 Asynchro-<br>nous Transmit. Al-<br>so used as receive<br>input in half duplex<br>communication.<br>USART0 Synchro-<br>nous mode Master<br>Output / Slave In-<br>put (MOSI). |

| US1_CLK       | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14            | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | USART1 clock in-<br>put / output.                                                                                                                                                  |

| US1_CS        | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15            | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | USART1 chip se-<br>lect input / output.                                                                                                                                            |

| US1_CTS       | 0: PA4<br>1: PA5<br>2: PB11<br>3: PB12  | 4: PB13<br>5: PB14<br>6: PB15<br>7: PC6             | 8: PC7<br>9: PC8<br>10: PC9<br>11: PC10   | 12: PC11<br>13: PD9<br>14: PD10<br>15: PD11 | 16: PD12<br>17: PD13<br>18: PD14<br>19: PD15 | 20: PF0<br>21: PF1<br>22: PF2<br>23: PF3     | 24: PF4<br>25: PF5<br>26: PF6<br>27: PF7 | 28: PA0<br>29: PA1<br>30: PA2<br>31: PA3 | USART1 Clear To<br>Send hardware<br>flow control input.                                                                                                                            |

## EFM32PG12 Family Data Sheet Pin Definitions

| Port    | Bus                   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

|---------|-----------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| VD      | VDAC0_OUT1 / OPA1_OUT |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |      |      |      |     |     |

| APORT1Y | BUSAY                 | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      | PC5  |      | PC3  |      | PC1 |     |

| APORT2Y | BUSBY                 |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | PC6  |      | PC4  |      | PC2  |     | PC0 |

| APORT3Y | BUSCY                 | PB15 |      | PB13 |      | PB11 |      | PB9  |      | PB7  |      |      |      |      |      |      |      | PA7  |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4Y | BUSDY                 |      | PB14 |      | PB12 |      | PB10 |      | PB8  |      | PB6  |      |      |      |      |      |      |      | PA6  |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     | PD8 |

### 7.2 BGA125 PCB Land Pattern

Figure 7.2. BGA125 PCB Land Pattern Drawing

Figure 8.3. QFN48 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.