Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 36MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 768KB (768K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 80K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101rft6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.   | STM32F101xF and STM32F101xG access line block diagram                          | 12 |

|-------------|--------------------------------------------------------------------------------|----|

| Figure 2.   | Clock tree                                                                     | 13 |

| Figure 3.   | LQFP144 pinout                                                                 | 23 |

| Figure 4.   | LQFP100 pinout                                                                 | 24 |

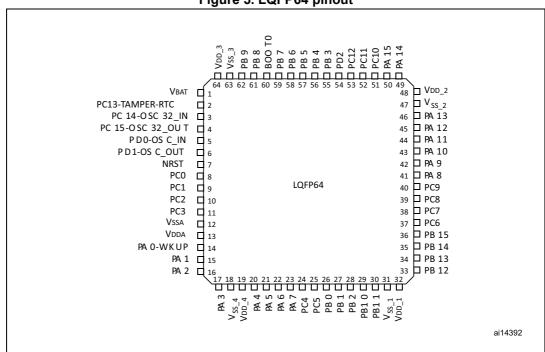

| Figure 5.   | LQFP64 pinout                                                                  | 25 |

| Figure 6.   | Memory map                                                                     | 34 |

| Figure 7.   | Pin loading conditions                                                         | 36 |

| Figure 8.   | Pin input voltage                                                              | 36 |

| Figure 9.   | Power supply scheme.                                                           | 36 |

| Figure 10.  | Current consumption measurement scheme                                         |    |

| Figure 11.  | Typical current consumption in Run mode versus frequency (at 3.6 V) -          |    |

| 0           | code with data processing running from RAM, peripherals enabled.               | 43 |

| Figure 12.  | Typical current consumption in Run mode versus frequency (at 3.6 V) -          |    |

| -           | code with data processing running from RAM, peripherals disabled               | 43 |

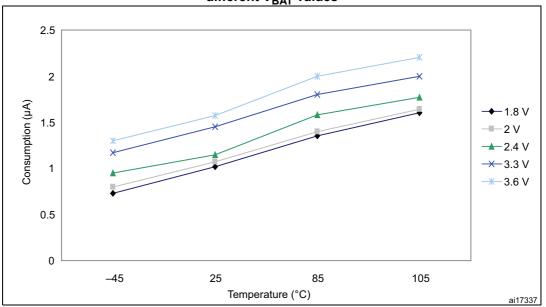

| Figure 13.  | Typical current consumption on V <sub>BAT</sub> with RTC on vs. temperature at |    |

| U           | different V <sub>BAT</sub> values                                              | 45 |

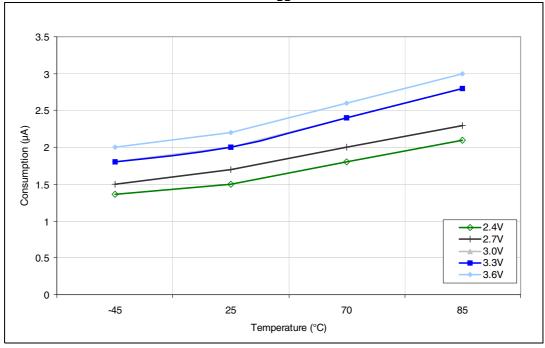

| Figure 14.  | Typical current consumption in Standby mode versus temperature at              |    |

| U           | different V <sub>DD</sub> values                                               | 45 |

| Figure 15.  | High-speed external clock source AC timing diagram                             | 51 |

| Figure 16.  | Low-speed external clock source AC timing diagram                              | 51 |

| Figure 17.  | Typical application with an 8 MHz crystal                                      |    |

| Figure 18.  | Typical application with a 32.768 kHz crystal                                  |    |

| Figure 19.  | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                     |    |

| Figure 20.  | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                    |    |

| Figure 21.  | Asynchronous multiplexed NOR/PSRAM read waveforms.                             |    |

| Figure 22.  | Asynchronous multiplexed NOR/PSRAM write waveforms                             |    |

| Figure 23.  | Synchronous multiplexed NOR/PSRAM read timings                                 |    |

| Figure 24.  | Synchronous multiplexed PSRAM write timings                                    |    |

| Figure 25.  | Synchronous non-multiplexed NOR/PSRAM read timings                             |    |

| Figure 26.  | Synchronous non-multiplexed PSRAM write timings                                |    |

| Figure 27.  | PC Card/CompactFlash controller waveforms for common memory read access        |    |

| Figure 28.  | PC Card/CompactFlash controller waveforms for common memory write access       |    |

| Figure 29.  | PC Card/CompactFlash controller waveforms for attribute memory read            |    |

|             | access                                                                         | 71 |

| Figure 30.  | PC Card/CompactFlash controller waveforms for attribute memory write           |    |

|             | access                                                                         | 72 |

| Figure 31.  | PC Card/CompactFlash controller waveforms for I/O space read access            |    |

| Figure 32.  | PC Card/CompactFlash controller waveforms for I/O space write access           |    |

| Figure 33.  | NAND controller waveforms for read access                                      |    |

| Figure 34.  | NAND controller waveforms for write access                                     |    |

| Figure 35.  | NAND controller waveforms for common memory read access                        |    |

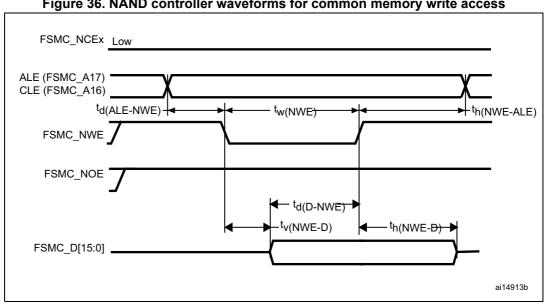

| Figure 36.  | NAND controller waveforms for common memory write access                       |    |

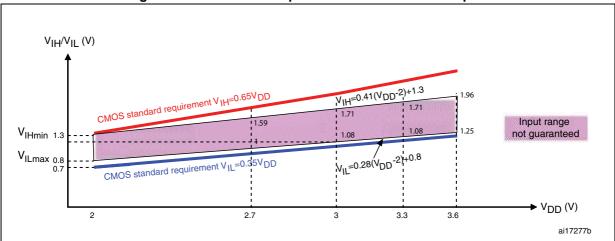

| Figure 37.  | Standard I/O input characteristics - CMOS port                                 |    |

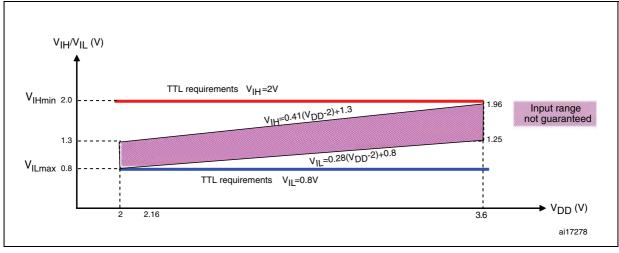

| Figure 38.  | Standard I/O input characteristics - TTL port                                  |    |

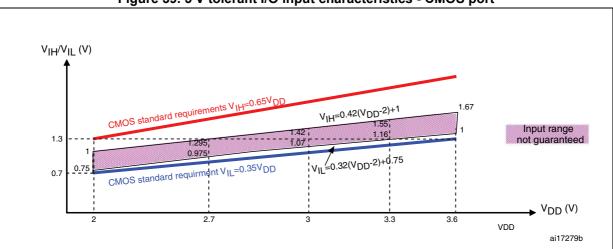

| Figure 39.  | 5 V tolerant I/O input characteristics - CMOS port                             |    |

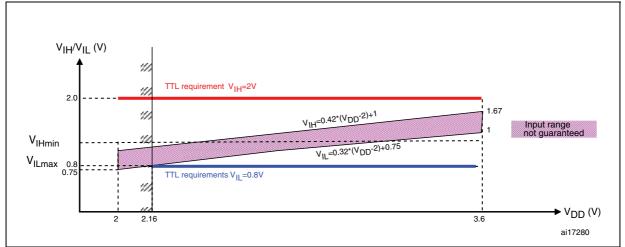

| Figure 40.  | 5 V tolerant I/O input characteristics - TTL port                              |    |

| Figure 41.  | I/O AC characteristics definition                                              |    |

| Figure 42.  | Recommended NRST pin protection                                                |    |

| . iguio 42. |                                                                                | 00 |

# 2.1 Device overview

The STM32F101xx XL-density access line family offers devices in 3 different package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

*Figure 1* shows the general block diagram of the device family.

| Perij                    | pherals                                                                                                                  | STM32  | =101Rx | STM32F101Vx |                    | STM32F101Zx |      |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|--------|-------------|--------------------|-------------|------|--|

| Flash memory             |                                                                                                                          | 768 KB | 1 MB   | 768 KB      | 1 MB               | 768 KB      | 1 MB |  |

| SRAM in Kbytes           |                                                                                                                          | 80     |        | 80          |                    | 8           | 0    |  |

| FSMC                     |                                                                                                                          | N      | 0      | Yes Yes     |                    |             | es   |  |

| General-purpose          |                                                                                                                          |        |        | 1           | 0                  | •           |      |  |

| Timers                   | Basic                                                                                                                    |        |        | 2           | 2                  |             |      |  |

|                          | SPI                                                                                                                      |        |        | 3           | 3                  |             |      |  |

| Communication interfaces | I <sup>2</sup> C                                                                                                         | 2      |        |             |                    |             |      |  |

|                          | USART                                                                                                                    | 5      |        |             |                    |             |      |  |

| GPIOs                    | •                                                                                                                        | 5      | 1      | 8           | 0                  | 11          | 2    |  |

| 12-bit ADC               |                                                                                                                          | 1      |        |             |                    |             |      |  |

| Number of chann          | nels                                                                                                                     | 16     |        |             |                    |             |      |  |

| 12-bit DAC               |                                                                                                                          | YES    |        |             |                    |             |      |  |

| Number of chann          | nels                                                                                                                     | 2      |        |             |                    |             |      |  |

| CPU frequency            |                                                                                                                          | 36 MHz |        |             |                    |             |      |  |

| Operating voltag         | 2.0 to 3.6 V                                                                                                             |        |        |             |                    |             |      |  |

| Operating tempe          | Ambient temperature: -40 to +85 °C (see <i>Table 10</i> )<br>Junction temperature: -40 to +105 °C (see <i>Table 10</i> ) |        |        |             |                    |             |      |  |

| Package                  |                                                                                                                          | LQF    | P64    | LQFP        | 100 <sup>(1)</sup> | LQFF        | P144 |  |

For the LQFP100 package, only FSMC Bank1 and Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

# 2.3.10 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers are used to configure the AHB frequency, the high-speed APB (APB2) domain and the low-speed APB (APB1) domain. The maximum frequency of the AHB and APB domains is 36 MHz. See *Figure 2* for details on the clock tree.

# 2.3.11 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash memory bank 2 by setting a bit in the option bytes.

- Boot from system memory

- Boot from embedded SRAM

The bootloader is located in system memory. It is used to reprogram the Flash memory by using USART1.

# 2.3.12 Power supply schemes

- V<sub>DD</sub> = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to Figure 9: Power supply scheme.

# 2.3.13 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

Figure 5. LQFP64 pinout

1. The above figure shows the package top view.

|         | Pins   |         |                                |                     |                            |                                                  | Alternate funct     | ions <sup>(4)</sup> |

|---------|--------|---------|--------------------------------|---------------------|----------------------------|--------------------------------------------------|---------------------|---------------------|

| LQFP144 | LQFP64 | LQFP100 | Pin name                       | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default             | Remap               |

| 1       | -      | 1       | PE2                            | I/O                 | FT                         | PE2                                              | TRACECLK / FSMC_A23 | -                   |

| 2       | -      | 2       | PE3                            | I/O                 | FT                         | PE3                                              | TRACED0 / FSMC_A19  | -                   |

| 3       | -      | 3       | PE4                            | I/O                 | FT                         | PE4                                              | TRACED1 / FSMC_A20  | -                   |

| 4       | -      | 4       | PE5                            | I/O                 | FT                         | PE5                                              | TRACED2 / FSMC_A21  | TIM9_CH1            |

| 5       | -      | 5       | PE6                            | I/O                 | FT                         | PE6                                              | TRACED3 / FSMC_A22  | TIM9_CH2            |

| 6       | 1      | 6       | V <sub>BAT</sub>               | S                   | -                          | V <sub>BAT</sub>                                 | -                   | -                   |

| 7       | 2      | 7       | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                          | PC13 <sup>(6)</sup>                              | TAMPER-RTC          | -                   |

| 8       | 3      | 8       | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                          | PC14 <sup>(6)</sup>                              | OSC32_IN            | -                   |

| 9       | 4      | 9       | PC15-OSC32_OUT <sup>(5)</sup>  | I/O                 | -                          | PC15 <sup>(6)</sup>                              | OSC32_OUT           | -                   |

| 10      | -      | -       | PF0                            | I/O                 | FT                         | PF0                                              | FSMC_A0             | -                   |

| 11      | -      | -       | PF1                            | I/O                 | FT                         | PF1                                              | FSMC_A1             | -                   |

#### Table 5. STM32F101xF/STM32F101xG pin definitions

|         | Pins   |         |                   |                     |                            |                                                  | Alternate funct                                                                        | -     |

|---------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|-------|

| LQFP144 | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | l / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                | Remap |

| 37      | 17     | 26      | PA3               | I/O                 | -                          | PA3                                              | USART2_RX <sup>(8)</sup> /TIM5_CH4/<br>ADC_IN3 / TIM2_CH4 <sup>(8)</sup> /<br>TIM9_CH2 | -     |

| 38      | 18     | 27      | V <sub>SS_4</sub> | S                   | -                          | V <sub>SS_4</sub>                                | -                                                                                      | -     |

| 39      | 19     | 28      | V <sub>DD_4</sub> | S                   | -                          | V <sub>DD_4</sub>                                | -                                                                                      | -     |

| 40      | 20     | 29      | PA4               | I/O                 | -                          | PA4                                              | SPI1_NSS/ DAC_OUT1 /<br>ADC_IN4 / USART2_CK <sup>(8)</sup>                             | -     |

| 41      | 21     | 30      | PA5               | I/O                 | -                          | PA5                                              | SPI1_SCK / DAC_OUT2 /<br>ADC_IN5                                                       | -     |

| 42      | 22     | 31      | PA6               | I/O                 | -                          | PA6                                              | SPI1_MISO / ADC_IN6 /<br>TIM3_CH1 <sup>(8)</sup> / TIM13_CH1                           | -     |

| 43      | 23     | 32      | PA7               | I/O                 | -                          | PA7                                              | SPI1_MOSI / ADC_IN7 /<br>TIM3_CH2 <sup>(8)</sup> / TIM14_CH1                           | -     |

| 44      | 24     | 33      | PC4               | I/O                 | -                          | PC4                                              | ADC_IN14                                                                               | -     |

| 45      | 25     | 34      | PC5               | I/O                 | -                          | PC5                                              | ADC_IN15                                                                               | -     |

| 46      | 26     | 35      | PB0               | I/O                 | -                          | PB0                                              | ADC_IN8 / TIM3_CH3 <sup>(8)</sup>                                                      | -     |

| 47      | 27     | 36      | PB1               | I/O                 | -                          | PB1                                              | ADC_IN9 / TIM3_CH4 <sup>(8)</sup>                                                      | -     |

| 48      | 28     | 37      | PB2               | I/O                 | FT                         | PB2/BOOT1                                        | -                                                                                      | -     |

| 49      | -      | -       | PF11              | I/O                 | FT                         | PF11                                             | FSMC_NIOS16                                                                            | -     |

| 50      | -      | -       | PF12              | I/O                 | FT                         | PF12                                             | FSMC_A6                                                                                | _     |

| 51      | -      | -       | V <sub>SS_6</sub> | S                   | -                          | V <sub>SS_6</sub>                                | -                                                                                      | -     |

| 52      | -      | -       | V <sub>DD_6</sub> | S                   | -                          | $V_{DD_6}$                                       | -                                                                                      | _     |

| 53      | -      | -       | PF13              | I/O                 | FT                         | PF13                                             | FSMC_A7                                                                                | -     |

| 54      | -      | -       | PF14              | I/O                 | FT                         | PF14                                             | FSMC_A8                                                                                | -     |

| 55      | -      | -       | PF15              | I/O                 | FT                         | PF15                                             | FSMC_A9                                                                                | -     |

| 56      | -      | -       | PG0               | I/O                 | FT                         | PG0                                              | FSMC_A10                                                                               | -     |

| 57      | -      | -       | PG1               | I/O                 | FT                         | PG1                                              | FSMC_A11                                                                               | _     |

| 58      | -      | 38      | PE7               | I/O                 | FT                         | PE7                                              | FSMC_D4                                                                                | _     |

| 59      | -      | 39      | PE8               | I/O                 | FT                         | PE8                                              | FSMC_D5                                                                                | _     |

| 60      | -      | 40      | PE9               | I/O                 | FT                         | PE9                                              | FSMC_D6                                                                                | -     |

| 61      | -      | -       | V <sub>SS_7</sub> | S                   | -                          | V <sub>SS_7</sub>                                | -                                                                                      | -     |

# Table 5. STM32F101xF/STM32F101xG pin definitions (continued)

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

# 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

# 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 2 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

# 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 7*.

Figure 13. Typical current consumption on  $\rm V_{BAT}$  with RTC on vs. temperature at different  $\rm V_{BAT}$  values

Figure 14. Typical current consumption in Standby mode versus temperature at different  $V_{DD}$  values

## Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 36 MHz)

- Prefetch is on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK/4</sub>, f<sub>PCLK2</sub> = f<sub>HCLK/2</sub>, f<sub>ADCCLK</sub> = f<sub>PCLK2</sub>/4

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}$ ,  $f_{PCLK2} = f_{HCLK}$ ,  $f_{ADCCLK} = f_{PCLK2}/2$

The parameters given in *Table 18* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

|                 |                                  |                                  |                   | Typ <sup>(1)</sup>                        | Typ <sup>(1)</sup>          |      |

|-----------------|----------------------------------|----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                        | Conditions                       | <sup>f</sup> нсlк | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                  |                                  | 36 MHz            | 28.5                                      | 18.7                        |      |

|                 |                                  |                                  | 24 MHz            | 24.1                                      | 12.8                        |      |

|                 |                                  |                                  | 16 MHz            | 14                                        | 9.2                         |      |

|                 |                                  |                                  | 8 MHz             | 7.7                                       | 5.4                         |      |

|                 |                                  | External<br>clock <sup>(3)</sup> | 4 MHz             | 4.6                                       | 3.4                         |      |

|                 | Supply<br>current in<br>Run mode |                                  | 2 MHz             | 3                                         | 2.3                         | mA   |

|                 |                                  |                                  | 1 MHz             | 2.2                                       | 1.8                         |      |

|                 |                                  |                                  | 500 kHz           | 1.7                                       | 1.5                         |      |

|                 |                                  |                                  | 125 kHz           | 1.4                                       | 1.3                         |      |

| I <sub>DD</sub> |                                  | Running on<br>high speed         | 36 MHz            | 27.5                                      | 17.5                        | IIIA |

|                 |                                  |                                  | 24 MHz            | 18.9                                      | 11.6                        |      |

|                 |                                  |                                  | 16 MHz            | 12.2                                      | 8.2                         |      |

|                 |                                  | internal RC                      | 8 MHz             | 7.2                                       | 4.8                         |      |

|                 |                                  | (HSI), AHB<br>prescaler          | 4 MHz             | 4                                         | 2.7                         |      |

|                 |                                  | used to                          | 2 MHz             | 2.3                                       | 1.7                         |      |

|                 |                                  | reduce the<br>frequency          | 1 MHz             | 1.5                                       | 1.2                         |      |

|                 |                                  |                                  | 500 kHz           | 1.1                                       | 0.9                         |      |

|                 |                                  |                                  | 125 kHz           | 0.75                                      | 0.7                         |      |

Table 18. Typical current consumption in Run mode, code with data processing<br/>running from Flash

1. Typical values are measures at T\_A = 25 °C, V\_{DD} = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

DocID16553 Rev 5

# 5.3.8 PLL characteristics

The parameters given in *Table 28* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol               | Devemeder                      |                    | Unit |                    |      |

|----------------------|--------------------------------|--------------------|------|--------------------|------|

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| f                    | PLL input clock <sup>(2)</sup> | 1                  | 8.0  | 25                 | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40                 | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -    | 36                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | -    | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | -    | 300                | ps   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

# 5.3.9 Memory characteristics

# **Flash memory**

The characteristics are given at  $T_A = -40$  to 85 °C unless otherwise specified.

| Symbol                   | Parameter               | Conditions                                                                            | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------------|-------------------------|---------------------------------------------------------------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>        | 16-bit programming time | $T_A = -40$ to +85 °C                                                                 | 40  | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub>       | Page (2 KB) erase time  | $T_A = -40$ to +85 °C                                                                 | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>          | Mass erase time         | $T_A = -40$ to +85 °C                                                                 | 20  | -    | 40                 | ms   |

|                          |                         | Read mode<br>f <sub>HCLK</sub> = 36 MHz with 1<br>wait state, V <sub>DD</sub> = 3.3 V | -   | -    | 28                 | mA   |

| I <sub>DD</sub> Supply o | Supply current          | Write mode<br>f <sub>HCLK</sub> = 36 MHz, V <sub>DD</sub> =<br>3.3 V                  | -   | -    | 7                  | mA   |

|                          |                         | Erase mode<br>f <sub>HCLK</sub> = 36 MHz, V <sub>DD</sub> =<br>3.3 V                  | -   | -    | 5                  | mA   |

|                          |                         | Power-down mode / Halt,<br>V <sub>DD</sub> = 3.0 to 3.6 V                             | -   | -    | 50                 | μA   |

| V <sub>prog</sub>        | Programming voltage     | -                                                                                     | 2   | -    | 3.6                | V    |

#### Table 29. Flash memory characteristics

1. Guaranteed by design.

| Symbol                       | Parameter                             | Min | Max | Unit |

|------------------------------|---------------------------------------|-----|-----|------|

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high | 7   | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high  | 2   | -   | ns   |

# Table 38. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 15 pF.

2. Guaranteed by characterization results.

## PC Card/CompactFlash controller waveforms and timings

*Figure 27* through *Figure 32* represent synchronous waveforms and *Table 40* and *Table 41* provide the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC WaitSetupTime = 0x07;

- IO.FSMC HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

Figure 36. NAND controller waveforms for common memory write access

Table 41. Switching characteristics for NAND Flash write cycles<sup>(1)</sup>

| Symbol                  | Parameter                             | Min                    | Мах                      | Unit |

|-------------------------|---------------------------------------|------------------------|--------------------------|------|

| t <sub>w(NWE)</sub>     | FSMC_NWE low width                    | 3t <sub>HCLK</sub>     | 3t <sub>HCLK</sub>       | ns   |

| t <sub>v(NWE-D)</sub>   | FSMC_NWE low to FSMC_D[15:0] valid    | -                      | 0                        | ns   |

| t <sub>h(NWE-D)</sub>   | FSMC_NWE high to FSMC_D[15:0] invalid | 2t <sub>HCLK</sub> + 2 | -                        | ns   |

| t <sub>d(ALE-NWE)</sub> | FSMC_ALE valid before FSMC_NWE low    | -                      | 3t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NWE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid     | 3t <sub>HCLK</sub> + 8 | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FSMC_ALE valid before FSMC_NOE low    | -                      | 2t <sub>HCLK</sub>       | ns   |

| t <sub>h(NOE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid     | 2t <sub>HCLK</sub>     | -                        | ns   |

1. C<sub>L</sub> = 15 pF.

#### 5.3.11 **EMC** characteristics

Susceptibility tests are performed on a sample basis during device characterization.

# Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports), the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 42*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                     | Level/Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP144,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 36 MHz<br>conforms to IEC 61000-4-2 | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP144,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 36 MHz<br>conforms to IEC 61000-4-4 | 4A          |

| Table 42. EMS | characteristics |

|---------------|-----------------|

|---------------|-----------------|

# Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

# **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device is monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/36 MHz | Unit |

|------------------|------------|-------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|                  | Peak level | $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, LQFP144 package compliant with IEC 61967-2$ | 0.1 MHz to 30 MHz           | 8                                                          |      |

| 6                |            |                                                                                           | 30 MHz to 130 MHz           | 27                                                         | dBµV |

| S <sub>EMI</sub> |            |                                                                                           | 130 MHz to 1 GHz            | 26                                                         |      |

|                  |            |                                                                                           | SAE EMI Level               | 4                                                          | -    |

The test results are given in Table 46

| Symbol           |                                                            | Functional s       |                    |      |  |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|--|

|                  | Description                                                | Negative injection | Positive injection | Unit |  |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |  |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |  |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |  |

# Table 46. I/O current injection susceptibility

Figure 37. Standard I/O input characteristics - CMOS port

Figure 38. Standard I/O input characteristics - TTL port

Figure 39. 5 V tolerant I/O input characteristics - CMOS port

Figure 40. 5 V tolerant I/O input characteristics - TTL port

# **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxedV<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to ±3 mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 8*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 8*).

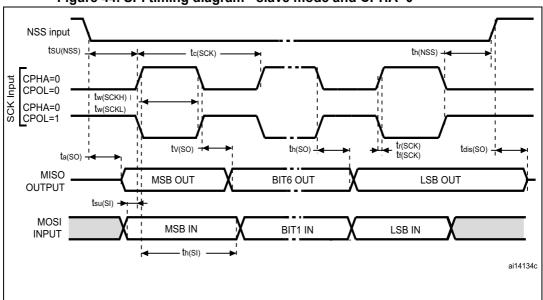

Figure 44. SPI timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

The formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |  |  |

|-------------------------|---------------------|---------------------------|--|--|

| 1.5                     | 0.11                | 0.4                       |  |  |

| 7.5                     | 0.54                | 5.9                       |  |  |

| 13.5                    | 0.96                | 11.4                      |  |  |

| 28.5                    | 2.04                | 25.2                      |  |  |

| 41.5                    | 2.96                | 37.2                      |  |  |

| 55.5                    | 3.96                | 50                        |  |  |

| 71.5                    | 5.11                | NA                        |  |  |

| 239.5                   | 17.1                | NA                        |  |  |

1. Guaranteed by design.

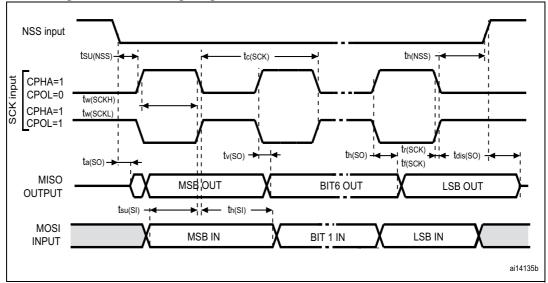

| Symbol | Parameter                    | Test conditions                                                                                             | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | $f_{PCLK2} = 28 \text{ MHz},$                                                                               | ±1.3 | ±2                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V, T <sub>A</sub> = 25 | ±1   | ±1.5               |      |

| EG     | Gain error                   | °C                                                                                                          | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after<br>ADC calibration                                                                  | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | $V_{\text{REF+}} = V_{\text{DDA}}$                                                                          | ±0.8 | ±1.5               |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in *Section 5.3.13* does not affect the ADC accuracy. 2.

3. Guaranteed by characterization results.

| Symbol | Parameter                    | Test conditions                                                                      | Тур  | Max <sup>(4)</sup> | Unit |  |  |  |  |

|--------|------------------------------|--------------------------------------------------------------------------------------|------|--------------------|------|--|--|--|--|

| ET     | Total unadjusted error       |                                                                                      | ±2   | ±5                 |      |  |  |  |  |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 28 MHz,<br>f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ, | ±1.5 | ±2.5               |      |  |  |  |  |

| EG     | Gain error                   | $V_{DDA} = 2.4 V \text{ to } 3.6 V$                                                  | ±1.5 | ±3                 | LSB  |  |  |  |  |

| ED     | Differential linearity error | Measurements made after<br>ADC calibration                                           | ±1   | ±2                 |      |  |  |  |  |

| EL     | Integral linearity error     |                                                                                      | ±1.5 | ±3                 |      |  |  |  |  |

## Table 59. ADC $accuracy^{(1)}(2)(3)$

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted  $V_{DD}$ , frequency,  $V_{REF}$  and temperature ranges.

3. ADC accuracy vs. negative injection current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 5.3.13 does not affect the ADC accuracy.

4. Preliminary values.

### STM32F101xF, STM32F101xG

| Symbol                        | Parameter                                                                                                                                                                | Cond | itions | Min | Тур | Max <sup>(1)</sup> | Unit | Comments                                                                                                                |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-----|-----|--------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| tsettling                     | Settling time (full<br>scale: for a 10-bit<br>input code transition<br>between the lowest<br>and the highest input<br>codes when<br>DAC_OUT reaches<br>final value ±1LSB |      |        | -   | 3   | 4                  | μs   | C <sub>LOAD</sub> ≤50 pF, R <sub>LOAD</sub> ≥ 5 kΩ                                                                      |

| Update<br>rate <sup>(1)</sup> | Max frequency for a<br>correct DAC_OUT<br>change when small<br>variation in the input<br>code (from code i to<br>i+1LSB)                                                 |      |        | -   | -   | 1                  | MS/s | C <sub>LOAD</sub> ≤50 pF, R <sub>LOAD</sub> ≥ 5 kΩ                                                                      |

| t <sub>wakeup</sub> (1)       | Wakeup time from off<br>state (Setting the<br>ENx bit in the DAC<br>Control register)                                                                                    |      |        | -   | 6.5 | 10                 | μs   | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest<br>and highest possible ones. |

| PSRR+ <sup>(2)</sup>          | Power supply<br>rejection ratio (to<br>V <sub>DDA</sub> ) (static DC<br>measurement                                                                                      |      |        | -   | -67 | -40                | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |

Table 60. DAC characteristics (continued)

1. Preliminary values.

2. Guaranteed by design.

3. Quiescent mode refers to the state of the DAC when a steady value is kept on the output so that no dynamic consumption is involved.

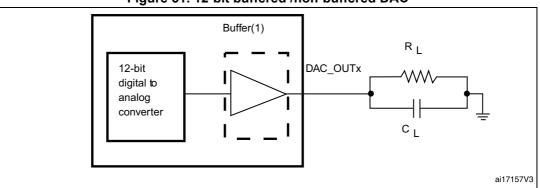

Figure 51. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |  |

| θ      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |  |

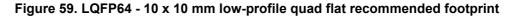

## Table 64. LQFP64 – 10 x 10 mm, 64 pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.