#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 56800                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 80MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 120KB (60K x 16)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | ·                                                                      |

| RAM Size                   | 4K x 16                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 160-BGA                                                                |

| Supplier Device Package    | 160-MAPBGA (15x15)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56f807vf80e |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Document Revision History**

| Version History | Description of Change                                                                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 16         | Added revision history.<br>Added this text to footnote 2 in <b>Table 3-8</b> : "However, the high pulse width does not have to<br>be any particular percent of the low pulse width." |

### **1.4 Product Documentation**

The four documents listed in **Table 1-1** are required for a complete description and proper design with the 56F807. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, Freescale Literature Distribution Centers, or online at **http://www.freescale.com**.

| Торіс                                  | Description                                                                                                 | Order Number  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------|

| 56800E<br>Family Manual                | Detailed description of the 56800 family architecture,<br>and 16-bit core processor and the instruction set | 56800EFM      |

| DSP56F801/803/805/807<br>User's Manual | Detailed description of memory, peripherals, and interfaces of the 56F801, 56F803, 56F805, and 56F807       | DSP56F801-7UM |

| 56F807<br>Technical Data Sheet         | Electrical and timing specifications, pin descriptions, and package descriptions (this document)            | DSP56F807     |

| 56F807<br>Errata                       | Details any chip issues that might be present                                                               | 56F807E       |

#### Table 1-1 56F807 Chip Documentation

### 1.5 Data Sheet Conventions

This data sheet uses the following conventions:

| OVERBAR      | This is used to indicate a signal that is active when pulled low. For example, the $\overline{\text{RESET}}$ pin is active when low. |                                                             |                               |                                  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------|--|--|--|--|

| "asserted"   | A high true (active high) s                                                                                                          | signal is high or a low tr                                  | ue (active low) signal is lov | Ν.                               |  |  |  |  |

| "deasserted" | A high true (active high) s                                                                                                          | signal is low or a low tru                                  | ie (active low) signal is hig | h.                               |  |  |  |  |

| Examples:    | Signal/Symbol                                                                                                                        | Signal/Symbol Logic State Signal State Voltage <sup>1</sup> |                               |                                  |  |  |  |  |

|              | PIN                                                                                                                                  | True                                                        | Asserted                      | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |  |

|              | PIN                                                                                                                                  | False                                                       | Deasserted                    | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |  |

|              | PIN                                                                                                                                  | True                                                        | Asserted                      | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |  |

|              | PIN                                                                                                                                  | PIN False Deasserted V <sub>IL</sub> /V <sub>OL</sub>       |                               |                                  |  |  |  |  |

|              |                                                                                                                                      |                                                             |                               |                                  |  |  |  |  |

1. Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

\*includes TCS pin which is reserved for factory use and is tied to VSS

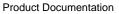

#### Figure 2-1 56F807 Signals Identified by Functional Group<sup>1</sup>

<sup>1.</sup> Alternate pin functionality is shown in parenthesis.

## 2.10 Serial Communications Interface (SCI) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type   | State During<br>Reset | Signal Description                                                                                                                                                                                                                                             |  |  |

|----------------|----------------|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

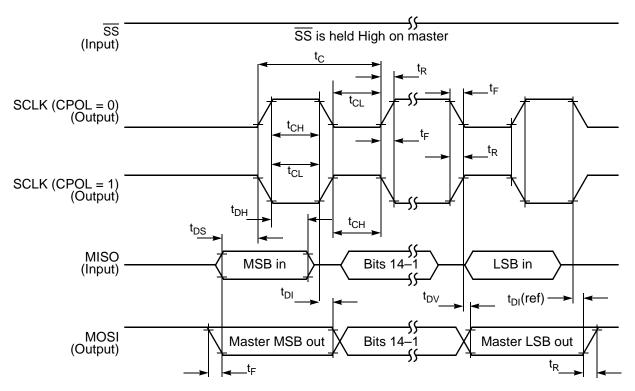

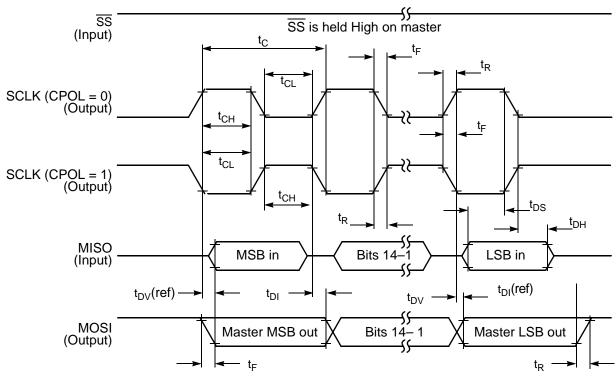

| 1              | MISO           | Input/<br>Output | Input                 | SPI Master In/Slave Out (MISO)—This serial data pin is an input to a master device and an output from a slave device. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected.                               |  |  |

|                | GPIOE6         | Input/Outp<br>ut | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                   |  |  |

|                |                |                  |                       | After reset, the default state is MISO.                                                                                                                                                                                                                        |  |  |

| 1              | MOSI           | Input/<br>Output | Input                 | SPI Master Out/Slave In (MOSI)—This serial data pin is an output from<br>a master device and an input to a slave device. The master device<br>places data on the MOSI line a half-cycle before the clock edge that the<br>slave device uses to latch the data. |  |  |

|                | GPIOE5         | Input/Outp<br>ut | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.<br>After reset, the default state is MOSI.                                                                                        |  |  |

|                | 00116          |                  |                       |                                                                                                                                                                                                                                                                |  |  |

| 1              | SCLK           | Input/Outp<br>ut | Input                 | <b>SPI Serial Clock</b> —In master mode, this pin serves as an output, clocking slaved listeners. In slave mode, this pin serves as the data clock input.                                                                                                      |  |  |

|                | GPIOE4         | Input/Outp<br>ut | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                   |  |  |

|                |                |                  |                       | After reset, the default state is SCLK.                                                                                                                                                                                                                        |  |  |

| 1              | SS             | Input            | Input                 | SPI Slave Select—In master mode, this pin is used to arbitrate multiple masters. In slave mode, this pin is used to select the slave.                                                                                                                          |  |  |

|                | GPIOE7         | Input/Outp<br>ut | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                   |  |  |

|                |                |                  |                       | After reset, the default state is $\overline{SS}$ .                                                                                                                                                                                                            |  |  |

Table 2-14 Serial Peripheral Interface (SPI) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type   | State During<br>Reset | Signal Description                                                                                                           |  |

|----------------|----------------|------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| 1              | TXD0           | Output           | Input                 | Transmit Data (TXD0)—transmit data output                                                                                    |  |

|                | GPIOE0         | Input/Outp<br>ut | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin. |  |

|                |                |                  |                       | After reset, the default state is SCI output.                                                                                |  |

| 1              | RXD0           | Input            | Input                 | Receive Data (RXD0)— receive data input                                                                                      |  |

|                | GPIOE1         | Input/Outp<br>ut | Input                 | <b>Port E GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin. |  |

|                |                |                  |                       | After reset, the default state is SCI input.                                                                                 |  |

| 1              | TXD1           | Output           | Input                 | Transmit Data (TXD1)—transmit data output                                                                                    |  |

|                | GPIOD6         | Input/Outp<br>ut | Input                 | <b>Port D GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin. |  |

|                |                |                  |                       | After reset, the default state is SCI output.                                                                                |  |

| 1              | RXD1           | Input            | Input                 | Receive Data (RXD1)— receive data input                                                                                      |  |

|                | GPIOD7         | Input/Outp<br>ut | Input                 | <b>Port D GPIO</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin. |  |

|                |                |                  |                       | After reset, the default state is SCI input.                                                                                 |  |

### Table 2-15 Serial Communications Interface (SCI0 and SCI1) Signals

## 2.11 CAN Signals

#### Table 2-16 CAN Module Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type     | State During<br>Reset | Signal Description                                                                                |  |

|----------------|----------------|--------------------|-----------------------|---------------------------------------------------------------------------------------------------|--|

| 1              | MSCAN_RX       | Input<br>(Schmitt) | Input                 | <b>MSCAN Receive Data</b> —MSCAN input. This pin has an internal pull-up resistor.                |  |

| 1              | MSCAN_TX       | Output             | Output                | MSCAN Transmit Data—MSCAN output. CAN output is open-drain output and pull-up resistor is needed. |  |

### 2.12 Analog-to-Digital Converter (ADC) Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type | State During<br>Reset | Signal Description                                                                                            |  |

|----------------|----------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------|--|

| 4              | ANA0-3         | Input          | Input                 | ANA0-3—Analog inputs to ADCA channel 1                                                                        |  |

| 4              | ANA4-7         | Input          | Input                 | ANA4-7—Analog inputs to ADCA channel 2                                                                        |  |

| 2              | VREF           | Input          | Input                 | <b>VREF</b> —Analog reference voltage for ADC. Must be set to V <sub>DDA</sub> -0.3V for optimal performance. |  |

| 4              | ANB0-3         | Input          | Input                 | ANB0-3—Analog inputs to ADCB, channel 1                                                                       |  |

| 4              | ANB4-7         | Input          | Input                 | ANB4-7—Analog inputs to ADCB, channel 2                                                                       |  |

### Table 2-17 Analog to Digital Converter Signals

## 2.13 Quad Timer Module Signals

| No. of<br>Pins | Signal<br>Name | Signal Type  | State During<br>Reset | Signal Description                    |  |

|----------------|----------------|--------------|-----------------------|---------------------------------------|--|

| 2              | TC0-1          | Input/Output | Input                 | TC0-1—Timer C Channels 0 and 1        |  |

| 4              | TD0-3          | Input/Output | Input                 | TD0-3—Timer D Channels 0, 1, 2, and 3 |  |

#### Table 2-18 Quad Timer Module Signals

damage to the device.

The 56F807 DC/AC electrical specifications are preliminary and are from design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after complete characterization and device qualifications have been completed.

#### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

| Characteristic                                                                                                                 | Symbol          | Min                   | Max                    | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|------------------------|------|

| Supply voltage                                                                                                                 | V <sub>DD</sub> | V <sub>SS</sub> – 0.3 | V <sub>SS</sub> + 4.0  | V    |

| All other input voltages, excluding Analog inputs                                                                              | V <sub>IN</sub> | V <sub>SS</sub> – 0.3 | V <sub>SS</sub> + 5.5V | V    |

| Voltage difference $V_{DD}$ to $V_{DDA}$                                                                                       | $\Delta V_{DD}$ | - 0.3                 | 0.3                    | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$                                                                                       | $\Delta V_{SS}$ | - 0.3                 | 0.3                    | V    |

| Analog inputs, ANA0-7 and VREF                                                                                                 | V <sub>IN</sub> | V <sub>SSA</sub> -0.3 | V <sub>DDA</sub> + 0.3 | V    |

| Analog inputs EXTAL and XTAL                                                                                                   | V <sub>IN</sub> | V <sub>SSA</sub> -0.3 | V <sub>SSA</sub> + 3.0 | V    |

| Current drain per pin excluding V <sub>DD</sub> , V <sub>SS</sub> , PWM outputs, TCS, VPP, V <sub>DDA</sub> , V <sub>SSA</sub> | I               | _                     | 10                     | mA   |

#### Table 3-1 Absolute Maximum Ratings

| <b>Table 3-2 Recommended</b> | Operating | Conditions |

|------------------------------|-----------|------------|

|------------------------------|-----------|------------|

| Characteristic                           | Symbol           | Min  | Тур | Max | Unit |

|------------------------------------------|------------------|------|-----|-----|------|

| Supply voltage, digital                  | V <sub>DD</sub>  | 3.0  | 3.3 | 3.6 | V    |

| Supply Voltage, analog                   | V <sub>DDA</sub> | 3.0  | 3.3 | 3.6 | V    |

| Voltage difference $V_{DD}$ to $V_{DDA}$ | $\Delta V_{DD}$  | -0.1 | -   | 0.1 | V    |

- 4. Thermal Characterization Parameter, Psi-JT ( $\Psi_{JT}$ ), is the "resistance" from junction to reference point thermocouple on top center of case as defined in JESD51-2.  $\Psi_{JT}$  is a useful value to use to estimate junction temperature in steady state customer environments.

- 5. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 6. See Section 5.1 from more details on thermal design considerations.

- 7. TJ = Junction Temperature TA = Ambient Temperature

### 3.2 DC Electrical Characteristics

#### **Table 3-4 DC Electrical Characteristics**

Operating Conditions:  $V_{SS} = V_{SSA} = 0$  V,  $V_{DD} = V_{DDA} = 3.0-3.6$  V,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$  pF,  $f_{op} = 80$  MHz

|                                                                                            |                                   |                       | -   |      |      |

|--------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-----|------|------|

| Characteristic                                                                             | Symbol                            | Min                   | Тур | Мах  | Unit |

| Input high voltage (XTAL/EXTAL)                                                            | V <sub>IHC</sub>                  | 2.25                  | _   | 2.75 | V    |

| Input low voltage (XTAL/EXTAL)                                                             | V <sub>ILC</sub>                  | 0                     |     | 0.5  | V    |

| Input high voltage (Schmitt trigger inputs) <sup>1</sup>                                   | V <sub>IHS</sub>                  | 2.2                   | _   | 5.5  | V    |

| Input low voltage (Schmitt trigger inputs) <sup>1</sup>                                    | V <sub>ILS</sub>                  | -0.3                  | _   | 0.8  | V    |

| Input high voltage (all other digital inputs)                                              | V <sub>IH</sub>                   | 2.0                   |     | 5.5  | V    |

| Input low voltage (all other digital inputs)                                               | V <sub>IL</sub>                   | -0.3                  |     | 0.8  | V    |

| Input current high (pullup/pulldown resistors disabled, $V_{\text{IN}} {=} V_{\text{DD}})$ | I <sub>IH</sub>                   | -1                    | _   | 1    | μΑ   |

| Input current low (pullup/pulldown resistors disabled, $\mathrm{V_{IN}=V_{SS}}$ )          | IIL                               | -1                    | _   | 1    | μΑ   |

| Input current high (with pullup resistor, $V_{IN}=V_{DD}$ )                                | I <sub>IHPU</sub>                 | -1                    | _   | 1    | μΑ   |

| Input current low (with pullup resistor, $V_{IN}=V_{SS}$ )                                 | I <sub>ILPU</sub>                 | -210                  |     | -50  | μΑ   |

| Input current high (with pulldown resistor, $V_{IN}=V_{DD}$ )                              | I <sub>IHPD</sub>                 | 20                    | _   | 180  | μΑ   |

| Input current low (with pulldown resistor, $V_{IN}=V_{SS}$ )                               | I <sub>ILPD</sub>                 | -1                    |     | 1    | μΑ   |

| Nominal pullup or pulldown resistor value                                                  | R <sub>PU</sub> , R <sub>PD</sub> |                       | 30  |      | KΩ   |

| Output tri-state current low                                                               | I <sub>OZL</sub>                  | -10                   | _   | 10   | μΑ   |

| Output tri-state current high                                                              | I <sub>OZH</sub>                  | -10                   |     | 10   | μΑ   |

| Input current high (analog inputs, $V_{IN}=V_{DDA}$ ) <sup>2</sup>                         | I <sub>IHA</sub>                  | -15                   | -   | 15   | μΑ   |

| Input current low (analog inputs, $V_{IN}=V_{SSA}$ ) <sup>3</sup>                          | I <sub>ILA</sub>                  | -15                   |     | 15   | μΑ   |

| Output High Voltage (at IOH)                                                               | V <sub>OH</sub>                   | V <sub>DD</sub> - 0.7 | —   | —    | V    |

#### Table 3-4 DC Electrical Characteristics (Continued)

Operating Conditions:  $V_{SS} = V_{SSA} = 0 V$ ,  $V_{DD} = V_{DDA} = 3.0-3.6 V$ ,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$  pF,  $f_{op} = 80$  MHz

| Characteristic                                            | Symbol                        | Min | Тур | Max | Unit |

|-----------------------------------------------------------|-------------------------------|-----|-----|-----|------|

| Output Low Voltage (at IOL)                               | V <sub>OL</sub>               | —   | -   | 0.4 | V    |

| Output source current                                     | I <sub>ОН</sub>               | 4   | —   |     | mA   |

| Output source current                                     | I <sub>OL</sub>               | 4   | —   | _   | mA   |

| PWM pin output source current <sup>3</sup>                | I <sub>OHP</sub>              | 10  | —   | _   | mA   |

| PWM pin output sink current <sup>4</sup>                  | I <sub>OLP</sub>              | 16  | —   | _   | mA   |

| Input capacitance                                         | C <sub>IN</sub>               | —   | 8   |     | pF   |

| Output capacitance                                        | C <sub>OUT</sub>              | —   | 12  | _   | pF   |

| V <sub>DD</sub> supply current                            | I <sub>DDT</sub> <sup>5</sup> |     |     |     |      |

| Run <sup>6</sup>                                          |                               | —   | 195 | 220 | mA   |

| Wait <sup>7</sup>                                         |                               | —   | 170 | 200 | mA   |

| Stop                                                      |                               | _   | 115 | 145 | mA   |

| Low Voltage Interrupt, external power supply <sup>8</sup> | V <sub>EIO</sub>              | 2.4 | 2.7 | 3.0 | V    |

| Low Voltage Interrupt, internal power supply <sup>9</sup> | V <sub>EIC</sub>              | 2.0 | 2.2 | 2.4 | V    |

| Power on Reset <sup>10</sup>                              | V <sub>POR</sub>              | -   | 1.7 | 2.0 | V    |

1. Schmitt Trigger inputs are: EXTBOOT, IRQA, IRQB, RESET, TCS, ISA0-2, FAULTA0-3, ISB0-2, FAULTB0-3, TCK, TRST, TMS, TDI, and MSCAN\_RX

2. Analog inputs are: ANA[0:7], XTAL and EXTAL. Specification assumes ADC is not sampling.

3. PWM pin output source current measured with 50% duty cycle.

4. PWM pin output sink current measured with 50% duty cycle.

5.  $I_{DDT} = I_{DD} + I_{DDA}$  (Total supply current for  $V_{DD} + V_{DDA}$ )

6. Run (operating) I<sub>DD</sub> measured using 8MHz clock source. All inputs 0.2V from rail; outputs unloaded. All ports configured as inputs; measured with all modules enabled.

7. Wait I<sub>DD</sub> measured using external square wave clock source ( $f_{osc} = 8MHz$ ) into XTAL; all inputs 0.2V from rail; no DC loads; less than 50pF on all outputs. C<sub>L</sub> = 20pF on EXTAL; all ports configured as inputs; EXTAL capacitance linearly affects wait I<sub>DD</sub>; measured with PLL enabled.

8. This low voltage interrupt monitors the V<sub>DDA</sub> external power supply. V<sub>DDA</sub> is generally connected to the same potential as V<sub>DD</sub> via separate traces. If V<sub>DDA</sub> drops below V<sub>EIO</sub>, an interrupt is generated. Functionality of the device is guaranteed under transient conditions when V<sub>DDA</sub> $\geq$ V<sub>EIO</sub> (between the minimum specified V<sub>DD</sub> and the point when the V<sub>EIO</sub> interrupt is generated).

9. This low voltage interrupt monitors the internally regulated core power supply. If the output from the internal voltage is regulator drops below V<sub>EIC</sub>, an interrupt is generated. Since the core logic supply is internally regulated, this interrupt will not be generated unless the external power supply drops below the minimum specified value (3.0V).

10. Power—on reset occurs whenever the internally regulated 2.5V digital supply drops below 1.5V typical. While power is ramping up, this signal remains active as long as the internal 2.5V is below 1.5V typical, no matter how long the ramp-up rate is. The internally regulated voltage is typically 100mV less than V<sub>DD</sub> during ramp-up until 2.5V is reached, at which time it self-regulates.

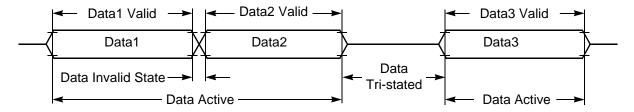

Figure 3-3 Signal States

| Mode         | XE <sup>1</sup> | YE <sup>2</sup> | SE <sup>3</sup> | OE <sup>4</sup> | PROG <sup>5</sup> | ERASE <sup>6</sup> | MAS1 <sup>7</sup> | NVSTR <sup>8</sup> |

|--------------|-----------------|-----------------|-----------------|-----------------|-------------------|--------------------|-------------------|--------------------|

| Standby      | L               | L               | L               | L               | L                 | L                  | L                 | L                  |

| Read         | Н               | Н               | Н               | Н               | L                 | L                  | L                 | L                  |

| Word Program | Н               | Н               | L               | L               | Н                 | L                  | L                 | Н                  |

| Page Erase   | Н               | L               | L               | L               | L                 | Н                  | L                 | Н                  |

| Mass Erase   | Н               | L               | L               | L               | L                 | Н                  | Н                 | Н                  |

- 1. X address enable, all rows are disabled when XE=0

- 2. Y address enable, YMUX is disabled when YE=0

- 3. Sense amplifier enable

- 4. Output enable, tri-state Flash data out bus when OE=0

- 5. Defines program cycle

- 6. Defines erase cycle

- 7. Defines mass erase cycle, erase whole block

- 8. Defines non-volatile store cycle

#### **Table 3-6 IFREN Truth Table**

| Mode         | IFREN=1                   | IFREN=0                   |

|--------------|---------------------------|---------------------------|

| Read         | Read information block    | Read main memory block    |

| Word program | Program information block | Program main memory block |

| Page erase   | Erase information block   | Erase main memory block   |

| Mass erase   | Erase both block          | Erase main memory block   |

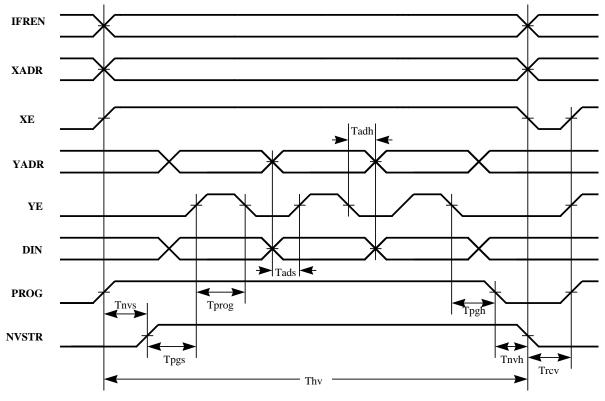

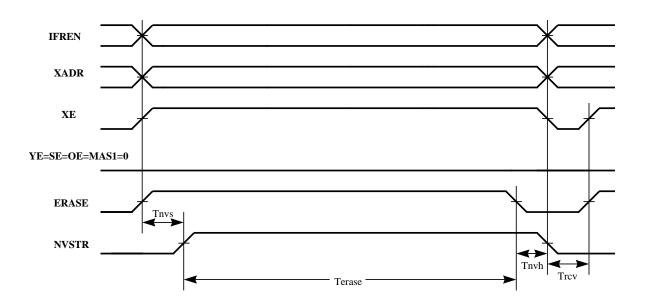

#### **Table 3-7 Flash Timing Parameters**

Operating Conditions:  $V_{SS} = V_{SSA} = 0 V$ ,  $V_{DD} = V_{DDA} = 3.0-3.6V$ ,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$  pF

| Characteristic              | Symbol           | Min    | Тур    | Max | Unit   | Figure     |

|-----------------------------|------------------|--------|--------|-----|--------|------------|

| Program time                | Tprog*           | 20     | -      | _   | us     | Figure 3-4 |

| Erase time                  | Terase*          | 20     | _      | _   | ms     | Figure 3-5 |

| Mass erase time             | Tme*             | 100    | -      | _   | ms     | Figure 3-6 |

| Endurance <sup>1</sup>      | E <sub>CYC</sub> | 10,000 | 20,000 | _   | cycles |            |

| Data Retention <sup>1</sup> | D <sub>RET</sub> | 10     | 30     | _   | years  |            |

The following parameters should only be used in the Manual Word Programming Mode

| ÷ ·                                          |        | • |     |   |    | -                                        |

|----------------------------------------------|--------|---|-----|---|----|------------------------------------------|

| PROG/ERASE to NVSTR set up time              | Tnvs*  | _ | 5   | - | us | Figure 3-4,<br>Figure 3-5,<br>Figure 3-6 |

| NVSTR hold time                              | Tnvh*  | _ | 5   | _ | us | Figure 3-4,<br>Figure 3-5                |

| NVSTR hold time (mass erase)                 | Tnvh1* | - | 100 | - | us | Figure 3-6                               |

| NVSTR to program set up time                 | Tpgs*  | _ | 10  | _ | us | Figure 3-4                               |

| Recovery time                                | Trcv*  | - | 1   | - | us | Figure 3-4,<br>Figure 3-5,<br>Figure 3-6 |

| Cumulative program<br>HV period <sup>2</sup> | Thv    | _ | 3   | _ | ms | Figure 3-4                               |

| Program hold time <sup>3</sup>               | Tpgh   | _ | _   | _ |    | Figure 3-4                               |

| Address/data set up time <sup>3</sup>        | Tads   | - | -   | - |    | Figure 3-4                               |

| Address/data hold time <sup>3</sup>          | Tadh   | _ | _   | _ |    | Figure 3-4                               |

1. One cycle is equal to an erase program and read.

2. Thy is the cumulative high voltage programming time to the same row before next erase. The same address cannot be programmed twice before next erase.

3. Parameters are guaranteed by design in smart programming mode and must be one cycle or greater.

\*The Flash interface unit provides registers for the control of these parameters.

Figure 3-4 Flash Program Cycle

Figure 3-5 Flash Erase Cycle

56F807 Technical Data Technical Data, Rev. 16

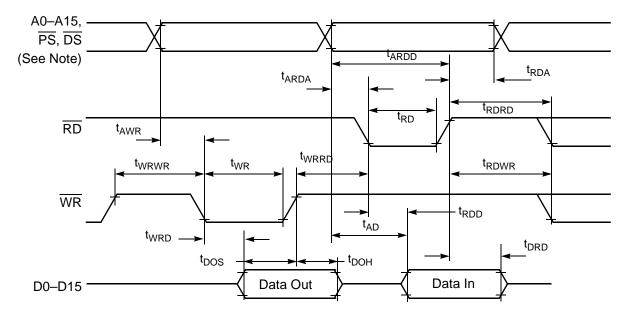

- 1. Timing is both wait state and frequency dependent. In the formulas listed, WS = the number of wait states and

- T = Clock Period. For 80MHz operation, T = 12.5ns.

- 2. Parameters listed are guaranteed by design.

To calculate the required access time for an external memory for any frequency < 80MHz, use this formula:

Top = Clock period @ desired operating frequency

WS = Number of wait states

Memory Access Time = (Top\*WS) + (Top- 11.5)

Note: During read-modify-write instructions and internal instructions, the address lines do not change state.

Figure 3-11 External Bus Asynchronous Timing

### 3.6 Reset, Stop, Wait, Mode Select, and Interrupt Timing

### Table 3-11 Reset, Stop, Wait, Mode Select, and Interrupt Timing<sup>1,5</sup>

Operating Conditions:  $V_{SS} = V_{SSA} = 0$  V,  $V_{DD} = V_{DDA} = 3.0-3.6$  V,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$  pF

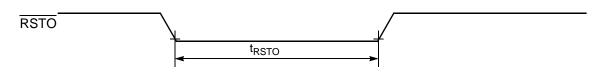

| Characteristic                                                                                                                                                                                               | Symbol           | Min              | Мах             | Unit     | See Figure |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|----------|------------|

| RESET Assertion to Address, Data and Control Signals<br>High Impedance                                                                                                                                       | t <sub>RAZ</sub> | —                | 21              | ns       | 3-12       |

| Minimum $\overline{\text{RESET}}$ Assertion Duration <sup>2</sup><br>OMR Bit 6 = 0<br>OMR Bit 6 = 1                                                                                                          | t <sub>RA</sub>  | 275,000T<br>128T |                 | ns<br>ns | 3-12       |

| RESET Deassertion to First External Address Output                                                                                                                                                           | t <sub>RDA</sub> | 33T              | 34T             | ns       | 3-12       |

| Edge-sensitive Interrupt Request Width                                                                                                                                                                       | t <sub>IRW</sub> | 1.5T             | —               | ns       | 3-13       |

| IRQA, IRQB Assertion to External Data Memory Access<br>Out Valid, caused by first instruction execution in the<br>interrupt service routine                                                                  | t <sub>IDM</sub> | 15T              | _               | ns       | 3-14       |

| IRQA, IRQB Assertion to General Purpose Output Valid,<br>caused by first instruction execution in the interrupt<br>service routine                                                                           | t <sub>IG</sub>  | 16T              | _               | ns       | 3-14       |

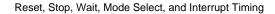

| IRQA Low to First Valid Interrupt Vector Address Out recovery from Wait State <sup>3</sup>                                                                                                                   | t <sub>IRI</sub> | 13T              | _               | ns       | 3-15       |

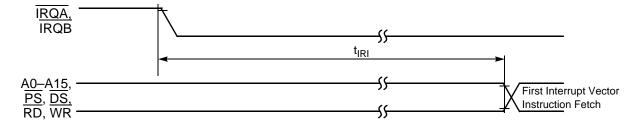

| IRQA Width Assertion to Recover from Stop State <sup>4</sup>                                                                                                                                                 | t <sub>IW</sub>  | 2T               | _               | ns       | 3-16       |

| Delay from IRQA Assertion to Fetch of first instruction<br>(exiting Stop)<br>OMR Bit 6 = 0<br>OMR Bit 6 = 1                                                                                                  | t <sub>IF</sub>  |                  | 275,000T<br>12T | ns<br>ns | 3-16       |

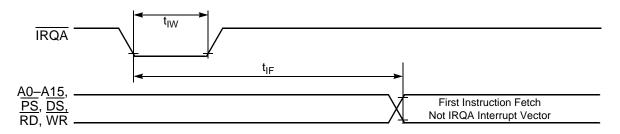

| Duration for Level Sensitive $\overline{IRQA}$ Assertion to Cause<br>the Fetch of First $\overline{IRQA}$ Interrupt Instruction (exiting Stop)<br>OMR Bit 6 = 0<br>OMR Bit 6 = 1                             | t <sub>IRQ</sub> |                  | 275,000T<br>12T | ns<br>ns | 3-17       |

| Delay from Level Sensitive IRQA Assertion to First<br>Interrupt Vector Address Out Valid (exiting Stop)<br>OMR Bit 6 = 0<br>OMR Bit 6 = 1<br>1. In the formulas, T = clock cycle, For an operating frequency | t <sub>ll</sub>  |                  | 275,000T<br>12T | ns<br>ns | 3-17       |

1. In the formulas, T = clock cycle. For an operating frequency of 80MHz, T = 12.5ns.

Circuit stabilization delay is required during reset when using an external clock or crystal oscillator in two cases:

After power-on reset

• When recovering from Stop state

3. The minimum is specified for the duration of an edge-sensitive IRQA interrupt required to recover from the Stop state. This is not the minimum required so that the IRQA interrupt is accepted.

4. The interrupt instruction fetch is visible on the pins only in Mode 3.

5. Parameters listed are guaranteed by design.

56F807 Technical Data Technical Data, Rev. 16

Figure 3-15 Interrupt from Wait State Timing

Figure 3-16 Recovery from Stop State Using Asynchronous Interrupt Timing

Figure 3-17 Recovery from Stop State Using IRQA Interrupt Service

Figure 3-18 Reset Output Timing

### 3.11 Analog-to-Digital Converter (ADC) Characteristics

#### **Table 3-16 ADC Characteristics**

$\begin{array}{l} \text{Operating Conditions: } V_{\text{SS}} = V_{\text{SSA}} = 0 \text{ V}, V_{\text{DD}} = V_{\text{DDA}} = 3.0 - 3.6 \text{ V}, V_{\text{REF}} = V_{\text{DD}} - 0.3 \text{ V}, \text{ADCDIV} = 4, 9, \text{ or } 14, \text{ (for optimal performance)}, \\ \text{ADC clock} = 4 \text{MHz}, 3.0 - 3.6 \text{ V}, T_{\text{A}} = -40^{\circ} \text{ to } +85^{\circ}\text{C}, C_{\text{L}} \leq 50 \text{pF}, f_{\text{OP}} = 80 \text{MHz} \end{array}$

| Characteristic                                     | Symbol              | Min              | Тур      | Max                           | Unit                                 |

|----------------------------------------------------|---------------------|------------------|----------|-------------------------------|--------------------------------------|

| ADC input voltages                                 | V <sub>ADCIN</sub>  | 0 <sup>1</sup>   | _        | V <sub>REF</sub> <sup>2</sup> | V                                    |

| Resolution                                         | R <sub>ES</sub>     | 12               | —        | 12                            | Bits                                 |

| Integral Non-Linearity <sup>3</sup>                | INL                 | _                | +/- 2.5  | +/- 4                         | LSB <sup>4</sup>                     |

| Differential Non-Linearity                         | DNL                 | —                | +/- 0.9  | +/- 1                         | LSB <sup>4</sup>                     |

| Monotonicity                                       |                     |                  | GUARANTE | ED                            |                                      |

| ADC internal clock <sup>5</sup>                    | f <sub>ADIC</sub>   | 0.5              | _        | 5                             | MHz                                  |

| Conversion range                                   | R <sub>AD</sub>     | V <sub>SSA</sub> | —        | V <sub>DDA</sub>              | V                                    |

| Conversion time                                    | t <sub>ADC</sub>    | —                | 6        | _                             | t <sub>AIC</sub> cycles <sup>6</sup> |

| Sample time                                        | t <sub>ADS</sub>    | —                | 1        | —                             | t <sub>AIC</sub> cycles <sup>6</sup> |

| Input capacitance                                  | C <sub>ADI</sub>    | _                | 5        | _                             | pF <sup>6</sup>                      |

| Gain Error (transfer gain) <sup>5</sup>            | E <sub>GAIN</sub>   | 0.93             | 1.00     | 1.08                          | —                                    |

| Total Harmonic Distortion <sup>5</sup>             | THD                 | 60               | 64       |                               |                                      |

| Offset Voltage <sup>5</sup>                        | V <sub>OFFSET</sub> | -90              | -25      | +10                           | mV                                   |

| Signal-to-Noise plus Distortion <sup>5</sup>       | SINAD               | 55               | 60       | _                             | —                                    |

| Effective Number of Bits <sup>5</sup>              | ENOB                | 9                | 10       |                               | bit                                  |

| Spurious Free Dynamic Range <sup>5</sup>           | SFDR                | 65               | 70       |                               | dB                                   |

| Bandwidth                                          | BW                  | _                | 100      | _                             | KHz                                  |

| ADC Quiescent Current (each dual ADC)              | I <sub>ADC</sub>    |                  | 50       |                               | mA                                   |

| V <sub>REF</sub> Quiescent Current (each dual ADC) | I <sub>VREF</sub>   | _                | 12       | 16.5                          | mA                                   |

1. For optimum ADC performance, keep the minimum  $V_{ADCIN}$  value  $\geq 25$ mV. Inputs less than 25mV may convert to a digital output code of 0.

2.  $V_{\text{REF}}$  must be equal to or less than  $V_{\text{DDA}}$  and must be greater than 2.7V. For optimal ADC performance, set  $V_{\text{REF}}$  to  $V_{\text{DDA}}$ -0.3V.

3. Measured in 10-90% range.

- 4. LSB = Least Significant Bit.

- 5. Guaranteed by characterization.

6.  $t_{AIC} = 1/f_{ADIC}$

- Ensure that capacitor leads and associated printed circuit traces that connect to the chip  $V_{DD}$  and  $V_{SS}$  pins are less than 0.5 inch per capacitor lead.

- Bypass the  $V_{DD}$  and  $V_{SS}$  layers of the PCB with approximately 100  $\mu$ F, preferably with a high-grade capacitor such as a tantalum capacitor.

- Because the controller's output signals have fast rise and fall times, PCB trace lengths should be minimal.

- Consider all device loads as well as parasitic capacitance due to PCB traces when calculating capacitance. This is especially critical in systems with higher capacitive loads that could create higher transient currents in the  $V_{DD}$  and  $V_{SS}$  circuits.

- Take special care to minimize noise levels on the VREF,  $V_{DDA}$  and  $V_{SSA}$  pins.

- Designs that utilize the TRST pin for JTAG port or OnCE module functionality (such as development or debugging systems) should allow a means to assert TRST whenever RESET is asserted, as well as a means to assert TRST independently of RESET. TRST must be asserted at power up for proper operation. Designs that do not require debugging functionality, such as consumer products, TRST should be tied low.

- Because the Flash memory is programmed through the JTAG/OnCE port, designers should provide an interface to this port to allow in-circuit Flash programming.

# Part 6 Ordering Information

**Table 6-1** lists the pertinent information needed to place an order. Consult a Freescale Semiconductor sales office or authorized distributor to determine availability and to order parts.

| Part   | Supply<br>Voltage | Package Type                                   | Pin<br>Count | Ambient<br>Frequency<br>(MHz) | Order Number    |

|--------|-------------------|------------------------------------------------|--------------|-------------------------------|-----------------|

| 56F807 | 3.0–3.6 V         | Low-Profile Quad Flat Pack (LQFP)              | 160          | 80                            | DSP56F807PY80   |

| 56F807 | 3.0–3.6 V         | Mold Array Process Ball Grid Array<br>(MAPBGA) | 160          | 80                            | DSP56F807VF80   |

|        |                   |                                                |              |                               |                 |

| 56F807 | 3.0–3.6 V         | Low-Profile Quad Flat Pack (LQFP)              | 160          | 80                            | DSP56F807PY80E* |

| 56F807 | 3.0–3.6 V         | Mold Array Process Ball Grid Array<br>(MAPBGA) | 160          | 80                            | DSP56F807VF80E* |

### Table 6-1 56F807 Ordering Information

\*This package is RoHS compliant.

\_\_\_\_\_

**Electrical Design Considerations**