Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b, 1x10b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1764-e-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIN ALLOCATION TABLES**

# TABLE 3:

# 14-PIN AND 16-PIN ALLOCATION TABLE (PIC16(L)F1764/5)

|                    |                        |            |     |                                            |                      |         |                  |            | (                              |                                                      |      |                     |                       |                       |                       |                     |                                            |                           |          |            |                |

|--------------------|------------------------|------------|-----|--------------------------------------------|----------------------|---------|------------------|------------|--------------------------------|------------------------------------------------------|------|---------------------|-----------------------|-----------------------|-----------------------|---------------------|--------------------------------------------|---------------------------|----------|------------|----------------|

| NО                 | 14-Pin PDIP/SOIC/TSSOP | 16-Pin QFN | ADC | Reference                                  | DAC                  | Op Amp  | Comparator       | Zero Cross | Programmable<br>Ramp Generator | Timers                                               | MWd  | ССР                 | 900                   | CLC                   | Modulator             | EUSART              | MSSP                                       | Interrupts                | Pull-ups | Hi Current | Basic          |

| RA0                | 13                     | 12         | AN0 | V <sub>REF</sub> -<br>DAC1REF-<br>DAC3REF- | DAC1OUT1<br>DAC3OUT1 | -       | C1IN0+           | -          | _                              | —                                                    | _    | _                   | —                     | -                     | -                     | _                   | —                                          | IOC                       | Y        | —          | ICSPDAT        |

| RA1                | 12                     | 11         | AN1 | VREF+<br>DAC1REF+<br>DAC3REF+              | _                    | —       | C1IN0-<br>C2IN0- | _          | -                              | —                                                    | _    | —                   | —                     | —                     | _                     | _                   | —                                          | IOC                       | Y        | —          | ICSPCLK        |

| RA2                | 11                     | 10         | AN2 | —                                          | —                    | -       | -                | ZCD        | _                              | T0CKI <sup>(1)</sup>                                 | -    | -                   | COG1IN <sup>(1)</sup> | -                     | —                     | _                   | —                                          | INT <sup>(1)</sup><br>IOC | Y        | —          | -              |

| RA3                | 4                      | 3          | -   | —                                          | _                    | -       | —                | —          | —                              | T6IN <sup>(1)</sup>                                  | _    | —                   | —                     | _                     | MD1CH <sup>(1)</sup>  | —                   | —                                          | IOC                       | Y        | —          | VPP<br>MCLR    |

| RA4                | 3                      | 2          | AN3 | —                                          | —                    | —       | -                | -          | —                              | T1G <sup>(1)</sup><br>SOSCO                          | —    | —                   | —                     | —                     | MD1CL <sup>(1)</sup>  | -                   | —                                          | IOC                       | Y        | —          | OSC2<br>CLKOUT |

| RA5                | 2                      | 1          |     |                                            |                      | —       | —                | _          | _                              | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup><br>SOSCI | _    | _                   | _                     | CLCIN3 <sup>(1)</sup> | MD1MOD <sup>(1)</sup> | _                   | —                                          | IOC                       | Υ        | —          | OSC1<br>CLKIN  |

| RC0                | 10                     | 9          | AN4 | —                                          | —                    | OPA1IN+ | C2IN0+           | _          | —                              | T5CKI <sup>(1)</sup>                                 | —    | —                   | —                     | —                     | —                     |                     | SCL <sup>(1)</sup><br>SCK <sup>(1,3)</sup> | IOC                       | Y        | —          | —              |

| RC1                | 9                      | 8          | AN5 | —                                          | —                    | OPA1IN- | C1IN1-<br>C2IN1- | —          | —                              | T4IN <sup>(1)</sup>                                  | —    | —                   | —                     | CLCIN2 <sup>(1)</sup> | —                     | —                   | SDI <sup>(1)</sup><br>SDA <sup>(1,3)</sup> | IOC                       | Y        | —          | —              |

| RC2                | 8                      | 7          | AN6 | —                                          | —                    | OPA1OUT | C1IN2-<br>C2IN2- | —          | PRG1IN0                        | —                                                    | —    | —                   | -                     | —                     | —                     | —                   | —                                          | IOC                       | Y        | —          | —              |

| RC3                | 7                      | 6          | AN7 | —                                          | —                    | —       | C1IN3-<br>C2IN3- | —          | —                              | T5G <sup>(1)</sup>                                   | —    | —                   | —                     | CLCIN0 <sup>(1)</sup> | —                     | —                   | <u>SS</u> (1)                              | IOC                       | Y        | —          | —              |

| RC4                | 6                      | 5          | —   | _                                          | _                    | -       | _                | _          | PRG1R <sup>(1)</sup>           | T3G <sup>(1)</sup>                                   | _    | —                   | _                     | CLCIN1 <sup>(1)</sup> |                       | CK <sup>(1)</sup>   | _                                          | IOC                       | Y        | Y          | —              |

| RC5                | 5                      | 4          | -   | _                                          |                      | _       | _                | _          | PRG1F <sup>(1)</sup>           | T3CKI <sup>(1)</sup>                                 | _    | CCP1 <sup>(1)</sup> | _                     |                       | _                     | RX <sup>(1,3)</sup> |                                            | IOC                       | Υ        | Y          | _              |

| VDD                | 1                      | 16         | _   | —                                          | —                    | -       | —                | —          | —                              | —                                                    | —    | —                   | —                     | -                     | —                     | —                   | —                                          | —                         | —        | —          | Vdd            |

| Vss                | 14                     | 13         | -   |                                            |                      | —       | _                | _          | _                              | _                                                    |      | _                   | _                     | _                     | _                     |                     |                                            | —                         | -        | -          | Vss            |

| OUT <sup>(2)</sup> | —                      | —          | -   | -                                          | -                    | -       | C1OUT            | _          | —                              | _                                                    | PWM3 | CCP1                | COG1A                 | CLC10UT               | MD10UT                | DT <sup>(3)</sup>   | SDO                                        | INT                       | —        | —          | _              |

|                    | —                      | —          | -   | _                                          | _                    | -       | C2OUT            | _          | _                              | _                                                    | PWM5 | _                   | COG1B                 | CLC2OUT               | _                     | TX                  | SDA <sup>(3)</sup>                         | _                         | -        | -          | -              |

|                    | —                      | —          | -   | -                                          | —                    | —       | _                | —          | —                              | —                                                    | -    | _                   | COG1C                 | CLC3OUT               | —                     | СК                  | SCK<br>SCL <sup>(3)</sup>                  | _                         | —        | —          | _              |

|                    | —                      | —          | -   | -                                          | -                    | -       | -                | _          | -                              | -                                                    | _    | -                   | COG1D                 | —                     | -                     | —                   | SUL                                        | —                         | —        | —          | —              |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS Input Selection register. See Table 12-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS Output Selection registers. See Table 12-2.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# TABLE 3-3: PIC16(L)F1764 MEMORY MAP (BANKS 0-7)

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                               | 200h |                               | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | WPUA                          | 28Ch | ODCONA                        | 30Ch | SLRCONA                       | 38Ch | INLVLA                        |

| 00Dh | —                             | 08Dh | —                             | 10Dh | —                             | 18Dh | —                             | 20Dh | —                             | 28Dh | —                             | 30Dh | —                             | 38Dh | —                             |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | WPUC                          | 28Eh | ODCONC                        | 30Eh | SLRCONC                       | 38Eh | INLVLC                        |

| 00Fh | _                             | 08Fh | —                             | 10Fh | CMOUT                         | 18Fh | _                             | 20Fh | _                             | 28Fh | —                             | 30Fh | —                             | 38Fh | _                             |

| 010h | _                             | 090h | _                             | 110h | CM1CON0                       | 190h | _                             | 210h |                               | 290h |                               | 310h |                               | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON1                       | 191h | PMADRL                        | 211h | SSP1BUF                       | 291h | CCPR1L                        | 311h |                               | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1NSEL                       | 192h | PMADRH                        | 212h | SSP1ADD                       | 292h | CCPR1H                        | 312h |                               | 392h | IOCAN                         |

| 013h | PIR3                          | 093h | PIE3                          | 113h | CM1PSEL                       | 193h | PMDATL                        | 213h | SSP1MSK                       | 293h | CCP1CON                       | 313h |                               | 393h | IOCAF                         |

| 014h | PIR4                          | 094h | PIE4                          | 114h | CM2CON0                       | 194h | PMDATH                        | 214h | SSP1STAT                      | 294h | CCP1CAP                       | 314h |                               | 394h | _                             |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CM2CON1                       | 195h | PMCON1                        | 215h | SSP1CON1                      | 295h |                               | 315h |                               | 395h | _                             |

| 016h | TMR1L                         | 096h | PCON                          | 116h | CM2NSEL                       | 196h | PMCON2                        | 216h | SSP1CON2                      | 296h |                               | 316h |                               | 396h | _                             |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | CM2PSEL                       | 197h | VREGCON <sup>(1)</sup>        | 217h | SSP1CON3                      | 297h |                               | 317h |                               | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | _                             | 198h | —                             | 218h |                               | 298h |                               | 318h |                               | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | _                             | 199h | RC1REG                        | 219h |                               | 299h |                               | 319h |                               | 399h | IOCCF                         |

| 01Ah | T2TMR                         | 09Ah | OSCSTAT                       | 11Ah | —                             | 19Ah | TX1REG                        | 21Ah |                               | 29Ah |                               | 31Ah |                               | 39Ah | _                             |

| 01Bh | T2PR                          | 09Bh | ADRESL                        | 11Bh |                               | 19Bh | SP1BRGL                       | 21Bh |                               | 29Bh |                               | 31Bh |                               | 39Bh | MD1CON0                       |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | _                             | 19Ch | SP1BRGH                       | 21Ch | _                             | 29Ch | _                             | 31Ch | _                             | 39Ch | MD1CON1                       |

| 01Dh | T2HLT                         | 09Dh | ADCON0                        | 11Dh | _                             | 19Dh | RC1STA                        | 21Dh | BORCON                        | 29Dh | _                             | 31Dh | _                             | 39Dh | MD1SRC                        |

| 01Eh | T2CLKCON                      | 09Eh | ADCON1                        | 11Eh | —                             | 19Eh | TX1STA                        | 21Eh | FVRCON                        | 29Eh | CCPTMRS                       | 31Eh | _                             | 39Eh | MD1CARL                       |

| 01Fh | T2RST                         | 09Fh | ADCON2                        | 11Fh | _                             | 19Fh | BAUD1CON                      | 21Fh | ZCD1CON                       | 29Fh | _                             | 31Fh | —                             | 39Fh | MD1CARH                       |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h | General Purpose<br>Register   | 3A0h |                               |

|      | General                       | 32Fh | 16 Bytes                      |      |                               |

|      | Purpose                       | 330h |                               |      | Unimplemented                 |

|      | Register<br>80 Bytes          |      | Unimplemented                 |      | Read as '0'                   |

|      | oo bytes                      |      | oo bytes                      |      | oo bytes                      |      | of Bytes                      |      | ou bytes                      |      | ou bytes                      |      | Read as '0'                   |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h |                               | 0F0h |                               | 170h |                               | 1F0h |                               | 270h |                               | 2F0h |                               | 370h |                               | 3F0h |                               |

|      | Common RAM<br>70h-7Fh         |      | Accesses<br>70h-7Fh           |

| 07Fh |                               | 0FFh |                               | 17Fh |                               | 1FFh |                               | 27Fh |                               | 2FFh |                               | 37Fh |                               | 3FFh |                               |

Legend: 🔲 = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1764.

# TABLE 3-5: PIC16(L)F1768 MEMORY MAP (BANKS 0-7)

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |       | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|-------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                               | 200h |                               | 280h |                               | 300h  |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh  |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | WPUA                          | 28Ch | ODCONA                        | 30Ch  | SLRCONA                       | 38Ch | INLVLA                        |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh | WPUB                          | 28Dh | ODCONB                        | 30Dh  | SLRCONB                       | 38Dh | INLVLB                        |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | WPUC                          | 28Eh | ODCONC                        | 30Eh  | SLRCONC                       | 38Eh | INLVLC                        |

| 00Fh | —                             | 08Fh | _                             | 10Fh | CMOUT                         | 18Fh | —                             | 20Fh | _                             | 28Fh | _                             | 30Fh  | -                             | 38Fh | _                             |

| 010h | —                             | 090h | —                             | 110h | CM1CON0                       | 190h | —                             | 210h | _                             | 290h | _                             | 310h  | _                             | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON1                       | 191h | PMADRL                        | 211h | SSP1BUF                       | 291h | CCPR1L                        | 311h  | _                             | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1NSEL                       | 192h | PMADRH                        | 212h | SSP1ADD                       | 292h | CCPR1H                        | 312h  | _                             | 392h | IOCAN                         |

| 013h | PIR3                          | 093h | PIE3                          | 113h | CM1PSEL                       | 193h | PMDATL                        | 213h | SSP1MSK                       | 293h | CCP1CON                       | 313h  | —                             | 393h | IOCAF                         |

| 014h | PIR4                          | 094h | PIE4                          | 114h | CM2CON0                       | 194h | PMDATH                        | 214h | SSP1STAT                      | 294h | CCP1CAP                       | 314h  | _                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CM2CON1                       | 195h | PMCON1                        | 215h | SSP1CON1                      | 295h | _                             | 315h  | _                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | CM2NSEL                       | 196h | PMCON2                        | 216h | SSP1CON2                      | 296h | —                             | 316h  | —                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | CM2PSEL                       | 197h | VREGCON <sup>(1)</sup>        | 217h | SSP1CON3                      | 297h | _                             | 317h  | _                             | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | CM3CON0                       | 198h | —                             | 218h | —                             | 298h | CCPR2L                        | 318h  | —                             | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | CM3CON1                       | 199h | RC1REG                        | 219h | —                             | 299h | CCPR2H                        | 319h  | —                             | 399h | IOCCF                         |

| 01Ah | T2TMR                         | 09Ah | OSCSTAT                       | 11Ah | CM3NSEL                       | 19Ah | TX1REG                        | 21Ah | _                             | 29Ah | CCP2CON                       | 31Ah  | _                             | 39Ah | —                             |

| 01Bh | T2PR                          | 09Bh | ADRESL                        | 11Bh | CM3PSEL                       | 19Bh | SP1BRGL                       | 21Bh | —                             | 29Bh | CCP2CAP                       | 31Bh  | MD2CON0                       | 39Bh | MD1CON0                       |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | CM4CON0                       | 19Ch | SP1BRGH                       | 21Ch | —                             | 29Ch | —                             | 31Ch  | MD2CON1                       | 39Ch | MD1CON1                       |

| 01Dh | T2HLT                         | 09Dh | ADCON0                        | 11Dh | CM4CON1                       | 19Dh | RC1STA                        | 21Dh | BORCON                        | 29Dh | —                             | 31Dh  | MD2SRC                        | 39Dh | MD1SRC                        |

| 01Eh | T2CLKCON                      | 09Eh | ADCON1                        | 11Eh | CM4NSEL                       | 19Eh | TX1STA                        | 21Eh | FVRCON                        | 29Eh | CCPTMRS                       | 31Eh  | MD2CARL                       | 39Eh | MD1CARL                       |

| 01Fh | T2RST                         | 09Fh | ADCON2                        | 11Fh | CM4PSEL                       | 19Fh | BAUD1CON                      | 21Fh | ZCD1CON                       | 29Fh | —                             | 31Fh  | MD2CARH                       | 39Fh | MD1CARH                       |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h  | General Pur-                  | 3A0h |                               |

|      | Quanta                        |      | Osmannl                       |      | Osasas                        |      | Quantal                       |      | 0                             |      | 0                             | 32Fh  | pose Register<br>16 Bytes     |      |                               |

|      | General<br>Purpose            | 330h  | TO Dytes                      |      | Unimplemented                 |

|      | Register                      | 00011 | Unimplemented                 |      | Read as '0'                   |

|      | 80 Bytes                      |       | Unimplemented<br>Read as '0'  |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh  |                               | 3EFh |                               |

| 070h |                               | 0F0h |                               | 170h |                               | 1F0h |                               | 270h | L                             | 2F0h | L                             | 370h  |                               | 3F0h |                               |

|      | Common RAM                    |      | Accesses                      |       | Accesses                      |      | Accesses                      |

|      | 70h-7Fh                       |       | 70h-7Fh                       |      | 70h-7Fh                       |

| 07Fh |                               | 0FFh |                               | 17Fh |                               | 1FFh |                               | 27Fh |                               | 2FFh |                               | 37Fh  |                               | 3FFh |                               |

Legend: 🔲 = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1768.

# 4.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

4.7 Register Definitions: Device and Revision

## REGISTER 4-3: DEVID: DEVICE ID REGISTER

|   | R      | R | R    | R     | R | R     |

|---|--------|---|------|-------|---|-------|

|   |        |   | DEV< | 13:8> |   |       |

|   | bit 13 |   |      |       |   | bit 8 |

|   |        |   |      |       |   |       |

| R | R      | R | R    | R     | R | R     |

DEV<7:0>

'1' = Bit is set

bit 7

# Legend:

R = Readable bit

R

'0' = Bit is cleared

### bit 13-0 **DEV<13:0>**: Device ID bits

| Device      | DEVID<13:0> Values                 |

|-------------|------------------------------------|

| PIC16F1764  | 11 0000 1000 0000 ( <b>3080h</b> ) |

| PIC16F1765  | 11 0000 1000 0001 ( <b>3081h</b> ) |

| PIC16F1768  | 11 0000 1000 0100 ( <b>3084h</b> ) |

| PIC16F1769  | 11 0000 1000 0101 ( <b>3085h</b> ) |

| PIC16LF1764 | 11 0000 1000 0010 ( <b>3082h</b> ) |

| PIC16LF1765 | 11 0000 1000 0011 ( <b>3083h</b> ) |

| PIC16LF1768 | 11 0000 1000 0110 ( <b>3086h</b> ) |

| PIC16LF1769 | 11 0000 1000 0111 ( <b>3087h</b> ) |

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

bit 0

E.

| R/W-0/0               | R/W-0/0       | R/W-0/0                                 | R/W-0/0       | R/W-0/0                   | R/W-0/0         | R/W-0/0          | R/W-0/0     |

|-----------------------|---------------|-----------------------------------------|---------------|---------------------------|-----------------|------------------|-------------|

| PWM6IE <sup>(1)</sup> | PWM5IE        | COG1IE                                  | ZCDIE         | COG2IE <sup>(1)</sup>     | CLC3IE          | CLC2IE           | CLC1IE      |

| bit 7                 |               |                                         |               |                           |                 |                  | bit (       |

|                       |               |                                         |               |                           |                 |                  |             |

| Legend:               |               |                                         |               |                           |                 |                  |             |

| R = Readable          |               | W = Writable                            |               |                           |                 |                  |             |

| u = Bit is unch       | anged         | x = Bit is unkr                         |               | •                         | ented bit, read |                  |             |

| '1' = Bit is set      |               | '0' = Bit is cle                        | ared          | -n/n = Value a            | t POR and BO    | R/Value at all o | ther Resets |

| bit 7                 |               | VM6 Interrupt E                         | nable bit(1)  |                           |                 |                  |             |

|                       |               | nterrupt is enab                        |               |                           |                 |                  |             |

|                       |               | nterrupt is disab                       |               |                           |                 |                  |             |

| bit 6                 | PWM5IE: PV    | VM5 Interrupt E                         | nable bit     |                           |                 |                  |             |

|                       |               | nterrupt is enab                        |               |                           |                 |                  |             |

|                       |               | nterrupt is disab                       |               |                           |                 |                  |             |

| bit 5                 |               | G1 Auto-Shutd                           | -             | Enable bit                |                 |                  |             |

|                       |               | nterrupt is enable<br>nterrupt is disab |               |                           |                 |                  |             |

| bit 4                 |               | -Cross Detectio                         |               | able bit                  |                 |                  |             |

|                       |               | errupt is enable                        | •             |                           |                 |                  |             |

|                       | 0 = ZCD inte  | errupt is disable                       | d             |                           |                 |                  |             |

| bit 3                 | COG2IE: CO    | G2 Auto-Shutd                           | own Interrupt | Enable bit <sup>(1)</sup> |                 |                  |             |

|                       |               | nterrupt is enable<br>Iterrupt is disab |               |                           |                 |                  |             |

| bit 2                 |               | C3 Interrupt Ena                        |               |                           |                 |                  |             |

|                       |               | terrupt is enable                       |               |                           |                 |                  |             |

|                       |               | terrupt is disabl                       |               |                           |                 |                  |             |

| bit 1                 | CLC2IE: CLC   | C2 Interrupt Ena                        | able bit      |                           |                 |                  |             |

|                       |               | terrupt is enable                       |               |                           |                 |                  |             |

|                       |               | terrupt is disabl                       |               |                           |                 |                  |             |

| bit 0                 |               | C1 Interrupt Ena                        |               |                           |                 |                  |             |

|                       |               | terrupt is enable<br>terrupt is disabl  |               |                           |                 |                  |             |

|                       |               |                                         |               |                           |                 |                  |             |

| Note 1: PIC           | C16(L)F1768/9 | only.                                   |               |                           |                 |                  |             |

# REGISTER 7-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

# 22.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt-on-rollover, you must set these bits:

- ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 22.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- SYNC bit of the T1CON register must be set

- CS<1:0> bits of the T1CON register must be configured

- OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

The secondary oscillator will continue to operate in Sleep regardless of the SYNC bit setting.

# 22.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be an Auto-conversion Trigger.

For more information, see Section 24.0 "Capture/Compare/PWM Modules".

# 22.10 CCP Auto-Conversion Trigger

When any of the CCPs are configured to trigger an auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of Timer1 can cause an Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with an Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see Section 24.2.1 "Auto-Conversion Trigger".

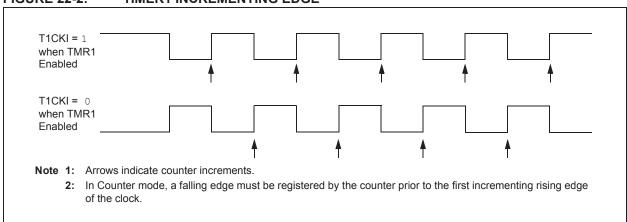

# FIGURE 22-2: TIMER1 INCREMENTING EDGE

# 23.5 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE1 register. Interrupt timing is illustrated in Figure 23-3.

# FIGURE 23-3: TIMER2 PRESCALER, POSTSCALER AND INTERRUPT TIMING DIAGRAM

| r               | Rev. 10-000205A<br>47/2016 |

|-----------------|----------------------------|

| CKPS            | 0b010                      |

| PRx             | 1                          |

| OUTPS           | 0b0001                     |

| TMRx_clk        |                            |

| TMRx            |                            |

| TMRx_postscaled |                            |

| TMRxIF          | (1) (2) (1)                |

|                 |                            |

# REGISTER 26-7: PWMxPHH: PWMx PHASE COUNT HIGH REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | PH<     | :15:8>         |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     |                |                  |                  |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | U = Unimpler   | mented bit, read | d as '0'         |              |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

|                  |         |                   |         |                |                  |                  |              |

bit 7-0 **PH<15:8>**: PWMx Phase High bits Upper eight bits of PWMx phase count.

# REGISTER 26-8: PWMxPHL: PWMx PHASE COUNT LOW REGISTER

| R/W-x/u        | R/W-x/u | R/W-x/u        | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------|---------|----------------|---------|---------|---------|---------|---------|

|                |         |                | PH<     | 7:0>    |         |         |         |

| bit 7          |         |                |         |         |         |         | bit 0   |

|                |         |                |         |         |         |         |         |

| Legend:        |         |                |         |         |         |         |         |

| D - Doodoblo b | i+      | M - Mritabla k | sit     |         |         |         |         |

| R = Readable bit     | vv = vvritable bit   |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-0 **PH<7:0>**: PWMx Phase Low bits Lower eight bits of PWMx phase count.

# 27.0 COMPLEMENTARY OUTPUT GENERATOR (COG) MODULE

The primary purpose of the Complementary Output Generator (COG) is to convert a single output PWM signal into a two-output complementary PWM signal. The COG can also convert two separate input events into a single or complementary PWM output.

The COG PWM frequency and duty cycle are determined by a rising event input and a falling event input. The rising event and falling event may be the same source. Sources may be synchronous or asynchronous to the COG\_clock.

The rate at which the rising event occurs determines the PWM frequency. The time from the rising event to the falling event determines the duty cycle.

A selectable clock input is used to generate the phase delay, blanking and dead-band times. Dead-band time can also be generated with a programmable delay chain, which is independent from all clock sources.

Simplified block diagrams of the various COG modes are shown in Figure 27-2 through Figure 27-6.

The COG module has the following features:

- Six modes of operation:

- Steered PWM mode

- Synchronous Steered PWM mode

- Forward Full-Bridge mode

- Reverse Full-Bridge mode

- Half-Bridge mode

- Push-Pull mode

- Selectable COG\_clock clock source

- Independently selectable rising event sources

- · Independently selectable falling event sources

- Independently selectable edge or level event sensitivity

- Independent output polarity selection

- Phase delay with independent rising and falling delay times

- Dead-band control with:

- independent rising and falling event dead-band times

- Synchronous and asynchronous timing

- Blanking control with independent rising and falling event blanking times

- · Auto-shutdown control with:

- Independently selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control (high, low, off and High-Z)

# 27.1 Output to Pins (all modes)

The COG peripheral has four outputs: COGA, COGB, COGC and COGD.

The operating mode, selected with the MD<2:0> bits of the COGxCON0 register, determines the waveform available at each output. An individual peripheral source control for each device pin selects the pin or pins at which the outputs will appear. Please refer to the RxyPPS register (Register 12-2) for more information.

# 27.2 Event-Driven PWM (All Modes)

Besides generating PWM and complementary outputs from a single PWM input, the COG can also generate PWM waveforms from a periodic rising event and a separate falling event. In this case, the falling event is usually derived from analog feedback within the external PWM driver circuit. In this configuration, high-power switching transients may trigger a false falling event that needs to be blanked out. The COG can be configured to blank falling (and rising) event inputs for a period of time immediately following the rising (and falling) event drive output. This is referred to as input blanking and is covered in Section 27.8 "Blanking Control".

It may be necessary to guard against the possibility of external circuit Faults. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in Section 27.10 "Auto-Shutdown Control".

The COG can be configured to operate in phase delayed conjunction with another PWM. The active drive cycle is delayed from the rising event by a phase delay timer. Phase delay is covered in more detail in **Section 27.9 "Phase Delay"**.

A typical operating waveform, with phase delay and dead band, generated from a single CCP1 input is shown in Figure 27-10.

16(L)F1764/5/8/9

# 32.7 BAUD RATE GENERATOR

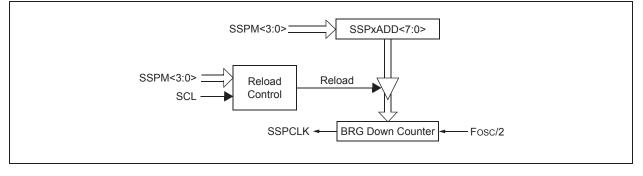

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPxADD register (Register 32-6). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 32-40 triggers the value from SSPxADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 32-4demonstratesclockratesbasedoninstructioncyclesandtheBRGvalueloadedintoSSPxADD.

## EQUATION 32-1:

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

# FIGURE 32-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPxADD when used as a Baud Rate Generator for I<sup>2</sup>C; this is an implementation limitation.

# TABLE 32-4: MSSP CLOCK RATE w/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 36-10 and Figure 36-7 to ensure the system is designed to support I/O timing requirements.

| R/W-0/0          | R/W-0/0                                                             | R/W-0/0                                                               | R/W-0/0                            | R/W-0/0         | R-0/0                                | R-0/0            | R-0/0        |  |  |  |

|------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------|-----------------|--------------------------------------|------------------|--------------|--|--|--|

| SPEN             | RX9                                                                 | SREN                                                                  | CREN                               | ADDEN           | FERR                                 | OERR             | RX9D         |  |  |  |

| bit 7            | ·                                                                   |                                                                       |                                    |                 |                                      |                  | bit C        |  |  |  |

|                  |                                                                     |                                                                       |                                    |                 |                                      |                  |              |  |  |  |

| Legend:          |                                                                     |                                                                       |                                    |                 |                                      |                  |              |  |  |  |

| R = Readable     | e bit                                                               | W = Writable                                                          | bit                                |                 |                                      |                  |              |  |  |  |

| u = Bit is uncl  | nanged                                                              | x = Bit is unk                                                        | nown                               | U = Unimple     | mented bit, read                     | as '0'           |              |  |  |  |

| '1' = Bit is set |                                                                     | '0' = Bit is cle                                                      | ared                               | -n/n = Value    | at POR and BO                        | R/Value at all o | other Resets |  |  |  |

| 1.1.7            |                                                                     |                                                                       |                                    |                 |                                      |                  |              |  |  |  |

| bit 7            |                                                                     | I Port Enable b                                                       | IT                                 |                 |                                      |                  |              |  |  |  |

|                  |                                                                     | ort is enabled<br>ort is disabled (l                                  | neld in Reset)                     |                 |                                      |                  |              |  |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R                                                 | eceive Enable I                                                       | oit                                |                 |                                      |                  |              |  |  |  |

|                  |                                                                     | 9-bit reception<br>8-bit reception                                    |                                    |                 |                                      |                  |              |  |  |  |

| bit 5            | SREN: Singl                                                         | e Receive Enal                                                        | ole bit                            |                 |                                      |                  |              |  |  |  |

|                  | Asynchronous mode:<br>Don't care.                                   |                                                                       |                                    |                 |                                      |                  |              |  |  |  |

|                  | 1 = Enables<br>0 = Disables                                         | s mode – Maste<br>single receive<br>single receive<br>ared after rece |                                    | ete.            |                                      |                  |              |  |  |  |

|                  |                                                                     | s mode – Slave                                                        |                                    |                 |                                      |                  |              |  |  |  |

| bit 4            | CREN: Conti                                                         | inuous Receive                                                        | Enable bit                         |                 |                                      |                  |              |  |  |  |

|                  | Asynchronous mode:<br>1 = Enables receiver<br>0 = Disables receiver |                                                                       |                                    |                 |                                      |                  |              |  |  |  |

|                  |                                                                     |                                                                       |                                    | ble bit, CREN,  | is cleared (CRE                      | N overrides SF   | REN)         |  |  |  |

| bit 3            | ADDEN: Add                                                          | dress Detect Er                                                       | able bit                           |                 |                                      |                  |              |  |  |  |

|                  | 1 = Enables<br>0 = Disables                                         | address detec                                                         | tion, enables i<br>tion, all bytes | •               | ads the receive<br>and ninth bit can |                  |              |  |  |  |

|                  | Asynchronous mode, 8-bit (RX9 = 0):<br>Don't care.                  |                                                                       |                                    |                 |                                      |                  |              |  |  |  |

| bit 2            | FERR: Fram                                                          | ing Error bit                                                         |                                    |                 |                                      |                  |              |  |  |  |

|                  |                                                                     | error (can be u                                                       | pdated by rea                      | ading RCxREG    | Fregister and re                     | ceiving next va  | lid byte)    |  |  |  |

| bit 1            | OERR: Over                                                          | run Error bit                                                         |                                    |                 |                                      |                  |              |  |  |  |

|                  | 1 = Overrun<br>0 = No overr                                         | error (can be c<br>run error                                          | leared by clea                     | aring bit, CREN | 1)                                   |                  |              |  |  |  |

| bit 0            | RX9D: Ninth                                                         | bit of Received                                                       | l Data                             |                 |                                      |                  |              |  |  |  |

|                  |                                                                     |                                                                       |                                    |                 | calculated by us                     |                  |              |  |  |  |

# REGISTER 33-2: RC1STA: RECEIVE STATUS AND CONTROL REGISTER

# PIC16(L)F1764/5/8/9

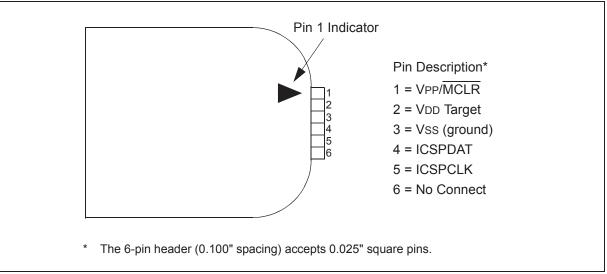

# FIGURE 34-2: PICkit<sup>™</sup> PROGRAMMER STYLE CONNECTOR INTERFACE

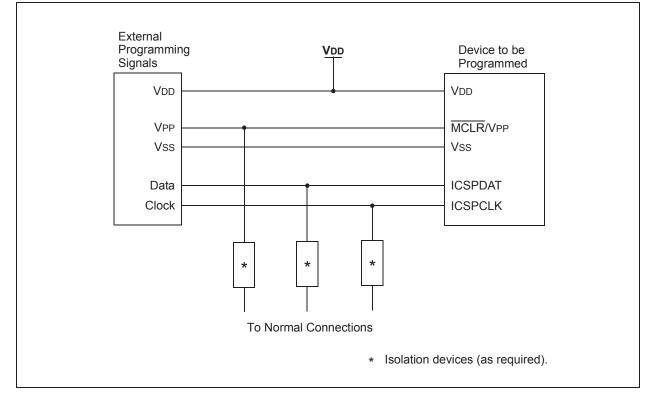

# FIGURE 34-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

# PIC16(L)F1764/5/8/9

| CALL             | Call Subroutine                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<6:3>) \rightarrow PC<14:11> \end{array}$                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                   |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits<10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT       | Clear Watchdog Timer                                                                                                                                                                     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:      | [label] CLRWDT                                                                                                                                                                           |

| Operands:    | None                                                                                                                                                                                     |

| Operation:   | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \overline{PD} \end{array}$ |

| Description: | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$<br>are set.                               |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                 |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $\begin{array}{l} (\text{PC}) +1 \rightarrow \text{TOS}, \\ (\text{W}) \rightarrow \text{PC} < 7:0 >, \\ (\text{PCLATH} < 6:0 >) \rightarrow \text{PC} < 14:8 > \end{array}$                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                   |  |  |  |  |  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W are loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                   |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

| CLRF             | Clear f                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                                                    |

| Operands:        | $0 \leq f \leq 127$                                                                        |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{(f)} \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                             |

| DECF             | Decrement f                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                              |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                      |

| Status Affected: | Z                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

# TABLE 36-15: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3,4)</sup>

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = 3.0V, TA = +25°C, Single-Ended, 2 μs TAD, VREF+ = 3V, VREF- = Vss |      |                                                   |      |      |      |       |                                                                                |  |

|----------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------------|--|

| Param<br>No.                                                                                                                     | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                                     |  |

| AD01                                                                                                                             | Nr   | Resolution                                        | -    | _    | 10   | bit   |                                                                                |  |

| AD02                                                                                                                             | EIL  | Integral Error                                    |      |      | ±1.7 | LSb   | VREF = 3.0V                                                                    |  |

| AD03                                                                                                                             | Edl  | Differential Error                                |      |      | ±1   | LSb   | No missing codes, VREF = 3.0V                                                  |  |

| AD04                                                                                                                             | EOFF | Offset Error                                      | _    | —    | ±2.5 | LSb   | VREF = 3.0V                                                                    |  |

| AD05                                                                                                                             | Egn  | Gain Error                                        | _    | —    | ±2.0 | LSb   | VREF = 3.0V                                                                    |  |

| AD06                                                                                                                             | Vref | Reference Voltage                                 | 1.8  |      | Vdd  | V     | VREF = (VREF+ – VREF-)                                                         |  |

| AD07                                                                                                                             | VAIN | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                                |  |

| AD08                                                                                                                             | Zain | Recommended Impedance of<br>Analog Voltage Source | -    | —    | 10   | kΩ    | Can go higher if external 0.01 $\mu\text{F}$ capacitor is present on input pin |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF+ pin, VDD pin or FVR, whichever is selected as reference input.

- 4: See Section 37.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

## TABLE 36-16: ADC CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |      |                                                                 |      |                 |      |       |                                        |  |