Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-11-                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x5b, 1x10b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1764t-i-sl |

TABLE 1-2: PIC16(L)F1764/5 PINOUT DESCRIPTION (CONTINUED)

| Name                    | Function              | Input<br>Type | Output<br>Type | Description                              |

|-------------------------|-----------------------|---------------|----------------|------------------------------------------|

| RC4/T3G/PRG1R/CLCIN1/CK | RC4                   | TTL/ST        | CMOS           | General purpose I/O.                     |

|                         | T3G <sup>(1)</sup>    | TTL/ST        | _              | Timer3 gate input.                       |

|                         | PRG1R <sup>(1)</sup>  | TTL/ST        | _              | Ramp generator set_rising input.         |

|                         | CLCIN1 <sup>(1)</sup> | TTL/ST        | _              | CLC Input 1.                             |

|                         | CK <sup>(1)</sup>     | TTL/ST        | _              | EUSART clock input.                      |

| RC5/T3CKI/PRG1F/CCP1/RX | RC5                   | TTL/ST        | CMOS           | General purpose I/O.                     |

|                         | T3CKI <sup>(1)</sup>  | TTL/ST        | _              | Timer3 clock input.                      |

|                         | PRG1F <sup>(1)</sup>  | TTL/ST        | _              | Ramp generator set_falling input.        |

|                         | CCP1 <sup>(1)</sup>   | TTL/ST        | _              | CCP1 capture input.                      |

|                         | RX <sup>(1,3)</sup>   | TTL/ST        | _              | EUSART receive input.                    |

| VDD                     | VDD                   | Power         | _              | Positive supply.                         |

| Vss                     | Vss                   | Power         | _              | Ground reference.                        |

| OUT <sup>(2)</sup>      | C10UT                 |               | CMOS           | Comparator 1 output.                     |

|                         | C2OUT                 |               | CMOS           | Comparator 2 output.                     |

|                         | CCP1                  |               | CMOS           | Compare/PWM1 output.                     |

|                         | MD10UT                |               | CMOS           | Data Signal Modulator 1 output.          |

|                         | PWM3                  |               | CMOS           | PWM3 output.                             |

|                         | PWM5                  |               | CMOS           | PWM5 output.                             |

|                         | COG1A                 |               | CMOS           | Complementary Output Generator Output A. |

|                         | COG1B                 |               | CMOS           | Complementary Output Generator Output B. |

|                         | COG1C                 |               | CMOS           | Complementary Output Generator Output C. |

|                         | COG1D                 |               | CMOS           | Complementary Output Generator Output D. |

|                         | SDA <sup>(3)</sup>    |               | OD             | I <sup>2</sup> C data output.            |

|                         | SCK                   |               | CMOS           | SPI clock output.                        |

|                         | SCL <sup>(3)</sup>    |               | OD             | I <sup>2</sup> C clock output.           |

|                         | SDO                   |               | CMOS           | SPI data output.                         |

|                         | TX                    |               | CMOS           | EUSART asynchronous TX data out.         |

|                         | CK                    |               | CMOS           | EUSART synchronous clock out.            |

|                         | DT <sup>(3)</sup>     |               | CMOS           | EUSART synchronous data output.          |

|                         | CLC10UT               |               | CMOS           | Configurable Logic Cell 1 output.        |

|                         | CLC2OUT               |               | CMOS           | Configurable Logic Cell 2 output.        |

|                         | CLC3OUT               |               | CMOS           | Configurable Logic Cell 3 output.        |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS Input Selection registers.

- 2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as peripheral digital outputs with the PPS Output Selection registers.

- 3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

#### 4.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See Section 10.4 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

#### 4.7 Register Definitions: Device and Revision

#### **REGISTER 4-3: DEVID: DEVICE ID REGISTER**

| R         | R | R | R | R | R     |  |  |  |  |

|-----------|---|---|---|---|-------|--|--|--|--|

| DEV<13:8> |   |   |   |   |       |  |  |  |  |

| bit 13    |   |   |   |   | bit 8 |  |  |  |  |

| R        | R | R | R | R | R | R | R |  |  |  |

|----------|---|---|---|---|---|---|---|--|--|--|

| DEV<7:0> |   |   |   |   |   |   |   |  |  |  |

| bit 7    |   |   |   |   |   |   |   |  |  |  |

| Legend:          |                  |                      |  |

|------------------|------------------|----------------------|--|

| R = Readable bit | '1' = Bit is set | '0' = Bit is cleared |  |

#### bit 13-0 **DEV<13:0>**: Device ID bits

| Device      | DEVID<13:0> Values                 |  |  |  |  |  |  |  |  |

|-------------|------------------------------------|--|--|--|--|--|--|--|--|

| PIC16F1764  | 11 0000 1000 0000 ( <b>3080h</b> ) |  |  |  |  |  |  |  |  |

| PIC16F1765  | 11 0000 1000 0001 ( <b>3081h</b> ) |  |  |  |  |  |  |  |  |

| PIC16F1768  | 11 0000 1000 0100 ( <b>3084h</b> ) |  |  |  |  |  |  |  |  |

| PIC16F1769  | 11 0000 1000 0101 ( <b>3085h</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1764 | 11 0000 1000 0010 ( <b>3082h</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1765 | 11 0000 1000 0011 ( <b>3083h</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1768 | 11 0000 1000 0110 ( <b>3086h</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1769 | 11 0000 1000 0111 ( <b>3087h</b> ) |  |  |  |  |  |  |  |  |

#### REGISTER 4-4: REVID: REVISION ID REGISTER

| R         | R | R | R | R | R     |  |  |  |  |

|-----------|---|---|---|---|-------|--|--|--|--|

| REV<13:8> |   |   |   |   |       |  |  |  |  |

| bit 13    |   |   |   |   | bit 8 |  |  |  |  |

| R         | R | R | R | R | R | R | R |  |  |  |

|-----------|---|---|---|---|---|---|---|--|--|--|

| REV<7:0>  |   |   |   |   |   |   |   |  |  |  |

| bit 7 bit |   |   |   |   |   |   |   |  |  |  |

| Legend:          |                  |                      |  |

|------------------|------------------|----------------------|--|

| R = Readable bit | '1' = Bit is set | '0' = Bit is cleared |  |

bit 13-0 **REV<13:0>**: Revision ID bits

TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7                 | Bit 6  | Bit 5  | Bit 4  | Bit 3                 | Bit 2               | Bit 1               | Bit 0                 | Register on Page |

|------------|-----------------------|--------|--------|--------|-----------------------|---------------------|---------------------|-----------------------|------------------|

| INTCON     | GIE                   | PEIE   | TMR0IE | INTE   | IOCIE                 | TMR0IF              | INTF                | IOCIF                 | 101              |

| OPTION_REG | WPUEN                 | INTEDG | TMR0CS | TMR0SE | PSA                   | PS<2:0>             |                     |                       | 214              |

| PIE1       | TMR1GIE               | ADIE   | RCIE   | TXIE   | SSP1IE                | CCP1IE              | TMR2IE              | TMR1IE                | 102              |

| PIE2       | OSFIE                 | C2IE   | C1IE   | _      | BCL1IE                | C4IE <sup>(1)</sup> | C3IE <sup>(1)</sup> | CCP2IE <sup>(1)</sup> | 103              |

| PIE3       | PWM6IE <sup>(1)</sup> | PWM5IE | COG1IE | ZCDIE  | COG2IE <sup>(1)</sup> | CLC3IE              | CLC2IE              | CLC1IE                | 104              |

| PIR1       | TMR1GIF               | ADIF   | RCIF   | TXIF   | SSP1IF                | CCP1IF              | TMR2IF              | TMR1IF                | 105              |

| PIR2       | OSFIF                 | C2IF   | C1IF   | _      | BCL1IF                | C4IF <sup>(1)</sup> | C3IF <sup>(1)</sup> | CCP2IF <sup>(1)</sup> | 106              |

| PIR3       | PWM6IF <sup>(1)</sup> | PWM5IF | COG1IF | ZCDIF  | COG2IF <sup>(1)</sup> | CLC3IF              | CLC2IF              | CLC1IF                | 107              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

Note 1: PIC16(L)F1768/9 only.

# 20.0 ZERO-CROSS DETECTION (ZCD) MODULE

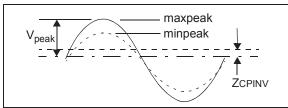

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, ZCPINV, which is typically 0.75V above ground.

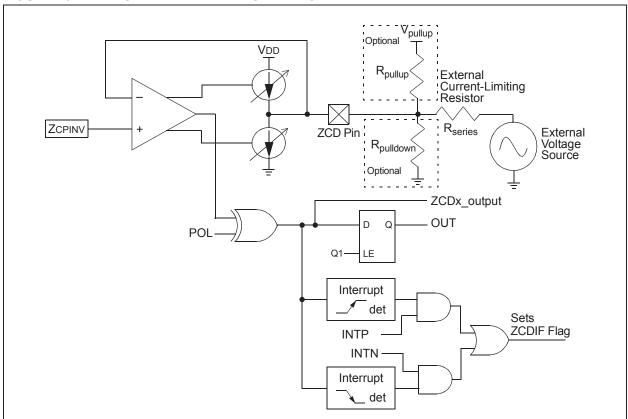

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram (Figure 20-2).

The ZCD module is useful when monitoring an AC waveform for, but not limited to, the following purposes:

- · A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- · Low EMI cycle switching

#### 20.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu A$ . Refer to Equation 20-1 and Figure 20-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it doesn't interfere with the current source and sink.

#### **EQUATION 20-1: EXTERNAL RESISTOR**

$$R_{series} = \frac{V_{peak}}{3 \times 10^{-4}}$$

FIGURE 20-1: EXTERNAL VOLTAGE

FIGURE 20-2: SIMPLIFIED ZCD BLOCK DIAGRAM

#### 24.4 CCP/PWM Clock Selection

The PIC16(L)F1764/5/8/9 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2/4/6), the PWM mode on the CCP and PWM modules can use any of these timers.

The CCPTMRS register is used to select which timer is used.

### 24.4.1 USING THE TMR2/4/6 WITH THE CCP MODULE

This device has a new version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than older parts. Refer to **Section 23.6 "Operation Examples"** for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the Fosc/4 clock source selected.

#### 24.4.2 PWM PERIOD

The PWM period is specified by the T2PR/T4PR/T6PR register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

#### **EQUATION 24-1: PWM PERIOD**

$$PWM \ Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$$

$(TMR2 \ Prescale \ Value)$

Note 1: Tosc = 1/Fosc.

When TMR2/4/6 is equal to its respective T2PR/T4PR/T6PR register, the following three events occur on the next increment cycle:

- · TMR2/4/6 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from the CCPRxH:CCPRxL pair into the internal 10-bit latch.

**Note:** The Timer postscaler (see Figure 24-1) is not used in the determination of the PWM frequency.

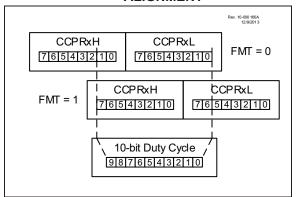

#### 24.4.3 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to two registers: the CCPRxH:CCPRxL register pair. Where the particular bits go is determined by the FMT bit of the CCPxCON register. If FMT = 0, the two Most Significant bits of the duty cycle value should be written to bits<1:0> of the CCPRxH register and the remaining eight bits to the CCPRxL register. If FMT = 1, the Least Significant two bits of the duty cycle should be written to bits<7:6> of the CCPRxL register and the Most Significant eight bits to the CCPRxH register. This is illustrated in Figure 24-4. These bits can be written at any time. The duty cycle value is not latched into the internal latch until after the period completes (i.e., a match between T2PR/T4PR/T6PR and TMR2/4/6 registers occurs).

Equation 24-2 is used to calculate the PWM pulse width. Equation 24-3 is used to calculate the PWM duty cycle ratio.

#### **EQUATION 24-2: PULSE WIDTH**

#### **EQUATION 24-3: DUTY CYCLE RATIO**

$$Duty\ Cycle\ Ratio\ =\ \frac{(CCPRxH:CCPRxL)}{4(PRx+I)}$$

The PWM Duty Cycle registers are double-buffered for glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the internal buffer register, then the CCPx pin is cleared (see Figure 24-3).

### FIGURE 24-4: CCPx DUTY CYCLE ALIGNMENT

#### 24.4.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when T2PR/T4PR/T6PR is 255. The resolution is a function of the T2PR/T4PR/T6PR register value as shown by Equation 24-4.

#### **EQUATION 24-4: PWM RESOLUTION**

Resolution =

$$\frac{log[4(PR2 + 1)]}{log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

#### TABLE 24-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| T2PR Value                | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6         |

#### TABLE 24-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| T2PR Value                | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 24.4.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 24.4.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 24.4.7 PWM OUTPUT

The output of the CCP in PWM mode is the PWM signal generated by the module and described above. This output is available to the following peripherals:

- · ADC trigger

- COG

- PRG

- DSM

- CLC

- · Op amp override

- · Timer2/4/6 Reset

- · Any device pins

# 25.0 10-BIT PULSE-WIDTH MODULATION (PWM) MODULE

The 10-bit PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period and resolution that are configured by the following registers:

- T2PR

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

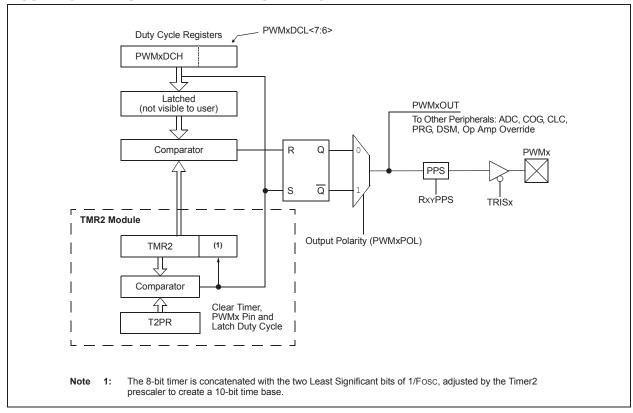

Figure 25-1 shows a simplified block diagram of PWM operation.

Figure 25-2 shows a typical waveform of the PWM signal.

#### FIGURE 25-1: SIMPLIFIED PWM BLOCK DIAGRAM

#### 26.3 Offset Modes

The Offset modes provide the means to adjust the waveform of a slave PWM module relative to the waveform of a master PWM module in the same device.

#### 26.3.1 INDEPENDENT RUN MODE

In Independent Run mode (OFM<1:0> = 00), the PWM module is unaffected by the other PWM modules in the device. The PWMxTMR associated with the PWM module in this mode starts counting as soon as the EN bit associated with this PWM module is set, and continues counting until the EN bit is cleared. Period events reset the PWMxTMR to zero, after which, the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-8.

### 26.3.2 SLAVE RUN MODE WITH SYNC START

In Slave Run mode with Sync Start (OFM<1:0> = 01), the slave PWMxTMR waits for the master's OF\_match event. When this event occurs, if the EN bit is set, the PWMxTMR begins counting and continues to count until software clears the EN bit. Slave period events reset the PWMxTMR to zero, after which, the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-9.

### 26.3.3 ONE-SHOT SLAVE MODE WITH SYNC START

In One-Shot Slave mode with Synchronous Start (OFM<1:0> = 10), the slave PWMxTMR waits until the master's OF\_match event. The timer then begins counting, starting from the value that is already in the timer, and continues to count until the period match event. When the period event occurs, the timer resets to zero and stops counting. The timer then waits until the next master OF\_match event, after which, it begins counting again to repeat the cycle. An OF\_match event that occurs before the slave PWM has completed the triggered period will be ignored. A slave period that is greater than the master period, but less that twice the master period, will result in a slave output every other master period.

Note: During the time the slave timers are resetting to zero, if another offset match event is received, it is possible that the slave PWM would not recognize this match event and the slave timers would fail to begin counting again. This would result in missing duty cycles in the output of the slave PWM. To prevent this from happening, avoid using the same period for both the master and slave PWMs.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-10.

# 26.3.4 CONTINUOUS RUN SLAVE MODE WITH SYNC START AND TIMER RESET

In Continuous Run Slave mode with Synchronous Start and Timer Reset (OFM<1:0> = 11), the slave PWMxTMR is inhibited from counting after the slave PWM enable is set. The first master OF\_match event starts the slave PWMxTMR. Subsequent master OF\_match events reset the slave PWMxTMR timer value back to 1, after which, the slave PWMxTMR continues to count. The next master OF\_match event resets the slave PWMxTMR back to 1 to repeat the cycle. Slave period events that occur before the master's OF\_match event will reset the slave PWMxTMR to zero, after which, the timer will continue to count. Slaves operating in this mode must have a PWMxPH register pair value equal to, or greater than, 1; otherwise, the phase match event will not occur precluding the start of the PWM output duty cycle.

The offset timing will persist if both the master and slave PWMxPR values are the same and the Slave Offset mode is changed to Independent Run mode while the PWM module is operating.

A detailed timing diagram of this mode used in Standard PWM mode is shown in Figure 26-11.

**Note:** Unexpected results will occur if the slave PWM\_clock is a higher frequency than the master PWM\_clock.

### 26.3.5 OFFSET MATCH IN CENTER-ALIGNED MODE

When a master is operating in Center-Aligned mode, the offset match event depends on which direction the PWMxTMR is counting. Clearing the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting up. Setting the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting down. The OFO bit is ignored in Non-Center-Aligned modes.

The OFO bit is double-buffered and requires setting the LDA bit to take effect when the PWM module is operating.

Detailed timing diagrams of Center-Aligned mode using offset match control in Independent Slave with Sync Start mode can be seen in Figure 26-12 and Figure 26-13.

# 27.0 COMPLEMENTARY OUTPUT GENERATOR (COG) MODULE

The primary purpose of the Complementary Output Generator (COG) is to convert a single output PWM signal into a two-output complementary PWM signal. The COG can also convert two separate input events into a single or complementary PWM output.

The COG PWM frequency and duty cycle are determined by a rising event input and a falling event input. The rising event and falling event may be the same source. Sources may be synchronous or asynchronous to the COG\_clock.

The rate at which the rising event occurs determines the PWM frequency. The time from the rising event to the falling event determines the duty cycle.

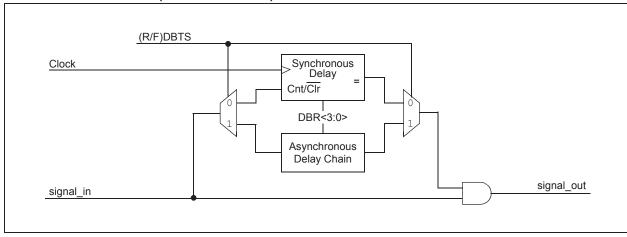

A selectable clock input is used to generate the phase delay, blanking and dead-band times. Dead-band time can also be generated with a programmable delay chain, which is independent from all clock sources.

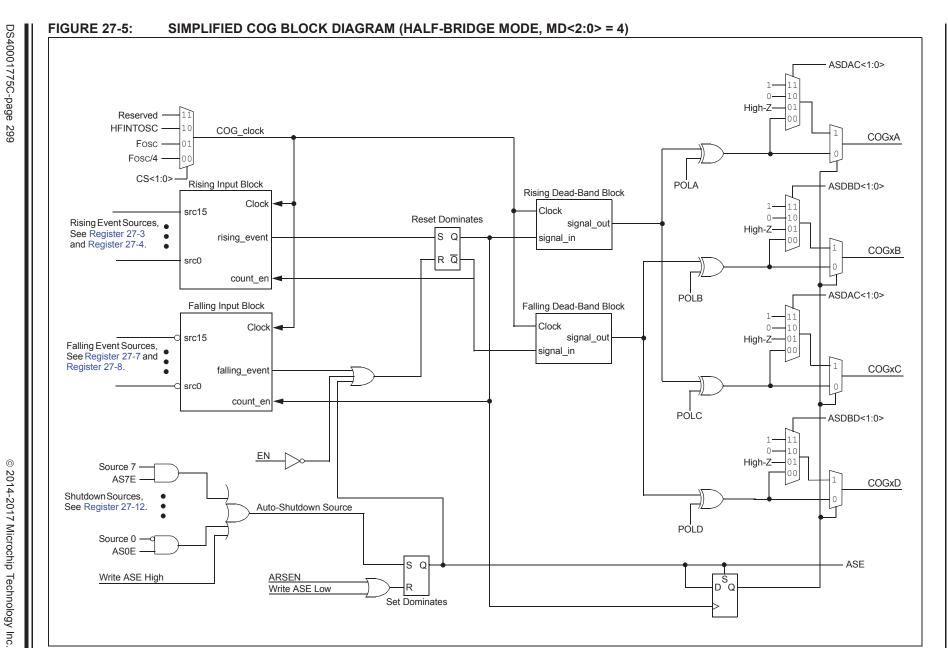

Simplified block diagrams of the various COG modes are shown in Figure 27-2 through Figure 27-6.

The COG module has the following features:

- Six modes of operation:

- Steered PWM mode

- Synchronous Steered PWM mode

- Forward Full-Bridge mode

- Reverse Full-Bridge mode

- Half-Bridge mode

- Push-Pull mode

- Selectable COG clock clock source

- Independently selectable rising event sources

- Independently selectable falling event sources

- Independently selectable edge or level event sensitivity

- Independent output polarity selection

- Phase delay with independent rising and falling delay times

- · Dead-band control with:

- independent rising and falling event dead-band times

- Synchronous and asynchronous timing

- Blanking control with independent rising and falling event blanking times

- Auto-shutdown control with:

- Independently selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control (high, low, off and High-Z)

#### 27.1 Output to Pins (all modes)

The COG peripheral has four outputs: COGA, COGB, COGC and COGD.

The operating mode, selected with the MD<2:0> bits of the COGxCON0 register, determines the waveform available at each output. An individual peripheral source control for each device pin selects the pin or pins at which the outputs will appear. Please refer to the RxyPPS register (Register 12-2) for more information.

#### 27.2 Event-Driven PWM (All Modes)

Besides generating PWM and complementary outputs from a single PWM input, the COG can also generate PWM waveforms from a periodic rising event and a separate falling event. In this case, the falling event is usually derived from analog feedback within the external PWM driver circuit. In this configuration, high-power switching transients may trigger a false falling event that needs to be blanked out. The COG can be configured to blank falling (and rising) event inputs for a period of time immediately following the rising (and falling) event drive output. This is referred to as input blanking and is covered in Section 27.8 "Blanking Control".

It may be necessary to guard against the possibility of external circuit Faults. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in Section 27.10 "Auto-Shutdown Control".

The COG can be configured to operate in phase delayed conjunction with another PWM. The active drive cycle is delayed from the rising event by a phase delay timer. Phase delay is covered in more detail in **Section 27.9 "Phase Delay"**.

A typical operating waveform, with phase delay and dead band, generated from a single CCP1 input is shown in Figure 27-10.

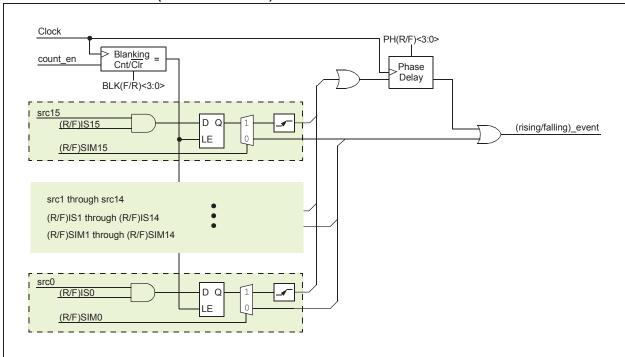

FIGURE 27-7: COG (RISING/FALLING) INPUT BLOCK

#### FIGURE 27-8: COG (RISING/FALLING) DEAD-BAND BLOCK

#### REGISTER 27-3: COGxRIS0: COGx RISING EVENT INPUT SELECTION REGISTER 0

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RIS7    | RIS6    | RIS5    | RIS4    | RIS3    | RIS2    | RIS1    | RIS0    |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Leg | end: |

|-----|------|

|-----|------|

$R = Readable \ bit \\ u = Bit \ is \ unchanged \\ x = Bit \ is \ unknown \\ U = Unimplemented \ bit, \ read \ as \ `0`$

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

| bit 7 | RIS7: COGx Rising Event Input Source 7 Enable bit                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = PWM3 output is enabled as a rising event input</li><li>0 = PWM3 output has no effect on the rising event</li></ul>                                                    |

| bit 6 | RIS6: COGx Rising Event Input Source 6 Enable bit                                                                                                                                 |

|       | <ul><li>1 = CCP2 output is enabled as a rising event input</li><li>0 = CCP2 output has no effect on the rising event</li></ul>                                                    |

| bit 5 | RIS5: COGx Rising Event Input Source 5 Enable bit                                                                                                                                 |

|       | <ul><li>1 = CCP1 output is enabled as a rising event input</li><li>0 = CCP1 output has no effect on the rising event</li></ul>                                                    |

| bit 4 | RIS4: COGx Rising Event Input Source 4 Enable bit                                                                                                                                 |

|       | <ul><li>1 = Comparator 4 output is enabled as a rising event input</li><li>0 = Comparator 4 output has no effect on the rising event</li></ul>                                    |

| bit 3 | RIS3: COGx Rising Event Input Source 3 Enable bit                                                                                                                                 |

|       | <ul><li>1 = Comparator 3 output is enabled as a rising event input</li><li>0 = Comparator 3 output has no effect on the rising event</li></ul>                                    |

| bit 2 | RIS2: COGx Rising Event Input Source 2 Enable bit                                                                                                                                 |

|       | <ul><li>1 = Comparator 2 output is enabled as a rising event input</li><li>0 = Comparator 2 output has no effect on the rising event</li></ul>                                    |

| bit 1 | RIS1: COGx Rising Event Input Source 1 Enable bit                                                                                                                                 |

|       | <ul><li>1 = Comparator 1 output is enabled as a rising event input</li><li>0 = Comparator 1 output has no effect on the rising event</li></ul>                                    |

| bit 0 | RIS0: COGx Rising Event Input Source 0 Enable bit                                                                                                                                 |

|       | <ul> <li>1 = Pin selected with COGxINPPS register is enabled as rising event input</li> <li>0 = Pin selected with COGxINPPS register has no effect on the rising event</li> </ul> |

#### REGISTER 27-12: COGxASD1: COGx AUTO-SHUTDOWN CONTROL REGISTER 1

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| AS7E    | AS6E    | AS5E    | AS4E    | AS3E    | AS2E    | AS1E    | AS0E    |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | AS7E: COGx Auto-shutdown Source Enable bit 7  1 = COGx is shutdown when Timer4_output is high  0 = Timer4_output has no effect on shutdown                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | AS6E: COGx Auto-shutdown Source Enable bit 6  1 = COGx is shutdown when Timer2_output is high                                                                                          |

| bit 5 | 0 = Timer2_output has no effect on shutdown  AS5E: COGx Auto-shutdown Source Enable bit 5  1 = COGx is shutdown when CLC LC2_out is low  0 = CLC2 output has no effect on shutdown     |

| bit 4 | AS4E: COGx Auto-shutdown Source Enable bit 4  1 = COGx is shutdown when Comparator sync_C4OUT is low  0 = Comparator 4 output has no effect on shutdown                                |

| bit 3 | AS3E: COGx Auto-shutdown Source Enable bit 3  1 = COGx is shutdown when Comparator sync_C3OUT is low  0 = Comparator 3 output has no effect on shutdown                                |

| bit 2 | AS2E: COGx Auto-shutdown Source Enable bit 2  1 = COGx is shutdown when Comparator sync_C2OUT is low  0 = Comparator 2 output has no effect on shutdown                                |

| bit 1 | AS1E: COGx Auto-shutdown Source Enable bit 1  1 = COGx is shutdown when comparator sync_C10UT is low  0 = Comparator 1 output has no effect on shutdown                                |

| bit 0 | AS0E: COGx Auto-shutdown Source Enable bit 0  1 = COGx is shutdown when pin selected with COGxINPPS register is low 0 = Pin selected with COGxINPPS register has no effect on shutdown |

#### REGISTER 28-10: CLCxGLS3: CLCx GATE 4 LOGIC SELECT REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| G4D4T   | G4D4N   | G4D3T   | G4D3N   | G4D2T   | G4D2N   | G4D1T   | G4D1N   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7 G4D4T: Gate 4 Data 4 True (non-inverted) bit

1 = d4T is gated into g40 = d4T is not gated into g4

bit 6 G4D4N: Gate 4 Data 4 Negated (inverted) bit

1 = d4N is gated into g40 = d4N is not gated into g4

bit 5 G4D3T: Gate 4 Data 3 True (non-inverted) bit

1 = d3T is gated into g4 0 = d3T is not gated into g4

bit 4 G4D3N: Gate 4 Data 3 Negated (inverted) bit

1 = d3N is gated into g40 = d3N is not gated into g4

bit 3 G4D2T: Gate 4 Data 2 True (non-inverted) bit

1 = d2T is gated into g40 = d2T is not gated into g4

bit 2 G4D2N: Gate 4 Data 2 Negated (inverted) bit

1 = d2N is gated into g40 = d2N is not gated into g4

bit 1 G4D1T: Gate 4 Data 1 True (non-inverted) bit

1 = d1T is gated into g4 0 = d1T is not gated into g4

bit 0 G4D1N: Gate 4 Data 1 Negated (inverted) bit

1 = d1N is gated into g40 = d1N is not gated into g4

#### REGISTER 32-1: SSP1STAT: MSSP STATUS REGISTER (CONTINUED)

bit 0 **BF:** Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes):

1 = Receive is complete, SSPxBUF is full

0 = Receive is not complete, SSPxBUF is empty

Transmit (I<sup>2</sup>C mode only):

1 = Data transmit is in progress (does not include the  $\overline{ACK}$  and Stop bits), SSPxBUF is full

0 = Data transmit is complete (does not include the ACK and Stop bits), SSPxBUF is empty

#### REGISTER 33-3: BAUD1CON: BAUD RATE CONTROL REGISTER

| R-0/0  | R-1/1 | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|--------|-------|-----|---------|---------|-----|---------|---------|

| ABDOVF | RCIDL | _   | SCKP    | BRG16   | _   | WUE     | ABDEN   |

| bit 7  |       |     |         |         |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7 ABDOVF: Auto-Baud Detect Overflow bit

Asynchronous mode:

1 = Auto-baud timer overflowed0 = Auto-baud timer did not overflow

Synchronous mode:

Don't care.

bit 6 RCIDL: Receive Idle Flag bit

<u>Asynchronous mode:</u> 1 = Receiver is Idle

0 = Start bit has been received and the receiver is receiving

Synchronous mode:

Don't care.

bit 5 **Unimplemented:** Read as '0'

bit 4 SCKP: Synchronous Clock Polarity Select bit

Asynchronous mode:

1 = Transmit inverted data to the TX/CK pin 0 = Transmit non-inverted data to the TX/CK pin

Synchronous mode:

1 = Data is clocked on rising edge of the clock0 = Data is clocked on falling edge of the clock

bit 3 BRG16: 16-bit Baud Rate Generator bit

1 = 16-bit Baud Rate Generator is used0 = 8-bit Baud Rate Generator is used

bit 2 **Unimplemented:** Read as '0' bit 1 **WUE:** Wake-up Enable bit

Asynchronous mode:

1 = Receiver is waiting for a falling edge, no character will be received, byte RCIF will be set; WUE will automatically clear after RCIF is set

0 = Receiver is operating normally

Synchronous mode:

Don't care.

bit 0 ABDEN: Auto-Baud Detect Enable bit

Asynchronous mode:

1 = Auto-Baud Detect mode is enabled (clears when auto-baud is complete)

0 = Auto-Baud Detect mode is disabled

Synchronous mode:

Don't care.

TABLE 33-7: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name                  | Bit 7   | Bit 6               | Bit 5  | Bit 4                         | Bit 3      | Bit 2      | Bit 1     | Bit 0  | Register<br>on Page |  |

|-----------------------|---------|---------------------|--------|-------------------------------|------------|------------|-----------|--------|---------------------|--|

| ANSELA                | _       | _                   | _      | ANSA4                         | _          |            | ANSA<2:0> |        | 137                 |  |

| ANSELB <sup>(1)</sup> |         | ANSB.               | <7:4>  |                               | _          | _          | _         | _      | 143                 |  |

| ANSELC                | ANSC<   | 7:6> <sup>(1)</sup> | _      | _                             |            | ANSC       | >3:0>     |        | 148                 |  |

| BAUD1CON              | ABDOVF  | RCIDL               | _      | SCKP                          | BRG16      | _          | WUE       | ABDEN  | 442                 |  |

| INTCON                | GIE     | PEIE                | TMR0IE | INTE                          | IOCIE      | TMR0IF     | INTF      | IOCIF  | 101                 |  |

| PIE1                  | TMR1GIE | ADIE                | RCIE   | TXIE                          | SSP1IE     | CCP1IE     | TMR2IE    | TMR1IE | 102                 |  |

| PIR1                  | TMR1GIF | ADIF                | RCIF   | TXIF                          | SSP1IF     | CCP1IF     | TMR2IF    | TMR1IF | 105                 |  |

| RC1STA                | SPEN    | RX9                 | SREN   | CREN                          | ADDEN      | FERR       | OERR      | RX9D   | 441                 |  |

| RxyPPS                | _       | _                   | _      |                               | F          | RxyPPS<4:0 | >         |        | 154                 |  |

| SP1BRGL               |         |                     |        | BRG<                          | :7:0>      |            |           |        | 443                 |  |

| SP1BRGH               |         |                     |        | BRG<                          | 15:8>      |            |           |        | 443                 |  |

| TRISA                 | _       | _                   | TRISA  | SA<5:4>(2) TRISA<2            |            |            |           |        | 136                 |  |

| TRISB <sup>(1)</sup>  |         | TRISB               | <7:4>  |                               | _          | _          | _         | _      | 142                 |  |

| TRISC                 | TRISC<  | 7:6> <sup>(1)</sup> |        |                               | TRISC<5:0> |            |           |        | 147                 |  |

| TX1REG                |         |                     | EUS    | EUSART Transmit Data Register |            |            |           |        |                     |  |

| TX1STA                | CSRC    | TX9                 | TXEN   | SYNC                          | SENDB      | BRGH       | TRMT      | TX9D   | 440                 |  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

Page provides register information.

**Note 1:** PIC16(L)F1768/9 only.

2: Unimplemented, read as '1'.

TABLE 35-3: PIC16(L)F1764/5/8/9 INSTRUCTION SET

| Mnemonic,                              |              | Description                                        | Cycles     |     | 14-Bit | Opcode | )    | Status   | Notes |  |

|----------------------------------------|--------------|----------------------------------------------------|------------|-----|--------|--------|------|----------|-------|--|

| Oper                                   | rands        | Description                                        |            | MSb |        |        | LSb  | Affected | Notes |  |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |              |                                                    |            |     |        |        |      |          |       |  |

| ADDWF                                  | f, d         | Add W and f                                        | 1          | 0.0 | 0111   | dfff   | ffff | C, DC, Z | 2     |  |

| ADDWFC                                 | f, d         | Add with Carry W and f                             | 1          | 11  | 1101   | dfff   | ffff | C, DC, Z | 2     |  |

| ANDWF                                  | f, d         | AND W with f                                       | 1          | 00  | 0101   | dfff   | ffff | Z        | 2     |  |

| ASRF                                   | f, d         | Arithmetic Right Shift                             | 1          | 11  | 0111   | dfff   | ffff | C, Z     | 2     |  |

| LSLF                                   | f, d         | Logical Left Shift                                 | 1          | 11  | 0101   | dfff   | ffff | C, Z     | 2     |  |

| LSRF                                   | f, d         | Logical Right Shift                                | 1          | 11  | 0110   | dfff   | ffff | C, Z     | 2     |  |

| CLRF                                   | f            | Clear f                                            | 1          | 00  | 0001   | lfff   | ffff | Z        | 2     |  |

| CLRW                                   | _            | Clear W                                            | 1          | 0.0 | 0001   | 0000   | 00xx | Z        |       |  |

| COMF                                   | f, d         | Complement f                                       | 1          | 00  | 1001   | dfff   | ffff | Z        | 2     |  |

| DECF                                   | f, d         | Decrement f                                        | 1          | 00  | 0011   | dfff   | ffff | Z        | 2     |  |

| INCF                                   | f, d         | Increment f                                        | 1          | 0.0 | 1010   | dfff   |      | Z        | 2     |  |

| IORWF                                  | f. d         | Inclusive OR W with f                              | 1          | 00  |        | dfff   |      | _        | 2     |  |

| MOVF                                   | f, d         | Move f                                             | 1          | 00  | 1000   | dfff   |      |          | 2     |  |

| MOVWF                                  | f            | Move W to f                                        | 1          | 00  |        | 1fff   |      | _        | 2     |  |

| RLF                                    | f. d         | Rotate Left f through Carry                        | 1          | 00  | 1101   |        | ffff | С        | 2     |  |

| RRF                                    | f, d         | Rotate Right f through Carry                       | i          | 00  | 1100   |        | ffff | C        | 2     |  |

| SUBWF                                  | f, d         | Subtract W from f                                  | i          | 00  |        | dfff   |      | _        | 2     |  |

| SUBWFB                                 | f, d         | Subtract with Borrow W from f                      | 1          | 11  | 1011   |        | ffff | C, DC, Z | 2     |  |

| SWAPF                                  | f, d         | Swap nibbles in f                                  |            | 00  | 1110   |        | ffff | C, DC, Z | 2     |  |

| XORWF                                  | f, d         | Exclusive OR W with f                              |            | 00  | 0110   |        | ffff | 7        | 2     |  |

| XORWI                                  | 1, u         | BYTE ORIENTED SKIP (                               | 1 .        |     | 0110   | ulli   | TITI |          |       |  |

| DECFSZ                                 | f d          |                                                    |            |     | 1011   | 1555   |      | I        | 1 2   |  |

| INCFSZ                                 | f, d<br>f, d | Decrement f, Skip if 0                             | 1(2)       | 00  | 1011   | dfff   | ffff |          | 1, 2  |  |

| INCFSZ                                 | T, O         | Increment f, Skip if 0                             | 1(2)       |     | 11111  | dfff   | ffff |          | 1, 2  |  |

|                                        | 1            | BIT-ORIENTED FILE REGIST                           |            |     |        |        | ı    | I        | 1 -   |  |

| BCF                                    | f, b         | Bit Clear f                                        | 1          | 01  | 00bb   | bfff   | ffff |          | 2     |  |

| BSF                                    | f, b         | Bit Set f                                          | 1          | 01  | 01bb   | bfff   | ffff |          | 2     |  |

|                                        |              | BIT-ORIENTED SKIP O                                |            | NS  |        |        |      | 1        | 1     |  |

| BTFSC                                  | f, b         | Bit Test f, Skip if Clear                          | 1 (2)      | 01  | 10bb   | bfff   | ffff |          | 1, 2  |  |

| BTFSS                                  | f, b         | Bit Test f, Skip if Set                            | 1 (2)      | 01  | 11bb   | bfff   | ffff |          | 1, 2  |  |

|                                        |              | LITERAL OPERA                                      | TIONS      |     |        |        |      |          |       |  |

| ADDLW                                  | k            | Add literal and W                                  | 1          | 11  | 1110   | kkkk   | kkkk | C, DC, Z |       |  |

| ANDLW                                  | k            | AND literal with W                                 | 1          | 11  | 1001   | kkkk   | kkkk | Z        |       |  |

| IORLW                                  | k            | Inclusive OR literal with W                        | 1          | 11  | 1000   | kkkk   | kkkk | Z        |       |  |

| MOVLB                                  | k            | Move literal to BSR                                | 1          | 00  | 0000   | 001k   | kkkk |          |       |  |

| MOVLP                                  | k            | Move literal to PCLATH                             | 1          | 11  | 0001   | 1kkk   | kkkk |          |       |  |

| MOVLW                                  | k            | Move literal to W                                  | 1          | 11  | 0000   | kkkk   | kkkk |          |       |  |

| SUBLW                                  | k            | Subtract W from literal                            | 1          | 11  | 1100   | kkkk   |      | C, DC, Z |       |  |

| XORLW                                  | k            | Exclusive OR literal with W                        | 1          | 11  |        | kkkk   |      |          |       |  |

| Note 1:                                |              | ram Counter (PC) is modified, or a conditional tes | tic truc t |     |        |        |      |          | oond  |  |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDFn register and the MSb of the corresponding FSRn is set, this instruction will require one additional instruction cycle.

<sup>3:</sup> See Table 35-3 for the MOVIW and MOVWI instruction descriptions.

TABLE 36-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

| PIC16LF1 | 764/5/8/9 Star  | dard Operating Conditions (unless otherwise stated) |      |      |       |     |                             |  |

|----------|-----------------|-----------------------------------------------------|------|------|-------|-----|-----------------------------|--|

| PIC16F17 | 64/5/8/9        |                                                     |      |      |       |     |                             |  |

| Param    | Device          | Min.                                                | Typ+ | Max. | Units |     | Conditions                  |  |

| No.      | Characteristics | IVIIII.                                             | Typ† | Wax. | Units | VDD | Note                        |  |

| D017     |                 | _                                                   | 115  | 175  | μА    | 1.8 | Fosc = 500 kHz,             |  |

|          | l               | _                                                   | 145  | 210  | μΑ    | 3.0 | MFINTOSC mode               |  |

| D017     |                 | _                                                   | 160  | 230  | μΑ    | 2.3 | Fosc = 500 kHz,             |  |

|          |                 | _                                                   | 180  | 260  | μΑ    | 3.0 | MFINTOSC mode               |  |

|          |                 | _                                                   | 230  | 320  | μΑ    | 5.0 |                             |  |

| D019     |                 | _                                                   | 0.9  | 1.3  | mA    | 1.8 | Fosc = 16 MHz,              |  |

|          |                 |                                                     | 1.5  | 1.9  | mA    | 3.0 | HFINTOSC mode               |  |

| D019     | ,               | _                                                   | 1.2  | 1.8  | mA    | 2.3 | Fosc = 16 MHz,              |  |

|          |                 | _                                                   | 1.5  | 2    | mA    | 3.0 | HFINTOSC mode               |  |

|          |                 | _                                                   | 1.7  | 2.1  | mA    | 5.0 |                             |  |

| D020     | <br>            | _                                                   | 2.9  | 3.3  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | _                                                   | 3.5  | 4.1  | mA    | 3.6 | HFINTOSC mode               |  |

| D020     |                 | _                                                   | 2.9  | 3.8  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | _                                                   | 3.0  | 3.9  | mA    | 5.0 | HFINTOSC mode               |  |

| D022     |                 | _                                                   | 2.6  | 3.1  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|          |                 | _                                                   | 3.4  | 3.9  | mA    | 3.6 | HS Oscillator mode (Note 5) |  |

| D022     |                 | _                                                   | 2.6  | 3.2  | mA    | 3.0 | Fosc = 32 MHz               |  |

|          |                 | _                                                   | 3.3  | 4.2  | mA    | 5.0 | HS Oscillator mode (Note 5) |  |

<sup>†</sup> Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: For EXTRC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ ..

- 4: FVR and BOR are disabled.

- 5: 8 MHz crystal/oscillator with 4x PLL enabled.