Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b, 1x10b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1765-e-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

The PIC16(L)F1764/5/8/9 are described within this data sheet. See Table 2 for available package configurations.

Figure 1-1 shows a block diagram of the PIC16(L)F1764/5 devices. Figure 1-2 shows a block diagram of the PIC16(L)F1768/9 devices. Table 1-2 and Table 1-3 show the pinout descriptions.

Refer to Table 1-1 for peripherals available per device.

## TABLE 1-1:DEVICE PERIPHERAL<br/>SUMMARY

| 30101                     |              |               |               |               |               |

|---------------------------|--------------|---------------|---------------|---------------|---------------|

| Peripheral                |              | PIC16(L)F1764 | PIC16(L)F1765 | PIC16(L)F1768 | PIC16(L)F1769 |

| Analog-to-Digital Conve   | erter (ADC)  | •             | ٠             | ٠             | ٠             |

| Fixed Voltage Reference   | e (FVR)      | ٠             | ٠             | ٠             | ٠             |

| Zero-Cross Detection (Z   | ZCD)         | ٠             | ٠             | ٠             | ٠             |

| Temperature Indicator     |              | ٠             | ٠             | ٠             | ٠             |

| Complementary Output (    | Generator (C | OG)           |               |               |               |

|                           | COG1         | •             | ٠             | ٠             | ٠             |

|                           | COG2         |               |               | ٠             | •             |

| Programmable Ramp G       | enerator (Pl | RG)           |               |               |               |

|                           | PRG1         | ٠             | ٠             | ٠             | ٠             |

|                           | PRG2         |               |               | ٠             | ٠             |

| 10-Bit Digital-to-Analog  | Converter (I | DAC           | )             |               |               |

|                           | DAC1         | ٠             | ٠             | ٠             | ٠             |

|                           | DAC2         |               |               | ٠             | ٠             |

| 5-Bit Digital-to-Analog C | Converter (D | AC)           |               |               |               |

|                           | DAC3         | ٠             | ٠             | ٠             | ٠             |

|                           | DAC4         |               |               | ٠             | ٠             |

| Capture/Compare/PWM       | I (CCP/ECC   | P) M          | odul          | es            |               |

|                           | CCP1         | ٠             | ٠             | ٠             | ٠             |

|                           | CCP2         |               |               | ٠             | ٠             |

| Comparators               |              |               |               |               |               |

|                           | C1           | ٠             | ٠             | ٠             | ٠             |

|                           | C2           | •             | ٠             | ٠             | ٠             |

|                           | C3           |               |               | ٠             | ٠             |

|                           | C4           |               |               | ٠             | ٠             |

| Configurable Logic Cell   | (CLC)        |               |               |               |               |

|                           | CLC1         | ٠             | ٠             | ٠             | ٠             |

|                           | CLC2         | ٠             | ٠             | •             | ٠             |

|                           | CLC3         | ٠             | ٠             | ٠             | ٠             |

| Data Signal Modulator (   | DSM)         |               | •             | •             | •             |

|                           | DSM1         | ٠             | •             | •             | •             |

|                           | DSM2         |               |               | ٠             | ٠             |

|                           |              |               |               |               |               |

## TABLE 1-1:DEVICE PERIPHERAL<br/>SUMMARY (CONTINUED)

| Peripheral<br>Enhanced Universal Sys |              | PIC16(L)F1764 | PIC16(L)F1765 | E PIC16(L)F1768 | PIC16(L)F1769 |

|--------------------------------------|--------------|---------------|---------------|-----------------|---------------|

| Receiver/Transmitter (E              |              | Sync          | mone          | Jus             |               |

|                                      | EUSART       | ٠             | ٠             | ٠               | •             |

| Master Synchronous Se                | erial Ports  |               |               |                 |               |

|                                      | MSSP         | •             | •             | •               | •             |

| Op Amp                               |              |               |               |                 |               |

|                                      | Op Amp 1     | ٠             | ٠             | ٠               | ٠             |

|                                      | Op Amp 2     |               |               | ٠               | •             |

| 10-Bit Pulse-Width Mod               | lulator (PWN | 1)            |               |                 |               |

|                                      | PWM3         | ٠             | ٠             | ٠               | ٠             |

|                                      | PWM4         |               |               | ٠               | •             |

| 16-Bit Pulse-Width Mod               | lulator (PWN | 1)            |               |                 |               |

|                                      | PWM5         | ٠             | ٠             | ٠               | •             |

|                                      | PWM6         |               |               | ٠               | ٠             |

| 8-Bit Timers                         |              |               |               |                 |               |

|                                      | Timer0       | ٠             | ٠             | ٠               | ٠             |

|                                      | Timer2       | ٠             | ٠             | ٠               | ٠             |

|                                      | Timer4       | ٠             | •             | ٠               | ٠             |

|                                      | Timer6       | ٠             | ٠             | ٠               | ٠             |

| 16-Bit Timers                        |              |               | -             |                 |               |

|                                      | Timer1       | ٠             | ٠             | ٠               | •             |

|                                      | Timer3       | ٠             | ٠             | ٠               | •             |

|                                      | Timer5       | ٠             | ٠             | ٠               | •             |

#### TABLE 3-6: PIC16(L)F1769 MEMORY MAP (BANKS 0-7)

|      | BANK 0                                     |      | BANK 1                                     |      | BANK 2                                     |      | BANK 3                                     |      | BANK 4                                     |      | BANK 5                                     |      | BANK 6                                     |      | BANK 7                                     |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|

| 000h |                                            | 080h |                                            | 100h |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |                                            |

|      | Core Registers<br>(Table 3-2)              |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |                                            |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch | INLVLA                                     |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                                     | 20Dh | WPUB                                       | 28Dh | ODCONB                                     | 30Dh | SLRCONB                                    | 38Dh | INLVLB                                     |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh | INLVLC                                     |

| 00Fh | _                                          | 08Fh | —                                          | 10Fh | CMOUT                                      | 18Fh | _                                          | 20Fh | —                                          | 28Fh | _                                          | 30Fh | _                                          | 38Fh | —                                          |

| 010h | _                                          | 090h | —                                          | 110h | CM1CON0                                    | 190h | _                                          | 210h | —                                          | 290h | _                                          | 310h | _                                          | 390h | —                                          |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON1                                    | 191h | PMADRL                                     | 211h | SSP1BUF                                    | 291h | CCPR1L                                     | 311h | —                                          | 391h | IOCAP                                      |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1NSEL                                    | 192h | PMADRH                                     | 212h | SSP1ADD                                    | 292h | CCPR1H                                     | 312h | —                                          | 392h | IOCAN                                      |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM1PSEL                                    | 193h | PMDATL                                     | 213h | SSP1MSK                                    | 293h | CCP1CON                                    | 313h |                                            | 393h | IOCAF                                      |

| 014h | PIR4                                       | 094h | PIE4                                       | 114h | CM2CON0                                    | 194h | PMDATH                                     | 214h | SSP1STAT                                   | 294h | CCP1CAP                                    | 314h |                                            | 394h | IOCBP                                      |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CM2CON1                                    | 195h | PMCON1                                     | 215h | SSP1CON1                                   | 295h | —                                          | 315h |                                            | 395h | IOCBN                                      |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | CM2NSEL                                    | 196h | PMCON2                                     | 216h | SSP1CON2                                   | 296h | —                                          | 316h |                                            | 396h | IOCBF                                      |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | CM2PSEL                                    | 197h | VREGCON <sup>(1)</sup>                     | 217h | SSP1CON3                                   | 297h | _                                          | 317h |                                            | 397h | IOCCP                                      |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | CM3CON0                                    | 198h |                                            | 218h |                                            | 298h | CCPR2L                                     | 318h |                                            | 398h | IOCCN                                      |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | CM3CON1                                    | 199h | RC1REG                                     | 219h |                                            | 299h | CCPR2H                                     | 319h |                                            | 399h | IOCCF                                      |

| 01Ah | T2TMR                                      | 09Ah | OSCSTAT                                    | 11Ah | CM3NSEL                                    | 19Ah | TX1REG                                     | 21Ah |                                            | 29Ah | CCP2CON                                    | 31Ah |                                            | 39Ah |                                            |

| 01Bh | T2PR                                       | 09Bh | ADRESL                                     | 11Bh | CM3PSEL                                    | 19Bh | SP1BRGL                                    | 21Bh |                                            | 29Bh | CCP2CAP                                    | 31Bh | MD2CON0                                    | 39Bh | MD1CON0                                    |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | CM4CON0                                    | 19Ch | SP1BRGH                                    | 21Ch |                                            | 29Ch |                                            | 31Ch | MD2CON1                                    | 39Ch | MD1CON1                                    |

| 01Dh | T2HLT                                      | 09Dh | ADCON0                                     | 11Dh | CM4CON1                                    | 19Dh | RC1STA                                     | 21Dh | BORCON                                     | 29Dh |                                            | 31Dh | MD2SRC                                     | 39Dh | MD1SRC                                     |

| 01Eh | T2CLKCON                                   | 09Eh | ADCON1                                     | 11Eh | CM4NSEL                                    | 19Eh | TX1STA                                     | 21Eh | FVRCON                                     | 29Eh | CCPTMRS                                    | 31Eh | MD2CARL                                    | 39Eh | MD1CARL                                    |

| 01Fh | T2RST                                      | 09Fh | ADCON2                                     | 11Fh | CM4PSEL                                    | 19Fh | BAUD1CON                                   | 21Fh | ZCD1CON                                    | 29Fh | _                                          | 31Fh | MD2CARH                                    | 39Fh | MD1CARH                                    |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |                                            |

|      | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |                                            |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |                                            |

|      | Common RAM<br>70h – 7Fh                    |      | Accesses<br>70h-7Fh                        |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |                                            |

Legend: 🔲 = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1769.

## 3.3.6 CORE FUNCTION REGISTERS SUMMARY

The core function registers listed in Table 3-15 can be addressed from any bank.

| Addr            | Name   | Bit 7      | Bit 6                                                                                                 | Bit 5       | Bit 4        | Bit 3    | Bit 2      | Bit 1      | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>Resets |

|-----------------|--------|------------|-------------------------------------------------------------------------------------------------------|-------------|--------------|----------|------------|------------|--------|----------------------|---------------------------------|

| Bank (          | 0-31   |            |                                                                                                       |             |              |          |            |            |        |                      |                                 |

| x00h or<br>x80h | INDF0  |            | dressing this location uses contents of FSR0H/FSR0L to address data memory<br>of a physical register) |             |              |          |            |            |        | XXXX XXXX            | uuuu uuuu                       |

| x01h or<br>x81h | INDF1  |            | ng this locat<br>vsical regist                                                                        |             | ontents of F | SR1H/FSF | 1L to addr | ess data n | nemory | XXXX XXXX            | uuuu uuuu                       |

| x02h or<br>x82h | PCL    | Program    | Counter (P                                                                                            | C) Least Si | gnificant By | rte      |            |            |        | 0000 0000            | 0000 0000                       |

| x03h or<br>x83h | STATUS | _          | _                                                                                                     | _           | TO           | PD       | Z          | DC         | С      | 1 1000               | q quuu                          |

| x04h or<br>x84h | FSR0L  | Indirect D | ndirect Data Memory Address 0 Low Pointer                                                             |             |              |          |            |            |        | 0000 0000            | uuuu uuuu                       |

| x05h or<br>x85h | FSR0H  | Indirect D | ata Memor                                                                                             | y Address   | 0 High Poin  | ter      |            |            |        | 0000 0000            | 0000 0000                       |

| x06h or<br>x86h | FSR1L  | Indirect D | ata Memor                                                                                             | y Address   | 1 Low Point  | er       |            |            |        | 0000 0000            | uuuu uuuu                       |

| x07h or<br>x87h | FSR1H  | Indirect D | ata Memor                                                                                             | y Address   | 1 High Poin  | ter      |            |            |        | 0000 0000            | 0000 0000                       |

| x08h or<br>x88h | BSR    | _          | _                                                                                                     | _           | BSR4         | BSR3     | BSR2       | BSR1       | BSR0   | 0 0000               | 0 0000                          |

| x09h or<br>x89h | WREG   | Working F  | Vorking Register                                                                                      |             |              |          |            |            |        | 0000 0000            | uuuu uuuu                       |

| x0Ah or<br>x8Ah | PCLATH | _          | — Write Buffer for the upper 7 bits of the Program Counter                                            |             |              |          |            |            |        | -000 0000            | -000 0000                       |

| x0Bh or<br>x8Bh | INTCON | GIE        | PEIE                                                                                                  | TMR0IE      | INTE         | IOCIE    | TMR0IF     | INTF       | IOCIF  | 0000 0000            | 0000 0000                       |

#### TABLE 3-15: CORE FUNCTION REGISTERS SUMMARY<sup>(1)</sup>

Legend: x = unknown; u = unchanged; q = value depends on condition; - = unimplemented, read as '0'. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

## PIC16(L)F1764/5/8/9

#### TABLE 3-16: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    | LE 3-10.   |             |                                                                             |                     |                   |                 |           |        | i      | +                 | ·                               |

|--------------------|------------|-------------|-----------------------------------------------------------------------------|---------------------|-------------------|-----------------|-----------|--------|--------|-------------------|---------------------------------|

| Addr               | Name       | Bit 7       | Bit 6                                                                       | Bit 5               | Bit 4             | Bit 3           | Bit 2     | Bit 1  | Bit 0  | Value on POR, BOR | Value on<br>All Other<br>Resets |

| Bank               | < 8        |             |                                                                             |                     |                   |                 |           |        |        |                   |                                 |

| 40Ch               |            |             |                                                                             |                     |                   |                 |           |        |        |                   |                                 |

| <br>40Dh           | _          | Unimpleme   | nted                                                                        |                     |                   |                 |           |        |        | _                 | _                               |

| 40Eh               | HIDRVC     | _           | _                                                                           | HIDC                | <5:4>             | —               | —         | _      | —      | 00                | 00                              |

| 40Fh               |            |             | •                                                                           | •                   |                   |                 |           | •      | •      |                   |                                 |

| <br>412h           | _          | Unimpleme   | nted                                                                        |                     | -                 | —               |           |        |        |                   |                                 |

| 413h               | T4TMR      | Holding Reg | gister for the 8                                                            | -Bit TMR4 Regist    | er                |                 |           |        |        | 0000 0000         | 0000 0000                       |

| 413h               | T4PR       | TMR4 Peric  | od Register                                                                 |                     | 1111 1111         | 1111 1111       |           |        |        |                   |                                 |

| 415h               | T4CON      | ON          |                                                                             | CKPS<2:0>           |                   |                 | OUTP      | S<3:0> |        | 0000 0000         | 0000 0000                       |

| 416h               | T4HLT      | PSYNC       | CKPOL                                                                       | CKSYNC              |                   |                 | MODE<4:0> |        |        | 0000 0000         | 0000 0000                       |

| 417h               | T4CLKCON   | —           | _                                                                           | —                   | —                 |                 | CS<       | <3:0>  |        | 0000              | 0000                            |

| 418h               | T4RST      | —           | _                                                                           | —                   | —                 |                 | RSEL      | _<3:0> |        | 0000              | 0000                            |

| 419h               | _          | Unimpleme   | nted                                                                        | •                   |                   | ·               |           |        |        | _                 | —                               |

| 41Ah               | T6TMR      | Holding Ree | gister for the 8                                                            | -Bit TMR4 Regist    | er                |                 |           |        |        | 0000 0000         | 0000 0000                       |

| 41Bh               | T6PR       | TMR4 Perio  | od Register                                                                 |                     |                   |                 |           |        |        | 1111 1111         | 1111 1111                       |

| 41Ch               | T6CON      | ON          |                                                                             | CKPS<2:0>           |                   |                 | OUTP      | S<3:0> |        | 0000 0000         | 0000 0000                       |

| 41Dh               | T6HLT      | PSYNC       | CKPOL                                                                       | CKSYNC              |                   | I               | MODE<4:0> |        |        | 0000 0000         | 0000 0000                       |

| 41Eh               | T6CLKCON   | —           | —                                                                           | —                   | _                 |                 | CS<       | <3:0>  |        | 0000              | 0000                            |

| 41Fh               | T6RST      | —           | —                                                                           | —                   | —                 |                 | RSEL      | _<3:0> |        | 0000              | 0000                            |

| Bank               | <b>(</b> 9 |             |                                                                             |                     |                   |                 |           |        |        |                   |                                 |

| 48Ch<br>to<br>492h | _          | Unimpleme   | nted                                                                        |                     |                   |                 |           |        |        | _                 | _                               |

| 493h               | TMR3L      | Holding Reg | gister for the L                                                            | east Significant B  | yte of the 16-Bi  | t TMR1 Register | r         |        |        | XXXX XXXX         | uuuu uuuu                       |

| 494h               | TMR3H      | Holding Reg | gister for the N                                                            | lost Significant By | yte of the 16-Bit | TMR1 Register   |           |        |        | XXXX XXXX         | uuuu uuuu                       |

| 495h               | T3CON      | CS          | <1:0>                                                                       | CKPS                | <1:0>             | OSCEN           | SYNC      | —      | ON     | 0000 00-0         | uuuu uu-u                       |

| 496h               | T3GCON     | GE          | GPOL                                                                        | GTM                 | GSPM              | GGO/DONE        | GVAL      | GSS    | S<1:0> | 00x0 0x00         | uuuu uxuu                       |

| 497h<br>to<br>499h | _          | Unimpleme   | Unimplemented                                                               |                     |                   |                 |           |        |        |                   | _                               |

| 49Ah               | TMR5L      | Holding Reg | Holding Register for the Least Significant Byte of the 16-Bit TMR1 Register |                     |                   |                 |           |        |        |                   | uuuu uuuu                       |

| 49Bh               | TMR5H      | Holding Reg | gister for the N                                                            | lost Significant By | yte of the 16-Bit | TMR1 Register   |           |        |        | XXXX XXXX         | uuuu uuuu                       |

| 49Ch               | T5CON      | CS          | <1:0>                                                                       | CKPS                | 0000 00-0         | uuuu uu-u       |           |        |        |                   |                                 |

| 49Dh               | T5GCON     | GE          | GPOL                                                                        | GTM                 | GSPM              | GGO/DONE        | GVAL      | GSS    | 6<1:0> | 00x0 0x00         | uuuu uxuu                       |

| 49Eh<br>to<br>49Fh | —          | Unimpleme   | nted                                                                        |                     | _                 | _               |           |        |        |                   |                                 |

Legend: x = unknown; u = unchanged; q = value depends on condition; - = unimplemented, read as '0'; x = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1768/9 only.

3: PIC16(L)F1764/5 only.

4: Unimplemented on PIC16LF1764/5/8/9.

## PIC16(L)F1764/5/8/9

| R/W-0/0          | R/W-0/0                                                                                                  | R/W-0/0                       | R/W-0/0          | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0     |  |  |

|------------------|----------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------|------------------|----------|-------------|--|--|

| TMR1GIE          | ADIE                                                                                                     | RCIE                          | TXIE             | SSP1IE          | CCP1IE           | TMR2IE   | TMR1IE      |  |  |

| bit 7            |                                                                                                          | ·                             |                  |                 |                  |          | bit         |  |  |

| Legend:          |                                                                                                          |                               |                  |                 |                  |          |             |  |  |

| R = Readable     | bit                                                                                                      | W = Writable                  | hit              |                 |                  |          |             |  |  |

| u = Bit is unch  |                                                                                                          | x = Bit is unkr               |                  | U = Unimpler    | mented bit, read | l as '0' |             |  |  |

| '1' = Bit is set | •                                                                                                        | '0' = Bit is cle              |                  |                 | at POR and BO    |          | ther Resets |  |  |

|                  |                                                                                                          | 0 21110 010                   |                  |                 |                  |          |             |  |  |

| bit 7            | TMR1GIE: Ti                                                                                              | mer1 Gate Inte                | errupt Enable b  | oit             |                  |          |             |  |  |

|                  | 1 = Enables t                                                                                            | he Timer1 gate                | e acquisition ir | nterrupt        |                  |          |             |  |  |

|                  | 0 = Disables                                                                                             | the Timer1 gate               | e acquisition i  | nterrupt        |                  |          |             |  |  |

| bit 6            | -                                                                                                        | j-to-Digital Con              | , ,              | Interrupt Enabl | le bit           |          |             |  |  |

|                  |                                                                                                          | he ADC interru                |                  |                 |                  |          |             |  |  |

|                  |                                                                                                          | the ADC interru               | •                |                 |                  |          |             |  |  |

| bit 5            |                                                                                                          | RT Receive Int                | •                |                 |                  |          |             |  |  |

|                  |                                                                                                          | he EUSART re<br>the EUSART re |                  |                 |                  |          |             |  |  |

| bit 4            |                                                                                                          | RT Transmit Int               |                  |                 |                  |          |             |  |  |

|                  |                                                                                                          | he EUSART tra                 | •                |                 |                  |          |             |  |  |

|                  |                                                                                                          | the EUSART tr                 |                  |                 |                  |          |             |  |  |

| bit 3            | SSP1IE: Mas                                                                                              | ter Synchrono                 | us Serial Port   | (MSSP) Interru  | upt Enable bit   |          |             |  |  |

|                  |                                                                                                          | he MSSP inter                 |                  |                 |                  |          |             |  |  |

|                  |                                                                                                          | the MSSP inter                |                  |                 |                  |          |             |  |  |

| bit 2            |                                                                                                          | P1 Interrupt En               |                  |                 |                  |          |             |  |  |

|                  |                                                                                                          | he CCP1 interi                |                  |                 |                  |          |             |  |  |

| bit 1            |                                                                                                          | the CCP1 inter                | •                | -nabla bit      |                  |          |             |  |  |

| DILI             | <b>TMR2IE:</b> TMR2 to T2PR Match Interrupt Enable bit<br>1 = Enables the Timer2 to T2PR match interrupt |                               |                  |                 |                  |          |             |  |  |

|                  |                                                                                                          | the Timer2 to T               |                  |                 |                  |          |             |  |  |

| bit 0            |                                                                                                          | er1 Overflow Ir               |                  | •               |                  |          |             |  |  |

|                  |                                                                                                          | he Timer1 ove                 |                  |                 |                  |          |             |  |  |

|                  | 0 = Disables                                                                                             |                               |                  |                 |                  |          |             |  |  |

#### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

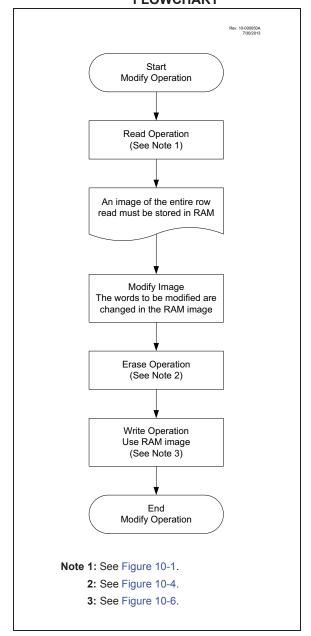

#### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

#### FIGURE 10-7:

#### FLASH PROGRAM MEMORY MODIFY FLOWCHART

#### 11.6 Register Definitions: PORTC

#### REGISTER 11-17: PORTC: PORTC REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u              | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|-------------------|---------|----------------------|------------------|------------------|-------------|

|                  |         |                   | RC<7    | :0> <sup>(1,2)</sup> |                  |                  |             |

| bit 7            |         |                   |         |                      |                  |                  | bit 0       |

|                  |         |                   |         |                      |                  |                  |             |

| Legend:          |         |                   |         |                      |                  |                  |             |

| R = Readable     | bit     | W = Writable I    | bit     |                      |                  |                  |             |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | U = Unimpler         | nented bit, read | l as '0'         |             |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | -n/n = Value a       | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1,2)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

2: RC<7:6> are available on PIC16(L)F1768/9 only.

#### REGISTER 11-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|---------|----------------------|---------|---------|---------|

|         |         |         | TRISC   | <7:0> <sup>(1)</sup> |         |         |         |

| bit 7   |         |         |         |                      |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-0 **TRISC<7:0>:** PORTC Tri-State Control bits<sup>(1)</sup> 1 = PORTC pin is configured as an input (tri-stated) 0 = PORTC pin is configured as an output

Note 1: TRISC<7:6> are available on PIC16(L)F1768/9 only.

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from the PORTC register are the return of actual I/O pin values.

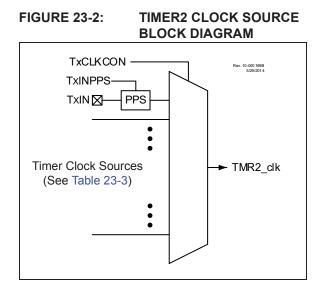

#### 23.1 Timer2 Operation

Timer2 operates in three major modes:

- · Free-Running Period

- One-Shot

- Monostable

Within each mode, there are several options for starting, stopping and resetting. Table 23-1 lists the options.

In all modes, the TMR2 Count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The T2PR period register is double buffered. Software reads and writes the T2PR register. However, the timer uses a buffered PRx register for operation. Software does not have direct access to the buffered PRx register. The content of the PRx register is transferred to the buffer by any of the following events:

- A write to the TMR2 register

- · A write to the T2CON register

- When TMR2 = PRx buffer and the prescaler rolls over

- An external Reset event

The TMR2 register is directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

• A write to the TMR2 register

- A write to the T2CON register

- Any device Reset

• External Reset source event that resets the timer.

| Note: | TMR2     | is | not | cleared | when | T2CON | is |

|-------|----------|----|-----|---------|------|-------|----|

|       | written. |    |     |         |      |       |    |

#### 23.1.1 FREE-RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each clock cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next cycle and increments the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register then a one clock period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

#### 23.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free-Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR, and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

#### 23.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

#### 23.2 Timer2 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2xCON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- · The ADC module as an auto-conversion trigger

- · COG as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 24.6 "CCP/PWM Clock Selection"** for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in **Section 23.6 "Operation Examples"** for examples of how the varying Timer2 modes affect CCP PWM output.

#### 24.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle and resolution are controlled by the following registers:

- T2PR/T4PR/T6PR registers

- T2CON/T4CON/T6CON registers

- CCPRxH:CCPRxL register pair

Figure 24-3 shows a simplified block diagram of PWM operation.

Note 1: The corresponding TRISx bit must be cleared to enable the PWM output on the CCPx pin.

2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### 24.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- 1. Disable the CCPx pin output driver by setting the associated TRISx bit.

- 2. Select the timer associated with the PWM by setting the CCPTMRS register.

- 3. Load the associated T2PR/T4PR/T6PR register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 5. Load the CCPRxH:CCPRxL register pair with the PWM duty cycle value.

- 6. Configure and start the timer selected in Step 2:

- Clear the timer interrupt flag bit of the PIRx register. See Note below.

- Configure the CKPSx bits of the TxCON register with the timer prescale value.

- Enable the timer by setting the ON bit of the TxCON register.

- 7. Enable PWM output pin:

- Wait until the timer overflows and the timer interrupt bit of the PIRx register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRISx bit.

| Note: | In order to send a complete duty cycle and<br>period on the first PWM output, the above |

|-------|-----------------------------------------------------------------------------------------|

|       | steps must be included in the setup                                                     |

|       | sequence. If it is not critical to start with a                                         |

|       | complete PWM signal on the first output,                                                |

|       | then Step 6 may be ignored.                                                             |

#### 26.3 Offset Modes

The Offset modes provide the means to adjust the waveform of a slave PWM module relative to the waveform of a master PWM module in the same device.

#### 26.3.1 INDEPENDENT RUN MODE

In Independent Run mode (OFM<1:0> = 00), the PWM module is unaffected by the other PWM modules in the device. The PWMxTMR associated with the PWM module in this mode starts counting as soon as the EN bit associated with this PWM module is set, and continues counting until the EN bit is cleared. Period events reset the PWMxTMR to zero, after which, the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-8.

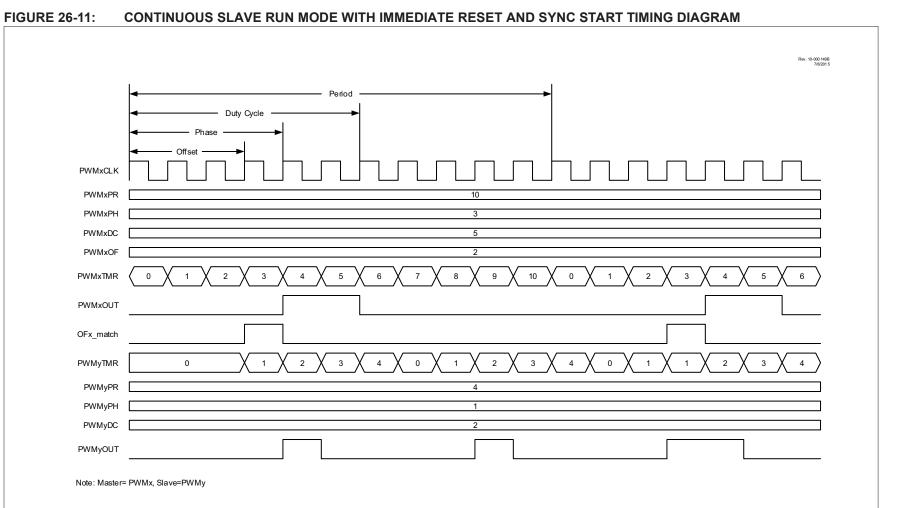

### 26.3.2 SLAVE RUN MODE WITH SYNC START

In Slave Run mode with Sync Start (OFM<1:0> = 01), the slave PWMxTMR waits for the master's OF\_match event. When this event occurs, if the EN bit is set, the PWMxTMR begins counting and continues to count until software clears the EN bit. Slave period events reset the PWMxTMR to zero, after which, the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-9.

#### 26.3.3 ONE-SHOT SLAVE MODE WITH SYNC START

In One-Shot Slave mode with Synchronous Start (OFM<1:0> = 10), the slave PWMxTMR waits until the master's OF\_match event. The timer then begins counting, starting from the value that is already in the timer, and continues to count until the period match event. When the period event occurs, the timer resets to zero and stops counting. The timer then waits until the next master OF\_match event, after which, it begins counting again to repeat the cycle. An OF\_match event that occurs before the slave PWM has completed the triggered period will be ignored. A slave period that is greater than the master period, but less that twice the master period, will result in a slave output every other master period.

Note: During the time the slave timers are resetting to zero, if another offset match event is received, it is possible that the slave PWM would not recognize this match event and the slave timers would fail to begin counting again. This would result in missing duty cycles in the output of the slave PWM. To prevent this from happening, avoid using the same period for both the master and slave PWMs.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-10.

#### 26.3.4 CONTINUOUS RUN SLAVE MODE WITH SYNC START AND TIMER RESET

In Continuous Run Slave mode with Synchronous Start and Timer Reset (OFM<1:0> = 11), the slave PWMxTMR is inhibited from counting after the slave PWM enable is set. The first master OF\_match event starts the slave PWMxTMR. Subsequent master OF\_match events reset the slave PWMxTMR timer value back to 1, after which, the slave PWMxTMR continues to count. The next master OF\_match event resets the slave PWMxTMR back to 1 to repeat the cycle. Slave period events that occur before the master's OF\_match event will reset the slave PWMxTMR to zero, after which, the timer will continue to count. Slaves operating in this mode must have a PWMxPH register pair value equal to, or greater than, 1; otherwise, the phase match event will not occur precluding the start of the PWM output duty cycle.

The offset timing will persist if both the master and slave PWMxPR values are the same and the Slave Offset mode is changed to Independent Run mode while the PWM module is operating.

A detailed timing diagram of this mode used in Standard PWM mode is shown in Figure 26-11.

| Note: | Unexpected results will occur if the slave |

|-------|--------------------------------------------|

|       | PWM_clock is a higher frequency than the   |

|       | master PWM_clock.                          |

#### 26.3.5 OFFSET MATCH IN CENTER-ALIGNED MODE

When a master is operating in Center-Aligned mode, the offset match event depends on which direction the PWMxTMR is counting. Clearing the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting up. Setting the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting down. The OFO bit is ignored in Non-Center-Aligned modes.

The OFO bit is double-buffered and requires setting the LDA bit to take effect when the PWM module is operating.

Detailed timing diagrams of Center-Aligned mode using offset match control in Independent Slave with Sync Start mode can be seen in Figure 26-12 and Figure 26-13.

# DS40001775C-page 276

PIC16(L)F1764/5/8/9

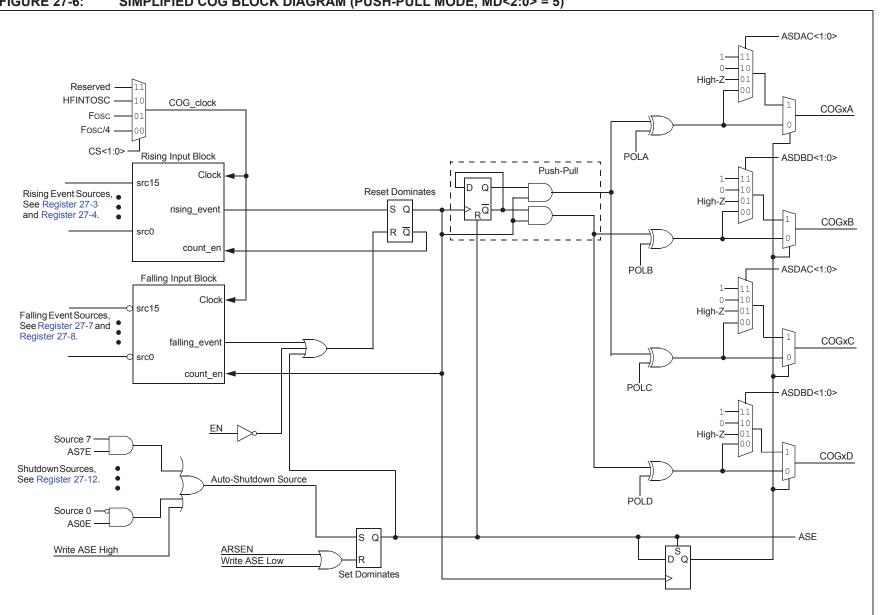

#### SIMPLIFIED COG BLOCK DIAGRAM (PUSH-PULL MODE, MD<2:0> = 5) **FIGURE 27-6:**

PIC16(L)F1764/5/8/9

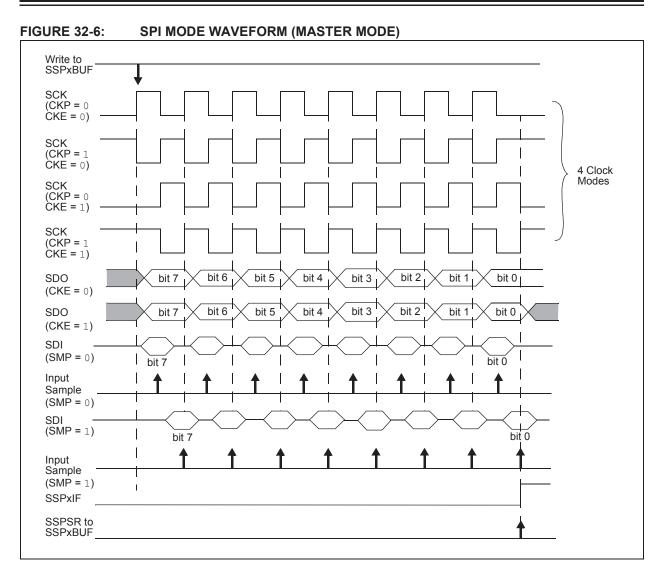

#### 32.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 32.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 32-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

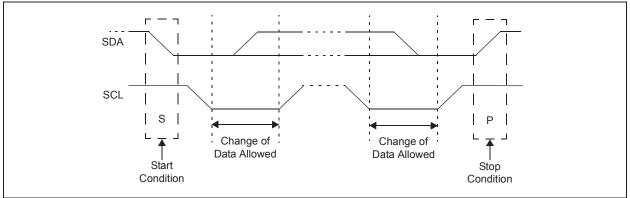

#### 32.4.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA from a high to a low state while the SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an active state. Figure 32-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the I<sup>2</sup>C specification that states no bus collision can occur on a Start.

#### 32.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low, then high again while the SCL line stays high, only the Start condition is detected.

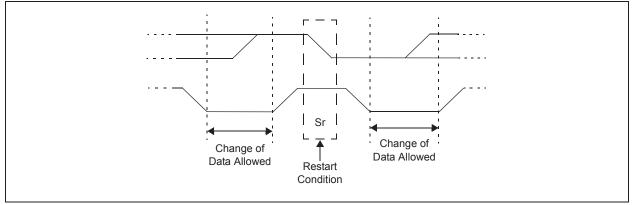

#### 32.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 32-13 shows the wave form for a Restart condition.

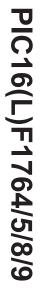

In 10-Bit Addressing Slave mode, a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with  $R/\overline{W}$  clear or high address match fails.

#### 32.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. In Slave modes where interrupt on Start and Stop detect is already enabled, these bits will have no effect.

© 2014-2017 Microchip Technology Inc.

DS40001775C-page 403

#### 35.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 35-3 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of four oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 35.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified and the result is stored according to either the instruction or the destination designator, 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 35-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F).                                                                                                                                             |

| W     | Working register (accumulator).                                                                                                                                                   |

| b     | Bit address within an 8-bit file register.                                                                                                                                        |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number (0-1).                                                                                                                                                         |

| mm    | Pre/Post-Increment/Decrement mode selection.                                                                                                                                      |

## TABLE 35-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

## PIC16(L)F1764/5/8/9

| BCF                                             | Bit Clear f                                                         |

|-------------------------------------------------|---------------------------------------------------------------------|

| Syntax:                                         | [ <i>label</i> ]BCF f,b                                             |

| Operands:                                       | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:                                      | 0 → (f <b>)</b>                                                     |

| Status Affected:                                | None                                                                |

| Description: Bit 'b' in register 'f' is cleared |                                                                     |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

Bit Test f, Skip if Set

$\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$

| BRA              | Relative Branch                                                                                                                                                                                                                                 | BTFSS                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                                           | Syntax:                     |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255                                                                                                                                                                                                                     | Operands:                   |

| Operation:       | $-256 \le k \le 255$ (PC) + 1 + k $\rightarrow$ PC                                                                                                                                                                                              | Operation:<br>Status Affect |

| Status Affected: | None                                                                                                                                                                                                                                            | Description:                |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |                             |

|                                                                              | Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

|------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              | Status Affected: | None                                                                                                                                                                                                            |

| ral 'k' to the<br>ave<br>e next<br>ress will be<br>tion is a<br>branch has a | Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruction<br>is discarded and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |

## BRW Relative Branch with W Syntax: [ label ] BRW Operands: None

| Operands:        | None                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |  |

|------------------|---------------------------------------------------------------------|--|

| Syntax:          | [label]BSF f,b                                                      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |  |

| Status Affected: | None                                                                |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |

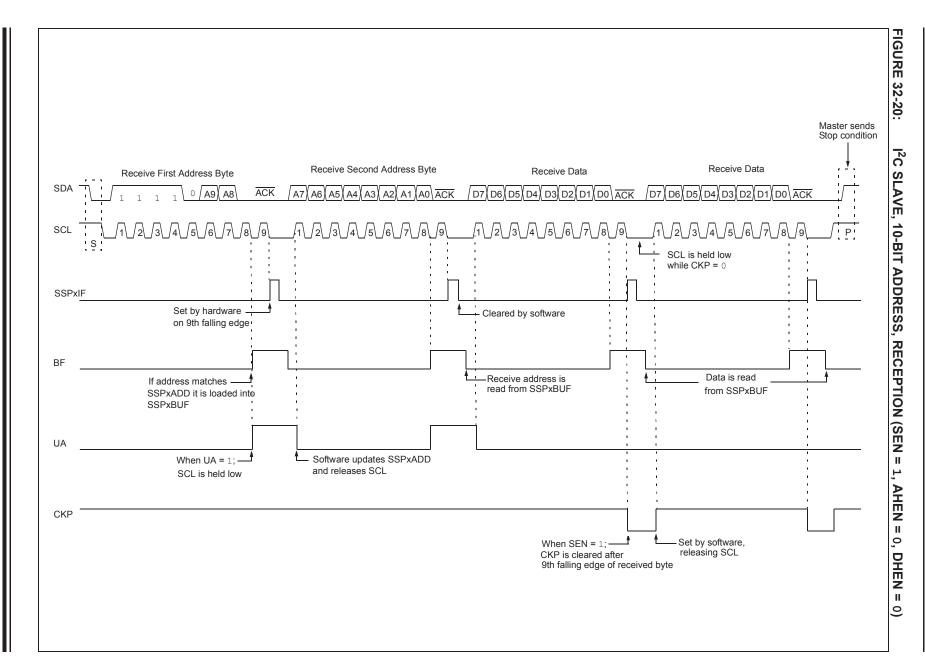

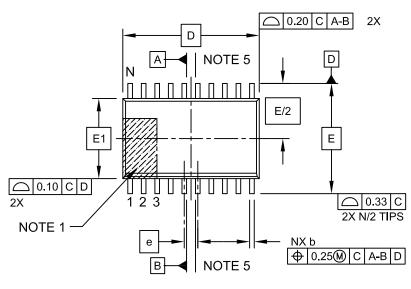

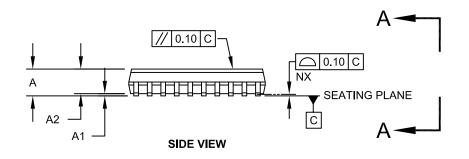

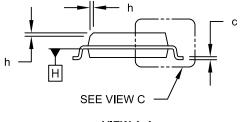

#### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| V     | EW | C |

|-------|----|---|

| · v I |    |   |

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Number of Pins           | N  | 14          |          |      |

| Pitch                    | е  |             | 1.27 BSC |      |

| Overall Height           | Α  | -           | -        | 1.75 |

| Molded Package Thickness | A2 | 1.25        | -        | -    |

| Standoff §               | A1 | 0.10        | -        | 0.25 |

| Overall Width            | E  | 6.00 BSC    |          |      |

| Molded Package Width     | E1 | 3.90 BSC    |          |      |

| Overall Length           | D  | 8.65 BSC    |          |      |

| Chamfer (Optional)       | h  | 0.25        | -        | 0.50 |

| Foot Length              | L  | 0.40        | -        | 1.27 |

| Footprint                | L1 | 1.04 REF    |          |      |

| Lead Angle               | Θ  | 0°          | -        | -    |

| Foot Angle               | φ  | 0°          | -        | 8°   |

| Lead Thickness           | С  | 0.10        | -        | 0.25 |

| Lead Width               | b  | 0.31        | -        | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -        | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -        | 15°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2