# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b, 1x10b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1765-i-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2 (CONTINUED)

bit 1-0 WRT<1:0>: Flash Memory Self-Write Protection bits

#### 4 kW Flash Memory (PIC16(L)F1764/8):

- 11 = Off Write protection is off

- 10 = Boot 0000h to 01FFh are write-protected, 0200h to 0FFFh may be modified by PMCON control

- 01 = Half 0000h to 07FFh are write-protected, 0800h to 0FFFh may be modified by PMCON control

- 00 = All 0000h to 0FFFh are write-protected, no addresses may be modified by PMCON control

- 8 kW Flash Memory (PIC16(L)F1765/9):

- 11 = Off Write protection is off

- 10 = Boot 0000h to 01FFh are write-protected, 0200h to 1FFFh may be modified by PMCON control

- 01 = Half 0000h to 0FFFh are write-protected, 1000h to 1FFFh may be modified by PMCON control

- 00 = All 0000h to 1FFFh are write-protected, no addresses may be modified by PMCON control

- Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

- 2: The DEBUG bit in the Configuration Words is managed automatically by device development tools, including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

- **3:** See VBOR parameter for specific trip point voltages.

# 8.2 Low-Power Sleep Mode

The PIC16F1764/5/8/9 devices contain an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC16F1764/5/8/9 devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

# 8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

# 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with the following peripherals only:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/Interrupt-On-Change pins

- Timer1 (with external clock source < 100 kHz)</li>

Note: The PIC16LF1764/5/8/9 devices do not have a configurable Low-Power Sleep mode. PIC16LF1764/5/8/9 devices are unregulated devices and are always in the lowest power state when in Sleep, with no wake-up time penalty. These devices have a lower maximum VDD and I/O voltage than the PIC16F1764/5/8/9. See Section 36.0 "Electrical Specifications" for more information.

# PIC16(L)F1764/5/8/9

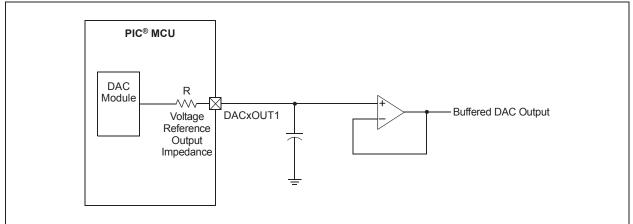

### FIGURE 18-3: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

# 18.5 Operation During Sleep

When the device wakes up from Sleep as the result of an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 18.6 Effects of a Reset

A device Reset affects the following:

- · DAC is disabled

- DAC output voltage is removed from the DACxOUT1 pin

- The REF<9:0> reference selection bits are cleared

# 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- **Note 1:** When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### **FIGURE 19-4**: ANALOG INPUT MODEL

# 22.3 Timer1 Prescaler

Timer1 has four prescaler options, allowing 1, 2, 4 or 8 divisions of the clock input. The CKPS<1:0> bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 22.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built in between pins, SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

# 22.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit, SYNC of the T1CON register, is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 22.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

# 22.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 22.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 22.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 22-3 for timing details.

| <b>TABLE 22-3</b> : | TIMER1 GATE ENABLE |

|---------------------|--------------------|

|                     | SELECTIONS         |

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 23.6.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level, and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either of the external signals is not in Reset, or the ON bit is set, then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control, the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation, the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

#### REGISTER 24-3: CCPRxL: CCPx LOW BYTE REGISTER

| R/W-0/0                           | R/W-0/0                                          | R/W-0/0                                                                                                                    | R/W-0/0                                                           | R/W-0/0                                               | R/W-0/0         | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|-----------------|---------|---------|--|

|                                   |                                                  |                                                                                                                            | CCPF                                                              | R<7:0>                                                |                 |         |         |  |

| bit 7                             |                                                  |                                                                                                                            |                                                                   |                                                       |                 |         | bit 0   |  |

| Legend:                           |                                                  |                                                                                                                            |                                                                   |                                                       |                 |         |         |  |

| R = Readable bit W = Writable bit |                                                  |                                                                                                                            |                                                                   |                                                       |                 |         |         |  |

| u = Bit is unchanged              |                                                  | x = Bit is unknown                                                                                                         |                                                                   | U = Unimplemented bit, read as '0'                    |                 |         |         |  |

| '1' = Bit is set                  |                                                  | '0' = Bit is clea                                                                                                          | ared                                                              | -n/n = Value at POR and BOR/Value at all other Resets |                 |         |         |  |

| bit 7-0                           | CCPRxL<7:<br>MODE<3:0><br>CCPRxL<7:<br>MODE<3:0> | = Capture Mod<br><b>0</b> >: LSB of capt<br>= Compare Mo<br><b>0</b> >: LSB compa<br>= PWM Mode 8<br><b>0</b> >: CCPW<7:02 | ured TMR1 va<br><u>de:</u><br>red to TMR1 v<br>&& FMT = <u>0:</u> | value.                                                | ant eight bits. |         |         |  |

REGISTER 24-4: CCPRxH: CCPx HIGH BYTE REGISTER

MODE<3:0> = PWM Mode and FMT = 1:

CCPRxL<5:0>: Not used.

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | CCPR    | <15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

CCPRxL<7:6>: CCPW<1:0> - Pulse-width Least Significant two bits.

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-0

MODE<3:0> = Capture Mode:

CCPRxH<7:0>: MSB of captured TMR1 value.

MODE<3:0> = Compare Mode:

CCPRxH<7:0>: MSB compared to TMR1 value.

MODE<3:0> = PWM Mode && FMT = 0:

CCPRxH<7:2>: Not used.

CCPRxH<7:2>: Not used.

CCPRxH<1:0>: CCPW<9:8> - Pulse-width Most Significant two bits.

MODE<3:0> = PWM Mode and FMT = 1:

CCPRxH<7:0>: CCPW<9:2> - Pulse-width Most Significant eight bits.

# 25.11 Register Definitions: 10-Bit PWM Control

Long bit name prefixes for the PWM peripherals are shown in Table 25-3. Refer to **Section 1.1.2.2 "Long Bit Names**" for more information.

#### TABLE 25-3: BIT NAME PREFIXES

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| PWM3                | PWM3            |

| PWM4 <sup>(1)</sup> | PWM4            |

Note 1: PIC16(L)F1768/9 devices only.

#### REGISTER 25-1: PWMxCON: PWMx CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-------|---------|-----|-----|-----|-------|

| EN      | —   | OUT   | POL     | —   | —   | —   | —     |

| bit 7   |     | •     |         |     |     |     | bit 0 |

| Legend:         |                                                   |                            |                                                       |

|-----------------|---------------------------------------------------|----------------------------|-------------------------------------------------------|

| R = Readabl     | e bit                                             | W = Writable bit           |                                                       |

| u = Bit is und  | changed                                           | x = Bit is unknown         | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is se | et                                                | '0' = Bit is cleared       | -n/n = Value at POR and BOR/Value at all other Resets |

|                 |                                                   |                            |                                                       |

| bit 7           | EN: PWMx                                          | Module Enable bit          |                                                       |

|                 | 1 = PWMx                                          | module is enabled          |                                                       |

|                 | 0 = PWMx                                          | module is disabled         |                                                       |

| bit 6           | Unimplem                                          | ented: Read as '0'         |                                                       |

| bit 5           | OUT: PWM                                          | Ix Module Output Level Whe | en Read bit                                           |

| bit 4           | bit 4 <b>POL:</b> PWMx Output Polarity Select bit |                            |                                                       |

|                 | 1 = PWMx                                          | output is active-low       |                                                       |

|                 | 0 = PWMx                                          | output is active-high      |                                                       |

| bit 3-0         | Unimplem                                          | ented: Read as '0'         |                                                       |

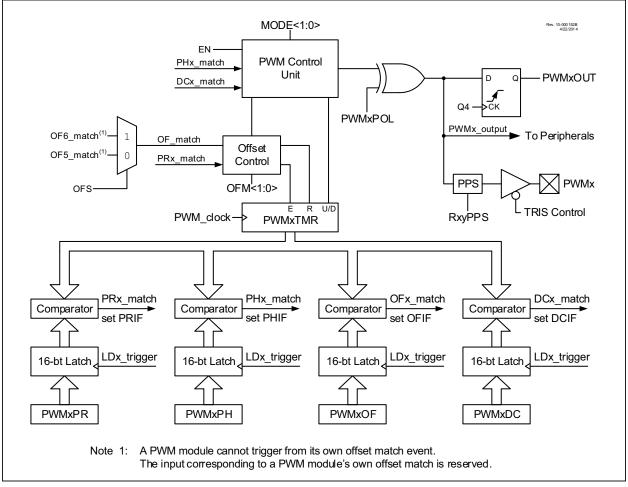

# 26.0 16-BIT PULSE-WIDTH MODULATION (PWM) MODULE

The Pulse-Width Modulation (PWM) module generates a Pulse-Width Modulated signal determined by the phase, duty cycle, period and offset event counts that are contained in the following registers:

- PWMxPH registers

- PWMxDC registers

- PWMxPR registers

- PWMxOF registers

Figure 26-1 shows a simplified block diagram of the PWM operation.

Each PWM module has four modes of operation:

- Standard

- Set On Match

- Toggle On Match

- · Center-Aligned

For a more detailed description of each PWM mode, refer to Section 26.2 "PWM Modes".

Each PWM module has four Offset modes:

- Independent Run

- Slave Run with Synchronous Start

- · One-Shot Slave with Synchronous Start

- Continuous Run Slave with Synchronous Start and Timer Reset

Using the Offset modes, each PWM module can offset its waveform relative to any other PWM module in the same device. For a more detailed description of the Offset modes, refer to **Section 26.3 "Offset Modes"**.

Every PWM module has a configurable reload operation to ensure all event count buffers change at the end of a period, thereby avoiding signal glitches. Figure 26-2 shows a simplified block diagram of the reload operation. For a more detailed description of the reload operation, refer to Section 26.4 "Reload Operation".

# FIGURE 26-1: 16-BIT PWMx BLOCK DIAGRAM

# PIC16(L)F1764/5/8/9

| FIGURE 27-12: | FULL-BRIDGE FORWARD MODE COG OPERATION WITH CCP1 |

|---------------|--------------------------------------------------|

| CCP1          |                                                  |

| COGxA         |                                                  |

| COGxB         |                                                  |

| COGxC         |                                                  |

| COGxD         |                                                  |

### FIGURE 27-13: FULL-BRIDGE MODE COG OPERATION WITH CCP1 AND DIRECTION CHANGE

| CCP1  |  |          |                   |        |  |

|-------|--|----------|-------------------|--------|--|

| COGxA |  |          |                   |        |  |

| COGxB |  | →   ← Fa | alling Event Dead | I-Band |  |

| COGxC |  |          |                   |        |  |

| COGxD |  |          |                   |        |  |

| MD0   |  |          |                   |        |  |

| R/W-0/0         | R/W-0/0                          | U-0                              | U-0            | R/W-0/0                            | R/W-0/0           | R/W-0/0          | R/W-0/0      |

|-----------------|----------------------------------|----------------------------------|----------------|------------------------------------|-------------------|------------------|--------------|

| RDBS            | FDBS                             | —                                | _              | POLD                               | POLC              | POLB             | POLA         |

| bit 7           |                                  |                                  |                |                                    |                   |                  | bit 0        |

|                 |                                  |                                  |                |                                    |                   |                  |              |

| Legend:         |                                  |                                  |                |                                    |                   |                  |              |

| R = Readable    | bit                              | W = Writable                     | bit            |                                    |                   |                  |              |

| u = Bit is unch | anged                            | x = Bit is unkr                  | nown           | U = Unimpler                       | mented bit, read  | l as '0'         |              |

| 1' = Bit is set |                                  | '0' = Bit is clea                | ared           | -n/n = Value a                     | at POR and BO     | R/Value at all c | other Resets |

|                 |                                  |                                  |                |                                    |                   |                  |              |

| bit 7           |                                  | 0                                |                | Timing Source S                    |                   |                  |              |

|                 |                                  |                                  |                | l for dead-band<br>d for dead-banc | 00                |                  |              |

| bit 6           | FDBS: COG                        | k Falling Event                  | Dead-band 1    | iming Source s                     | elect bit         |                  |              |

|                 | 1 = Delay cha                    | ain and COGxD                    | BF are used    | for dead-band                      | timing generation | on               |              |

|                 | 0 = COGx_cl                      | ock and COGx                     | DBF are use    | d for dead-band                    | I timing generat  | ion              |              |

| bit 5-4         | Unimplemen                       | ted: Read as '                   | 0'             |                                    |                   |                  |              |

| bit 3           | POLD: COG                        | xD Output Pola                   | rity Control b | it                                 |                   |                  |              |

|                 |                                  | el of COGxD o                    |                |                                    |                   |                  |              |

|                 | 0 = Active lev                   | el of COGxD o                    | utput is high  |                                    |                   |                  |              |

| bit 2           |                                  | xC Output Pola                   | 5              | it                                 |                   |                  |              |

|                 |                                  | el of COGxC o                    |                |                                    |                   |                  |              |

|                 |                                  | el of COGxC o                    |                |                                    |                   |                  |              |

| bit 1           |                                  | kB Output Pola                   |                | it                                 |                   |                  |              |

|                 |                                  | vel of COGxB o<br>vel of COGxB o |                |                                    |                   |                  |              |

|                 |                                  |                                  |                | :+                                 |                   |                  |              |

| bit 0           |                                  | xA Output Pola<br>vel of COGxA o | 5              | ii.                                |                   |                  |              |

|                 | 1 = Active lev<br>0 = Active lev |                                  |                |                                    |                   |                  |              |

# REGISTER 27-2: COGxCON1: COGx CONTROL REGISTER 1

#### REGISTER 29-4: OPAxPCHS: OP AMP x POSITIVE CHANNEL SOURCE SELECT REGISTER

| U-0              | U-0        | U-0               | U-0        | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|------------------|------------|-------------------|------------|-------------------------------------------------------|---------|---------|---------|--|--|

| _                | _          |                   | _          |                                                       | PCH     | <3:0>   |         |  |  |

| bit 7            |            |                   |            |                                                       |         |         | bit 0   |  |  |

|                  |            |                   |            |                                                       |         |         |         |  |  |

| Legend:          |            |                   |            |                                                       |         |         |         |  |  |

| R = Readable I   | bit        | W = Writable      | bit        |                                                       |         |         |         |  |  |

| u = Bit is uncha | anged      | x = Bit is unkr   | iown       | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| '1' = Bit is set |            | '0' = Bit is clea | ared       | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

|                  |            |                   |            |                                                       |         |         |         |  |  |

| bit 7-4          | Unimplemen | nted: Read as '   | ) <b>'</b> |                                                       |         |         |         |  |  |

|         | Ommplemented. Read as 0                                     |  |  |  |  |  |  |  |

|---------|-------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 3-0 | PCH<3:0>: Op Amp Non-Inverting Input Channel Selection bits |  |  |  |  |  |  |  |

|         | 1111 = Reserved; do not use                                 |  |  |  |  |  |  |  |

|         | •                                                           |  |  |  |  |  |  |  |

|         | •                                                           |  |  |  |  |  |  |  |

|         | •                                                           |  |  |  |  |  |  |  |

|         | 1010 = Reserved; do not use                                 |  |  |  |  |  |  |  |

|         | 1001 = Programmable Ramp Generator PRG2_out <sup>(1)</sup>  |  |  |  |  |  |  |  |

|         | 1000 = Programmable Ramp Generator PRG1_out                 |  |  |  |  |  |  |  |

|         | 0111 = Reserved. Do not use.                                |  |  |  |  |  |  |  |

|         | 0110 = FVR Buffer2                                          |  |  |  |  |  |  |  |

|         | 0101 = $DAC\overline{4}$ out <sup>(1)</sup>                 |  |  |  |  |  |  |  |

|         | 0100 = DAC3_out                                             |  |  |  |  |  |  |  |

|         | 0011 = DAC2_out <sup>(1)</sup>                              |  |  |  |  |  |  |  |

|         | 0010 = DAC1_out                                             |  |  |  |  |  |  |  |

|         | $0001 = OPAxIN1 + pin^{(1)}$                                |  |  |  |  |  |  |  |

|         | 0000 = OPAxIN0 + pin                                        |  |  |  |  |  |  |  |

|         | •                                                           |  |  |  |  |  |  |  |

Note 1: PIC16(L)F1768/9 only

#### TABLE 29-2: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

| Name                    | Bit 7     | Bit 6                | Bit 5      | Bit 4    | Bit 3            | Bit 2 | Bit 1      | Bit 0  | Register<br>on Page |  |

|-------------------------|-----------|----------------------|------------|----------|------------------|-------|------------|--------|---------------------|--|

| ANSELB <sup>(2)</sup>   | ANSB      | <7:6>                | ANSE       | 8<5:4>   | —                | —     | —          | —      | 143                 |  |

| ANSELC <sup>(2)</sup>   | ANSC<     | <7:6> <sup>(2)</sup> | _          | _        | ANSC             | <3:2> | ANSC       | <1:0>  | 148                 |  |

| DACxCON0                | EN        | FM                   | OE1        | —        | PSS<             | <1:0> | NSS        | <1:0>  | 188                 |  |

| DACxREF                 |           |                      |            | REF<4:0> |                  |       |            |        |                     |  |

| DACxREFL <sup>(2)</sup> | REF<7:0>  |                      |            |          |                  |       |            |        |                     |  |

| DACxREFH <sup>(2)</sup> | REF<15:8> |                      |            |          |                  |       |            |        | 194                 |  |

| FVRCON                  | FVREN     | FVRRDY               | TSEN       | TSRNG    | CDAFVR<1:0>      |       | ADFVR<1:0> |        | 169                 |  |

| OPAxCON                 | EN        | —                    | —          | UG       | —                | ORPOL | ORM        | <1:0>  | 348                 |  |

| OPAxNCHS                | _         | —                    | —          | —        |                  | NCH<  | 3:0>       |        | 350                 |  |

| OPAxPCHS                | _         | _                    | —          | PCH<3:0> |                  |       |            |        |                     |  |

| OPAxORS                 | _         | _                    | — ORS<4:0> |          |                  |       |            | 349    |                     |  |

| TRISB <sup>(2)</sup>    | TRISE     | 3<7:6>               | TRISE      | 3<5:4>   | _                | _     | _          | _      | 142                 |  |

| TRISC <sup>(2)</sup>    | TRISC     | <7:6> <sup>(2)</sup> | TRISC      | 2<5:4>   | TRISC<3:2> TRISC |       |            | C<1:0> | 147                 |  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1768/9 only

# 32.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a chip select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 32-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 32-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 32-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin, which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin. To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin), and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its Slave Select line must disregard the clock and transmission signals and must not transmit out any data of its own.

### TABLE 33-3: BAUD RATE FORMULAS

| Co   | onfiguration B | its  |                     | Baud Rate Formula |

|------|----------------|------|---------------------|-------------------|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Baud Kale Formula |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0              | 1    | 8-bit/Asynchronous  |                   |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |

| 1    | 0              | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1              | х    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPxBRGH, SPxBRGL register pair.

#### TABLE 33-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name     | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |  |

|----------|-----------|-------|-------|-------|-------|-------|-------|-------|---------------------|--|

| BAUD1CON | ABDOVF    | RCIDL | —     | SCKP  | BRG16 |       | WUE   | ABDEN | 442                 |  |

| RC1STA   | SPEN      | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 441                 |  |

| SP1BRGL  | BRG<7:0>  |       |       |       |       |       |       |       |                     |  |

| SP1BRGH  | BRG<15:8> |       |       |       |       |       |       |       | 443                 |  |

| TX1STA   | CSRC      | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 440                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

|        |                                     | SYNC = 0, BRGH = 0, BRG16 = 0 |                              |                   |            |                              |                    |            |                              |                |            |                              |

|--------|-------------------------------------|-------------------------------|------------------------------|-------------------|------------|------------------------------|--------------------|------------|------------------------------|----------------|------------|------------------------------|

| BAUD   | Fosc = 32.000 MHz Fosc = 20.000 MHz |                               | Foso                         | Fosc = 18.432 MHz |            |                              | Fosc = 11.0592 MHz |            |                              |                |            |                              |

| RATE   | Actual<br>Rate                      | %<br>Error                    | SPxBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPxBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPxBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRG<br>value<br>(decimal) |

| 300    | —                                   | _                             | _                            | —                 | _          | _                            | _                  | _          | _                            | _              | _          | —                            |

| 1200   | —                                   | _                             | —                            | 1221              | 1.73       | 255                          | 1200               | 0.00       | 239                          | 1200           | 0.00       | 143                          |

| 2400   | 2404                                | 0.16                          | 207                          | 2404              | 0.16       | 129                          | 2400               | 0.00       | 119                          | 2400           | 0.00       | 71                           |

| 9600   | 9615                                | 0.16                          | 51                           | 9470              | -1.36      | 32                           | 9600               | 0.00       | 29                           | 9600           | 0.00       | 17                           |

| 10417  | 10417                               | 0.00                          | 47                           | 10417             | 0.00       | 29                           | 10286              | -1.26      | 27                           | 10165          | -2.42      | 16                           |

| 19.2k  | 19.23k                              | 0.16                          | 25                           | 19.53k            | 1.73       | 15                           | 19.20k             | 0.00       | 14                           | 19.20k         | 0.00       | 8                            |

| 57.6k  | 55.55k                              | -3.55                         | 3                            | —                 | _          | _                            | 57.60k             | 0.00       | 7                            | 57.60k         | 0.00       | 2                            |

| 115.2k | —                                   | _                             | —                            | —                 | _          | —                            | —                  | _          | —                            | _              | _          | _                            |

|        |                | SYNC = 0, BRGH = 0, BRG16 = 0 |                              |                |            |                              |                |            |                              |                |            |                              |

|--------|----------------|-------------------------------|------------------------------|----------------|------------|------------------------------|----------------|------------|------------------------------|----------------|------------|------------------------------|

| BAUD   | Fos            | c = 8.000                     | ) MHz                        | Fos            | c = 4.000  | ) MHz                        | Foso           | ; = 3.686  | 4 MHz                        | Fos            | c = 1.000  | ) MHz                        |

| RATE   | Actual<br>Rate | %<br>Error                    | SPxBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRG<br>value<br>(decimal) |

| 300    | —              | _                             | _                            | 300            | 0.16       | 207                          | 300            | 0.00       | 191                          | 300            | 0.16       | 51                           |

| 1200   | 1202           | 0.16                          | 103                          | 1202           | 0.16       | 51                           | 1200           | 0.00       | 47                           | 1202           | 0.16       | 12                           |

| 2400   | 2404           | 0.16                          | 51                           | 2404           | 0.16       | 25                           | 2400           | 0.00       | 23                           | —              | —          | —                            |

| 9600   | 9615           | 0.16                          | 12                           | —              | _          | _                            | 9600           | 0.00       | 5                            | —              | _          | —                            |

| 10417  | 10417          | 0.00                          | 11                           | 10417          | 0.00       | 5                            | —              | _          | _                            | —              | _          | _                            |

| 19.2k  | —              | _                             | _                            | —              | _          | _                            | 19.20k         | 0.00       | 2                            | —              | _          | _                            |

| 57.6k  | —              | _                             | _                            | —              | _          | _                            | 57.60k         | 0.00       | 0                            | —              | _          | _                            |

| 115.2k | _              | _                             | _                            | _              | _          | —                            | _              | _          | _                            | —              | _          | —                            |

|        |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                              |                   |            |                              |                |            |                              |                    |            |                              |

|--------|----------------|-------------------------------|------------------------------|-------------------|------------|------------------------------|----------------|------------|------------------------------|--------------------|------------|------------------------------|

| BAUD   | Fosc           | : = 32.00                     | 0 MHz                        | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz            |                |            | Fosc                         | Fosc = 11.0592 MHz |            |                              |

| RATE   | Actual<br>Rate | %<br>Error                    | SPxBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPxBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPxBRG<br>value<br>(decimal) |

| 300    | —              | _                             | _                            | —                 | _          | _                            | _              | _          | _                            | _                  | _          | _                            |

| 1200   | —              | —                             | —                            | —                 |            | —                            | —              | —          | —                            | —                  | —          | —                            |

| 2400   | —              | —                             | —                            | —                 |            | —                            | —              | —          | —                            | —                  | —          | —                            |

| 9600   | 9615           | 0.16                          | 207                          | 9615              | 0.16       | 129                          | 9600           | 0.00       | 119                          | 9600               | 0.00       | 71                           |

| 10417  | 10417          | 0.00                          | 191                          | 10417             | 0.00       | 119                          | 10378          | -0.37      | 110                          | 10473              | 0.53       | 65                           |

| 19.2k  | 19.23k         | 0.16                          | 103                          | 19.23k            | 0.16       | 64                           | 19.20k         | 0.00       | 59                           | 19.20k             | 0.00       | 35                           |

| 57.6k  | 57.14k         | -0.79                         | 34                           | 56.82k            | -1.36      | 21                           | 57.60k         | 0.00       | 19                           | 57.60k             | 0.00       | 11                           |

| 115.2k | 117.64k        | 2.12                          | 16                           | 113.64k           | -1.36      | 10                           | 115.2k         | 0.00       | 9                            | 115.2k             | 0.00       | 5                            |

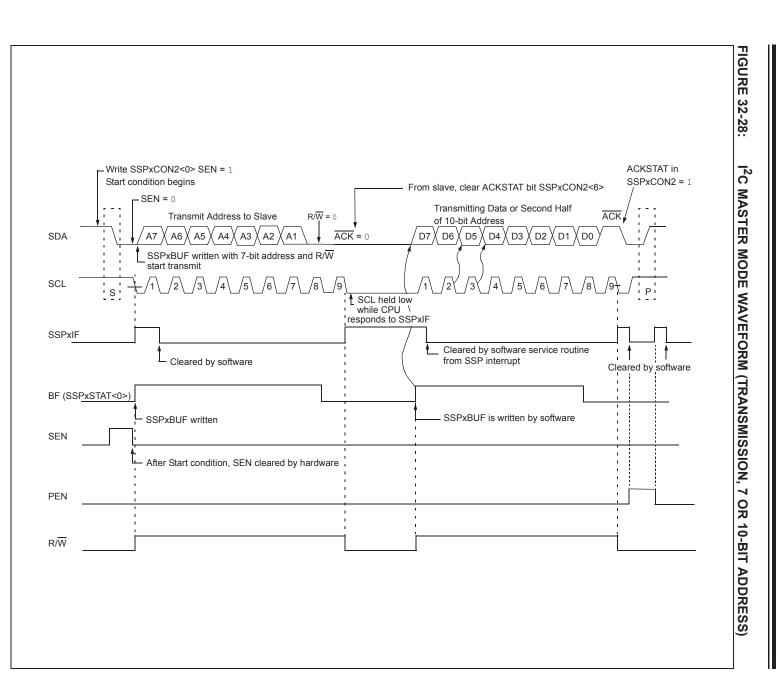

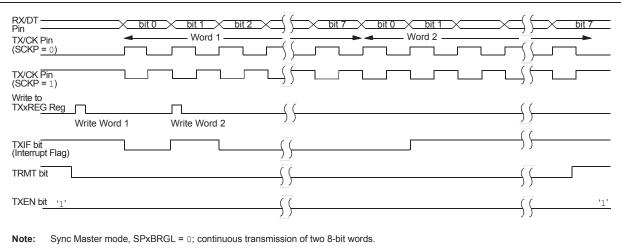

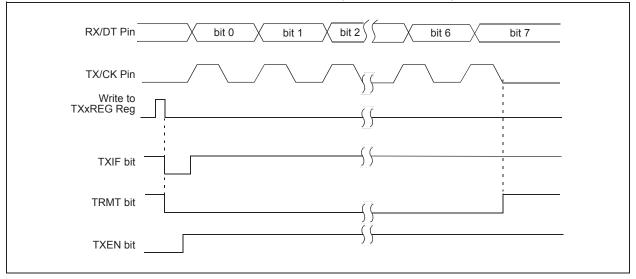

### FIGURE 33-10: SYNCHRONOUS TRANSMISSION

#### FIGURE 33-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# 38.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 38.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 38.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 38.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

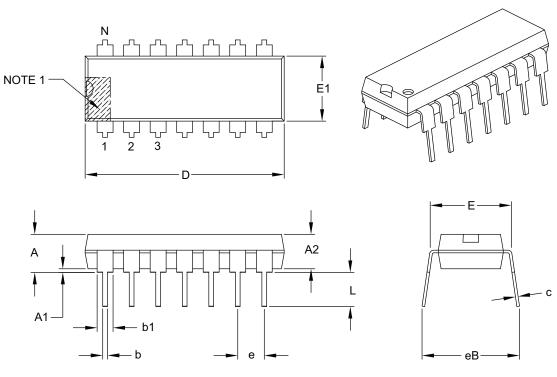

### 39.2 Package Details

The following sections give the technical details of the packages.

# 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |      |          |      |  |  |  |

|----------------------------|------------------|------|----------|------|--|--|--|

| Dimensio                   | MIN              | NOM  | MAX      |      |  |  |  |

| Number of Pins             | Number of Pins N |      |          |      |  |  |  |

| Pitch                      | е                |      | .100 BSC |      |  |  |  |

| Top to Seating Plane       | Α                | -    | -        | .210 |  |  |  |

| Molded Package Thickness   | A2               | .115 | .130     | .195 |  |  |  |

| Base to Seating Plane      | A1               | .015 | -        | -    |  |  |  |

| Shoulder to Shoulder Width | E                | .290 | .310     | .325 |  |  |  |

| Molded Package Width       | E1               | .240 | .250     | .280 |  |  |  |

| Overall Length             | D                | .735 | .750     | .775 |  |  |  |

| Tip to Seating Plane       | L                | .115 | .130     | .150 |  |  |  |

| Lead Thickness             | с                | .008 | .010     | .015 |  |  |  |

| Upper Lead Width           | b1               | .045 | .060     | .070 |  |  |  |

| Lower Lead Width           | b                | .014 | .018     | .022 |  |  |  |

| Overall Row Spacing §      | eB               | _    | _        | .430 |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

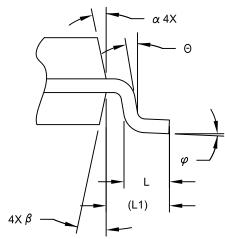

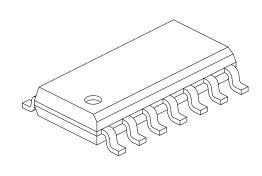

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| 1/1   | EW | C |

|-------|----|---|

| · v I |    |   |

| Units                    |    | MILLIMETERS |     |      |

|--------------------------|----|-------------|-----|------|

| Dimension Limits         |    | MIN         | NOM | MAX  |

| Number of Pins           | N  | 14          |     |      |

| Pitch                    | е  | 1.27 BSC    |     |      |

| Overall Height           | A  | -           | -   | 1.75 |

| Molded Package Thickness | A2 | 1.25        | -   | -    |

| Standoff §               | A1 | 0.10        | -   | 0.25 |

| Overall Width            | E  | 6.00 BSC    |     |      |

| Molded Package Width     | E1 | 3.90 BSC    |     |      |

| Overall Length           | D  | 8.65 BSC    |     |      |

| Chamfer (Optional)       | h  | 0.25        | -   | 0.50 |

| Foot Length              | L  | 0.40        | -   | 1.27 |

| Footprint                | L1 | 1.04 REF    |     |      |

| Lead Angle               | Θ  | 0°          | -   | -    |

| Foot Angle               | φ  | 0°          | -   | 8°   |

| Lead Thickness           | С  | 0.10        | -   | 0.25 |

| Lead Width               | b  | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2