# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 2x5b, 2x10b                                              |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1768-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

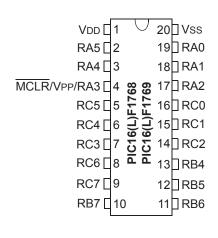

Note: See Table 4 for location of all peripheral functions.

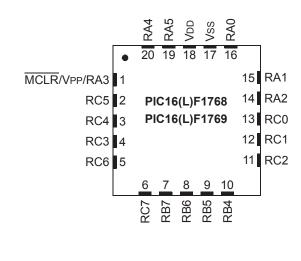

#### FIGURE 4: 20-PIN QFN (4x4)

Note: See Table 4 for location of all peripheral functions.

#### **TABLE 1-2:** PIC16(L)F1764/5 PINOUT DESCRIPTION (CONTINUED)

| Name                    | Function                  | Input<br>Type | Output<br>Type | Description                              |

|-------------------------|---------------------------|---------------|----------------|------------------------------------------|

| RC4/T3G/PRG1R/CLCIN1/CK | RC4                       | RC4 TTL/ST    |                | General purpose I/O.                     |

|                         | T3G <sup>(1)</sup> TTL/ST |               | _              | Timer3 gate input.                       |

|                         | PRG1R <sup>(1)</sup>      | TTL/ST        | _              | Ramp generator set_rising input.         |

|                         | CLCIN1 <sup>(1)</sup>     | TTL/ST        | _              | CLC Input 1.                             |

|                         | CK <sup>(1)</sup>         | TTL/ST        | _              | EUSART clock input.                      |

| RC5/T3CKI/PRG1F/CCP1/RX | RC5                       | TTL/ST        | CMOS           | General purpose I/O.                     |

|                         | T3CKI <sup>(1)</sup>      | TTL/ST        | —              | Timer3 clock input.                      |

|                         | PRG1F <sup>(1)</sup>      | TTL/ST        | —              | Ramp generator set_falling input.        |

|                         | CCP1 <sup>(1)</sup>       | TTL/ST        | —              | CCP1 capture input.                      |

|                         | RX <sup>(1,3)</sup>       | TTL/ST        | —              | EUSART receive input.                    |

| VDD                     | Vdd                       | Power         | —              | Positive supply.                         |

| Vss                     | Vss                       | Power         | —              | Ground reference.                        |

| OUT <sup>(2)</sup>      | C1OUT                     |               | CMOS           | Comparator 1 output.                     |

|                         | C2OUT                     |               | CMOS           | Comparator 2 output.                     |

|                         | CCP1                      |               | CMOS           | Compare/PWM1 output.                     |

|                         | MD10UT                    |               | CMOS           | Data Signal Modulator 1 output.          |

|                         | PWM3                      |               | CMOS           | PWM3 output.                             |

|                         | PWM5                      |               | CMOS           | PWM5 output.                             |

|                         | COG1A                     |               | CMOS           | Complementary Output Generator Output A. |

|                         | COG1B                     |               | CMOS           | Complementary Output Generator Output B. |

|                         | COG1C                     |               | CMOS           | Complementary Output Generator Output C. |

|                         | COG1D                     |               | CMOS           | Complementary Output Generator Output D. |

|                         | SDA <sup>(3)</sup>        |               | OD             | I <sup>2</sup> C data output.            |

|                         | SCK                       |               | CMOS           | SPI clock output.                        |

|                         | SCL <sup>(3)</sup>        |               | OD             | I <sup>2</sup> C clock output.           |

|                         | SDO                       |               | CMOS           | SPI data output.                         |

|                         | ТХ                        |               | CMOS           | EUSART asynchronous TX data out.         |

|                         | СК                        |               | CMOS           | EUSART synchronous clock out.            |

|                         | DT <sup>(3)</sup>         |               | CMOS           | EUSART synchronous data output.          |

|                         | CLC10UT                   |               | CMOS           | Configurable Logic Cell 1 output.        |

|                         | CLC2OUT                   |               | CMOS           | Configurable Logic Cell 2 output.        |

|                         | CLC3OUT                   |               | CMOS           | Configurable Logic Cell 3 output.        |

XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS Input Selection registers. 2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as peripheral digital outputs with the PPS Output Selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

HV = High Voltage

#### FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1764/5/8/9

|                 | PC<14:0>                   | 7               |

|-----------------|----------------------------|-----------------|

|                 | L, CALLW 15<br>N, RETLW 15 |                 |

|                 | Stack Level 0              | ר ר             |

|                 | Stack Level 1              |                 |

|                 | •                          |                 |

|                 | Stack Level 15             |                 |

|                 | Reset Vector               | 0000h           |

|                 | •                          |                 |

|                 | Interrupt Vector           | 0004h           |

| ſ               |                            | 000411<br>0005h |

| On-Chip         | Page 0                     | 07554           |

| Program $\prec$ |                            | 07FFh<br>0800h  |

| Memory          | Page 1                     | 000011          |

| l               |                            | 0FFFh           |

|                 | Rollover to Page 0         | 1000h           |

|                 | •                          |                 |

|                 | Rollover to Page 1         | 7FFFh           |

## 3.2.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSRn to point to the program memory.

#### 3.2.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

| EXAMPLE 3-1:  | RETLW INSTRUCTION   |

|---------------|---------------------|

| constants     |                     |

| BRW           | ;Add Index in W to  |

|               | ;program counter to |

|               | ;select data        |

| RETLW DATA0   | ;Index0 data        |

| RETLW DATA1   | ;Index1 data        |

| RETLW DATA2   |                     |

| RETLW DATA3   |                     |

| my function   |                     |

| ; LOTS OF COI | ЭF.                 |

|               | TA_INDEX            |

| ; THE CONSTAN | NT IS IN W          |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available, so the older table read method must be used.

#### 3.2.1.2 Indirect Read with FSRn

The program memory can be accessed as data by setting bit 7 of the FSRnH register and reading the matching INDFn register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDFn registers. Instructions that access the program memory via the FSRn require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSRn.

The high directive will set bit 7 if a label points to a location in program memory.

#### TABLE 3-16: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    | LE 3-10.   |                                                                             |                  |                     |                   |                 |           |        | i      | +                 | ·                               |

|--------------------|------------|-----------------------------------------------------------------------------|------------------|---------------------|-------------------|-----------------|-----------|--------|--------|-------------------|---------------------------------|

| Addr               | Name       | Bit 7                                                                       | Bit 6            | Bit 5               | Bit 4             | Bit 3           | Bit 2     | Bit 1  | Bit 0  | Value on POR, BOR | Value on<br>All Other<br>Resets |

| Bank               | < 8        |                                                                             |                  |                     |                   |                 |           |        |        |                   |                                 |

| 40Ch               |            |                                                                             |                  |                     |                   |                 |           |        |        |                   |                                 |

| <br>40Dh           | _          | Unimpleme                                                                   | nted             |                     |                   |                 |           |        |        | _                 | _                               |

| 40Eh               | HIDRVC     | _                                                                           | _                | HIDC                | <5:4>             | —               | —         | _      | —      | 00                | 00                              |

| 40Fh               |            |                                                                             | •                | •                   |                   |                 |           | •      | •      |                   |                                 |

| <br>412h           | _          | Unimpleme                                                                   | nted             |                     |                   |                 |           |        |        | -                 | —                               |

| 413h               | T4TMR      | Holding Reg                                                                 | gister for the 8 | -Bit TMR4 Regist    | er                |                 |           |        |        | 0000 0000         | 0000 0000                       |

| 413h               | T4PR       | TMR4 Peric                                                                  | od Register      |                     |                   |                 |           |        |        | 1111 1111         | 1111 1111                       |

| 415h               | T4CON      | ON                                                                          |                  | CKPS<2:0>           |                   |                 | OUTP      | S<3:0> |        | 0000 0000         | 0000 0000                       |

| 416h               | T4HLT      | PSYNC                                                                       | CKPOL            | CKSYNC              |                   |                 | MODE<4:0> |        |        | 0000 0000         | 0000 0000                       |

| 417h               | T4CLKCON   | —                                                                           | _                | —                   | —                 |                 | CS<       | <3:0>  |        | 0000              | 0000                            |

| 418h               | T4RST      | —                                                                           | _                | —                   | —                 |                 | RSEL      | _<3:0> |        | 0000              | 0000                            |

| 419h               | _          | Unimpleme                                                                   | nted             | •                   |                   | ·               |           |        |        | _                 | —                               |

| 41Ah               | T6TMR      | Holding Register for the 8-Bit TMR4 Register                                |                  |                     |                   |                 |           |        |        | 0000 0000         | 0000 0000                       |

| 41Bh               | T6PR       | TMR4 Perio                                                                  | od Register      |                     |                   |                 |           |        |        | 1111 1111         | 1111 1111                       |

| 41Ch               | T6CON      | ON                                                                          |                  | CKPS<2:0>           |                   |                 | OUTP      | S<3:0> |        | 0000 0000         | 0000 0000                       |

| 41Dh               | T6HLT      | PSYNC                                                                       | CKPOL            | CKSYNC              |                   | I               | MODE<4:0> |        |        | 0000 0000         | 0000 0000                       |

| 41Eh               | T6CLKCON   | —                                                                           | —                | —                   | _                 |                 | CS<       | <3:0>  |        | 0000              | 0000                            |

| 41Fh               | T6RST      | —                                                                           | —                | —                   | —                 |                 | RSEL      | _<3:0> |        | 0000              | 0000                            |

| Bank               | <b>(</b> 9 |                                                                             |                  |                     |                   |                 |           |        |        |                   |                                 |

| 48Ch<br>to<br>492h | _          | Unimpleme                                                                   | nted             |                     |                   |                 |           |        |        | _                 | _                               |

| 493h               | TMR3L      | Holding Reg                                                                 | gister for the L | east Significant B  | yte of the 16-Bi  | t TMR1 Register | r         |        |        | XXXX XXXX         | uuuu uuuu                       |

| 494h               | TMR3H      | Holding Reg                                                                 | gister for the N | lost Significant By | yte of the 16-Bit | TMR1 Register   |           |        |        | XXXX XXXX         | uuuu uuuu                       |

| 495h               | T3CON      | CS                                                                          | <1:0>            | CKPS                | <1:0>             | OSCEN           | SYNC      | —      | ON     | 0000 00-0         | uuuu uu-u                       |

| 496h               | T3GCON     | GE                                                                          | GPOL             | GTM                 | GSPM              | GGO/DONE        | GVAL      | GSS    | S<1:0> | 00x0 0x00         | uuuu uxuu                       |

| 497h<br>to<br>499h | _          | Unimplemented                                                               |                  |                     |                   |                 |           |        |        | _                 | _                               |

| 49Ah               | TMR5L      | Holding Register for the Least Significant Byte of the 16-Bit TMR1 Register |                  |                     |                   |                 |           |        |        | XXXX XXXX         | uuuu uuuu                       |

| 49Bh               | TMR5H      | Holding Reg                                                                 | gister for the N | lost Significant By | yte of the 16-Bit | TMR1 Register   |           |        |        | XXXX XXXX         | uuuu uuuu                       |

| 49Ch               | T5CON      | CS                                                                          | <1:0>            | CKPS                | 0000 00-0         | uuuu uu-u       |           |        |        |                   |                                 |

| 49Dh               | T5GCON     | GE                                                                          | GPOL             | GTM                 | GSPM              | GGO/DONE        | GVAL      | GSS    | 6<1:0> | 00x0 0x00         | uuuu uxuu                       |

| 49Eh<br>to<br>49Fh | —          | Unimpleme                                                                   | nted             |                     |                   |                 |           |        |        | _                 | _                               |

Legend: x = unknown; u = unchanged; q = value depends on condition; - = unimplemented, read as '0'; x = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1768/9 only.

3: PIC16(L)F1764/5 only.

4: Unimplemented on PIC16LF1764/5/8/9.

#### 4.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

4.7 Register Definitions: Device and Revision

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|   | R         | R | R | R | R | R     |  |  |  |  |

|---|-----------|---|---|---|---|-------|--|--|--|--|

|   | DEV<13:8> |   |   |   |   |       |  |  |  |  |

|   | bit 13    |   |   |   |   | bit 8 |  |  |  |  |

|   |           |   |   |   |   |       |  |  |  |  |

| R | R         | R | R | R | R | R     |  |  |  |  |

DEV<7:0>

'1' = Bit is set

bit 7

#### Legend:

R = Readable bit

R

'0' = Bit is cleared

#### bit 13-0 **DEV<13:0>**: Device ID bits

| Device      | DEVID<13:0> Values                 |  |  |  |  |  |  |  |

|-------------|------------------------------------|--|--|--|--|--|--|--|

| PIC16F1764  | 11 0000 1000 0000 ( <b>3080h</b> ) |  |  |  |  |  |  |  |

| PIC16F1765  | 11 0000 1000 0001 ( <b>3081h</b> ) |  |  |  |  |  |  |  |

| PIC16F1768  | 11 0000 1000 0100 ( <b>3084h</b> ) |  |  |  |  |  |  |  |

| PIC16F1769  | 11 0000 1000 0101 ( <b>3085h</b> ) |  |  |  |  |  |  |  |

| PIC16LF1764 | 11 0000 1000 0010 ( <b>3082h</b> ) |  |  |  |  |  |  |  |

| PIC16LF1765 | 11 0000 1000 0011 ( <b>3083h</b> ) |  |  |  |  |  |  |  |

| PIC16LF1768 | 11 0000 1000 0110 ( <b>3086h</b> ) |  |  |  |  |  |  |  |

| PIC16LF1769 | 11 0000 1000 0111 ( <b>3087h</b> ) |  |  |  |  |  |  |  |

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

bit 0

#### 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS<1:0> bits:

- Default system oscillator determined by the FOSCx bits in the Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS<1:0>) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When SCS<1:0> = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When SCS<1:0> = 01, the system clock source is the secondary oscillator.

- When SCS<1:0> = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCSx bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

#### 5.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the OSCEN control bit in the T1CON register. See **Section 22.0 "Timer1/3/5 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCSx bits can be configured to select the secondary oscillator.

#### 5.3.5 CLOCK SWITCH BEFORE SLEEP

When a clock switch from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the sleep instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

#### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Secondary Oscillator and RC).

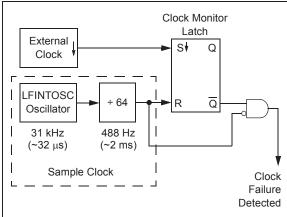

FIGURE 5-9: FSCM BLOCK DIAGRAM

#### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCSx bits of the OSCCON register. When the SCSx bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

#### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

#### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | х  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | х  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during Normal Operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during Normal Operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | 1u uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit (GIE) is set, the return address is pushed onto the stack and the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| REGISTER 11-5: | WPUA: WEAK PULL-UP PORTA REGISTER |  |

|----------------|-----------------------------------|--|

|                |                                   |  |

| U-0             | U-0                     | R/W-1/1                                                      | R/W-1/1                                               | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |

|-----------------|-------------------------|--------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| _               | _                       |                                                              | WPUA<5:0> <sup>(1,2)</sup>                            |                                                       |         |         |         |  |  |  |

| bit 7           | ·                       |                                                              |                                                       |                                                       |         |         | bit 0   |  |  |  |

|                 |                         |                                                              |                                                       |                                                       |         |         |         |  |  |  |

| Legend:         |                         |                                                              |                                                       |                                                       |         |         |         |  |  |  |

| R = Readabl     | e bit                   | W = Writable                                                 | bit                                                   |                                                       |         |         |         |  |  |  |

| u = Bit is und  | changed                 | x = Bit is unki                                              | a = Bit is unknown U = Unimplemented bit, read as '0' |                                                       |         |         |         |  |  |  |

| '1' = Bit is se | t                       | '0' = Bit is cle                                             | ared                                                  | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| h:+ 7 0         |                         | unte de De estere (                                          | 01                                                    |                                                       |         |         |         |  |  |  |

| bit 7-6         | Unimpieme               | Unimplemented: Read as '0'                                   |                                                       |                                                       |         |         |         |  |  |  |

| bit 5-0         | WPUA<5:0                | WPUA<5:0>: Weak Pull-up PORTA Register bits <sup>(1,2)</sup> |                                                       |                                                       |         |         |         |  |  |  |

|                 | 1 = Pull-up is enabled  |                                                              |                                                       |                                                       |         |         |         |  |  |  |

|                 | 0 = Pull-up is disabled |                                                              |                                                       |                                                       |         |         |         |  |  |  |

<sup>Note 1: The global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.</sup>

#### REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0  | R/W-0/0 | U-0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |

|-------|-----|----------|---------|-----|----------|---------|---------|

| —     | —   | ODA<5:4> |         | —   | ODA<2:0> |         |         |

| bit 7 |     |          |         |     |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

|                      | x = Bit is unknown   | II = II nimplemented bit read as '0'                  |

| u = Bit is unchanged |                      | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

|                      |                      |                                                       |

bit 7-6 Unimplemented: Read as '0'

| bit 5-4 | ODA<5:4>: PORTA Open-Drain Enable bits                                      |

|---------|-----------------------------------------------------------------------------|

|         | For RA<5:4> Pins:                                                           |

|         | 1 = Port pins operate as open-drain drive (sink current only)               |

|         | 0 = Port pins operate as standard push-pull drive (source and sink current) |

| bit 3   | Unimplemented: Read as '0'                                                  |

| bit 2-0 | ODA<2:0>: PORTA Open-Drain Enable bits                                      |

|         | For RA<2:0> Pins:                                                           |

|         | 1 = Port pipe operate as open-drain drive (sink current only)               |

1 = Port pins operate as open-drain drive (sink current only)

0 = Port pins operate as standard push-pull drive (source and sink current)

#### 23.6.8 LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

In Level-Triggered One-Shot mode, the timer count is reset on the external signal level and starts counting on the rising/falling edge of the transition from Reset level to the active level while the ON bit is set. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 01110)

- High Reset level (MODE<4:0> = 01111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control, a new external signal edge is required after the ON bit is set to start the counter.

When Level-Triggered Reset One-Shot mode is used in conjunction with the CCP PWM operation, the PWM drive goes active with the external signal edge that starts the timer. The PWM drive goes inactive when the timer count equals the CCPRx pulse-width count. The PWM drive does not go active when the timer count clears at the PRx period count match.

#### FIGURE 23-11: LOW-LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE TIMING DIAGRAM (MODE<4:0> = 01110)

#### REGISTER 25-2: PWMxDCH: PWMx DUTY CYCLE REGISTER HIGH BITS

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | DC·     | <9:2>          |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable b    | oit     |                |                  |                  |             |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | U = Unimplem   | nented bit, read | l as '0'         |             |

| '1' = Bit is set |         | '0' = Bit is clea | ired    | -n/n = Value a | t POR and BO     | R/Value at all c | ther Resets |

bit 7-0

DC<9:2>: PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in the PWMxDCL register.

#### REGISTER 25-3: PWMxDCL: PWMx DUTY CYCLE REGISTER LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| DC<1    | :0>     | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-6

DC<1:0>: PWM Duty Cycle Least Significant bits

These bits are the LSbs of the PWM duty cycle. The MSbs are found in the PWMxDCH register.

bit 5-0 Unimplemented: Read as '0'

#### TABLE 25-4: SUMMARY OF REGISTERS ASSOCIATED WITH 10-BIT PWM

| Name                 | Bit 7                 | Bit 6       | Bit 5      | Bit 4  | Bit 3      | Bit 2                      | Bit 1      | Bit 0  | Register<br>on Page |

|----------------------|-----------------------|-------------|------------|--------|------------|----------------------------|------------|--------|---------------------|

| CCPTMRS              | P4TSE                 | L<1:0>      | P3TSE      | L<1:0> | C2TSEL     | C2TSEL<1:0>(1) C1TSEL<1:0> |            |        | 264                 |

| PWMxCON              | EN                    | _           | OUT        | POL    | MODE       | <1:0>                      | _          | _      | 265                 |

| PWMxDCH              |                       | DC<9:2>     |            |        |            |                            |            | 266    |                     |

| PWMxDCL              | DC<                   | 1:0>        | _          | _      | —          | _                          | _          | —      | 266                 |

| RxyPPS               | —                     | —           |            |        |            | RxyPPS<4:0>                |            |        |                     |

| TxCON                | ON                    |             | CKPS<2:0>  |        | OUTPS<3:0> |                            |            |        | 244                 |

| TxCLKCON             | —                     | —           | —          | —      | CS<3:0>    |                            |            |        | 243                 |

| TxPR                 | TMRx Peri             | od Register |            |        |            |                            |            |        | 227                 |

| TRISA                | —                     | —           | TRISA      | <5:4>  | (1)        |                            | TRISA<2:0> |        | 136                 |

| TRISB <sup>(2)</sup> |                       | TRIS        | TRISB<7:4> |        |            | —                          | _          | _      | 142                 |

| TRISC                | TRISC7 <sup>(2)</sup> | TRISC6(2)   | TRISC5     | TRISC4 | TRISC3     | TRISC2                     | TRISC1     | TRISC0 | 147                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

**Note 1:** Unimplemented, read as '1'.

2: PIC16(L)F1768/9 only.

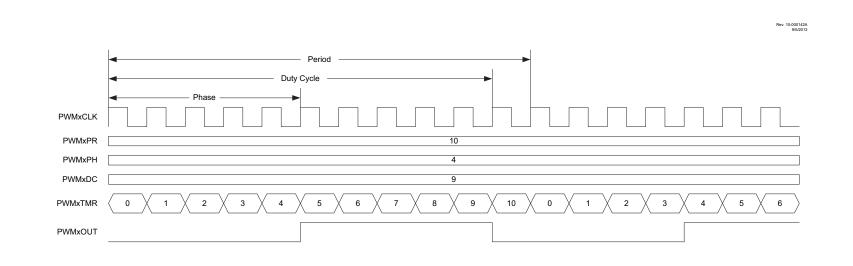

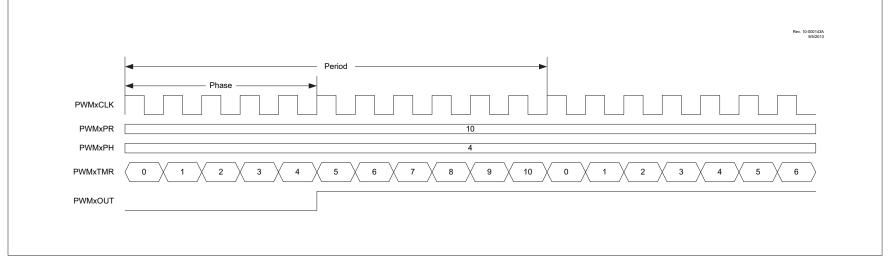

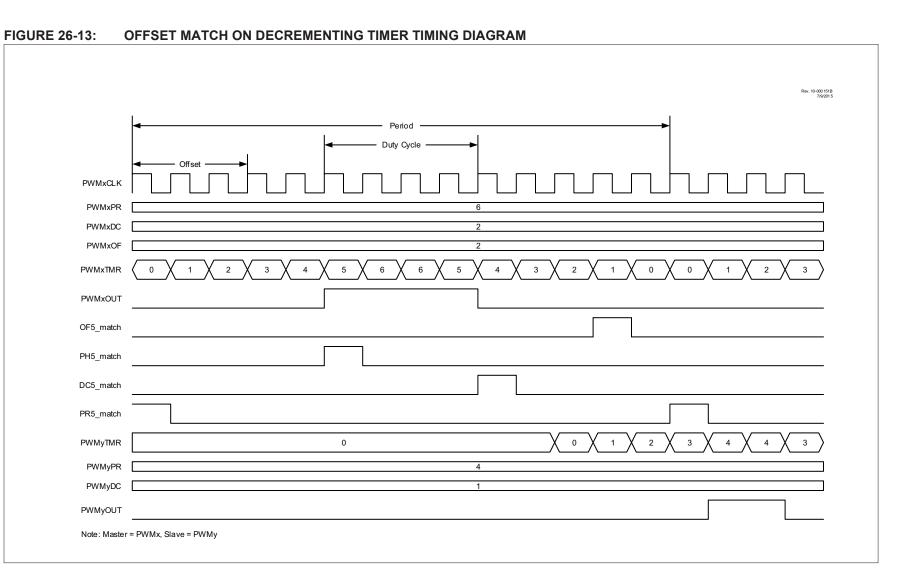

#### FIGURE 26-5: SET ON MATCH PWMx MODE TIMING DIAGRAM

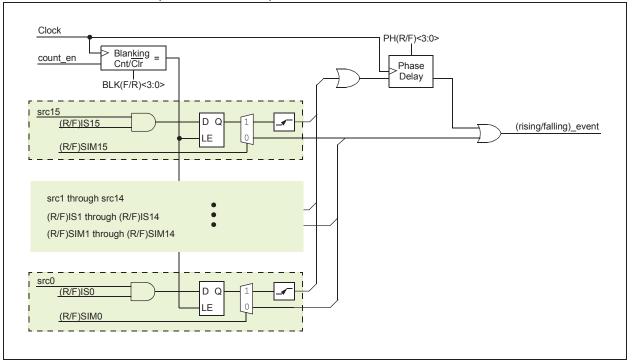

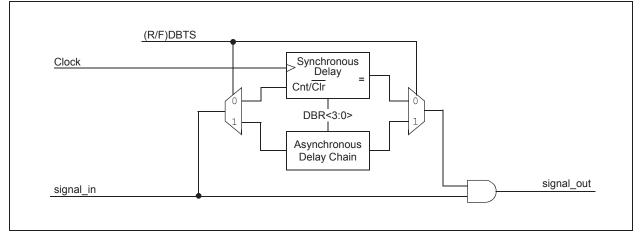

| FIGURE 27-7: | COG | (RISING/FALLING) | INPUT BLOCK | < |

|--------------|-----|------------------|-------------|---|

|              |     |                  | ,           |   |

#### FIGURE 27-8: COG (RISING/FALLING) DEAD-BAND BLOCK

#### REGISTER 29-3: OPAXNCHS: OP AMP x NEGATIVE CHANNEL SOURCE SELECT REGISTER

| U-0          | U-0               | U-0                                                                                                     | U-0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|------------------|-------------|--|--|--|--|

| _            | —                 | —                                                                                                       | _             |                  | NCH              | <3:0>            |             |  |  |  |  |

| bit 7        |                   |                                                                                                         |               |                  |                  |                  | bit 0       |  |  |  |  |

|              |                   |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

| Legend:      |                   |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

| R = Reada    | able bit          | W = Writable                                                                                            | bit           |                  |                  |                  |             |  |  |  |  |

| u = Bit is ι | unchanged         | x = Bit is unkn                                                                                         | iown          | U = Unimplen     | nented bit, read | l as '0'         |             |  |  |  |  |

| '1' = Bit is | set               | '0' = Bit is clea                                                                                       | ared          | -n/n = Value a   | at POR and BO    | R/Value at all c | ther Resets |  |  |  |  |

|              |                   |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

| bit 7-4      | Unimpleme         | nted: Read as '                                                                                         | )'            |                  |                  |                  |             |  |  |  |  |

| bit 3-0      | NCH<3:0>: (       | Op Amp Invertin                                                                                         | g Input Chanr | nel Selection bi | its              |                  |             |  |  |  |  |

|              |                   | erved; do not us                                                                                        | •             |                  |                  |                  |             |  |  |  |  |

|              | •                 | ,                                                                                                       |               |                  |                  |                  |             |  |  |  |  |

|              | •                 |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

|              | •                 |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

|              |                   | erved; do not us                                                                                        |               |                  |                  |                  |             |  |  |  |  |

|              |                   | 001 = Programmable Ramp Generator PRG2_out <sup>(1)</sup><br>000 = Programmable Ramp Generator PRG1_out |               |                  |                  |                  |             |  |  |  |  |

|              |                   |                                                                                                         |               | 'RG1_out         |                  |                  |             |  |  |  |  |

|              |                   | erved. Do not us                                                                                        | e.            |                  |                  |                  |             |  |  |  |  |

|              |                   | 0110 = FVR_Buffer2<br>0101 = DAC4 out <sup>(1)</sup>                                                    |               |                  |                  |                  |             |  |  |  |  |

|              |                   | D100 = DAC3  out                                                                                        |               |                  |                  |                  |             |  |  |  |  |

|              |                   | $0011 = DAC2 \text{ out}^{(1)}$                                                                         |               |                  |                  |                  |             |  |  |  |  |

|              | 0010 = DAC        |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

|              | 0001 <b>= OPA</b> |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

|              | 0000 <b>= OPA</b> |                                                                                                         |               |                  |                  |                  |             |  |  |  |  |

Note 1: PIC16(L)F1768/9 only

#### 32.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte-oriented and shifted out, MSb first. Six SFR registers and two interrupt flags interface the module with the  $PIC^{\mathbb{R}}$  microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 32.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an Acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 32.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of I<sup>2</sup>C communication that have definitions specific to I<sup>2</sup>C. That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips<sup>®</sup> I<sup>2</sup>C specification.

#### 32.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRISx bits.

- Note 1: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA

- input is selected with the SSPDATPPS registers. The SCL input is selected with the SSPCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

#### 32.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

#### TABLE 32-2: I<sup>2</sup>C BUS TERMS

| TADLE 32-2:         |                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                                     |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                                  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                                   |

| Master              | The device that initiates a transfer,<br>generates clock signals and<br>terminates a transfer.                                                                                                                  |

| Slave               | The device addressed by the master.                                                                                                                                                                             |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                               |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                             |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                                          |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                                    |

| Active              | Any time one or more master devices is controlling the bus.                                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                                    |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                                             |

| Write Request       | Slave receives a matching address with $R/\overline{W}$ bit clear and is ready to clock in data.                                                                                                                |

| Read Request        | Master sends an address byte with<br>the $R/\overline{W}$ bit set, indicating that it<br>wishes to clock data out of the<br>slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                                   |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is<br>outputting and expected high<br>state.                                                                                                     |

### 32.8 Register Definitions: MSSP Control

#### REGISTER 32-1: SSP1STAT: MSSP STATUS REGISTER

| R/W-0/0          | R/W-0/0                        | R-0/0                                                                                                                                                                                                    | R-0/0                       | R-0/0             | R-0/0                 | R-0/0            | R-0/0          |  |  |  |  |

|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|-----------------------|------------------|----------------|--|--|--|--|

| SMP              | CKE                            | D/A                                                                                                                                                                                                      | Р                           | S                 | R/W                   | UA               | BF             |  |  |  |  |

| bit 7            |                                |                                                                                                                                                                                                          |                             | •                 | -                     |                  | bit 0          |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

| Legend:          |                                |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

| R = Readable     | e bit                          | W = Writable                                                                                                                                                                                             | e bit                       |                   |                       |                  |                |  |  |  |  |

| u = Bit is unc   | hanged                         | x = Bit is unk                                                                                                                                                                                           | nown                        | U = Unimple       | mented bit, read      | l as '0'         |                |  |  |  |  |

| '1' = Bit is set | t                              | '0' = Bit is cle                                                                                                                                                                                         | eared                       | -n/n = Value      | at POR and BO         | R/Value at all c | other Resets   |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

| bit 7            |                                | ata Input Samp                                                                                                                                                                                           | le bit                      |                   |                       |                  |                |  |  |  |  |

|                  | <u>SPI Master n</u>            |                                                                                                                                                                                                          | and of data as              | have the second   |                       |                  |                |  |  |  |  |

|                  |                                | a sampled at e<br>a sampled at n                                                                                                                                                                         |                             |                   |                       |                  |                |  |  |  |  |

|                  | SPI Slave me                   | -                                                                                                                                                                                                        |                             | o alpar and       |                       |                  |                |  |  |  |  |

|                  |                                | e cleared wher                                                                                                                                                                                           | n SPI is used i             | n Slave mode.     |                       |                  |                |  |  |  |  |

|                  |                                | <u>r or Slave mod</u>                                                                                                                                                                                    |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             |                   | ode (100 kHz and      | d 1 MHz)         |                |  |  |  |  |

| bit 6            |                                | e control is ena                                                                                                                                                                                         | -                           |                   | 400 KHZ)              |                  |                |  |  |  |  |

|                  |                                | ock Edge Sele<br>r or Slave moc                                                                                                                                                                          |                             | ue only)          |                       |                  |                |  |  |  |  |

|                  |                                | occurs on tran                                                                                                                                                                                           |                             | tive to Idle clo  | ck state              |                  |                |  |  |  |  |

|                  | 0 = Transmit                   | occurs on tran                                                                                                                                                                                           | sition from Id              | e to active clo   | ck state              |                  |                |  |  |  |  |

|                  | In I <sup>2</sup> C mode       |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             | s are compliant   | t with SMBus spe      | ecification      |                |  |  |  |  |

| bit 5            | _                              | SMBus specific inputs<br>Idress bit (I <sup>2</sup> C mode only)                                                                                                                                         |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                | that the last byte received or transmitted was data                                                                                                                                                      |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                | that the last b                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

| bit 4            | P: Stop bit (I                 | <b>P:</b> Stop bit (I <sup>2</sup> C mode only; this bit is cleared when the MSSP module is disabled, SSPEN is cleared)                                                                                  |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                | s that a Stop bit has been detected last (this bit is '0' on Reset)                                                                                                                                      |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                | was not detecte                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

| bit 3            |                                | <b>S:</b> Start bit (I <sup>2</sup> C mode only; this bit is cleared when the MSSP module is disabled, SSPEN is cleared 1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset) |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                | was not detecte                                                                                                                                                                                          |                             | lected last (this | s dit is "0" on Res   | set)             |                |  |  |  |  |

| bit 2            |                                | Vrite bit information                                                                                                                                                                                    |                             | te only)          |                       |                  |                |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             |                   | address match.        | This bit is only | valid from the |  |  |  |  |

|                  |                                | ch to the next S                                                                                                                                                                                         |                             |                   |                       |                  |                |  |  |  |  |

|                  | In I <sup>2</sup> C Slave      | mode:                                                                                                                                                                                                    |                             |                   |                       |                  |                |  |  |  |  |

|                  | 1 = Read                       |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

|                  | 0 = Write                      |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

|                  | <u>In I<sup>2</sup>C Maste</u> | <u>r mode:</u><br>t is in progress                                                                                                                                                                       |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                | t is not in progress                                                                                                                                                                                     |                             |                   |                       |                  |                |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             | EN or ACKEN       | I will indicate if th | ne MSSP is in I  | dle mode.      |  |  |  |  |

| bit 1            | UA: Update                     | Address bit (10                                                                                                                                                                                          | )-bit I <sup>2</sup> C mode | only)             |                       |                  |                |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             |                   | in the SSPxADI        | D register       |                |  |  |  |  |

|                  | 0 = Address                    | does not need                                                                                                                                                                                            | to be update                | d .               |                       |                  |                |  |  |  |  |

|                  |                                |                                                                                                                                                                                                          |                             |                   |                       |                  |                |  |  |  |  |

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

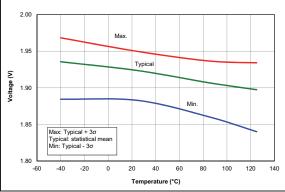

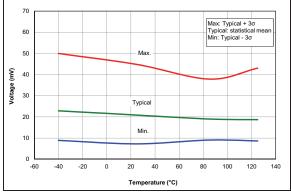

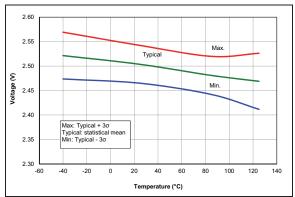

**FIGURE 37-61:** Brown-Out Reset Voltage, Low Trip Point (BORV = 1), PIC16LF1764/5/8/9 Only.

**FIGURE 37-62:** Brown-Out Reset Hysteresis, Low Trip Point (BORV = 1), PIC16LF1764/5/8/9 Only.

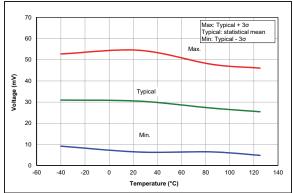

FIGURE 37-63: Brown-Out Reset Voltage, Low Trip Point (BORV = 1), PIC16F1764/5/8/9 Only.

**FIGURE 37-64:** Brown-Out Reset Hysteresis, Low Trip Point (BORV = 1), PIC16F1764/5/8/9 Only.

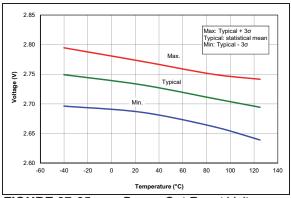

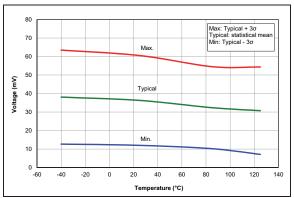

**FIGURE 37-65:** Brown-Out Reset Voltage, High Trip Point (BORV = 0).

**FIGURE 37-66:** Brown-Out Reset Hysteresis, High Trip Point (BORV = 0).

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

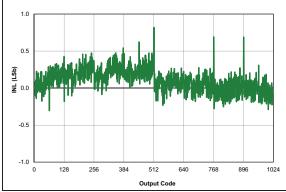

**FIGURE 37-79:** ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

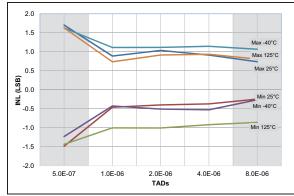

**FIGURE 37-80:** ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

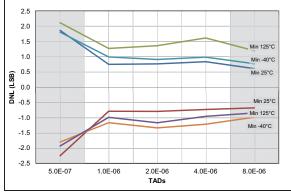

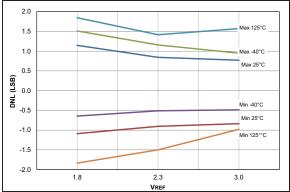

FIGURE 37-81: ADC 10-Bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

FIGURE 37-82: ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

**FIGURE 37-83:** ADC 10-Bit Mode, Single-Ended DNL, VDD = 3.0V, TAD =  $1 \mu$ S.

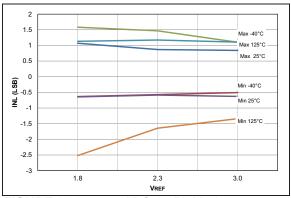

**FIGURE 37-84:** ADC 10-Bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S.