#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

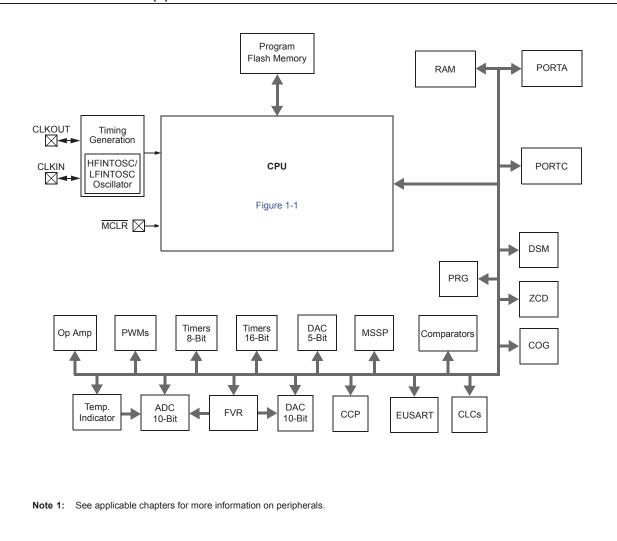

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b; D/A 2x5b, 2x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1768t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4: 20-PIN ALLOCATION TABLE (PIC16(L)F1768/9) (CONTINUED)

| IADL               |                       |            |     |           |     |                                 |                                      |            | 1100101                                      | (00111               |      |                     |       |                       |           |                   |                    |            |          |            |       |

|--------------------|-----------------------|------------|-----|-----------|-----|---------------------------------|--------------------------------------|------------|----------------------------------------------|----------------------|------|---------------------|-------|-----------------------|-----------|-------------------|--------------------|------------|----------|------------|-------|

| 0/1                | 20-Pin PDIP/SOIC/SSOP | 20-Pin QFN | ADC | Reference | DAC | Op Amp                          | Comparator                           | Zero Cross | Programmable<br>Ramp Generator               | Timers               | MWG  | ссь                 | 900   | CLC                   | Modulator | EUSART            | MSSP               | Interrupts | sdn-IInd | Hi Current | Basic |

| RC3                | 7                     | 4          | AN7 | —         | _   | OPA2OUT<br>OPA1IN1-<br>OPA1IN1+ | C1IN3-<br>C2IN3-<br>C3IN3-<br>C4IN3- | _          | PRG2IN0<br>PRG1IN1                           | T5G <sup>(1)</sup>   | _    | CCP2 <sup>(1)</sup> | _     | CLCIN0 <sup>(1)</sup> | _         | _                 | _                  | IOC        | Y        | —          | _     |

| RC4                | 6                     | 3          | —   | —         | —   | —                               | —                                    | —          | PRG1R <sup>(1)</sup><br>PRG2R <sup>(1)</sup> | T3G <sup>(1)</sup>   | _    | —                   | _     | CLCIN1 <sup>(1)</sup> | —         | —                 | _                  | IOC        | Y        | Y          | _     |

| RC5                | 5                     | 2          | —   | -         | _   | _                               | —                                    | _          | PRG1F <sup>(1)</sup><br>PRG2F <sup>(1)</sup> | T3CKI <sup>(1)</sup> | _    | CCP1 <sup>(1)</sup> | _     | —                     | _         | —                 | -                  | IOC        | Y        | Y          | _     |

| RC6                | 8                     | 5          | AN8 | —         | _   | OPA2IN0-                        | —                                    |            | _                                            | —                    | _    | —                   | _     | —                     | —         | _                 | SS <sup>(1)</sup>  | IOC        | Y        | _          | _     |

| RC7                | 9                     | 6          | AN9 | —         | _   | OPA2IN0+                        | —                                    | _          | —                                            | —                    | _    | —                   | _     | —                     | _         | —                 | _                  | IOC        | Υ        | —          | —     |

| Vdd                | 1                     | 18         | —   | —         | —   | _                               | —                                    | —          | —                                            | —                    | —    | —                   | —     | —                     |           | —                 | —                  | —          |          |            |       |

| Vss                | 20                    | 17         | —   | —         | —   | —                               | —                                    | _          | —                                            | —                    | —    | —                   | —     | —                     | _         | —                 | —                  | —          | _        |            |       |

| OUT <sup>(2)</sup> | —                     | —          | —   | —         | _   | _                               | C10UT                                | _          | _                                            | —                    | PWM3 | CCP1                | COG1A | CLC1OUT               | MD10UT    | DT <sup>(3)</sup> | SDO                | —          | —        | —          | —     |

|                    | -                     | —          | -   | _         |     |                                 | C2OUT                                | _          |                                              | —                    | PWM4 | CCP2                | COG1B | CLC2OUT               | MD2OUT    | ТХ                | SDA <sup>(3)</sup> | _          | _        | —          | _     |

|                    | —                     | —          | —   | —         |     | —                               | C3OUT                                | —          | —                                            | —                    | PWM5 | —                   | COG1C | CLC3OUT               | _         | СК                | SCK                | —          | —        | —          | —     |

|                    | -                     | —          | -   | _         |     |                                 | C4OUT                                | _          | _                                            | —                    | PWM6 |                     | COG1D | _                     |           |                   | SCL <sup>(3)</sup> | _          | _        | —          |       |

|                    | —                     | —          | —   | —         | —   | —                               | —                                    | —          | —                                            | —                    | —    | —                   | COG2A | —                     | —         | —                 | _                  | —          | —        | —          | _     |

|                    | -                     | —          | -   | _         | -   | _                               | _                                    | -          | _                                            | _                    | -    | _                   | COG2B | _                     | _         |                   | _                  | _          | _        | —          | _     |

|                    | —                     | —          | _   | —         |     | _                               | —                                    | _          | —                                            | —                    | _    | —                   | COG2C | —                     | —         | —                 |                    | —          | —        | —          | —     |

|                    | —                     | —          | —   | —         | —   | —                               | —                                    | —          | —                                            | —                    | —    | —                   | COG2D | —                     | —         | —                 | —                  | —          | —        | —          | —     |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS Input Selection register. See Table 12-1.

2: All pin outputs default to PORT latch data. Any input capable pin can be selected as a digital peripheral output with the PPS Output Selection registers. See Table 12-2.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Input only.

# PIC16(L)F1764/5/8/9

# PIC16(L)F1764/5/8/9

#### TABLE 3-16: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    |                 |                                            |                                                    |                   |                 | -              |       | - /   |       |                      | _                               |  |

|--------------------|-----------------|--------------------------------------------|----------------------------------------------------|-------------------|-----------------|----------------|-------|-------|-------|----------------------|---------------------------------|--|

| Addr               | Name            | Bit 7                                      | Bit 6                                              | Bit 5             | Bit 4           | Bit 3          | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>Resets |  |

| Banl               | c 31            |                                            |                                                    |                   |                 |                |       |       |       |                      |                                 |  |

| F8Ch<br>to<br>FE3h | _               | Unimpleme                                  | Unimplemented                                      |                   |                 |                |       |       |       |                      |                                 |  |

| FE4h               | STATUS_<br>SHAD | -                                          | —                                                  | —                 | —               | —              | Z     | DC    | С     | xxx                  | uuu                             |  |

| FE5h               | WREG_<br>SHAD   | Working Re                                 | gister Shadow                                      | 1                 |                 |                |       |       |       | XXXX XXXX            | uuuu uuuu                       |  |

| FE6h               | BSR_SHAD        | —                                          | —                                                  | _                 | Bank Select Re  | egister Shadow |       |       |       | x xxxx               | u uuuu                          |  |

| FE7h               | PCLATH_<br>SHAD | Program Counter Latch High Register Shadow |                                                    |                   |                 |                |       |       |       | -xxx xxxx            | -uuu uuuu                       |  |

| FE8h               | FSR0L_<br>SHAD  | Indirect Data                              | a Memory Add                                       | dress 0 Low Point | er Shadow       |                |       |       |       | XXXX XXXX            | uuuu uuuu                       |  |

| FE9h               | FSR0H_<br>SHAD  | Indirect Data                              | a Memory Ado                                       | dress 0 High Poin | ter Shadow      |                |       |       |       | XXXX XXXX            | uuuu uuuu                       |  |

| FEAh               | FSR1L_<br>SHAD  | Indirect Data                              | a Memory Ado                                       | dress 1 Low Point | er Shadow       |                |       |       |       | XXXX XXXX            | uuuu uuuu                       |  |

| FEBh               | FSR1H_<br>SHAD  | Indirect Data                              | Indirect Data Memory Address 1 High Pointer Shadow |                   |                 |                |       |       |       |                      | սսսս սսսս                       |  |

| FECh               | _               | Unimplemented                              |                                                    |                   |                 |                |       |       |       | —                    | —                               |  |

| FEDh               | STKPTR          | _                                          | _                                                  | _                 | Current Stack I | Pointer        |       |       |       | 1 1111               | 1 1111                          |  |

| FEEh               | TOSL            | Top of Stack Low byte                      |                                                    |                   |                 |                |       |       |       |                      | uuuu uuuu                       |  |

| FEFh               | TOSH            | —                                          | Top of Stack                                       | High Byte         |                 |                |       |       |       | -xxx xxxx            | -uuu uuuu                       |  |

**Legend:** x = unknown; u = unchanged; q = value depends on condition; - = unimplemented, read as '0'; r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1768/9 only.

**3:** PIC16(L)F1764/5 only.

4: Unimplemented on PIC16LF1764/5/8/9.

| R/W-0/0          | R/W-0/0                                                                     | R-0/0                                                                              | R-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------|-------------|--|--|--|--|--|

| TMR1GIF          | ADIF                                                                        | RCIF                                                                               | TXIF            | SSP1IF           | CCP1IF           | TMR2IF           | TMR1IF      |  |  |  |  |  |

| bit 7            |                                                                             | ·                                                                                  | •               |                  |                  |                  | bit (       |  |  |  |  |  |

|                  |                                                                             |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

| Legend:          |                                                                             |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

| R = Readable     |                                                                             | W = Writable                                                                       |                 |                  |                  |                  |             |  |  |  |  |  |

| u = Bit is uncha | anged                                                                       | x = Bit is unkr                                                                    |                 | •                | nented bit, read |                  |             |  |  |  |  |  |

| '1' = Bit is set |                                                                             | '0' = Bit is cle                                                                   | ared            | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |  |

| bit 7            | TMR1GIF: Ti                                                                 | imer1 Gate Inte                                                                    | rrunt Elag hit  |                  |                  |                  |             |  |  |  |  |  |

|                  | <b>TMR1GIF:</b> Timer1 Gate Interrupt Flag bit<br>1 = Interrupt is pending  |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  |                                                                             | is not pending                                                                     |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 6            | ADIF: Analog                                                                | g-to-Digital Con                                                                   | verter (ADC)    | Interrupt Flag b | oit              |                  |             |  |  |  |  |  |

|                  | 1 = Interrupt is pending                                                    |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  |                                                                             | is not pending                                                                     |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 5            | RCIF: EUSART Receive Interrupt Flag bit                                     |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  |                                                                             | <ul> <li>1 = Interrupt is pending</li> <li>0 = Interrupt is not pending</li> </ul> |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 4            |                                                                             |                                                                                    | errunt Flag hi  | t                |                  |                  |             |  |  |  |  |  |

|                  | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit<br>1 = Interrupt is pending |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  |                                                                             | 0 = Interrupt is not pending                                                       |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 3            | SSP1IF: Master Synchronous Serial Port (MSSP) Interrupt Flag bit            |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  | 1 = Interrupt is pending                                                    |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  | 0 = Interrupt is not pending                                                |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 2            |                                                                             | P1 Interrupt Fla                                                                   | g bit           |                  |                  |                  |             |  |  |  |  |  |

|                  | 1 = Interrupt is pending<br>0 = Interrupt is not pending                    |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 1            |                                                                             | er2 to T2PR In                                                                     | terrunt Elaa h  | i+               |                  |                  |             |  |  |  |  |  |

| DIC I            |                                                                             |                                                                                    | terrupt riag b  | it.              |                  |                  |             |  |  |  |  |  |

|                  | 1 = Interrupt is pending<br>0 = Interrupt is not pending                    |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

| bit 0            |                                                                             | er1 Overflow Ir                                                                    | iterrupt Flag I | pit              |                  |                  |             |  |  |  |  |  |

|                  | 1 = Interrupt                                                               |                                                                                    |                 |                  |                  |                  |             |  |  |  |  |  |

|                  | 0 = Interrupt                                                               | is not pending                                                                     |                 |                  |                  |                  |             |  |  |  |  |  |

#### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

| REGISTER 10-6: PMCON2 | : PROGRAM MEMORY | CONTROL 2 REGISTER |

|-----------------------|------------------|--------------------|

|-----------------------|------------------|--------------------|

| W-0/0            | W-0/0  | W-0/0             | W-0/0       | W-0/0          | W-0/0            | W-0/0            | W-0/0       |

|------------------|--------|-------------------|-------------|----------------|------------------|------------------|-------------|

|                  |        | Prog              | gram Memory | Control Regist | er 2             |                  |             |

| bit 7            |        |                   |             |                |                  |                  | bit 0       |

|                  |        |                   |             |                |                  |                  |             |

| Legend:          |        |                   |             |                |                  |                  |             |

| R = Readable b   | it     | W = Writable I    | bit         |                |                  |                  |             |

| S = Bit can only | be set | x = Bit is unkn   | iown        | U = Unimpler   | nented bit, read | l as '0'         |             |

| '1' = Bit is set |        | '0' = Bit is clea | ared        | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

#### bit 7-0 Program Memory Control 2: Flash Memory Unlock Pattern bits

To unlock writes, 55h must be written first, followed by AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

**TABLE 10-3**: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7 | Bit 6                             | Bit 5  | Bit 4 | Bit 3   | Bit 2  | Bit 1 | Bit 0 | Register<br>on Page |  |

|--------|-------|-----------------------------------|--------|-------|---------|--------|-------|-------|---------------------|--|

| INTCON | GIE   | PEIE                              | TMR0IE | INTE  | IOCIE   | TMR0IF | INTF  | IOCIF | 101                 |  |

| PMCON1 | (1)   | CFGS                              | LWLO   | FREE  | WRERR   | WREN   | WR    | RD    | 132                 |  |

| PMCON2 |       | Program Memory Control Register 2 |        |       |         |        |       |       |                     |  |

| PMADRL |       |                                   |        | PMAD  | RL<7:0> |        |       |       | 131                 |  |

| PMADRH | (1)   | (1) PMADRH<6:0>                   |        |       |         |        |       |       |                     |  |

| PMDATL |       | PMDATL<7:0>                       |        |       |         |        |       |       |                     |  |

| PMDATH | _     | – PMDATH<5:0>                     |        |       |         |        |       |       |                     |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory. Note 1: Unimplemented, read as '1'.

TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0 | Register<br>on Page |  |

|---------|------|---------|---------|----------|----------|----------|----------|----------|---------|---------------------|--|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREN    | V<1:0>   | _       | 62                  |  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   | F        | OSC<2:0> |         | - 63                |  |

|         | 13:8 | _       | —       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN   | PLLEN   | 65                  |  |

| CONFIG2 | 7:0  | ZCD     |         |          |          | _        | PPS1WAY  | WRT      | <1:0>   |                     |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

#### 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver, capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.1.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, the corresponding port pin drive slews at the maximum rate possible.

#### 11.1.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-On-Change occurs, if that feature is enabled. See Table 36-4 for more information on threshold levels.

| Note: | Changing the input threshold selection       |

|-------|----------------------------------------------|

|       | should be performed while all peripheral     |

|       | modules are disabled. Changing the thresh-   |

|       | old level during the time a module is active |

|       | may inadvertently generate a transition      |

|       | associated with an input pin, regardless of  |

|       | the actual voltage level on that pin.        |

#### 11.1.6 ANALOG CONTROL

The ANSELA register (Register 11-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRISx clear and ANSELx set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing Read-Modify-Write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSELA bits        |

|       | must be initialized to '0' by user software. |

#### EXAMPLE 11-1: INITIALIZING PORTA

| ; initia | ports are in | illustrates<br>ORTA register. The<br>itialized in the same |

|----------|--------------|------------------------------------------------------------|

| BANKSEL  | PORTA        | ;                                                          |

| CLRF     | PORTA        | ;Init PORTA                                                |

| BANKSEL  | LATA         | ;Data Latch                                                |

| CLRF     | LATA         | ;                                                          |

| BANKSEL  | ANSELA       | ;                                                          |

| CLRF     | ANSELA       | ;digital I/O                                               |

| BANKSEL  | TRISA        | ;                                                          |

| MOVLW    | B'00111000'  | ;Set RA<5:3> as inputs                                     |

| MOVWF    | TRISA        | ;and set RA<2:0> as                                        |

|          |              | ;outputs                                                   |

#### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the Peripheral Pin Select (PPS) logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as the ADC and comparator inputs, are not shown in the Peripheral Pin Select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

| REGISTER 11-5: | WPUA: WEAK PULL-UP PORTA REGISTER |  |

|----------------|-----------------------------------|--|

|                |                                   |  |

| U-0                  | U-0         | R/W-1/1             | R/W-1/1                                                             | R/W-1/1                    | R/W-1/1                            | R/W-1/1 | R/W-1/1      |  |  |  |

|----------------------|-------------|---------------------|---------------------------------------------------------------------|----------------------------|------------------------------------|---------|--------------|--|--|--|

| _                    | _           |                     | WPUA<5:0> <sup>(1,2)</sup>                                          |                            |                                    |         |              |  |  |  |

| bit 7                | ·           |                     |                                                                     |                            |                                    |         | bit 0        |  |  |  |

|                      |             |                     |                                                                     |                            |                                    |         |              |  |  |  |

| Legend:              |             |                     |                                                                     |                            |                                    |         |              |  |  |  |

| R = Readable bit     |             | W = Writable        | bit                                                                 |                            |                                    |         |              |  |  |  |

| u = Bit is unchanged |             | x = Bit is unki     | x = Bit is unknown                                                  |                            | U = Unimplemented bit, read as '0' |         |              |  |  |  |

| '1' = Bit is se      | t           | '0' = Bit is cle    | '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other |                            |                                    |         | other Resets |  |  |  |

| h:+ 7 0              |             | unte de De estere ( | 01                                                                  |                            |                                    |         |              |  |  |  |

| bit 7-6              | Unimpieme   | ented: Read as '    | 0                                                                   |                            |                                    |         |              |  |  |  |

| bit 5-0              | WPUA<5:0    | >: Weak Pull-up     | PORTA Regis                                                         | ster bits <sup>(1,2)</sup> |                                    |         |              |  |  |  |

|                      | 1 = Pull-up | is enabled          |                                                                     |                            |                                    |         |              |  |  |  |

|                      | 0 = Pull-up |                     |                                                                     |                            |                                    |         |              |  |  |  |

<sup>Note 1: The global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.</sup>

#### REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0  | R/W-0/0 | U-0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |

|-------|-----|----------|---------|-----|----------|---------|---------|

| —     | —   | ODA<5:4> |         | —   | ODA<2:0> |         |         |

| bit 7 |     |          |         |     |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-6 Unimplemented: Read as '0'

| bit 5-4 | ODA<5:4>: PORTA Open-Drain Enable bits                                      |

|---------|-----------------------------------------------------------------------------|

|         | For RA<5:4> Pins:                                                           |

|         | 1 = Port pins operate as open-drain drive (sink current only)               |

|         | 0 = Port pins operate as standard push-pull drive (source and sink current) |

| bit 3   | Unimplemented: Read as '0'                                                  |

| bit 2-0 | ODA<2:0>: PORTA Open-Drain Enable bits                                      |

|         | For RA<2:0> Pins:                                                           |

|         | 1 = Port pipe operate as open-drain drive (sink current only)               |

1 = Port pins operate as open-drain drive (sink current only)

0 = Port pins operate as standard push-pull drive (source and sink current)

|                                | xxxPPS                      | Default Pir                    | n Selection | Reset Value (xxxPPS<4:0>) |                 |  |  |

|--------------------------------|-----------------------------|--------------------------------|-------------|---------------------------|-----------------|--|--|

| Peripheral                     | Register<br>(Register 12-1) | PIC16(L)F1768/9 PIC16(L)F1764/ |             | PIC16(L)F1768/9           | PIC16(L)F1764/5 |  |  |

| Interrupt-On-Change            | INTPPS                      | RA2                            | RA2         | 00010                     | 00010           |  |  |

| Timer0 Clock                   | TOCKIPPS                    | RA2                            | RA2         | 00010                     | 00010           |  |  |

| Timer1 Clock                   | T1CKIPPS                    | RA5                            | RA5         | 00101                     | 00101           |  |  |

| Timer1 Gate                    | T1GPPS                      | RA4                            | RA4         | 00100                     | 00100           |  |  |

| Timer2 Clock                   | T2INPPS                     | RA5                            | RA5         | 0101                      | 0101            |  |  |

| Timer3 Clock                   | T3CKIPPS                    | RC5                            | RC5         | 10101                     | 10101           |  |  |

| Timer3 Gate                    | T3GPPS                      | RC4                            | RC4         | 10100                     | 10100           |  |  |

| Timer4 Clock                   | T4INPPS                     | RC1                            | RC1         | 10001                     | 10001           |  |  |

| Timer5 Clock                   | T5CKIPPS                    | RC0                            | RC0         | 10000                     | 10000           |  |  |

| Timer5 Gate                    | T5GPPS                      | RC3                            | RC3         | 10011                     | 10011           |  |  |

| Timer6 Clock                   | T6INPPS                     | RA3                            | RA3         | 00011                     | 00011           |  |  |

| CCP1                           | CCP1PPS                     | RC5                            | RC5         | 10101                     | 10101           |  |  |

| CCP2                           | CCP2PPS <sup>(1)</sup>      | RC3                            | _           | 10011                     | _               |  |  |

| COG1                           | COG1INPPS                   | RA2                            | RA2         | 00010                     | 00010           |  |  |

| COG2                           | COG2INPPS <sup>(1)</sup>    | RA2                            | _           | 00010                     | _               |  |  |

| SPI and I <sup>2</sup> C Clock | SSPCLKPPS                   | RB6                            | RC0         | 01110                     | 10000           |  |  |

| SPI and I <sup>2</sup> C Data  | SSPDATPPS                   | RB4                            | RC1         | 01100                     | 10001           |  |  |

| SPI Slave Select               | SSPSSPPS                    | RC6                            | RC3         | 10110                     | 10011           |  |  |

| EUSART RX                      | RXPPS                       | RB5                            | RC5         | 01101                     | 10101           |  |  |

| EUSART CK                      | CKPPS                       | RB7                            | RC4         | 01111                     | 10100           |  |  |

| All CLCs                       | CLCIN0PPS                   | RC3                            | RC3         | 10011                     | 10011           |  |  |

| All CLCs                       | CLCIN1PPS                   | RC4                            | RC4         | 10100                     | 10100           |  |  |

| All CLCs                       | CLCIN2PPS                   | RC1                            | RC1         | 10001                     | 10001           |  |  |

| All CLCs                       | CLCIN3PPS                   | RA5                            | RA5         | 00101                     | 00101           |  |  |

| PRG1 Set Rising                | PRG1RPPS                    | RC4                            | RC4         | 10100                     | 10100           |  |  |

| PRG1 Set Falling               | PRG1FPPS                    | RC5                            | RC5         | 10101                     | 10101           |  |  |

| PRG2 Set Rising                | PRG2RPPS <sup>(1)</sup>     | RC4                            | _           | 10100                     | _               |  |  |

| PRG2 Set Falling               | PRG2FPPS <sup>(1)</sup>     | RC5                            | _           | 10101                     | _               |  |  |

| DSM1 High Carrier              | MD1CHPPS                    | RA3                            | RA3         | 00011                     | 00011           |  |  |

| DSM1 Low Carrier               | MD1CLPPS                    | RA4                            | RA4         | 00100                     | 00100           |  |  |

| DSM1 Modulation                | MD1MODPPS                   | RA5                            | RA5         | 00101                     | 00101           |  |  |

| DSM2 High Carrier              | MD2CHPPS <sup>(1)</sup>     | RA3                            | _           | 00011                     | _               |  |  |

| DSM2 Low Carrier               | MD2CLPPS <sup>(1)</sup>     | RA4                            | _           | 00100                     | _               |  |  |

| DSM2 Modulation                | MD2MODPPS <sup>(1)</sup>    | RA5                            | _           | 00101                     | _               |  |  |

#### TABLE 12-1: PPS INPUT REGISTER RESET VALUES

**Example:** CCP1PPS = 0x13 selects RC3 as the CCP1 input.

**Note 1:** PIC16(L)F1768/9 only.

#### 18.7 Register Definitions: DAC Control

Long bit name prefixes for the 10-bit DAC peripherals are shown in Table 18-2. Refer to **Section 1.1 "Register and Bit Naming Conventions**" for more information.

#### TABLE 18-2: BIT NAME PREFIXES

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| DAC1                | DAC1            |

| DAC2 <sup>(1)</sup> | DAC2            |

Note 1: PIC16(L)F1768/9 devices only.

#### REGISTER 18-1: DACxCON0: DACx CONTROL REGISTER 0

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0  | R/W-0/0 | U-0 | R/W-0/0 |

|---------|---------|---------|-----|----------|---------|-----|---------|

| EN      | FM      | OE1     | —   | PSS<1:0> |         | —   | NSS     |

| bit 7   |         |         |     |          |         |     | bit 0   |

| Legend:          |                           |                                                                             |                                                       |  |  |  |  |

|------------------|---------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable     | bit                       | W = Writable bit                                                            |                                                       |  |  |  |  |

| u = Bit is unch  | anged                     | x = Bit is unknown                                                          | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| '1' = Bit is set |                           | '0' = Bit is cleared                                                        | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

|                  |                           |                                                                             |                                                       |  |  |  |  |

| bit 7            | EN: DACx Er               | hable bit                                                                   |                                                       |  |  |  |  |

|                  | 1 = DACx is               |                                                                             |                                                       |  |  |  |  |

|                  | 0 = DACx is               |                                                                             |                                                       |  |  |  |  |

| bit 6            | FM: DACx Re               | eference Format bit                                                         |                                                       |  |  |  |  |

|                  |                           | ference selection is left justified<br>ference selection is right justified |                                                       |  |  |  |  |

| bit 5            | OE1: DACx \               | /oltage Output Enable bit                                                   |                                                       |  |  |  |  |

|                  |                           | Itage level is also an outpu<br>Itage level is disconnected                 |                                                       |  |  |  |  |

| bit 4            | Unimplemen                | ted: Read as '0'                                                            |                                                       |  |  |  |  |

| bit 3-2          | <b>PSS&lt;1:0&gt;:</b> D  | ACx Positive Source Selec                                                   | t bits                                                |  |  |  |  |

|                  | 11 = Reserv<br>10 = FVR_b | ed; do not use.<br>uffer2                                                   |                                                       |  |  |  |  |

|                  | 01 = VREF+ <br>00 = VDD   | pin                                                                         |                                                       |  |  |  |  |

| bit 1            |                           | ted: Read as '0'                                                            |                                                       |  |  |  |  |

| bit 0            | NSS: DACx N               | Negative Source Select bit                                                  |                                                       |  |  |  |  |

|                  | 1 = VREF- pir             | 1                                                                           |                                                       |  |  |  |  |

|                  | 0 = Vss                   |                                                                             |                                                       |  |  |  |  |

#### 24.4 CCP/PWM Clock Selection

The PIC16(L)F1764/5/8/9 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2/4/6), the PWM mode on the CCP and PWM modules can use any of these timers.

The CCPTMRS register is used to select which timer is used.

## 24.4.1 USING THE TMR2/4/6 WITH THE CCP MODULE

This device has a new version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than older parts. Refer to **Section 23.6 "Operation Examples"** for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the Fosc/4 clock source selected.

#### 24.4.2 PWM PERIOD

The PWM period is specified by the T2PR/T4PR/T6PR register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

#### EQUATION 24-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc.

When TMR2/4/6 is equal to its respective T2PR/T4PR/T6PR register, the following three events occur on the next increment cycle:

- TMR2/4/6 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from the CCPRxH:CCPRxL pair into the internal 10-bit latch.

Note: The Timer postscaler (see Figure 24-1) is not used in the determination of the PWM frequency.

#### 24.4.3 PWM DUTY CYCLE

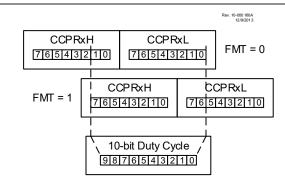

The PWM duty cycle is specified by writing a 10-bit value to two registers: the CCPRxH:CCPRxL register pair. Where the particular bits go is determined by the FMT bit of the CCPxCON register. If FMT = 0, the two Most Significant bits of the duty cycle value should be written to bits<1:0> of the CCPRxH register and the remaining eight bits to the CCPRxL register. If FMT = 1, the Least Significant two bits of the duty cycle should be written to bits<7:6> of the CCPRxL register and the Most Significant eight bits to the CCPRxL register and the Most Significant eight bits to the CCPRxL register. This is illustrated in Figure 24-4. These bits can be written at any time. The duty cycle value is not latched into the internal latch until after the period completes (i.e., a match between T2PR/T4PR/T6PR and TMR2/4/6 registers occurs).

Equation 24-2 is used to calculate the PWM pulse width. Equation 24-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 24-2: PULSE WIDTH

#### EQUATION 24-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL)}{4(PRx+1)}$

The PWM Duty Cycle registers are double-buffered for glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the internal buffer register, then the CCPx pin is cleared (see Figure 24-3).

#### FIGURE 24-4: CCPx DUTY CYCLE ALIGNMENT

| R/W-0/0            | R/W-0/0                                                                                                                         | R/W-0/0                                                                     | R/W-0/0                                                                                               | R/W-0/0                                   | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|----------------|--------------|

| P4TSEL             | _<1:0> <sup>(1)</sup>                                                                                                           | P3TSEL<1:0>                                                                 |                                                                                                       | C2TSE                                     | EL<1:0>          | C1TSEL<1:0>    |              |

| bit 7              |                                                                                                                                 |                                                                             |                                                                                                       |                                           |                  |                | bit 0        |

|                    |                                                                                                                                 |                                                                             |                                                                                                       |                                           |                  |                |              |

| Legend:            |                                                                                                                                 |                                                                             |                                                                                                       |                                           |                  |                |              |

| R = Readable       | bit                                                                                                                             | W = Writable                                                                | bit                                                                                                   |                                           |                  |                |              |

| u = Bit is unch    | anged                                                                                                                           | x = Bit is unkr                                                             | nown                                                                                                  | U = Unimpler                              | nented bit, read | d as '0'       |              |

| '1' = Bit is set   |                                                                                                                                 | '0' = Bit is clea                                                           | ared                                                                                                  | -n/n = Value a                            | at POR and BO    | R/Value at all | other Resets |

| bit 7-6<br>bit 5-4 | 11 = Reserve<br>10 = PWM4 i<br>01 = PWM4 i<br>00 = PWM4 i<br><b>P3TSEL&lt;1:0</b><br>11 = Reserve<br>10 = PWM3 i<br>01 = PWM3 i | s based off Tim<br>s based off Tim<br>s based off Tim<br>>: PWM3 Time       | ner6 in PWM r<br>ner4 in PWM r<br>ner2 in PWM r<br>er Selection bit<br>ner6 in PWM r<br>ner4 in PWM r | node<br>node<br>node<br>s<br>node<br>node |                  |                |              |

| bit 3-2            | 11 = Reserve<br>10 = CCP2 is<br>01 = CCP2 is                                                                                    | >: CCP2 (PWN<br>ed<br>s based off Tim<br>s based off Tim<br>s based off Tim | er6 in PWM m<br>er4 in PWM m                                                                          | ode                                       |                  |                |              |

| bit 1-0            | 11 = Reserve<br>10 = CCP1 is<br>01 = CCP1 is                                                                                    | >: CCP1 (PWN<br>ed<br>s based off Tim<br>s based off Tim<br>s based off Tim | er6 in PWM m<br>er4 in PWM m                                                                          | ode                                       |                  |                |              |

#### REGISTER 24-2: CCPTMRS: PWM TIMER SELECTION CONTROL REGISTER

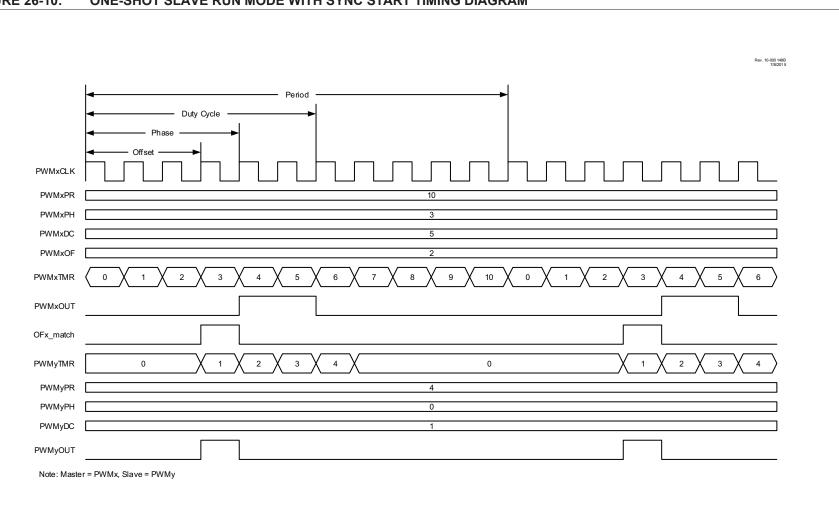

#### FIGURE 26-10: ONE-SHOT SLAVE RUN MODE WITH SYNC START TIMING DIAGRAM

PIC16(L)F1764/5/8/9

| U-0                                                    | U-0          | U-0                            | U-0                    | R/W/HS-0/0          | R/W/HS-0/0          | R/W/HS-0/0          | R/W/HS-0/0          |

|--------------------------------------------------------|--------------|--------------------------------|------------------------|---------------------|---------------------|---------------------|---------------------|

| _                                                      | _            | _                              | _                      | OFIF <sup>(1)</sup> | PHIF <sup>(1)</sup> | DCIF <sup>(1)</sup> | PRIF <sup>(1)</sup> |

| bit 7                                                  |              |                                |                        |                     |                     | •                   | bit 0               |

|                                                        |              |                                |                        |                     |                     |                     |                     |

| Legend:                                                |              |                                |                        |                     |                     |                     |                     |

| R = Reada                                              | ble bit      | W = Writable                   | bit                    | HS = Hardwa         | re Settable bit     |                     |                     |

| u = Bit is unchanged x = Bit is unknown U = Unimplemen |              |                                |                        | nented bit, read    | l as '0'            |                     |                     |

| '1' = Bit is s                                         | set          | '0' = Bit is clea              | ared                   | -n/n = Value a      | t POR and BO        | R/Value at all c    | other Resets        |

|                                                        |              |                                |                        |                     |                     |                     |                     |

| bit 7-4                                                | Unimplemen   | ited: Read as '                | )'                     |                     |                     |                     |                     |

| bit 3                                                  | OFIF: Offset | Interrupt Flag b               | it <sup>(1)</sup>      |                     |                     |                     |                     |

|                                                        |              | atch event occu                |                        |                     |                     |                     |                     |

|                                                        |              | atch event did r               |                        |                     |                     |                     |                     |

| bit 2                                                  | PHIF: Phase  | Interrupt Flag b               | oit <sup>(1)</sup>     |                     |                     |                     |                     |

|                                                        | ±            | 1 = Phase match event occurred |                        |                     |                     |                     |                     |

|                                                        | 0 = Phase m  | atch event did                 | not occur              |                     |                     |                     |                     |

| bit 1                                                  | DCIF: Duty C | ycle Interrupt F               | lag bit <sup>(1)</sup> |                     |                     |                     |                     |

|                                                        |              | le match event                 |                        |                     |                     |                     |                     |

|                                                        |              | le match event                 |                        |                     |                     |                     |                     |

| bit 0                                                  | PRIF: Period | Interrupt Flag b               | oit <sup>(1)</sup>     |                     |                     |                     |                     |

|                                                        | 1 = Period m | atch event occ                 | urred                  |                     |                     |                     |                     |

|                                                        | 0 = Period m | natch event did                | not occur              |                     |                     |                     |                     |

|                                                        |              |                                |                        |                     |                     |                     |                     |

#### REGISTER 26-3: PWMxINTF: PWMx INTERRUPT REQUEST REGISTER

Note 1: Bit is forced clear by hardware while module is disabled (EN = 0).

# PIC16(L)F1764/5/8/9

| FIGURE 27-12: | FULL-BRIDGE FORWARD MODE COG OPERATION WITH CCP1 |

|---------------|--------------------------------------------------|

| CCP1          |                                                  |

| COGxA         |                                                  |

| COGxB         |                                                  |

| COGxC         |                                                  |

| COGxD         |                                                  |

#### FIGURE 27-13: FULL-BRIDGE MODE COG OPERATION WITH CCP1 AND DIRECTION CHANGE

| CCP1  |  |          |                   |        |  |

|-------|--|----------|-------------------|--------|--|

| COGxA |  |          |                   |        |  |

| COGxB |  | →   ← Fa | alling Event Dead | I-Band |  |

| COGxC |  |          |                   |        |  |

| COGxD |  |          |                   |        |  |

| MD0   |  |          |                   |        |  |

#### 27.5.2 RISING EVENT

The rising event starts the PWM output active duty cycle period. The rising event is the low-to-high transition of the rising\_event output. When the rising event phase delay and dead-band time values are zero, the primary output starts immediately. Otherwise, the primary output is delayed. The rising event source causes all the following actions:

- Start rising event phase delay counter (if enabled)

- Clear complementary output after phase delay

- Start falling event input blanking (if enabled)

- Start dead-band delay (if enabled)

- · Set primary output after dead-band delay expires

#### 27.5.3 FALLING EVENT

The falling event terminates the PWM output active duty cycle period. The falling event is the high-to-low transition of the falling\_event output. When the falling event phase delay and dead-band time values are zero, the complementary output starts immediately. Otherwise, the complementary output is delayed. The falling event source causes all the following actions:

- Start falling event phase delay counter (if enabled)

- Clear primary output

- Start rising event input blanking (if enabled)

- Start falling event dead-band delay (if enabled)

- Set complementary output after dead-band delay expires

#### 27.6 Output Control

Upon disabling, or immediately after enabling the COG module, the primary COG outputs are inactive and complementary COG outputs are active.

#### 27.6.1 OUTPUT ENABLES

There are no output enable controls in the COG module. Instead, each device pin has an individual output selection control called the PPS register. All four COG outputs are available for selection in the PPS register of every pin.

When a COG output is enabled by PPS selection, the output on the pin has several possibilities which depend on the mode, steering control, EN bit and shutdown state, as shown in Table 27-1 and Table 27-2.

#### TABLE 27-1: PIN OUTPUT STATES MD<2:0> = 00x

| EN Bit | STR Bit | Shutdown | Output               |

|--------|---------|----------|----------------------|

| Х      | 0       | Inactive | Static Steering Data |

| х      | 1       | Active   | Shutdown Override    |

| 0      | 1       | Inactive | Inactive State       |

| 1      | 1       | Inactive | Active PWM Signal    |

## TABLE 27-2: PIN OUTPUT STATES MD<2:0>> 001

| EN Bit | STR Bit | Shutdown | Output            |

|--------|---------|----------|-------------------|

| x      | x       | Inactive | Inactive State    |

| x      | Х       | Active   | Shutdown Override |

| 1      | Х       | Inactive | Active PWM Signal |

#### 27.6.2 POLARITY CONTROL

The polarity of each COG output can be selected independently. When the output polarity bit is set, the corresponding output is active-low. Clearing the output polarity bit configures the corresponding output as active-high. However, polarity affects the outputs in only one of the four Shutdown Override modes. See **Section 27.10 "Auto-Shutdown Control**" for more details.

Output polarity is selected with the POLA through POLD bits of the COGxCON1 register (Register 27-2).

#### 27.7 Dead-Band Control

The dead-band control provides for non-overlapping PWM output signals to prevent shoot-through current in the external power switches. Dead-band time affects the output only in the Half-Bridge mode and when changing direction in the Full-Bridge mode.

The COG contains two dead-band timers. One dead-band timer is used for rising event dead-band control. The other is used for falling event dead-band control. Timer modes are selectable as either:

- · Asynchronous delay chain

- Synchronous counter

The Dead-Band Timer mode is selected for the rising event and falling event dead-band times, with the respective RDBS and FDBS bits of the COGxCON1 register (Register 27-2).

In Half-Bridge mode, the rising event dead-band time delays all selected primary outputs from going active for the selected dead-band time after the rising event. COGxA and COGxC are the primary outputs in Half-Bridge mode.

In Half-Bridge mode, the falling event dead-band time delays all selected complementary outputs from going active for the selected dead-band time after the falling event. COGxB and COGxD are the complementary outputs in Half-Bridge mode.

In Full-Bridge mode, the dead-band delay occurs only during direction changes. The modulated output is delayed for the falling event dead-band time after a direction change from forward to reverse. The modulated output is delayed for the rising event dead-band time after a direction change from reverse to forward.

| Bit 7 | Bit 6                | Bit 5 | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                       | Register<br>on Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |