#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 2x5b, 2x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1769-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: 20-PIN ALLOCATION TABLE (PIC16(L)F1768/9) (CONTINUED)

| IADL               |                       |            |     |           |     |                                 |                                      |            | 1100101                                      | (00111               |      |                     |       |                       |           |                   |                    |            |          |            |       |

|--------------------|-----------------------|------------|-----|-----------|-----|---------------------------------|--------------------------------------|------------|----------------------------------------------|----------------------|------|---------------------|-------|-----------------------|-----------|-------------------|--------------------|------------|----------|------------|-------|

| 0/1                | 20-Pin PDIP/SOIC/SSOP | 20-Pin QFN | ADC | Reference | DAC | Op Amp                          | Comparator                           | Zero Cross | Programmable<br>Ramp Generator               | Timers               | MWG  | ссь                 | 900   | CLC                   | Modulator | EUSART            | MSSP               | Interrupts | sdn-IInd | Hi Current | Basic |

| RC3                | 7                     | 4          | AN7 | —         | _   | OPA2OUT<br>OPA1IN1-<br>OPA1IN1+ | C1IN3-<br>C2IN3-<br>C3IN3-<br>C4IN3- | _          | PRG2IN0<br>PRG1IN1                           | T5G <sup>(1)</sup>   | _    | CCP2 <sup>(1)</sup> | _     | CLCIN0 <sup>(1)</sup> | _         | _                 | _                  | IOC        | Y        | —          | _     |

| RC4                | 6                     | 3          | —   | —         | —   | _                               | —                                    | —          | PRG1R <sup>(1)</sup><br>PRG2R <sup>(1)</sup> | T3G <sup>(1)</sup>   | _    | —                   | _     | CLCIN1 <sup>(1)</sup> | —         | —                 | _                  | IOC        | Y        | Y          | _     |

| RC5                | 5                     | 2          | —   | -         | _   | _                               | —                                    | _          | PRG1F <sup>(1)</sup><br>PRG2F <sup>(1)</sup> | T3CKI <sup>(1)</sup> | _    | CCP1 <sup>(1)</sup> | _     | —                     | _         | —                 | -                  | IOC        | Y        | Y          | _     |

| RC6                | 8                     | 5          | AN8 | —         | _   | OPA2IN0-                        | —                                    |            | _                                            | —                    | _    | —                   | _     | —                     | —         | _                 | SS <sup>(1)</sup>  | IOC        | Y        | _          | _     |

| RC7                | 9                     | 6          | AN9 | —         | _   | OPA2IN0+                        | —                                    | _          | —                                            | —                    | _    | —                   | _     | —                     | _         | —                 | _                  | IOC        | Υ        | —          | —     |

| Vdd                | 1                     | 18         | —   | —         | —   | _                               | —                                    | —          | —                                            | —                    | —    | —                   | —     | —                     |           | —                 | —                  | —          |          |            |       |

| Vss                | 20                    | 17         | —   | —         | —   | —                               | —                                    | _          | —                                            | —                    | —    | —                   | —     | —                     | _         | —                 | —                  | —          | _        |            |       |

| OUT <sup>(2)</sup> | —                     | —          | —   | —         | _   | _                               | C10UT                                | _          | _                                            | —                    | PWM3 | CCP1                | COG1A | CLC1OUT               | MD10UT    | DT <sup>(3)</sup> | SDO                | —          | —        | —          | _     |

|                    | -                     | —          | -   | _         |     |                                 | C2OUT                                | _          |                                              | —                    | PWM4 | CCP2                | COG1B | CLC2OUT               | MD2OUT    | ТХ                | SDA <sup>(3)</sup> | _          | _        | —          | _     |

|                    | —                     | —          | —   | —         |     | —                               | C3OUT                                | —          | —                                            | —                    | PWM5 | —                   | COG1C | CLC3OUT               | _         | СК                | SCK                | —          | —        | —          | —     |

|                    | -                     | —          | -   | _         |     |                                 | C4OUT                                | _          | _                                            | —                    | PWM6 |                     | COG1D | _                     |           |                   | SCL <sup>(3)</sup> | _          | _        | —          |       |

|                    | —                     | —          | —   | —         | —   | —                               | —                                    | —          | —                                            | —                    | —    | —                   | COG2A | —                     | —         | —                 | _                  | —          | —        | —          | _     |

|                    | -                     | —          | -   | —         | -   | _                               | _                                    | -          | _                                            | _                    | -    | _                   | COG2B | _                     | _         |                   | _                  | _          | _        | —          | _     |

|                    | —                     | —          | _   | —         |     | _                               | —                                    | _          | —                                            | —                    | _    | —                   | COG2C | —                     | —         | —                 |                    | —          | —        | —          | —     |

|                    | —                     | —          | —   | —         | —   | —                               | —                                    | —          | —                                            | —                    | —    | —                   | COG2D | —                     | —         | —                 | —                  | —          | —        | —          | —     |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS Input Selection register. See Table 12-1.

2: All pin outputs default to PORT latch data. Any input capable pin can be selected as a digital peripheral output with the PPS Output Selection registers. See Table 12-2.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Input only.

#### 3.6.2 LINEAR DATA MEMORY

The linear data memory is the region from FSRn address, 0x2000, to FSRn address, 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSRn beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

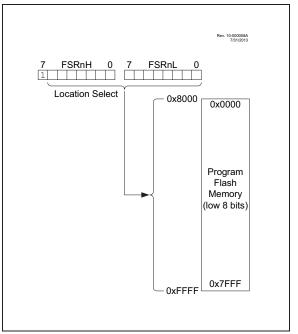

## 3.6.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire Program Flash Memory is mapped to the upper half of the FSRn address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDFn. Only the lower eight bits of each memory location are accessible via INDFn. Writing to the Program Flash Memory cannot be accomplished via the FSRn/INDFn interface. All instructions that access Program Flash Memory via the FSRn/INDFn interface will require one additional instruction cycle to complete.

FIGURE 3-11: PROGRAM FLASH MEMORY MAP

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4         | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|---------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     | _             | _     | _     |       | BORRDY | 90                  |

| PCON   | STKOVF | STKUNF | _     | RWDT          | RMCLR | RI    | POR   | BOR    | 94                  |

| STATUS | _      |        | _     | TO            | PD    | Z     | DC    | С      | 27                  |

| WDTCON | _      | _      |       | WDTPS<4:0> SV |       |       |       |        | 115                 |

TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0          | R/W-0/0       | R-0/0                     | R-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------------|---------------------------|-----------------|------------------|------------------|------------------|-------------|

| TMR1GIF          | ADIF          | RCIF                      | TXIF            | SSP1IF           | CCP1IF           | TMR2IF           | TMR1IF      |

| bit 7            |               | ·                         | •               |                  |                  |                  | bit (       |

|                  |               |                           |                 |                  |                  |                  |             |

| Legend:          |               |                           |                 |                  |                  |                  |             |

| R = Readable     |               | W = Writable              |                 |                  |                  |                  |             |

| u = Bit is uncha | anged         | x = Bit is unkr           |                 | •                | nented bit, read |                  |             |

| '1' = Bit is set |               | '0' = Bit is cle          | ared            | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets |

| bit 7            | TMR1GIF: Ti   | imer1 Gate Inte           | rrunt Elag hit  |                  |                  |                  |             |

|                  | 1 = Interrupt |                           | in aper lag bit |                  |                  |                  |             |

|                  |               | is not pending            |                 |                  |                  |                  |             |

| bit 6            | ADIF: Analog  | g-to-Digital Con          | verter (ADC)    | Interrupt Flag b | oit              |                  |             |

|                  | 1 = Interrupt |                           |                 |                  |                  |                  |             |

|                  |               | is not pending            |                 |                  |                  |                  |             |

| bit 5            |               | RT Receive Inte           | errupt Flag bi  | t                |                  |                  |             |

|                  | 1 = Interrupt | is pending is not pending |                 |                  |                  |                  |             |

| bit 4            |               | RT Transmit Int           | errunt Flag hi  | t                |                  |                  |             |

|                  | 1 = Interrupt |                           | chupt hag bi    | L .              |                  |                  |             |

|                  |               | is not pending            |                 |                  |                  |                  |             |

| bit 3            | SSP1IF: Mas   | ster Synchrono            | us Serial Port  | (MSSP) Interru   | upt Flag bit     |                  |             |

|                  | 1 = Interrupt |                           |                 |                  |                  |                  |             |

|                  |               | is not pending            |                 |                  |                  |                  |             |

| bit 2            |               | P1 Interrupt Fla          | g bit           |                  |                  |                  |             |

|                  | 1 = Interrupt | is pending is not pending |                 |                  |                  |                  |             |

| bit 1            |               | er2 to T2PR In            | terrunt Elaa h  | i+               |                  |                  |             |

| DICT             | 1 = Interrupt |                           | terrupt riag b  | it.              |                  |                  |             |

|                  |               | is not pending            |                 |                  |                  |                  |             |

| bit 0            |               | er1 Overflow Ir           | iterrupt Flag I | pit              |                  |                  |             |

|                  | 1 = Interrupt |                           |                 |                  |                  |                  |             |

|                  | 0 = Interrupt | is not pending            |                 |                  |                  |                  |             |

### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways: by code protection (CP bit in the Configuration Words) and write protection (WRT<1:0> bits in the Configuration Words).

Code protection  $\overline{(CP = 0)}$  disables access, reading and writing to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a bulk erase to the device, clearing all Flash program memory, Configuration bits and User IDs.<sup>(1)</sup>

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the WRT<1:0> bits. Write protection does not affect a device programmer's ability to read, write or erase the device.

## 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

## 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

See Table 10-1 for erase row size and the number of write latches for Flash program memory.

**Note:** If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

#### 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver, capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.1.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, the corresponding port pin drive slews at the maximum rate possible.

#### 11.1.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-On-Change occurs, if that feature is enabled. See Table 36-4 for more information on threshold levels.

| Note: | Changing the input threshold selection       |

|-------|----------------------------------------------|

|       | should be performed while all peripheral     |

|       | modules are disabled. Changing the thresh-   |

|       | old level during the time a module is active |

|       | may inadvertently generate a transition      |

|       | associated with an input pin, regardless of  |

|       | the actual voltage level on that pin.        |

#### 11.1.6 ANALOG CONTROL

The ANSELA register (Register 11-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRISx clear and ANSELx set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing Read-Modify-Write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSELA bits        |

|       | must be initialized to '0' by user software. |

#### EXAMPLE 11-1: INITIALIZING PORTA

| ; initia<br>; other | <pre>; This code example illustrates<br/>; initializing the PORTA register. The<br/>; other ports are initialized in the same<br/>; manner.</pre> |                        |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|--|

| BANKSEL             | PORTA                                                                                                                                             | ;                      |  |  |  |  |  |  |  |

| CLRF                | PORTA                                                                                                                                             | ;Init PORTA            |  |  |  |  |  |  |  |

| BANKSEL             | LATA                                                                                                                                              | ;Data Latch            |  |  |  |  |  |  |  |

| CLRF                | LATA                                                                                                                                              | ;                      |  |  |  |  |  |  |  |

| BANKSEL             | ANSELA                                                                                                                                            | ;                      |  |  |  |  |  |  |  |

| CLRF                | ANSELA                                                                                                                                            | ;digital I/O           |  |  |  |  |  |  |  |

| BANKSEL             | TRISA                                                                                                                                             | ;                      |  |  |  |  |  |  |  |

| MOVLW               | B'00111000'                                                                                                                                       | ;Set RA<5:3> as inputs |  |  |  |  |  |  |  |

| MOVWF               | TRISA                                                                                                                                             | ;and set RA<2:0> as    |  |  |  |  |  |  |  |

|                     |                                                                                                                                                   | ;outputs               |  |  |  |  |  |  |  |

#### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the Peripheral Pin Select (PPS) logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as the ADC and comparator inputs, are not shown in the Peripheral Pin Select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |  |

|-------|-----|------------|------------|------------|------------|------------|------------|--|

| —     | —   |            | IOCAF<5:0> |            |            |            |            |  |

| bit 7 |     |            |            |            |            |            | bit 0      |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware Settable bit                            |

| bit 7-6 | Unimplemented: Read as '0'                               |

|---------|----------------------------------------------------------|

| bit 5-0 | IOCAF<5:0>: Interrupt-On-Change PORTA Flag bits          |

|         | 1 = An enabled change was detected on the associated nin |

L = An enabled change was detected on the associated pin Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected or the user cleared the detected change

## REGISTER 13-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER<sup>(1)</sup>

| R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|--------------------|---------|---------|-----|-----|-----|-------|

|         | IOCBP <sup>.</sup> | <7:4>   |         | —   | —   | —   | —     |

| bit 7   |                    |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-4 **IOCBP<7:4>:** Interrupt-On-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-On-Change is enabled on the pin for a positive going edge; IOCBFx bit and IOCIF flag will be set upon edge detection

- 0 = Interrupt-On-Change is disabled for the associated pin

bit 3-0 Unimplemented: Read as '0'

Note 1: PIC16(L)F1768/9 only.

## **15.3** Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 16.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

#### 15.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu s$  after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu s$  between sequential conversions of the temperature indicator output.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFV  | R<1:0> | ADFV  | R<1:0> | 169                 |

Legend: Shaded cells are unused by the temperature indicator module.

#### REGISTER 16-3: ADCON2: ADC CONTROL REGISTER 2

| R/W-0/0          | R/W-0/0                                                                                                | R/W-0/0                       | R/W-0/0                | R/W-0/0                       | U-0              | U-0              | U-0          |  |  |

|------------------|--------------------------------------------------------------------------------------------------------|-------------------------------|------------------------|-------------------------------|------------------|------------------|--------------|--|--|

|                  | ٦                                                                                                      | rrigsel<4:0> <sup>(1</sup>    | 1)                     |                               |                  | —                | —            |  |  |

| bit 7            |                                                                                                        |                               |                        |                               |                  |                  | bit (        |  |  |

|                  |                                                                                                        |                               |                        |                               |                  |                  |              |  |  |

| Legend:          |                                                                                                        |                               |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | W = Writable                  | W = Writable bit       |                               | nented bit, read | d as '0'         |              |  |  |

|                  |                                                                                                        | x = Bit is unkr               | nown                   | -n/n = Value a                | t POR and BO     | R/Value at all o | other Resets |  |  |

| '1' = Bit is set | t                                                                                                      | '0' = Bit is clea             | ared                   |                               |                  |                  |              |  |  |

|                  |                                                                                                        |                               |                        | o                             | N N              |                  |              |  |  |

| bit 7-3          |                                                                                                        |                               | ersion Trigger         | Selection bits <sup>(1)</sup> | ,                |                  |              |  |  |

|                  | 11111 = Re                                                                                             | served                        |                        |                               |                  |                  |              |  |  |

|                  | •                                                                                                      |                               |                        |                               |                  |                  |              |  |  |

|                  | •                                                                                                      |                               |                        |                               |                  |                  |              |  |  |

|                  | 11011 <b>= Re</b>                                                                                      | served                        |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM6 – OF6_mat                 |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM6 – PH6_mat                 |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM6 – PR6_mat                 |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM6 – DC6_mat                 |                        |                               |                  |                  |              |  |  |

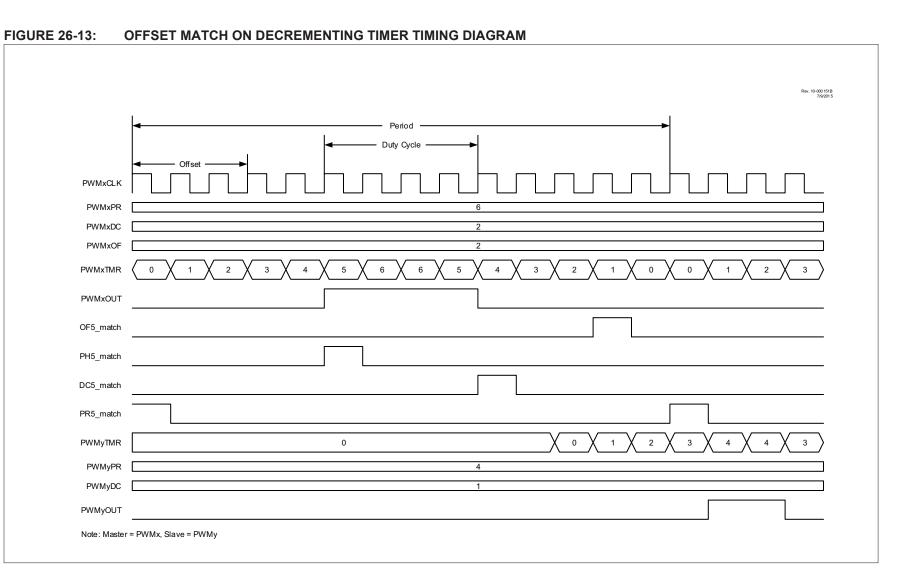

|                  |                                                                                                        | VM5 – OF5_mat                 |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM5 – PH5_mat                 |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM5 – PR5_mat                 |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM5 – DC5_mat<br>VM4 – PWM4OL | (0)                    |                               |                  |                  |              |  |  |

|                  |                                                                                                        | VM3 – PWM3OU                  |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | P2 - CCP2 trig                |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | $P1 - CCP1_trig$              |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | C3 – LC3 out                  | 901                    |                               |                  |                  |              |  |  |

|                  |                                                                                                        | C2 - LC2 out                  |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | C1 - LC1 out                  |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        |                               | vnc C4OUT <sup>(</sup> | 2)                            |                  |                  |              |  |  |

|                  | 01011 = Comparator C4 – sync_C4OUT <sup>(2)</sup><br>01010 = Comparator C3 – sync_C3OUT <sup>(2)</sup> |                               |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | mparator C2 – s               |                        |                               |                  |                  |              |  |  |

|                  | 01000 <b>= Co</b>                                                                                      | mparator C1 - s               | ync_C1OUT              |                               |                  |                  |              |  |  |

|                  | 00111 <b>= Tin</b>                                                                                     | ner6 – T6_posts               | caled                  |                               |                  |                  |              |  |  |

|                  |                                                                                                        | ner5 – T5_overfl              |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | ner4 – T4_posts               |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | ner3 – T3_overfl              |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | ner2 – T2_posts               |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | ner1 – T1_overfl              |                        |                               |                  |                  |              |  |  |

|                  |                                                                                                        | ner0 – T0_overfl              |                        |                               |                  |                  |              |  |  |

|                  | 00000 <b>= No</b>                                                                                      | auto-conversion               | n trigger selec        | ted                           |                  |                  |              |  |  |

| bit 3-0          | Unimplomo                                                                                              | nted: Read as '               | ∩'                     |                               |                  |                  |              |  |  |

- bit 3-0 Unimplemented: Read as '0'

- Note 1: This is a rising edge-sensitive input for all sources.

- 2: PIC16(L)F1768/9 only; reserved otherwise.

# PIC16(L)F1764/5/8/9

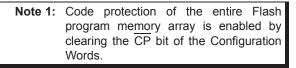

#### FIGURE 16-4: ANALOG INPUT MODEL

## 24.5 Register Definitions: CCP Control

## REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

|                  | U-0                                                                            | R-x              | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0         | R/W-0/0       |

|------------------|--------------------------------------------------------------------------------|------------------|-------------------|------------------|------------------|-----------------|---------------|

| EN               | —                                                                              | OUT              | FMT               |                  | MODE             | =<3:0>          |               |

| bit 7            |                                                                                |                  |                   |                  |                  |                 | bit 0         |

|                  |                                                                                |                  |                   |                  |                  |                 |               |

| Legend:          |                                                                                |                  |                   |                  |                  |                 |               |

| R = Readable     | bit                                                                            | W = Writable     | bit               |                  |                  |                 |               |

| u = Bit is uncha | anged                                                                          | x = Bit is unkr  | nown              |                  | nented bit, read |                 |               |

| '1' = Bit is set |                                                                                | '0' = Bit is cle | ared              | -n/n = Value a   | at POR and BO    | R/Value at all  | other Reset   |

|                  |                                                                                |                  |                   |                  |                  |                 |               |

| bit 7            |                                                                                | odule Enable b   | it                |                  |                  |                 |               |

|                  | 1 = CCPx is $0 = CCPx$ is                                                      |                  |                   |                  |                  |                 |               |

| bit 6            |                                                                                | ited: Read as '  | ٥'                |                  |                  |                 |               |

| bit 5            | -                                                                              |                  |                   |                  |                  |                 |               |

| bit 4            | OUT: CCPx Output Data bit (read-only)<br>FMT: CCPW (Pulse-Width) Alignment bit |                  |                   |                  |                  |                 |               |

| DIL 4            |                                                                                | > = PWM Mode     | •                 |                  |                  |                 |               |

|                  |                                                                                |                  |                   | e MSB of the F   | WM duty cycle    | 9               |               |

|                  | 0                                                                              |                  |                   | the LSB of the I |                  |                 |               |

| bit 3-0          | MODE<3:0>:                                                                     | CCPx Mode S      | Selection bits    |                  |                  |                 |               |

|                  | 11xx = PWN                                                                     | 1 mode           |                   |                  |                  |                 |               |

|                  | 1011 = Com                                                                     | pare mode: Pu    | lse output cle    | ar TMR1          |                  |                 |               |

|                  |                                                                                | pare mode: Pu    |                   |                  |                  |                 |               |

|                  |                                                                                |                  |                   | compare match    |                  |                 |               |

|                  | 1000 <b>= Com</b>                                                              | pare mode: Se    | t output on co    | mpare match; c   | output is set up | on selection of | this mode     |

|                  | 0111 = Capt                                                                    | ure mode: Eve    | rv 16th risina e  | edae             |                  |                 |               |

|                  | 0110 = Capt                                                                    | ure mode: Eve    | ry 4th rising ed  |                  |                  |                 |               |

|                  | 0101 = Capture mode: Every rising edge                                         |                  |                   |                  |                  |                 |               |

|                  | 0100 = Capt                                                                    | ure mode: Eve    | ry falling edge   |                  |                  |                 |               |

|                  | 0011 = Capt                                                                    | ure mode: Eve    | ry rising or fall | ing edge         |                  |                 |               |

|                  | 0010 = Com                                                                     | pare mode: To    | ggle output on    | match            |                  |                 |               |

|                  |                                                                                |                  |                   | d clear TMR1 c   |                  |                 |               |

|                  | 0000 = Capt                                                                    | ure/Compare/F    | vviM off (reset   | s CCPx module    | e) (reserved for | backwards co    | ompatibility) |

The maximum PWM resolution is ten bits when T2PR is 255. The resolution is a function of the T2PR register value as shown by Equation 25-4.

### EQUATION 25-4: PWM RESOLUTION

| Resolution | = | $\frac{\log[4(T2PR+1)]}{\log(2)}$ | bits |  |

|------------|---|-----------------------------------|------|--|

|------------|---|-----------------------------------|------|--|

Note: If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 25-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| T2PR Value                | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 25-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| T2PR Value                | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 25.7 Operation in Sleep Mode

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

## 25.8 Changes in System Clock Frequency

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

## 25.9 Effects of Reset

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

PIC16(L)F1764/5/8/9

#### REGISTER 27-5: COGxRSIM0: COGx RISING EVENT SOURCE INPUT MODE REGISTER 0 (CONTINUED)

bit 1 RSIM1: COGx Rising Event Input Source 1 Mode bit

RIS1 = 1:

- 1 = Comparator 1 low-to-high transition will cause a rising event after rising event phase delay

- 0 = Comparator 1 high level will cause an immediate rising event

RIS1 = 0:

Comparator 1 has no effect on rising event.

RSIM0: COGx Rising Event Input Source 0 Mode bit

RIS0 = 1:

bit 0

- 1 = Pin selected with COGxINPPS register low-to-high transition will cause a rising event after rising event phase delay

- 0 = Pin selected with COGxINPPS register high level will cause an immediate rising event RIS0 = 0:

Pin selected with COGxINPPS register has no effect on rising event.

#### REGISTER 27-9: COGxFSIM0: COGx FALLING EVENT SOURCE INPUT MODE REGISTER 0 (CONTINUED)

bit 1 FSIM1: COGx Falling Event Input Source 1 Mode bit

FIS1 = 1:

1 = Comparator 1 high-to-low transition will cause a falling event after falling event phase delay

0 = Comparator 1 low level will cause an immediate falling event

FIS1 = 0:

Comparator 1 has no effect on falling event.

FSIM0: COGx Falling Event Input Source 0 Mode bit

FIS0 = 1:

bit 0

1 = Pin selected with COGxINPPS control high-to-low transition will cause a falling event after falling event phase delay

0 = Pin selected with COGxINPPS control low level will cause an immediate falling event

FIS0 = 0:

Pin selected with COGxINPPS control has no effect on falling event.

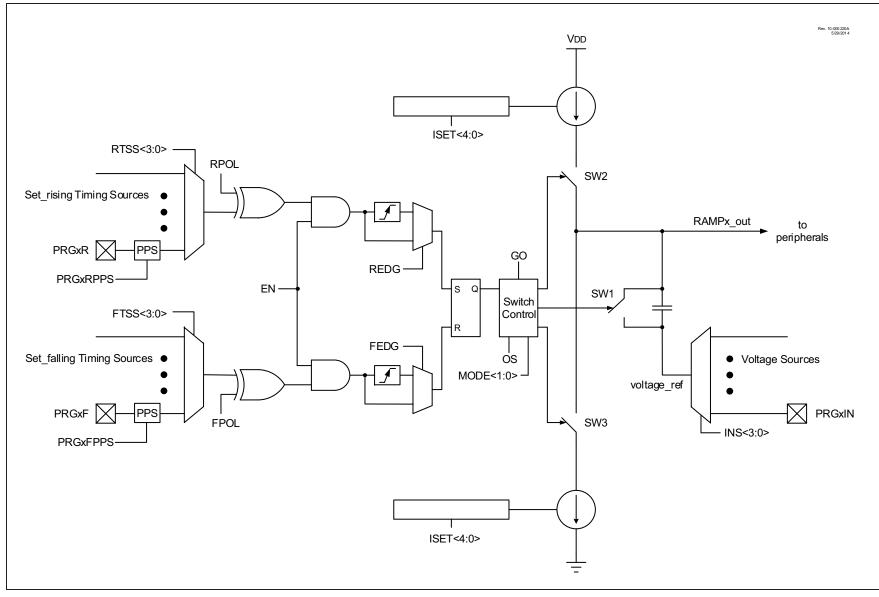

# FIGURE 30-1: SIMPLIFIED PRG MODULE BLOCK DIAGRAM

PIC16(L)F1764/5/8/9

| U-0                                       | U-0                                                                                                                                                                                                       | R/W-0/0         | R/W-0/0          | U-0              | U-0              | R/W-0/0          | R/W-0/0      |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------|------------------|--------------|--|

|                                           | —                                                                                                                                                                                                         | CHPOL           | CHSYNC           | —                | _                | CLPOL            | CLSYNC       |  |

| bit 7                                     |                                                                                                                                                                                                           |                 |                  |                  |                  |                  | bit 0        |  |

| <b></b>                                   |                                                                                                                                                                                                           |                 |                  |                  |                  |                  |              |  |

| Legend:                                   |                                                                                                                                                                                                           |                 |                  |                  |                  |                  |              |  |

| R = Readable                              | bit                                                                                                                                                                                                       | W = Writable    | bit              |                  |                  |                  |              |  |

| u = Bit is unchanged x = Bit is unknown U |                                                                                                                                                                                                           |                 | U = Unimpler     | nented bit, read | as '0'           |                  |              |  |

| '1' = Bit is set                          | '1' = Bit is set '0' = Bit is cleared                                                                                                                                                                     |                 |                  | -n/n = Value a   | at POR and BOI   | R/Value at all c | other Resets |  |

|                                           |                                                                                                                                                                                                           |                 |                  |                  |                  |                  |              |  |

| bit 7-6 Unimplemented: Read as '0'        |                                                                                                                                                                                                           |                 |                  |                  |                  |                  |              |  |

| bit 5                                     | CHPOL: Mod                                                                                                                                                                                                | ulation High Ca | arrier Polarity  | Select bit       |                  |                  |              |  |

|                                           | 1 = Selected                                                                                                                                                                                              | high carrier so | urce is inverte  | ed               |                  |                  |              |  |

|                                           | 0 = Selected                                                                                                                                                                                              | high carrier so | urce is not inv  | verted           |                  |                  |              |  |

| bit 4                                     | CHSYNC: Mo                                                                                                                                                                                                | dulation High   | Carrier Synch    | ronization Ena   | ble bit          |                  |              |  |

|                                           |                                                                                                                                                                                                           |                 |                  |                  | efore allowing a | switch to the le | ow carrier   |  |

|                                           |                                                                                                                                                                                                           | r output is not |                  | to the high car  | rier             |                  |              |  |

| bit 3-2                                   | Unimplemen                                                                                                                                                                                                | ted: Read as '  | 0'               |                  |                  |                  |              |  |

| bit 1                                     | CLPOL: Mod                                                                                                                                                                                                | ulation Low Ca  | rrier Polarity S | Select bit       |                  |                  |              |  |

|                                           | 1 = Selected low carrier source is inverted                                                                                                                                                               |                 |                  |                  |                  |                  |              |  |

|                                           | <ul><li>0 = Selected low carrier source is not inverted</li></ul>                                                                                                                                         |                 |                  |                  |                  |                  |              |  |

| bit 0                                     | CLSYNC: Mo                                                                                                                                                                                                | dulation Low C  | arrier Synchr    | onization Enab   | le bit           |                  |              |  |

|                                           | <ul> <li>1 = Modulator waits for a low edge on the low carrier before allowing a switch to the high carrier</li> <li>0 = Modulator output is not synchronized to the low carrier<sup>(1)</sup></li> </ul> |                 |                  |                  |                  |                  |              |  |

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### TABLE 33-3: BAUD RATE FORMULAS

| Co   | onfiguration B | its  |                     | Baud Rate Formula |  |

|------|----------------|------|---------------------|-------------------|--|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Baud Kale Formula |  |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |

| 0    | 0              | 1    | 8-bit/Asynchronous  |                   |  |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |  |

| 1    | 0              | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |

| 1    | 1              | х    | 16-bit/Synchronous  |                   |  |

**Legend:** x = Don't care, n = value of SPxBRGH, SPxBRGL register pair.

#### TABLE 33-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name     | Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-----------|----------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUD1CON | ABDOVF    | RCIDL    | —     | SCKP  | BRG16 |       | WUE   | ABDEN | 442                 |

| RC1STA   | SPEN      | RX9      | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 441                 |

| SP1BRGL  |           | BRG<7:0> |       |       |       |       |       |       | 443                 |

| SP1BRGH  | BRG<15:8> |          |       |       |       |       |       | 443   |                     |

| TX1STA   | CSRC      | TX9      | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 440                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

### TABLE 36-25: SPI MODE REQUIREMENTS

# Standard Operating Conditions (unless otherwise stated)

| Stanuar      | u Operating           | Conditions (unless otherwise state                                    | u)           | i    | i    | i     | i                                |

|--------------|-----------------------|-----------------------------------------------------------------------|--------------|------|------|-------|----------------------------------|

| Param<br>No. | Symbol                | Characteristic                                                        | Min.         | Тур† | Max. | Units | Conditions                       |

| SP70*        | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input | Тсү          | _    | —    | ns    |                                  |

| SP71*        | TscH                  | SCK Input High Time (Slave mode)                                      | Tcy + 20     | _    |      | ns    |                                  |

| SP72*        | TscL                  | SCK Input Low Time (Slave mode)                                       | Tcy + 20     | _    | _    | ns    |                                  |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup Time of SDI Data Input to SCK Edge                              | 100          | —    | —    | ns    |                                  |

| SP74*        | TscH2DIL,<br>TscL2DIL | Hold Time of SDI Data Input to SCK Edge                               | 100          | —    | _    | ns    |                                  |

| SP75*        | TDOR                  | SDO Data Output Rise Time                                             | —            | 10   | 25   | ns    | $3.0V \le V\text{DD} \le 5.5V$   |

|              |                       |                                                                       | —            | 25   | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| SP76*        | TDOF                  | SDO Data Output Fall Time                                             | —            | 10   | 25   | ns    |                                  |

| SP77*        | TssH2doZ              | SS↑ to SDO Output<br>High-Impedance                                   | 10           | —    | 50   | ns    |                                  |

| SP78*        | TscR                  | SCK Output Rise Time                                                  | —            | 10   | 25   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|              |                       | (Master mode)                                                         | —            | 25   | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| SP79*        | TSCF                  | SCK Output Fall Time<br>(Master mode)                                 | _            | 10   | 25   | ns    |                                  |

| SP80*        | TscH2doV,             | SDO Data Output Valid after                                           | —            | —    | 50   | ns    | $3.0V \le V\text{DD} \le 5.5V$   |

|              | TscL2doV              | SCK Edge                                                              | —            | _    | 145  | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDO Data Output Setup to<br>SCK Edge                                  | 1 Tcy        | —    | —    | ns    |                                  |

| SP82*        | TssL2doV              | SDO Data Output Valid after<br>SS↓ Edge                               | —            | —    | 50   | ns    |                                  |

| SP83*        | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                                   | 1.5 Tcy + 40 | —    | —    | ns    |                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

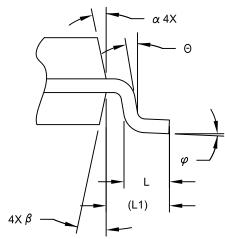

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| 1/1   | EW | C |

|-------|----|---|

| · v I |    |   |

| Units                    |    | MILLIMETERS |     |      |

|--------------------------|----|-------------|-----|------|

| Dimension Limits         |    | MIN         | NOM | MAX  |

| Number of Pins           | N  | 14          |     |      |

| Pitch                    | е  | 1.27 BSC    |     |      |

| Overall Height           | A  | -           | -   | 1.75 |

| Molded Package Thickness | A2 | 1.25        | -   | -    |

| Standoff §               | A1 | 0.10        | -   | 0.25 |

| Overall Width            | E  | 6.00 BSC    |     |      |

| Molded Package Width     | E1 | 3.90 BSC    |     |      |

| Overall Length           | D  | 8.65 BSC    |     |      |

| Chamfer (Optional)       | h  | 0.25        | -   | 0.50 |

| Foot Length              | L  | 0.40        | -   | 1.27 |

| Footprint                | L1 | 1.04 REF    |     |      |

| Lead Angle               | Θ  | 0°          | -   | -    |

| Foot Angle               | φ  | 0°          | -   | 8°   |

| Lead Thickness           | С  | 0.10        | -   | 0.25 |

| Lead Width               | b  | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2