### Microchip Technology - PIC16F1769-I/SO Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 × 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 2x5b, 2x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1769-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 3-12: PIC16(L)F1764/5 MEMORY MAP (BANKS 27-30)

|       | Bank 27    |               | Bank 28               |       | Bank 29 |      | Bank 30  |

|-------|------------|---------------|-----------------------|-------|---------|------|----------|

| 8Ch   | —          | E0Ch          | —                     | E8Ch  | —       | F0Ch | _        |

| 8Dh   | _          | E0Dh          | _                     | E8Dh  | _       | F0Dh | _        |

| 08Eh  | PWMEN      | E0Eh          | _                     | E8Eh  | _       | F0Eh | _        |

| D8Fh  | PWMLD      | E0Fh          | PPSLOCK               | E8Fh  | _       | F0Fh | CLCDATA  |

| D90h  | PWMOUT     | E10h          | INTPPS                | E90h  | RA0PPS  | F10h | CLC1CON  |

| D91h  | PWM5PHL    | E11h          | TOCKIPPS              | E91h  | RA1PPS  | F11h | CLC1POL  |

| D92h  | PWM5PHH    | E12h          | T1CKIPPS              | E92h  | RA2PPS  | F12h | CLC1SEL0 |

| D93h  | PWM5DCL    | E13h          | TIGPPS                | E93h  | -       | F13h | CLC1SEL1 |

| D94h  | PWM5DCH    | E14h          | CCP1PPS               | E94h  | RA4PPS  | F14h | CLC1SEL2 |

| D95h  | PWM5PRL    | E15h          | 0011110               | E95h  | RA5PPS  | F15h | CLC1SEL3 |

| D96h  | PWM5PRH    | E16h          | COG1INPPS             | E96h  | NAJEE 3 | F16h | CLC1GLS0 |

| D97h  | PWM50FL    | E17h          | COGHINFF3             | E97h  |         | F17h | CLC1GLS1 |

|       |            |               |                       |       |         |      |          |

| D98h  | PWM50FH    | E18h          |                       | E98h  |         | F18h | CLC1GLS2 |

| D99h  | PWM5TMRL   | E19h          | T2INPPS               | E99h  | _       | F19h | CLC1GLS3 |

| D9Ah  | PWM5TMRH   | E1Ah          | T3CKIPPS              | E9Ah  |         | F1Ah | CLC2CON  |

| D9Bh  | PWM5CON    | E1Bh          | T3GPPS                | E9Bh  |         | F1Bh | CLC2POL  |

| D9Ch  | PWM5INTE   | E1Ch          | T4INPPS               | E9Ch  | _       | F1Ch | CLC2SEL0 |

| D9Dh  | PWM5INTF   | E1Dh          | T5CKIPPS              | E9Dh  | _       | F1Dh | CLC2SEL1 |

| D9Eh  | PWM5CLKCON | E1Eh          | T5GPPS                | E9Eh  | _       | F1Eh | CLC2SEL2 |

| D9Fh  | PWM5LDCON  | E1Fh          | T6INPPS               | E9Fh  | _       | F1Fh | CLC2SEL3 |

| DA0h  | PWM50FC0N  | E20h          | SSPCLKPPS             | EA0h  | RC0PPS  | F20h | CLC2GLS0 |

| DA1h  | _          | E21h          | SSPDATPPS             | EA1h  | RC1PPS  | F21h | CLC2GLS1 |

| DA2h  | —          | E22h          | SSPSSPPS              | EA2h  | RC2PPS  | F22h | CLC2GLS2 |

| DA3h  | —          | E23h          | -                     | EA3h  | RC3PPS  | F23h | CLC2GLS3 |

| DA4h  | —          | E24h          | RXPPS                 | EA4h  | RC4PPS  | F24h | CLC3CON  |

| DA5h  | _          | E25h          | CKPPS                 | EA5h  | RC5PPS  | F25h | CLC3POL  |

| DA6h  | _          | E26h          | _                     | EA6h  | _       | F26h | CLC3SEL0 |

| DA7h  | _          | E27h          | _                     | EA7h  | —       | F27h | CLC3SEL1 |

| DA8h  | _          | E28h          | CLCIN0PPS             | EA8h  | _       | F28h | CLC3SEL2 |

| DA9h  | _          | E29h          | CLCIN1PPS             | EA9h  | _       | F29h | CLC3SEL3 |

| DAAh  | _          | E2Ah          | CLCIN2PPS             | EAAh  | _       | F2Ah | CLC3GLS0 |

| DABh  | _          | E2Bh          | CLCIN3PPS             | EABh  | _       | F2Bh | CLC3GLS1 |

| DACh  | _          | E2Ch          | PRG1FPPS              | EACh  | _       | F2Ch | CLC3GLS2 |

| DADh  |            | E2Dh          | PRG1RPPS              | EADh  |         | F2Dh | CLC3GLS3 |

| DAEh  |            | E2Eh          |                       | EAEh  |         | F2Eh |          |

| DAFh  |            | E2Fh          |                       | EAFh  |         | F2Fh |          |

| DB0h  |            | E30h          | MD1CHPPS              | EB0h  |         | F30h |          |

| DB011 |            | E3011<br>E31h | MD1CLPPS              | EB011 |         | F301 |          |

|       |            |               | MD1CLPPS<br>MD1MODPPS |       |         |      |          |

| DB2h  | _          | E32h          |                       | EB2h  | _       | F32h | _        |

| DB3h  | _          | E33h          | _                     | EB3h  | _       | F33h | _        |

| DB4h  | _          | E34h          | —                     | EB4h  | _       | F34h | _        |

| DB5h  |            | E35h          | —                     | EB5h  |         | F35h | _        |

| DB6h  | _          | E36h          | _                     | EB6h  |         | F36h | _        |

| DB7h  | —          | E37h          | —                     | EB7h  | —       | F37h | —        |

| DB8h  | —          | E38h          | —                     | EB8h  | _       | F38h | —        |

| DB9h  | —          | E39h          | —                     | EB9h  |         | F39h | —        |

| DBAh  | —          | E3Ah          | —                     | EBAh  | _       | F3Ah | _        |

| DBBh  | —          | E3Bh          | _                     | EBBh  | —       | F3Bh | —        |

| DBCh  | _          | E3Ch          | _                     | EBCh  | _       | F3Ch | _        |

| DBDh  | _          | E3Dh          | _                     | EBDh  | _       | F3Dh | _        |

| DBEh  | _          | E3Eh          | _                     | EBEh  | _       | F3Eh | _        |

| DBFh  | _          | E3Fh          | —                     | EBFh  | _       | F3Fh | _        |

| DC0h  |            | E40h          |                       | EC0h  |         | F40h |          |

|       |            |               |                       |       |         |      |          |

|       | -          |               | —                     |       | —       |      | -        |

|       |            |               |                       |       |         |      |          |

# PIC16(L)F1764/5/8/9

### TABLE 3-16: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    | LE 3-10.   |                                                   |                                                                             |                     |                   |                 |           |        | i         | +                 | ·                               |

|--------------------|------------|---------------------------------------------------|-----------------------------------------------------------------------------|---------------------|-------------------|-----------------|-----------|--------|-----------|-------------------|---------------------------------|

| Addr               | Name       | Bit 7                                             | Bit 6                                                                       | Bit 5               | Bit 4             | Bit 3           | Bit 2     | Bit 1  | Bit 0     | Value on POR, BOR | Value on<br>All Other<br>Resets |

| Bank               | < 8        |                                                   |                                                                             |                     |                   |                 |           |        |           |                   |                                 |

| 40Ch               |            |                                                   |                                                                             |                     |                   |                 |           |        |           |                   |                                 |

| <br>40Dh           | _          | Unimpleme                                         | nted                                                                        |                     |                   |                 |           |        |           | _                 | _                               |

| 40Eh               | HIDRVC     | _                                                 | _                                                                           | HIDC                | <5:4>             | —               | —         | _      | —         | 00                | 00                              |

| 40Fh               |            |                                                   | •                                                                           | •                   |                   |                 |           | •      | •         |                   |                                 |

| <br>412h           | _          | Unimpleme                                         | nted                                                                        |                     |                   |                 |           |        |           | -                 | —                               |

| 413h               | T4TMR      | Holding Reg                                       | gister for the 8                                                            | -Bit TMR4 Regist    | er                |                 |           |        |           | 0000 0000         | 0000 0000                       |

| 413h               | T4PR       | TMR4 Peric                                        | od Register                                                                 |                     |                   |                 |           |        |           | 1111 1111         | 1111 1111                       |

| 415h               | T4CON      | ON                                                |                                                                             | CKPS<2:0>           |                   |                 | OUTP      | S<3:0> |           | 0000 0000         | 0000 0000                       |

| 416h               | T4HLT      | PSYNC                                             | CKPOL                                                                       | CKSYNC              |                   |                 | MODE<4:0> |        |           | 0000 0000         | 0000 0000                       |

| 417h               | T4CLKCON   | —                                                 | _                                                                           | —                   | —                 |                 | CS<       | <3:0>  |           | 0000              | 0000                            |

| 418h               | T4RST      | —                                                 | _                                                                           | —                   | —                 |                 | RSEL      | _<3:0> |           | 0000              | 0000                            |

| 419h               | _          | Unimpleme                                         | Unimplemented                                                               |                     |                   |                 |           |        |           | _                 | —                               |

| 41Ah               | T6TMR      | 6TMR Holding Register for the 8-Bit TMR4 Register |                                                                             |                     |                   |                 |           |        |           | 0000 0000         | 0000 0000                       |

| 41Bh               | T6PR       | TMR4 Perio                                        | TMR4 Period Register                                                        |                     |                   |                 |           |        | 1111 1111 | 1111 1111         |                                 |

| 41Ch               | T6CON      | ON                                                | ON CKPS<2:0> OUTPS<3:0>                                                     |                     |                   |                 |           |        | 0000 0000 | 0000 0000         |                                 |

| 41Dh               | T6HLT      | PSYNC                                             | CKPOL                                                                       | CKSYNC              |                   | I               | MODE<4:0> |        |           | 0000 0000         | 0000 0000                       |

| 41Eh               | T6CLKCON   | —                                                 | —                                                                           | —                   | _                 |                 | CS<       | <3:0>  |           | 0000              | 0000                            |

| 41Fh               | T6RST      | —                                                 | —                                                                           | —                   | —                 |                 | RSEL      | _<3:0> |           | 0000              | 0000                            |

| Bank               | <b>(</b> 9 |                                                   |                                                                             |                     |                   |                 |           |        |           |                   |                                 |

| 48Ch<br>to<br>492h | _          | Unimplemented                                     |                                                                             |                     |                   |                 |           |        |           | _                 | _                               |

| 493h               | TMR3L      | Holding Reg                                       | gister for the L                                                            | east Significant B  | yte of the 16-Bi  | t TMR1 Register | r         |        |           | XXXX XXXX         | uuuu uuuu                       |

| 494h               | TMR3H      | Holding Reg                                       | gister for the N                                                            | lost Significant By | yte of the 16-Bit | TMR1 Register   |           |        |           | XXXX XXXX         | uuuu uuuu                       |

| 495h               | T3CON      | CS                                                | <1:0>                                                                       | CKPS                | <1:0>             | OSCEN           | SYNC      | —      | ON        | 0000 00-0         | uuuu uu-u                       |

| 496h               | T3GCON     | GE                                                | GPOL                                                                        | GTM                 | GSPM              | GGO/DONE        | GVAL      | GSS    | S<1:0>    | 00x0 0x00         | uuuu uxuu                       |

| 497h<br>to<br>499h | _          | Unimplemented                                     |                                                                             |                     |                   |                 |           |        |           | _                 | _                               |

| 49Ah               | TMR5L      | Holding Reg                                       | Holding Register for the Least Significant Byte of the 16-Bit TMR1 Register |                     |                   |                 |           |        |           | XXXX XXXX         | uuuu uuuu                       |

| 49Bh               | TMR5H      | Holding Reg                                       | gister for the N                                                            | lost Significant By | yte of the 16-Bit | TMR1 Register   |           |        |           | XXXX XXXX         | uuuu uuuu                       |

| 49Ch               | T5CON      | CS                                                | <1:0>                                                                       | CKPS                | <1:0>             | OSCEN           | SYNC      | —      | ON        | 0000 00-0         | uuuu uu-u                       |

| 49Dh               | T5GCON     | GE                                                | GPOL                                                                        | GTM                 | GSPM              | GGO/DONE        | GVAL      | GSS    | 6<1:0>    | 00x0 0x00         | uuuu uxuu                       |

| 49Eh<br>to<br>49Fh | —          | Unimpleme                                         | nted                                                                        |                     |                   |                 |           |        |           | _                 | _                               |

Legend: x = unknown; u = unchanged; q = value depends on condition; - = unimplemented, read as '0'; x = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1768/9 only.

3: PIC16(L)F1764/5 only.

4: Unimplemented on PIC16LF1764/5/8/9.

| R/W-0/0          | R/W-0/0                                                                                                         | R/W-0/0                      | R/W-0/0          | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0     |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------|------------------|-----------------|------------------|----------|-------------|--|

| TMR1GIE          | ADIE                                                                                                            | RCIE                         | TXIE             | SSP1IE          | CCP1IE           | TMR2IE   | TMR1IE      |  |

| bit 7            |                                                                                                                 | ·                            |                  |                 |                  |          | bit         |  |

| Legend:          |                                                                                                                 |                              |                  |                 |                  |          |             |  |

| R = Readable     | bit                                                                                                             | W = Writable                 | hit              |                 |                  |          |             |  |

| u = Bit is unch  |                                                                                                                 | x = Bit is unkr              |                  | U = Unimpler    | mented bit, read | l as '0' |             |  |

| '1' = Bit is set | •                                                                                                               | '0' = Bit is cle             |                  |                 | at POR and BO    |          | ther Resets |  |

|                  |                                                                                                                 | 0 21110 010                  |                  |                 |                  |          |             |  |

| bit 7            | TMR1GIE: Ti                                                                                                     | mer1 Gate Inte               | errupt Enable b  | oit             |                  |          |             |  |

|                  | 1 = Enables t                                                                                                   | he Timer1 gate               | e acquisition ir | nterrupt        |                  |          |             |  |

|                  | 0 = Disables                                                                                                    | the Timer1 gate              | e acquisition i  | nterrupt        |                  |          |             |  |

| bit 6            | -                                                                                                               | j-to-Digital Con             | , ,              | Interrupt Enabl | le bit           |          |             |  |

|                  |                                                                                                                 | he ADC interru               |                  |                 |                  |          |             |  |

|                  |                                                                                                                 | = Disables the ADC interrupt |                  |                 |                  |          |             |  |

| bit 5            |                                                                                                                 | RT Receive Int               | •                |                 |                  |          |             |  |

|                  | <ul> <li>1 = Enables the EUSART receive interrupt</li> <li>0 = Disables the EUSART receive interrupt</li> </ul> |                              |                  |                 |                  |          |             |  |

| bit 4            |                                                                                                                 | RT Transmit Int              |                  |                 |                  |          |             |  |

|                  |                                                                                                                 | he EUSART tra                | •                |                 |                  |          |             |  |

|                  |                                                                                                                 | the EUSART tr                |                  |                 |                  |          |             |  |

| bit 3            | SSP1IE: Mas                                                                                                     | ter Synchrono                | us Serial Port   | (MSSP) Interru  | upt Enable bit   |          |             |  |

|                  |                                                                                                                 | he MSSP inter                |                  |                 |                  |          |             |  |

|                  |                                                                                                                 | the MSSP inter               |                  |                 |                  |          |             |  |

| bit 2            |                                                                                                                 | P1 Interrupt En              |                  |                 |                  |          |             |  |

|                  |                                                                                                                 | he CCP1 interi               |                  |                 |                  |          |             |  |

| bit 1            |                                                                                                                 | the CCP1 inter               | •                | -nabla bit      |                  |          |             |  |

| DILI             | 1 TMR2IE: TMR2 to T2PR Match Interrupt Enable bit 1 = Enables the Timer2 to T2PR match interrupt                |                              |                  |                 |                  |          |             |  |

|                  |                                                                                                                 | the Timer2 to T              |                  |                 |                  |          |             |  |

| bit 0            |                                                                                                                 | er1 Overflow Ir              |                  | •               |                  |          |             |  |

|                  |                                                                                                                 | he Timer1 ove                |                  |                 |                  |          |             |  |

|                  | 0 = Disables                                                                                                    |                              |                  |                 |                  |          |             |  |

### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| IABLE /-1: | SUMMAI                | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |        |        |                       |                     |                     |                       |                     |

|------------|-----------------------|-------------------------------------------------|--------|--------|-----------------------|---------------------|---------------------|-----------------------|---------------------|

| Name       | Bit 7                 | Bit 6                                           | Bit 5  | Bit 4  | Bit 3                 | Bit 2               | Bit 1               | Bit 0                 | Register<br>on Page |

| INTCON     | GIE                   | PEIE                                            | TMR0IE | INTE   | IOCIE                 | TMR0IF              | INTF                | IOCIF                 | 101                 |

| OPTION_REG | WPUEN                 | INTEDG                                          | TMR0CS | TMR0SE | PSA                   |                     | PS<2:0>             |                       | 214                 |

| PIE1       | TMR1GIE               | ADIE                                            | RCIE   | TXIE   | SSP1IE                | CCP1IE              | TMR2IE              | TMR1IE                | 102                 |

| PIE2       | OSFIE                 | C2IE                                            | C1IE   | —      | BCL1IE                | C4IE <sup>(1)</sup> | C3IE <sup>(1)</sup> | CCP2IE <sup>(1)</sup> | 103                 |

| PIE3       | PWM6IE <sup>(1)</sup> | PWM5IE                                          | COG1IE | ZCDIE  | COG2IE <sup>(1)</sup> | CLC3IE              | CLC2IE              | CLC1IE                | 104                 |

| PIR1       | TMR1GIF               | ADIF                                            | RCIF   | TXIF   | SSP1IF                | CCP1IF              | TMR2IF              | TMR1IF                | 105                 |

| PIR2       | OSFIF                 | C2IF                                            | C1IF   | —      | BCL1IF                | C4IF <sup>(1)</sup> | C3IF <sup>(1)</sup> | CCP2IF <sup>(1)</sup> | 106                 |

| PIR3       | PWM6IF <sup>(1)</sup> | PWM5IF                                          | COG1IF | ZCDIF  | COG2IF <sup>(1)</sup> | CLC3IF              | CLC2IF              | CLC1IF                | 107                 |

#### **011**

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

Note 1: PIC16(L)F1768/9 only.

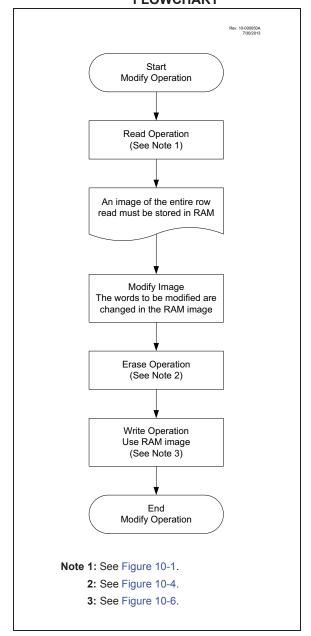

### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

### FIGURE 10-7:

### FLASH PROGRAM MEMORY MODIFY FLOWCHART

### 11.4 Register Definitions: PORTB

### **REGISTER 11-9: PORTB: PORTB REGISTER**

| R/W-x/u                                                                                 | R/W-x/u | R/W-x/u           | R/W-x/u | U-0          | U-0              | U-0    | U-0 |

|-----------------------------------------------------------------------------------------|---------|-------------------|---------|--------------|------------------|--------|-----|

|                                                                                         | RB<7:   | 4> <sup>(1)</sup> |         | —            | —                | —      | —   |

| bit 7                                                                                   |         |                   | · · ·   |              |                  | bit 0  |     |

|                                                                                         |         |                   |         |              |                  |        |     |

| Legend:                                                                                 |         |                   |         |              |                  |        |     |

| R = Readable bit W = Writable bit                                                       |         |                   |         |              |                  |        |     |

| u = Bit is uncha                                                                        | anged   | x = Bit is unkr   | nown    | U = Unimplen | nented bit, read | as '0' |     |

| '1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Re |         |                   |         | other Resets |                  |        |     |

bit 7-4 **RB<7:4>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to the corresponding LATB register. Reads from PORTB register are the return of the actual I/O pin values.

### REGISTER 11-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

|         | TRISB   | <7:4>   |         | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

| TRISB<7:4>: PORTB Tri-State Control bits             |

|------------------------------------------------------|

| 1 = PORTB pin is configured as an input (tri-stated) |

| 0 = PORTB pin is configured as an output             |

|                                                      |

bit 3-0 Unimplemented: Read as '0'

### REGISTER 11-19: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u | R/W-x/u           | R/W-x/u                                   | R/W-x/u              | R/W-x/u                                                           | R/W-x/u                                                                          | R/W-x/u                                                                                 |

|---------|-------------------|-------------------------------------------|----------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|         |                   | LATC                                      | <7:0> <sup>(1)</sup> |                                                                   |                                                                                  |                                                                                         |

|         |                   |                                           |                      |                                                                   |                                                                                  | bit 0                                                                                   |

|         |                   |                                           |                      |                                                                   |                                                                                  |                                                                                         |

|         |                   |                                           |                      |                                                                   |                                                                                  |                                                                                         |

| bit     | W = Writable      | bit                                       |                      |                                                                   |                                                                                  |                                                                                         |

| anged   | x = Bit is unkr   | nown                                      | U = Unimpler         | nented bit, read                                                  | as '0'                                                                           |                                                                                         |

|         | '0' = Bit is clea | ared                                      | -n/n = Value a       | at POR and BO                                                     | R/Value at all o                                                                 | ther Resets                                                                             |

|         | bit               | bit W = Writable<br>anged x = Bit is unkr | bit W = Writable bit | bit $W = Writable bit$<br>anged $x = Bit is unknown U = Unimpler$ | bit $W = Writable bit$<br>anged $x = Bit is unknown U = Unimplemented bit, read$ | bit $W = Writable bit$<br>anged $x = Bit is unknown U = Unimplemented bit, read as '0'$ |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

Note 1: LATC<7:6> are available on PIC16(L)F1768/9 only.

### REGISTER 11-20: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1 | R/W-1/1              | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|----------------------|-----|-----|---------|---------|---------|---------|

| ANSC<   | :7:6> <sup>(2)</sup> | —   | —   |         | ANSC    | 2<3:0>  |         |

| bit 7   |                      |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

| bit 7-6 | <ul> <li>ANSC&lt;7:6&gt;: Analog Select Between Analog or Digital Function on RC&lt;7:6&gt; Pins bits<sup>(2)</sup></li> <li>1 = Analog input; pin is assigned as an analog input, digital input buffer is disabled<sup>(1)</sup></li> <li>0 = Digital I/O; pin is assigned to port or digital special function</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                 |

| bit 3-0 | <b>ANSC&lt;3:0&gt;</b> : Analog Select Between Analog or Digital Function on RC<3:0> Pins bits<br>1 = Analog input; pin is assigned as an analog input, digital input buffer is disabled <sup>(1)</sup><br>0 = Digital I/O; pin is assigned to port or digital special function                                            |

- **Note 1:** When setting a pin to an analog input, the corresponding TRISx bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSC<7:6> are available on PIC16(L)F1768/9 only.

### 17.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- Operational amplifier inverting and non-inverting inputs

- · ADC input channel

- DACxOUT1 pin

### TABLE 17-1:AVAILABLE 5-BIT DACs

| Device        | D3 | D4 |

|---------------|----|----|

| PIC16(L)F1764 | •  |    |

| PIC16(L)F1765 | •  |    |

| PIC16(L)F1768 | •  | ٠  |

| PIC16(L)F1769 | ٠  | •  |

The Digital-to-Analog Converter (DAC) is enabled by setting the EN bit of the DACxCON0 register.

### 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the REF<4:0> bits of the DACxREF register.

The DAC output voltage is determined by Equation 17-1.

### EQUATION 17-1: DAC OUTPUT VOLTAGE

$$\frac{IF \ DACxEN = 1:}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[4:0]}{2^5} \right) + VSOURCE-$$

$$VSOURCE+ = VDD, \ VREF, \ or \ FVR \ Buffer 2$$

$$VSOURCE- = VSS$$

### 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 36-20.

### 17.3 DAC Voltage Reference Output

The DAC voltage can be output to the DACxOUT1 pin by setting the OE1 bit of the DACxCON0 register. Selecting the DAC voltage for output on the DACxOUT1 pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACxOUT1 pin when it has been configured for DAC voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage output for external connections to the DACxOUT1 pin. Figure 17-2 shows an example buffering technique.

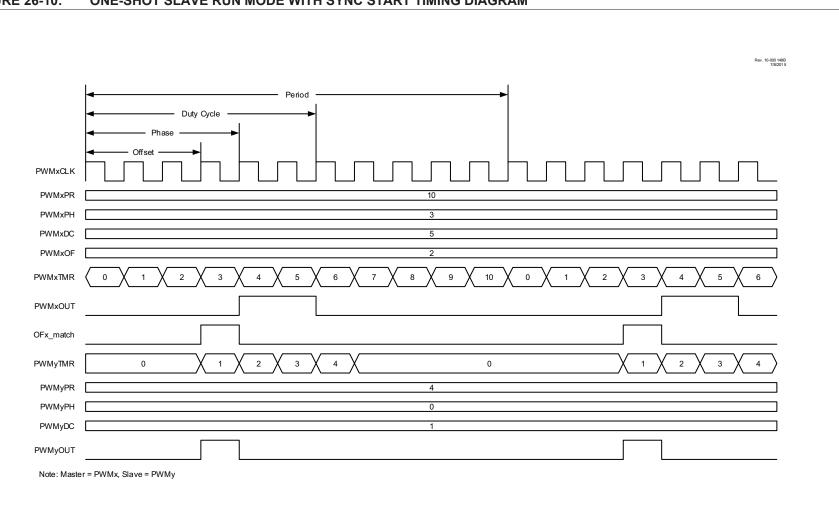

### FIGURE 26-10: ONE-SHOT SLAVE RUN MODE WITH SYNC START TIMING DIAGRAM

PIC16(L)F1764/5/8/9

### 27.15 Register Definitions: COG Control

Long bit name prefixes for the COG peripherals are shown in Table 27-3. Refer to **Section 1.1** "**Register and Bit Naming Conventions**" for more information.

### TABLE 27-3: BIT NAME PREFIXES

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| COG1                | G1              |

| COG2 <sup>(1)</sup> | G2              |

Note 1: PIC16(L)F1768/9 devices only.

### REGISTER 27-1: COGxCON0: COGx CONTROL REGISTER 0

| R/W-0/0                                                                                                                                                                                                                                                                                                                                             | R/W-0/0                        | U-0                             | R/W-0/0     | R/W-0/0        | R/W-0/0           | R/W-0/0          | R/W-0/0     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|-------------|----------------|-------------------|------------------|-------------|

| EN                                                                                                                                                                                                                                                                                                                                                  | LD                             |                                 | CS<1:0>     |                |                   | MD<2:0>          |             |

| bit 7                                                                                                                                                                                                                                                                                                                                               |                                |                                 |             |                |                   |                  | bit 0       |

|                                                                                                                                                                                                                                                                                                                                                     |                                |                                 |             |                |                   |                  |             |

| Legend:                                                                                                                                                                                                                                                                                                                                             |                                |                                 |             |                |                   |                  |             |

| R = Readable                                                                                                                                                                                                                                                                                                                                        | bit                            | W = Writable                    | bit         |                |                   |                  |             |

| u = Bit is unch                                                                                                                                                                                                                                                                                                                                     | anged                          | x = Bit is unkr                 | nown        | U = Unimpler   | mented bit, read  | 1 as '0'         |             |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                                    |                                | '0' = Bit is clea               | ared        | -n/n = Value a | at POR and BO     | R/Value at all o | ther Resets |

|                                                                                                                                                                                                                                                                                                                                                     |                                |                                 |             |                |                   |                  |             |

| bit 7                                                                                                                                                                                                                                                                                                                                               | EN: COGx Er                    | nable bit                       |             |                |                   |                  |             |

|                                                                                                                                                                                                                                                                                                                                                     | 1 = Module is<br>0 = Module is |                                 |             |                |                   |                  |             |

| bit 6                                                                                                                                                                                                                                                                                                                                               | LD: COGx Lo                    | ad Buffers bit                  |             |                |                   |                  |             |

|                                                                                                                                                                                                                                                                                                                                                     |                                | lanking and de to buffer transf |             |                | d with register v | alues on next i  | nput events |

| bit 5                                                                                                                                                                                                                                                                                                                                               | Unimplemen                     | ted: Read as '                  | 0'          |                |                   |                  |             |

| bit 4-3                                                                                                                                                                                                                                                                                                                                             | <b>CS&lt;1:0&gt;:</b> CO       | Gx Clock Sele                   | ction bits  |                |                   |                  |             |

| 11 = Reserved; do not use<br>10 = COG_clock is HFINTOSC (stays active during Sleep)<br>01 = COG_clock is Fosc<br>00 = COG_clock is Fosc/4                                                                                                                                                                                                           |                                |                                 |             |                |                   |                  |             |

| bit 2-0                                                                                                                                                                                                                                                                                                                                             | MD<2:0>: CC                    | OGx Mode Sele                   | ection bits |                |                   |                  |             |

| <pre>11x = Reserved; do not use 101 = COG outputs operate in Push-Pull mode 100 = COG outputs operate in Half-Bridge mode 011 = COG outputs operate in Reverse Full-Bridge mode 010 = COG outputs operate in Forward Full-Bridge mode 001 = COG outputs operate in Synchronous Steered PWM mode 000 = COG outputs operate in Steered PWM mode</pre> |                                |                                 |             |                |                   |                  |             |

# PIC16(L)F1764/5/8/9

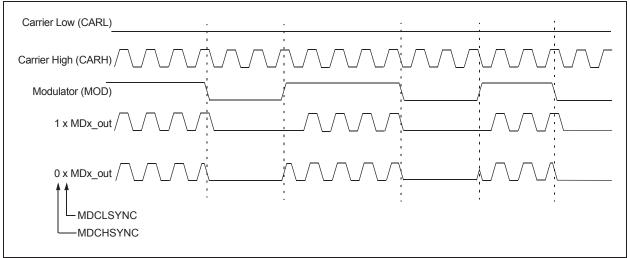

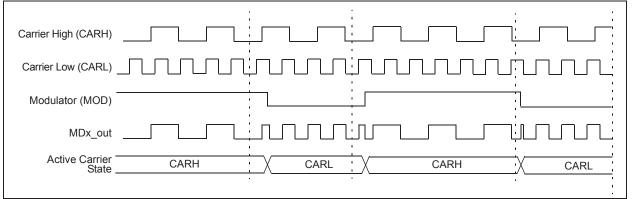

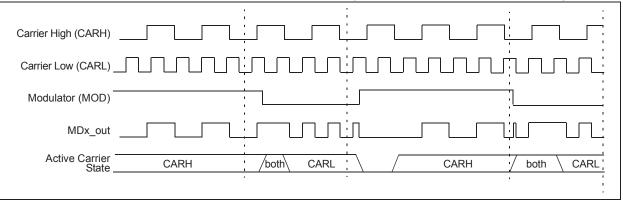

### FIGURE 31-4: CARRIER HIGH SYNCHRONIZATION (MDCHSYNC = 1, MDCLSYNC = 0)

### 32.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allows the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the Acknowledge time of the active bus. The ACKTIM status bit is only active when the AHEN bit or DHEN bit is enabled.

### 32.5 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected by the SSPM<3:0> bits of SSPxCON1 register. The modes can be divided into 7-Bit and 10-Bit Addressing modes. 10-Bit Addressing mode operates the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes, with SSPxIF additionally getting set upon detection of a Start, Restart or Stop condition.

### 32.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 32-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes Idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 32-5) affects the address matching process. See **Section 32.5.8 "SSP Mask Register**" for more information.

### 32.5.1.1 I<sup>2</sup>C Slave 7-Bit Addressing Mode

In 7-Bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

### 32.5.1.2 I<sup>2</sup>C Slave 10-Bit Addressing Mode

In 10-Bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSbs of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the Acknowledge of the high byte, the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match, SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated, the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-Bit Addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then Acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

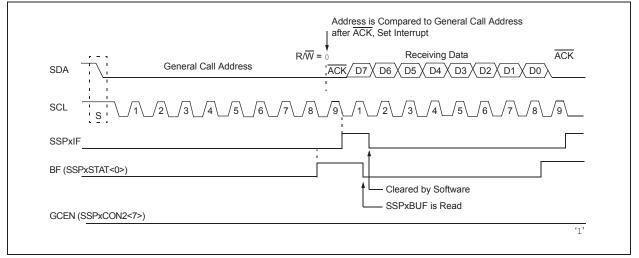

### 32.5.7 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is a reserved address in the  $I^{2}C$  protocol, defined as address: 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address, regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros, with the

R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 32-24 shows a general call reception sequence.

In 10-Bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

### FIGURE 32-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

### 32.5.8 SSP MASK REGISTER

An MSSP Mask (SSPxMSK) register (Register 32-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care". This register is reset to all '1's upon any Reset condition, and therefore, has no effect on standard SSP operation until written with a mask value.

The MSSP Mask register is active during:

- 7-Bit Address mode: Address compare of A<7:1>.

- 10-Bit Address mode: Address compare of A<7:0> only. The MSSP mask has no effect during the reception of the first (high) byte of the address.

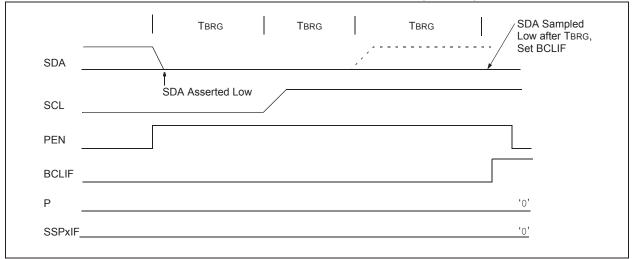

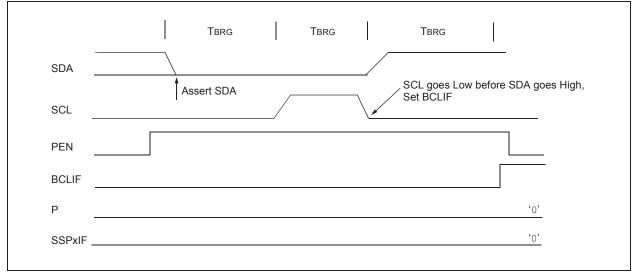

### 32.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 32-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 32-39).

### FIGURE 32-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

FIGURE 32-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| R-0/0                 | R/W-0/0                                 | R/W-0/0                                              | R/W-0/0                                      | R/W-0/0                                      | R/W-0/0                                   | R/W-0/0           | R/W-0/0        |

|-----------------------|-----------------------------------------|------------------------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------|-------------------|----------------|

| ACKTIM <sup>(3)</sup> | PCIE                                    | SCIE                                                 | BOEN                                         | SDAHT                                        | SBCDE                                     | AHEN              | DHEN           |

| bit 7                 |                                         |                                                      |                                              |                                              |                                           |                   | bit (          |

|                       |                                         |                                                      |                                              |                                              |                                           |                   |                |

| Legend:               |                                         |                                                      |                                              |                                              |                                           |                   |                |

| R = Readable          | e bit                                   | W = Writable                                         | bit                                          |                                              |                                           |                   |                |

| u = Bit is unc        | hanged                                  | x = Bit is unki                                      | nown                                         | U = Unimpler                                 | mented bit, read                          | l as '0'          |                |

| '1' = Bit is set      | t                                       | '0' = Bit is cle                                     | ared                                         | -n/n = Value                                 | at POR and BO                             | R/Value at all c  | other Resets   |

|                       |                                         |                                                      | or r - 1 · · · · · · · · · · · · · · · · · · |                                              | (3)                                       |                   |                |

| bit 7                 |                                         | nowledge Tim                                         |                                              |                                              | s only) <sup>ey</sup><br>e, set on eighth | falling adda of   | SCI alaak      |

|                       | 1 =  Indicates<br>0 =  Not an Ac        | knowledae se                                         | quence. cleare                               | edge sequenc<br>ed on 9 <sup>th</sup> rising | edge of SCL cl                            | lock              | SCL CIUCK      |

| bit 6                 |                                         | ondition Interru                                     | -                                            | -                                            | -                                         |                   |                |

|                       |                                         | nterrupt on det                                      |                                              | •                                            | 5,                                        |                   |                |

|                       | •                                       | ction interrupts                                     |                                              |                                              |                                           |                   |                |

| bit 5                 |                                         | ondition Interru                                     | •                                            | •                                            | • /                                       |                   |                |

|                       |                                         | nterrupt on det<br>ction interrupts                  |                                              |                                              | ditions                                   |                   |                |

| bit 4                 |                                         | · Overwrite Ena                                      |                                              | ,                                            |                                           |                   |                |

|                       | In SPI Slave                            |                                                      |                                              |                                              |                                           |                   |                |

|                       |                                         |                                                      | ry time that a r                             | new data byte                                | is shifted in, ign                        | oring the BF bi   | t              |

|                       |                                         | te is received<br>N1 register is s                   |                                              |                                              | T register alrea                          | dy set, the SS    | POV bit of th  |

|                       | In I <sup>2</sup> C Master              | mode and SP                                          | I Master mode                                | <u>:</u>                                     |                                           |                   |                |

|                       | This bit is igno                        |                                                      |                                              |                                              |                                           |                   |                |

|                       | of the SS                               | F is updated a POV bit only it                       | f the BF bit = 0                             | )                                            | eceived address                           | s/data byte, ign  | oring the stat |

|                       |                                         | F is only updat                                      |                                              |                                              |                                           |                   |                |

| bit 3                 |                                         | Hold Time Se                                         |                                              |                                              |                                           |                   |                |

|                       |                                         | of 300 ns hold<br>of 100 ns hold                     |                                              |                                              |                                           |                   |                |

| bit 2                 |                                         |                                                      |                                              | -                                            | C Slave mode o                            | onlv)             |                |

|                       | If, on the risir                        | ng edge of SC                                        | L, SDA is san                                | npled low whe                                | n the module is                           | • •               | high state, th |

|                       |                                         | the PIR2 regis                                       |                                              | the bus goes I                               | dle                                       |                   |                |

|                       |                                         | lave bus collis<br>collision interi                  |                                              | led                                          |                                           |                   |                |

| bit 1                 |                                         | ss Hold Enabl                                        | -                                            |                                              |                                           |                   |                |

|                       |                                         |                                                      | ,                                            | 3,                                           | ching received                            | address byte:     | CKP bit of th  |

|                       | SSPxCO                                  | N1 register wil                                      | I be cleared an                              |                                              |                                           |                   |                |

|                       |                                         | holding is disa                                      |                                              |                                              |                                           |                   |                |

| bit 0                 |                                         | Hold Enable bi                                       |                                              | 3,                                           |                                           |                   |                |

|                       | bit of the                              | y the eighth fall<br>SSPxCON1 re<br>ding is disabled | egister and SC                               |                                              | ed data byte; sla                         | ave hardware o    | lears the CK   |

|                       |                                         | -                                                    |                                              |                                              |                                           |                   |                |

| wł                    | or daisy-chained s<br>nen a new byte is | received and                                         | BF = 1, but ha                               | rdware continu                               | es to write the n                         | nost recent byte  | e to SSP1BU    |

|                       | his bit has no effe<br>abled.           | ect in Slave mo                                      | oues in which S                              | Start and Stop                               | condition detec                           | uon is explicitly | IISTED AS      |

### REGISTER 32-4: SSP1CON3: MSSP CONTROL REGISTER 3

3: The ACKTIM status bit is only active when the AHEN bit or DHEN bit is set.

# PIC16(L)F1764/5/8/9

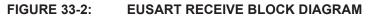

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 33-1, Register 33-2 and Register 33-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

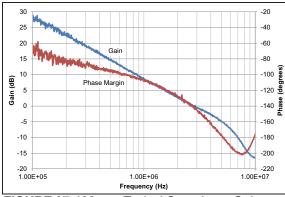

### TABLE 36-15: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3,4)</sup>

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = 3.0V, Ta = +25°C, Single-Ended, 2 μs TaD, VREF+ = 3V, VREF- = Vss |      |                                                   |      |      |      |       |                                                                                |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------------|--|--|--|

| Param<br>No.                                                                                                                     | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                                     |  |  |  |

| AD01                                                                                                                             | Nr   | Resolution                                        | _    | _    | 10   | bit   |                                                                                |  |  |  |

| AD02                                                                                                                             | EIL  | Integral Error                                    | —    |      | ±1.7 | LSb   | VREF = 3.0V                                                                    |  |  |  |

| AD03                                                                                                                             | Edl  | Differential Error                                | —    |      | ±1   | LSb   | No missing codes, VREF = 3.0V                                                  |  |  |  |

| AD04                                                                                                                             | EOFF | Offset Error                                      | _    | —    | ±2.5 | LSb   | VREF = 3.0V                                                                    |  |  |  |

| AD05                                                                                                                             | Egn  | Gain Error                                        | _    | —    | ±2.0 | LSb   | VREF = 3.0V                                                                    |  |  |  |

| AD06                                                                                                                             | Vref | Reference Voltage                                 | 1.8  |      | Vdd  | V     | VREF = (VREF+ – VREF-)                                                         |  |  |  |

| AD07                                                                                                                             | VAIN | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                                |  |  |  |

| AD08                                                                                                                             | Zain | Recommended Impedance of<br>Analog Voltage Source | -    | —    | 10   | kΩ    | Can go higher if external 0.01 $\mu\text{F}$ capacitor is present on input pin |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF+ pin, VDD pin or FVR, whichever is selected as reference input.

- 4: See Section 37.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

### TABLE 36-16: ADC CONVERSION REQUIREMENTS

| Standar      | Standard Operating Conditions (unless otherwise stated) |                                                                 |      |                 |      |       |                                        |  |  |  |

|--------------|---------------------------------------------------------|-----------------------------------------------------------------|------|-----------------|------|-------|----------------------------------------|--|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                                                  | Min. | Тур†            | Max. | Units | Conditions                             |  |  |  |

| AD130*       | TAD                                                     | ADC Clock Period (TADC)                                         | 1.0  | —               | 9.0  | μS    | Fosc-based                             |  |  |  |