Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 2x5b, 2x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1769-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

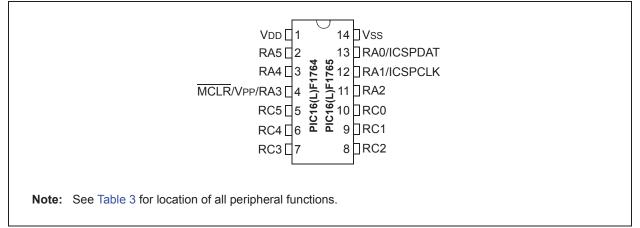

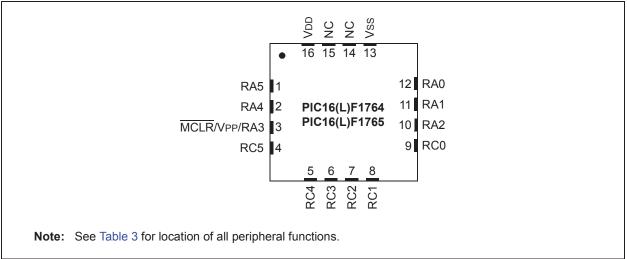

#### **PIN DIAGRAMS**

#### FIGURE 2: 16-PIN QFN (4x4)

|                |                | R/P-1                                  | R/P-1                | R/P-1              | R/P-1               | R/P-1         | R/P-1         |  |

|----------------|----------------|----------------------------------------|----------------------|--------------------|---------------------|---------------|---------------|--|

|                |                | LVP <sup>(1)</sup>                     | DEBUG <sup>(2)</sup> | LPBOR              | BORV <sup>(3)</sup> | STVREN        | PLLEN         |  |

|                |                | bit 13                                 | •                    |                    |                     |               | bit 8         |  |

|                |                |                                        |                      |                    |                     |               |               |  |

| R/P-1          | U-1            | U-1                                    | U-1                  | U-1                | R/P-1               | R/P-1         | R/P-1         |  |

| ZCD            |                | _                                      | _                    |                    | PPS1WAY             | WRT-          | <1:0>         |  |

| bit 7          | •              | •                                      | •                    |                    |                     |               | bit 0         |  |

|                |                |                                        |                      |                    |                     |               |               |  |

| Legend:        |                |                                        |                      |                    |                     |               |               |  |

| R = Readab     | ole bit        | P = Program                            | nable bit            | U = Unimpler       | nented bit, read    | as '1'        |               |  |

| '0' = Bit is c | leared         | '1' = Bit is set                       |                      | -n = Value wh      | en blank or afte    | er Bulk Erase |               |  |

|                |                |                                        |                      |                    |                     |               |               |  |

| bit 13         | LVP: Low-V     | oltage Program                         | ning Enable bit      | (1)                |                     |               |               |  |

|                |                | w-Voltage Progra                       |                      |                    |                     |               |               |  |

|                |                | gh-voltage on M                        |                      | sed for program    | nming               |               |               |  |

| bit 12         |                | -Circuit Debugge                       |                      |                    |                     |               | (O            |  |

|                |                | Circuit Debugge<br>Circuit Debugge     |                      |                    |                     |               |               |  |

| bit 11         |                | w-Power BOR E                          |                      | or orreation to    |                     |               | 00009901      |  |

|                |                | w-Power Brown-                         |                      | sabled             |                     |               |               |  |

|                | 0 = On Lo      | w-Power Brown-                         | out Reset is en      | abled              |                     |               |               |  |

| bit 10         | BORV: Brow     | wn-out Reset Vo                        | tage Selection       | bit <sup>(3)</sup> |                     |               |               |  |

|                |                | own-out Reset V                        |                      |                    |                     |               |               |  |

|                |                | own-out Reset V                        | •                    | •                  | s selected          |               |               |  |

| bit 9          |                | Stack Overflow/U                       |                      |                    |                     |               |               |  |

|                |                | ack Overflow or l<br>ack Overflow or l |                      |                    | set                 |               |               |  |

| bit 8          |                | L Enable bit                           |                      |                    |                     |               |               |  |

|                |                | PLL is enabled                         |                      |                    |                     |               |               |  |

|                | 0 = Off 4x     | PLL is disabled                        |                      |                    |                     |               |               |  |

| bit 7          | ZCD: ZCD I     | Enable bit                             |                      |                    |                     |               |               |  |

|                |                | D is disabled, Z                       |                      | bled by setting    | the ZCDSEN b        | it of ZCDCON  |               |  |

|                |                | D is always ena                        |                      |                    |                     |               |               |  |

| bit 6-3        | -              | ented: Read as '                       |                      |                    |                     |               |               |  |

| bit 2          |                | PPSLOCK Bit O                          |                      |                    |                     |               |               |  |

|                |                | e PPSLOCK bit<br>PSLOCK is set, a      |                      |                    |                     |               | (ecuted; once |  |

|                |                | e PPSLOCK bit                          | -                    | -                  |                     |               | g sequence is |  |

|                |                | ecuted)                                |                      |                    |                     |               |               |  |

| Note 1: 7      | he LVP bit car | not be program                         | ned to '0' when      | Programming        | mode is entere      | ed via LVP.   |               |  |

|                |                |                                        |                      |                    |                     |               |               |  |

|                |                | programmers. Fo                        |                      |                    |                     |               |               |  |

| •              |                |                                        |                      |                    |                     |               |               |  |

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

**3:** See VBOR parameter for specific trip point voltages.

| R-1/q                 | R-0/q                                                                                             | R-q/q                                            | R-0/q            | R-0/q           | R-q/q              | R-0/0            | R-0/q        |  |

|-----------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|-----------------|--------------------|------------------|--------------|--|

| SOSCR                 | PLLR                                                                                              | OSTS                                             | HFIOFR           | HFIOFL          | MFIOFR             | LFIOFR           | HFIOFS       |  |

| bit 7                 |                                                                                                   |                                                  |                  |                 |                    |                  |              |  |

|                       |                                                                                                   |                                                  |                  |                 |                    |                  |              |  |

| Legend:               |                                                                                                   |                                                  |                  |                 |                    |                  |              |  |

| R = Readable          | bit                                                                                               | W = Writable                                     | bit              | q = Condition   | al                 |                  |              |  |

| u = Bit is unch       | anged                                                                                             | x = Bit is unkr                                  | nown             |                 | mented bit, read   |                  |              |  |

| '1' = Bit is set      |                                                                                                   | '0' = Bit is cle                                 | ared             | -n/n = Value    | at POR and BO      | R/Value at all o | other Resets |  |

| hit 7                 | COCCD: Coo                                                                                        | andon ( Oppillo                                  | ar Doody bit     |                 |                    |                  |              |  |

| bit 7                 | If T10SCEN                                                                                        | ondary Oscillat<br>– 1 ·                         | IOF Ready DIL    |                 |                    |                  |              |  |

|                       |                                                                                                   | $\underline{-}$ $\underline{-}$ ry oscillator is | readv            |                 |                    |                  |              |  |

|                       |                                                                                                   | ry oscillator is                                 |                  |                 |                    |                  |              |  |

|                       | If T1OSCEN                                                                                        |                                                  |                  |                 |                    |                  |              |  |

|                       |                                                                                                   | ry clock source                                  | e is always rea  | dy              |                    |                  |              |  |

| bit 6                 | PLLR 4x PLL                                                                                       | 2                                                |                  |                 |                    |                  |              |  |

|                       | 1 = 4x PLL is<br>0 = 4x PLL is                                                                    |                                                  |                  |                 |                    |                  |              |  |

| bit 5                 |                                                                                                   | ator Start-up Ti                                 | mer Status bit   |                 |                    |                  |              |  |

|                       |                                                                                                   |                                                  |                  | FOSC<2:0> b     | oits of the Config | guration Words   |              |  |

|                       |                                                                                                   | from an interna                                  |                  |                 |                    | 5                |              |  |

| bit 4                 | HFIOFR: Hig                                                                                       | h-Frequency Ir                                   | nternal Oscillat | or Ready bit    |                    |                  |              |  |

|                       | 1 = HFINTOS                                                                                       |                                                  |                  |                 |                    |                  |              |  |

| 1.10                  |                                                                                                   | SC is not ready                                  |                  |                 |                    |                  |              |  |

| bit 3                 | •                                                                                                 | n-Frequency In                                   |                  | or Locked bit   |                    |                  |              |  |

|                       | <ul> <li>1 = HFINTOSC is at least 2% accurate</li> <li>0 = HFINTOSC is not 2% accurate</li> </ul> |                                                  |                  |                 |                    |                  |              |  |

| bit 2                 |                                                                                                   | dium Frequenc                                    |                  | illator Ready b | it                 |                  |              |  |

|                       | 1 = MFINTOSC is ready                                                                             |                                                  |                  |                 |                    |                  |              |  |

|                       | 0 = MFINTOSC is not ready                                                                         |                                                  |                  |                 |                    |                  |              |  |

| bit 1                 | LFIOFR: Low-Frequency Internal Oscillator Ready bit                                               |                                                  |                  |                 |                    |                  |              |  |

| 1 = LFINTOSC is ready |                                                                                                   |                                                  |                  |                 |                    |                  |              |  |

| hit 0                 | 0 = LFINTOSC is not ready                                                                         |                                                  |                  |                 |                    |                  |              |  |

| bit 0                 | HFIOFS: High-Frequency Internal Oscillator Stable bit<br>1 = HFINTOSC is at least 0.5% accurate   |                                                  |                  |                 |                    |                  |              |  |

|                       |                                                                                                   | SC is at least 0<br>SC is not 0.5%               |                  |                 |                    |                  |              |  |

|                       |                                                                                                   |                                                  |                  |                 |                    |                  |              |  |

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| R/W-0/0          | R/W-0/0                                  | R/W-0/0                      | U-0                    | R/W-0/0                 | R/W-0/0             | R/W-0/0             | R/W-0/0               |

|------------------|------------------------------------------|------------------------------|------------------------|-------------------------|---------------------|---------------------|-----------------------|

| OSFIE            | C2IE                                     | C1IE                         | _                      | BCL1IE                  | C4IE <sup>(1)</sup> | C3IE <sup>(1)</sup> | CCP2IE <sup>(1)</sup> |

| bit 7            |                                          |                              |                        | ·                       |                     |                     | bit 0                 |

| Lonordi          |                                          |                              |                        |                         |                     |                     |                       |

| Legend:          | 1.11                                     |                              |                        |                         |                     |                     |                       |

| R = Readable     |                                          | W = Writable k               |                        |                         |                     |                     |                       |

| u = Bit is uncl  | •                                        | x = Bit is unkn              |                        |                         | mented bit, read    |                     |                       |

| '1' = Bit is set |                                          | '0' = Bit is clea            | red                    | -n/n = Value a          | at POR and BO       | R/Value at all o    | other Resets          |

| bit 7            | <b>OSFIE:</b> Osci                       | llator Fail Interru          | pt Enable b            | it                      |                     |                     |                       |

|                  |                                          | the Oscillator fa            |                        |                         |                     |                     |                       |

|                  | 0 = Disables                             | s the Oscillator fa          | ail interrupt          |                         |                     |                     |                       |

| bit 6            | C2IE: Compa                              | arator C2 Interru            | pt Enable b            | t                       |                     |                     |                       |

|                  |                                          | the Comparator               |                        |                         |                     |                     |                       |

|                  |                                          | the Comparato                |                        |                         |                     |                     |                       |

| bit 5            |                                          | arator C1 Interru            |                        |                         |                     |                     |                       |

|                  |                                          | the Comparator               |                        |                         |                     |                     |                       |

|                  |                                          | the Comparato                |                        | Dt                      |                     |                     |                       |

| bit 4            | •                                        | nted: Read as '0             |                        |                         |                     |                     |                       |

| bit 3            |                                          | SP Bus Collision             |                        |                         |                     |                     |                       |

|                  |                                          | the MSSP bus of the MSSP bus |                        |                         |                     |                     |                       |

| bit 2            | C4IE: TMR6                               | to T6PR Match                | Interrupt En           | able bit <sup>(1)</sup> |                     |                     |                       |

|                  | 1 = Enables                              | the Comparator               | C4 interrup            | t                       |                     |                     |                       |

|                  | 0 = Disables the Comparator C4 interrupt |                              |                        |                         |                     |                     |                       |

| bit 1            | C3IE: TMR4                               | to T4PR Match                | Interrupt En           | able bit <sup>(1)</sup> |                     |                     |                       |

|                  | 1 = Enables the Comparator C3 interrupt  |                              |                        |                         |                     |                     |                       |

|                  | 0 = Disables the Comparator C3 interrupt |                              |                        |                         |                     |                     |                       |

| bit 0            | CCP2IE: CC                               | P2 Interrupt Ena             | ble bit <sup>(1)</sup> |                         |                     |                     |                       |

|                  |                                          | the CCP2 interr              |                        |                         |                     |                     |                       |

|                  | 0 = Disables                             | the CCP2 inter               | rupt                   |                         |                     |                     |                       |

| Note 1: Pl       | C16(L)F1768/9                            | onlv.                        |                        |                         |                     |                     |                       |

|                  |                                          |                              |                        |                         |                     |                     |                       |

#### **REGISTER 7-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2**

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| REGISTER 10-6: PMCON2 | : PROGRAM MEMORY | CONTROL 2 REGISTER |

|-----------------------|------------------|--------------------|

|-----------------------|------------------|--------------------|

| W-0/0            | W-0/0  | W-0/0                                                                      | W-0/0       | W-0/0          | W-0/0            | W-0/0    | W-0/0 |

|------------------|--------|----------------------------------------------------------------------------|-------------|----------------|------------------|----------|-------|

|                  |        | Prog                                                                       | gram Memory | Control Regist | er 2             |          |       |

| bit 7            |        |                                                                            |             |                |                  |          | bit 0 |

|                  |        |                                                                            |             |                |                  |          |       |

| Legend:          |        |                                                                            |             |                |                  |          |       |

| R = Readable b   | it     | W = Writable I                                                             | bit         |                |                  |          |       |

| S = Bit can only | be set | x = Bit is unkn                                                            | iown        | U = Unimpler   | nented bit, read | l as '0' |       |

| '1' = Bit is set |        | '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets |             |                |                  |          |       |

#### bit 7-0 Program Memory Control 2: Flash Memory Unlock Pattern bits

To unlock writes, 55h must be written first, followed by AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

**TABLE 10-3**: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7                             | Bit 6           | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Register<br>on Page |

|--------|-----------------------------------|-----------------|--------|-------|-------|--------|-------|-------|---------------------|

| INTCON | GIE                               | PEIE            | TMR0IE | INTE  | IOCIE | TMR0IF | INTF  | IOCIF | 101                 |

| PMCON1 | (1)                               | CFGS            | LWLO   | FREE  | WRERR | WREN   | WR    | RD    | 132                 |

| PMCON2 | Program Memory Control Register 2 |                 |        |       |       |        |       | 133   |                     |

| PMADRL |                                   | PMADRL<7:0>     |        |       |       |        |       | 131   |                     |

| PMADRH | (1)                               | (1) PMADRH<6:0> |        |       |       |        |       | 131   |                     |

| PMDATL | PMDATL<7:0>                       |                 |        |       |       |        | 130   |       |                     |

| PMDATH | — — PMDATH<5:0>                   |                 |        |       |       |        | 130   |       |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory. Note 1: Unimplemented, read as '1'.

TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|----------|---------|---------------------|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO      | CLKOUTEN | BOREN    | V<1:0>   | _       | 62                  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | F        | OSC<2:0> |         | 63                  |

| CONFIG2 | 13:8 | _       | —       | LVP      | DEBUG     | LPBOR    | BORV     | STVREN   | PLLEN   | 65                  |

| CONFIGZ | 7:0  | ZCD     |         |          |           | _        | PPS1WAY  | WRT      | <1:0>   |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

#### 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- **Note 1:** When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### **FIGURE 19-4**: ANALOG INPUT MODEL

#### 22.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 22-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| TABLE 22-4: TIM | IER1 GATE | SOURCES |

|-----------------|-----------|---------|

|-----------------|-----------|---------|

| T1GSS<1:0> | Timer1 Gate Source                                                        |

|------------|---------------------------------------------------------------------------|

| 00         | Timer1 Gate Pin                                                           |

| 01         | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 10         | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 11         | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

#### 22.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 22.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 22.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information, see Section 19.4.1 "Comparator Output Synchronization".

#### 22.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information, see Section 19.4.1 "Comparator Output Synchronization".

#### 22.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 22-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

## 22.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 22-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 22-6 for timing details.

#### 22.6.5 TIMER1 GATE VALUE STATUS

When Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 22.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

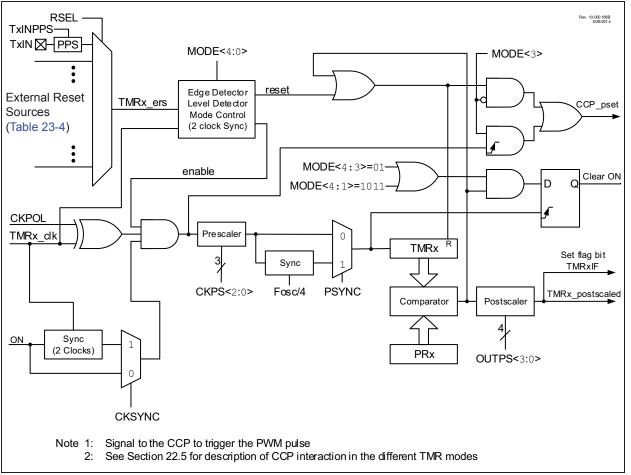

## 23.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control Start, Run, Freeze and Reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control, such as pulse density modulation, are possible by combining the operation of these timers with other internal peripherals, such as the comparators and CCP modules. Features of the timer include:

- 8-Bit Timer register

- 8-Bit Period register

- · Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- · Selectable synchronous/asynchronous operation

- · Alternate clock sources

- · Interrupt-on-period

- Three modes of operation:

- Free-Running Period

- One-Shot

- Monostable

See Figure 23-1 for a block diagram of Timer2. See Figure 23-2 for the clock source block diagram.

**Note:** Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4 and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to T2PR apply as well to T4PR and T6PR.

#### FIGURE 23-1: TIMER2 BLOCK DIAGRAM

#### 23.6.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode, except the TMRx\_ers external signal can also gate the timer. When used with the CCP, the gating extends the PWM period. If the timer is stopped when the PWM output is high, then the duty cycle is also extended.

When MODE<4:0> = 00001, then the timer is stopped when the external signal is high. When MODE<4:0> = 00010, then the timer is stopped when the external signal is low.

Figure 23-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

|                   | Rev. 19-00 1988<br>5/30/2014                           |

|-------------------|--------------------------------------------------------|

| MODE              | 0600001                                                |

| TMRx_dk           |                                                        |

| TMRx_ers          |                                                        |

| PRx               | 5                                                      |

| TMRx              | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

| TMRx_postscaled   |                                                        |

| PWM Duty<br>Cycle | 3                                                      |

| PWM Output        |                                                        |

| Name                   | Bit 7                                        | Bit 6                | Bit 5                  | Bit 4    | Bit 3      | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |  |

|------------------------|----------------------------------------------|----------------------|------------------------|----------|------------|------------|--------|--------|---------------------|--|

| CCP1CON                | EN                                           | OE                   | OUT                    | FMT      |            | MODE       | =<3:0> |        | 256                 |  |

| CCP2CON <sup>(2)</sup> | EN                                           | OE                   | DE OUT FMT MODE<3:0>   |          |            |            |        |        | 256                 |  |

| INTCON                 | GIE                                          | PEIE                 | TMR0IE                 | INTE     | IOCIE      | TMR0IF     | INTF   | IOCIF  | 101                 |  |

| PIE1                   | TMR1GIE                                      | ADIE                 | RCIE                   | TXIE     | SSP1IE     | CCP1IE     | TMR2IE | TMR1IE | 102                 |  |

| PIR1                   | TMR1GIF                                      | ADIF                 | RCIF                   | TXIF     | SSP1IF     | CCP1IF     | TMR2IF | TMR1IF | 105                 |  |

| T2PR                   | Timer2 Module Period Register                |                      |                        |          |            |            |        |        |                     |  |

| TMR2                   | Holding Register for the 8-Bit TMR2 Register |                      |                        |          |            |            |        |        | 227*                |  |

| T2CON                  | ON                                           | CKPS<2:0> OUTPS<3:0> |                        |          |            |            |        |        | 244                 |  |

| T2CLKCON               | —                                            | _                    | — — — CS<3:0>          |          |            |            |        |        | 243                 |  |

| T2RST                  |                                              | _                    | — — RSEL<3:0>          |          |            |            |        |        | 246                 |  |

| T2HLT                  | PSYNC                                        | CKPOL                | CKPOL CKSYNC MODE<4:0> |          |            |            |        |        |                     |  |

| T4PR                   | Timer4 Mod                                   | lule Period R        | legister               |          |            |            |        |        | 227*                |  |

| TMR4                   | Holding Reg                                  | gister for the       | 8-Bit TMR4 I           | Register |            |            |        |        | 227*                |  |

| T4CON                  | ON                                           | (                    | CKPS<2:0>              |          |            | OUTPS<3:0> |        |        |                     |  |

| T4CLKCON               | —                                            | _                    | —                      |          |            | CS<        | :3:0>  |        | 243                 |  |

| T4RST                  |                                              | _                    |                        |          |            | RSEL       | <3:0>  |        | 246                 |  |

| T4HLT                  | PSYNC                                        | CKPOL                | CKSYNC                 |          | •          | MODE<4:0   | >      |        | 245                 |  |

| T6PR                   | Timer6 Mod                                   | lule Period R        | legister               |          |            |            |        |        | 227*                |  |

| TMR6                   | Holding Reg                                  | gister for the       | 8-Bit TMR6 I           | Register |            |            |        |        | 227*                |  |

| T6CON                  | ON                                           |                      | CKPS<2:0>              |          | OUTPS<3:0> |            |        |        | 244                 |  |

| T6CLKCON               | —                                            |                      |                        |          | CS<3:0>    |            |        |        | 243                 |  |

| T6RST                  | —                                            | —                    | —                      | —        |            | RSEL       | <3:0>  |        | 246                 |  |

| T6HLT                  | PSYNC                                        | CKPOL                | CKSYNC                 |          | •          | MODE<4:0   | >      |        | 245                 |  |

| TABLE 23-5:         SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2 |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Timer2 module.

\* Page provides register information.

Note 1: PIC16(L)F1768/9 only.

#### 24.4 CCP/PWM Clock Selection

The PIC16(L)F1764/5/8/9 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2/4/6), the PWM mode on the CCP and PWM modules can use any of these timers.

The CCPTMRS register is used to select which timer is used.

## 24.4.1 USING THE TMR2/4/6 WITH THE CCP MODULE

This device has a new version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than older parts. Refer to **Section 23.6 "Operation Examples"** for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the Fosc/4 clock source selected.

#### 24.4.2 PWM PERIOD

The PWM period is specified by the T2PR/T4PR/T6PR register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

#### EQUATION 24-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc.

When TMR2/4/6 is equal to its respective T2PR/T4PR/T6PR register, the following three events occur on the next increment cycle:

- TMR2/4/6 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from the CCPRxH:CCPRxL pair into the internal 10-bit latch.

Note: The Timer postscaler (see Figure 24-1) is not used in the determination of the PWM frequency.

#### 24.4.3 PWM DUTY CYCLE

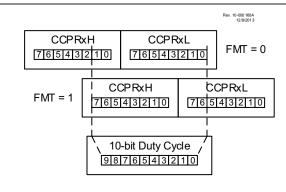

The PWM duty cycle is specified by writing a 10-bit value to two registers: the CCPRxH:CCPRxL register pair. Where the particular bits go is determined by the FMT bit of the CCPxCON register. If FMT = 0, the two Most Significant bits of the duty cycle value should be written to bits<1:0> of the CCPRxH register and the remaining eight bits to the CCPRxL register. If FMT = 1, the Least Significant two bits of the duty cycle should be written to bits<7:6> of the CCPRxL register and the Most Significant eight bits to the CCPRxL register and the Most Significant eight bits to the CCPRxL register. This is illustrated in Figure 24-4. These bits can be written at any time. The duty cycle value is not latched into the internal latch until after the period completes (i.e., a match between T2PR/T4PR/T6PR and TMR2/4/6 registers occurs).

Equation 24-2 is used to calculate the PWM pulse width. Equation 24-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 24-2: PULSE WIDTH

#### EQUATION 24-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL)}{4(PRx+1)}$

The PWM Duty Cycle registers are double-buffered for glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the internal buffer register, then the CCPx pin is cleared (see Figure 24-3).

#### FIGURE 24-4: CCPx DUTY CYCLE ALIGNMENT

### 24.5 Register Definitions: CCP Control

#### REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-0/0          | U-0                                                                                                          | R-x                            | R/W-0/0          | R/W-0/0                         | R/W-0/0          | R/W-0/0         | R/W-0/0      |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|---------------------------------|------------------|-----------------|--------------|--|--|--|

| EN               | —                                                                                                            | OUT                            | FMT              |                                 | MODE             | =<3:0>          |              |  |  |  |

| bit 7            |                                                                                                              |                                |                  |                                 |                  |                 | bit 0        |  |  |  |

|                  |                                                                                                              |                                |                  |                                 |                  |                 |              |  |  |  |

| Legend:          |                                                                                                              |                                |                  |                                 |                  |                 |              |  |  |  |

| R = Readable     | bit                                                                                                          | W = Writable                   | bit              |                                 |                  |                 |              |  |  |  |

| u = Bit is uncha | anged                                                                                                        | x = Bit is unkr                | nown             |                                 | nented bit, read |                 |              |  |  |  |

| '1' = Bit is set |                                                                                                              | '0' = Bit is cle               | ared             | -n/n = Value a                  | at POR and BC    | R/Value at all  | other Reset  |  |  |  |

|                  |                                                                                                              |                                |                  |                                 |                  |                 |              |  |  |  |

| bit 7            |                                                                                                              | odule Enable b                 | it               |                                 |                  |                 |              |  |  |  |

|                  | 1 = CCPx is $0 = CCPx$ is                                                                                    |                                |                  |                                 |                  |                 |              |  |  |  |

| bit 6            |                                                                                                              | ited: Read as '                | 0'               |                                 |                  |                 |              |  |  |  |

| bit 5            | -                                                                                                            | Dutput Data bit                |                  |                                 |                  |                 |              |  |  |  |

| bit 4            |                                                                                                              | (Pulse-Width)                  |                  |                                 |                  |                 |              |  |  |  |

| DIL 4            |                                                                                                              | , ,                            | •                |                                 |                  |                 |              |  |  |  |

|                  | <u>If MODE&lt;3:0&gt; = PWM Mode:</u><br>1 = Left-aligned format, CCPRxH<7> is the MSB of the PWM duty cycle |                                |                  |                                 |                  |                 |              |  |  |  |

|                  | 0                                                                                                            |                                |                  | the LSB of the I                |                  |                 |              |  |  |  |

| bit 3-0          | MODE<3:0>:                                                                                                   | CCPx Mode S                    | election bits    |                                 |                  |                 |              |  |  |  |

|                  | 11xx = PWN                                                                                                   | /I mode                        |                  |                                 |                  |                 |              |  |  |  |

|                  | 1011 <b>= Com</b>                                                                                            | pare mode: Pu                  | lse output, cle  | ar TMR1                         |                  |                 |              |  |  |  |

|                  | 1010 = Com                                                                                                   | pare mode: Pu                  | lse output (0 -  | 1-0)                            |                  |                 |              |  |  |  |

|                  |                                                                                                              |                                |                  | compare match                   |                  |                 |              |  |  |  |

|                  | 1000 = Com                                                                                                   | pare mode: Se                  | t output on co   | mpare match; c                  | output is set up | on selection of | this mode    |  |  |  |

|                  | 0111 = Capt                                                                                                  | ure mode: Eve                  | ry 16th rising e | edge                            |                  |                 |              |  |  |  |

|                  |                                                                                                              | ure mode: Eve                  |                  | dge                             |                  |                 |              |  |  |  |

|                  |                                                                                                              | ure mode: Eve<br>ure mode: Eve |                  |                                 |                  |                 |              |  |  |  |

|                  | 0100 <b>- Cap</b> i                                                                                          | ure mode. Eve                  | ry lailing euge  |                                 |                  |                 |              |  |  |  |

|                  |                                                                                                              | ure mode: Eve                  |                  |                                 |                  |                 |              |  |  |  |

|                  |                                                                                                              | pare mode: To                  |                  |                                 |                  |                 |              |  |  |  |

|                  |                                                                                                              |                                |                  | d clear TMR1 c<br>s CCPx module |                  | hackwards co    | mnatibility) |  |  |  |

|                  |                                                                                                              | are/compare/r                  |                  |                                 |                  |                 | mpationity)  |  |  |  |

| R/W/HC-0/0         | R/W-0/0                                                                                                                                                                                                                                | U-0                                                                      | U-0                                          | U-0              | U-0              | U-0              | R/W-0/0              |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------|------------------|------------------|------------------|----------------------|--|--|--|

| LDA <sup>(1)</sup> | LDT <sup>(3)</sup>                                                                                                                                                                                                                     | _                                                                        | _                                            | _                | _                | _                | LDS <sup>(2,3)</sup> |  |  |  |

| bit 7              | l                                                                                                                                                                                                                                      |                                                                          |                                              | 1                |                  |                  | bit 0                |  |  |  |

| Legend:            |                                                                                                                                                                                                                                        |                                                                          |                                              |                  |                  |                  |                      |  |  |  |

| R = Readable       | R = Readable bit W = Writable bit HC = Hardware Clearable bit                                                                                                                                                                          |                                                                          |                                              |                  |                  |                  |                      |  |  |  |

| u = Bit is unch    | nanged                                                                                                                                                                                                                                 | x = Bit is unkn                                                          | own                                          | U = Unimplem     | nented bit, read | as '0'           |                      |  |  |  |

| '1' = Bit is set   |                                                                                                                                                                                                                                        | '0' = Bit is clea                                                        | ared                                         | -n/n = Value a   | t POR and BOF    | R/Value at all o | other Resets         |  |  |  |

|                    | selected<br>0 = Does not<br>$\frac{\text{If LDT} = 0}{1 = \text{Loads the}}$<br>0 = Does not                                                                                                                                           | trigger occurs<br>load buffers, lo<br>e ODO bit, and<br>load buffers, lo | ad has compl<br>OFx, PHx, DC<br>ad has compl | Cx and PRx buff  |                  | ·                |                      |  |  |  |

| bit 6              | <b>LDT:</b> Load Buffer on Trigger bit <sup>(3)</sup><br>1 = Waits for trigger selected by the LDS<1:0> bits to occur before enabling the LDA bit<br>0 = Load triggering is disabled; buffer loads are controlled by the LDA bit alone |                                                                          |                                              |                  |                  |                  |                      |  |  |  |

| bit 5-1            | Unimplemen                                                                                                                                                                                                                             | ted: Read as '0                                                          | )'                                           |                  |                  |                  |                      |  |  |  |

| bit 0              | <b>LDS:</b> Load Tr<br>1 = LD6_trigg<br>0 = LD5_trigg                                                                                                                                                                                  | •                                                                        | elect bit <sup>(2,3)</sup>                   |                  |                  |                  |                      |  |  |  |

| Note 1: Thi        | is bit is cleared                                                                                                                                                                                                                      | by the module                                                            | after a reload                               | operation. It ca | n be cleared in  | software to cle  | ear an existing      |  |  |  |

#### REGISTER 26-5: PWMxLDCON: PWMx RELOAD TRIGGER SOURCE SELECT REGISTER

- **Note 1:** This bit is cleared by the module after a reload operation. It can be cleared in software to clear an existing arming event.

- **2:** The source corresponding to a PWM module's own LDx\_trigger is reserved.

- 3: PIC16(L)F1768/9 only.

#### REGISTER 29-3: OPAXNCHS: OP AMP x NEGATIVE CHANNEL SOURCE SELECT REGISTER

| U-0                                                                    | U-0                       | U-0              | U-0           | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0     |  |  |

|------------------------------------------------------------------------|---------------------------|------------------|---------------|------------------|------------------|----------|-------------|--|--|

| _                                                                      | —                         | —                | _             | NCH<3:0>         |                  |          |             |  |  |

| bit 7                                                                  |                           |                  |               |                  |                  |          | bit 0       |  |  |

|                                                                        |                           |                  |               |                  |                  |          |             |  |  |

| Legend:                                                                |                           |                  |               |                  |                  |          |             |  |  |

| R = Reada                                                              | able bit                  | W = Writable     | bit           |                  |                  |          |             |  |  |

| u = Bit is ι                                                           | unchanged                 | x = Bit is unkn  | iown          | U = Unimplen     | nented bit, read | l as '0' |             |  |  |

| '1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Valu |                           |                  |               |                  |                  |          | ther Resets |  |  |

|                                                                        |                           |                  |               |                  |                  |          |             |  |  |

| bit 7-4                                                                | Unimpleme                 | nted: Read as '  | )'            |                  |                  |          |             |  |  |

| bit 3-0                                                                | NCH<3:0>: (               | Op Amp Invertin  | g Input Chanr | nel Selection bi | its              |          |             |  |  |

|                                                                        |                           | erved; do not us | •             |                  |                  |          |             |  |  |

|                                                                        | •                         | ,                |               |                  |                  |          |             |  |  |

|                                                                        | •                         |                  |               |                  |                  |          |             |  |  |

|                                                                        | •                         |                  |               |                  |                  |          |             |  |  |

|                                                                        |                           | erved; do not us |               |                  |                  |          |             |  |  |

|                                                                        |                           | rammable Ram     |               |                  |                  |          |             |  |  |

|                                                                        |                           | rammable Ram     |               | 'RG1_out         |                  |          |             |  |  |

|                                                                        | 0111 = Rese<br>0110 = FVR | erved. Do not us | e.            |                  |                  |          |             |  |  |

|                                                                        | 0110 <b>– PVR</b>         |                  |               |                  |                  |          |             |  |  |

|                                                                        | 0100 = DAC                | _                |               |                  |                  |          |             |  |  |

|                                                                        | 0011 <b>= DAC</b>         |                  |               |                  |                  |          |             |  |  |

|                                                                        | 0010 = DAC                |                  |               |                  |                  |          |             |  |  |

|                                                                        | 0001 <b>= OPA</b>         |                  |               |                  |                  |          |             |  |  |

|                                                                        | 0000 <b>= OPA</b>         |                  |               |                  |                  |          |             |  |  |

Note 1: PIC16(L)F1768/9 only

| Name                  | Bit 7                        | Bit 6           | Bit 5  | Bit 4       | Bit 3      | Bit 2  | Bit 1      | Bit 0  | Register<br>on Page |

|-----------------------|------------------------------|-----------------|--------|-------------|------------|--------|------------|--------|---------------------|

| ANSELA                | —                            | —               | —      | ANSA4       | —          |        | ANSA<2:0>  |        | 137                 |

| ANSELB <sup>(1)</sup> |                              | ANSB            | <7:4>  |             | —          | —      | —          | —      | 143                 |

| ANSELC                | ANSC<                        | 7:6> <b>(1)</b> | —      | —           |            | ANSC   | <3:0>      |        | 148                 |

| BAUD1CON              | ABDOVF                       | RCIDL           | —      | SCKP        | BRG16      | _      | WUE        | ABDEN  | 442                 |

| INTCON                | GIE                          | PEIE            | TMR0IE | INTE        | IOCIE      | TMR0IF | INTF       | IOCIF  | 101                 |

| PIE1                  | TMR1GIE                      | ADIE            | RCIE   | TXIE        | SSP1IE     | CCP1IE | TMR2IE     | TMR1IE | 102                 |

| PIR1                  | TMR1GIF                      | ADIF            | RCIF   | TXIF        | SSP1IF     | CCP1IF | TMR2IF     | TMR1IF | 105                 |

| RC1REG                | EUSART Receive Data Register |                 |        |             |            |        |            | 436*   |                     |

| RC1STA                | SPEN                         | RX9             | SREN   | CREN        | ADDEN      | FERR   | OERR       | RX9D   | 441                 |

| RxyPPS                | _                            | —               | —      | RxyPPS<4:0> |            |        |            |        |                     |

| SP1BRGL               | BRG<7:0>                     |                 |        |             |            |        |            | 443    |                     |

| SP1BRGH               | BRG<15:8>                    |                 |        |             |            |        | 443        |        |                     |

| TRISA                 | _                            | _               | TRISA  | \<5:4>      | (2)        |        | TRISA<2:0> |        | 136                 |

| TRISB <sup>(1)</sup>  |                              | TRISB           | <7:4>  |             | _          | _      | _          | _      | 142                 |

| TRISC                 | TRISC<                       | 7:6>(1)         |        |             | TRISC<5:0> |        |            |        | 147                 |

| TX1STA                | CSRC                         | TX9             | TXEN   | SYNC        | SENDB      | BRGH   | TRMT       | TX9D   | 440                 |

TABLE 33-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

Note 1: PIC16(L)F1768/9 only.

**2:** Unimplemented, read as '1'.

### 33.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the Internal Oscillator Block (INTOSC) output. However, the INTOSC frequency may drift as VDD or temperature changes and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See Section 5.2.2.3 "Internal Oscillator Frequency Adjustment" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 33.4.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

| R/W-0/0          | R/W-0/0                                    | R/W-0/0                                                               | R/W-0/0                            | R/W-0/0         | R-0/0                                | R-0/0            | R-0/0        |  |  |  |  |

|------------------|--------------------------------------------|-----------------------------------------------------------------------|------------------------------------|-----------------|--------------------------------------|------------------|--------------|--|--|--|--|

| SPEN             | RX9                                        | SREN                                                                  | CREN                               | ADDEN           | FERR                                 | OERR             | RX9D         |  |  |  |  |

| bit 7            | ·                                          |                                                                       |                                    |                 |                                      |                  | bit C        |  |  |  |  |

|                  |                                            |                                                                       |                                    |                 |                                      |                  |              |  |  |  |  |

| Legend:          |                                            |                                                                       |                                    |                 |                                      |                  |              |  |  |  |  |

| R = Readable     | e bit                                      | W = Writable                                                          | bit                                |                 |                                      |                  |              |  |  |  |  |

| u = Bit is uncl  | nanged                                     | x = Bit is unk                                                        | nown                               | U = Unimple     | mented bit, read                     | as '0'           |              |  |  |  |  |

| '1' = Bit is set |                                            | '0' = Bit is cle                                                      | ared                               | -n/n = Value    | at POR and BO                        | R/Value at all o | other Resets |  |  |  |  |

| 1.1.7            |                                            |                                                                       |                                    |                 |                                      |                  |              |  |  |  |  |

| bit 7            |                                            | I Port Enable b                                                       | IT                                 |                 |                                      |                  |              |  |  |  |  |

|                  |                                            | ort is enabled<br>ort is disabled (l                                  | neld in Reset)                     |                 |                                      |                  |              |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R                        | eceive Enable I                                                       | oit                                |                 |                                      |                  |              |  |  |  |  |

|                  |                                            | 9-bit reception<br>8-bit reception                                    |                                    |                 |                                      |                  |              |  |  |  |  |

| bit 5            | SREN: Singl                                | e Receive Enal                                                        | ole bit                            |                 |                                      |                  |              |  |  |  |  |

|                  | <u>Asynchronou</u><br>Don't care.          | <u>is mode:</u>                                                       |                                    |                 |                                      |                  |              |  |  |  |  |