# E·X Renesas Electronics America Inc - <u>R7FS3A17C2A01CLJ#AC0 Datasheet</u>

### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 48MHz                                                                                 |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, MMC/SD, QSPI, SCI, SSIE, SPI, UART/USART, USB      |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 84                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | 8K x 8                                                                                |

| RAM Size                   | 192K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 25x14b; D/A 1x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 100-TFLGA                                                                             |

| Supplier Device Package    | 100-TFLGA (7x7)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs3a17c2a01clj-ac0 |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controller Area Network (CAN)<br>Module | The Controller Area Network (CAN) module provides functionality to receive and transmit data using a message-based protocol between multiple slaves and masters in electromagnetically noisy applications.<br>The CAN module complies with the ISO 11898-1 (CAN 2.0A/CAN 2.0B) standard and supports up to 32 mailboxes, which can be configured for transmission or reception in normal mailbox and FIFO modes. Both standard (11-bit) and extended (29-bit) messaging formats are supported. See section 31, Controller Area Network (CAN) Module in the User's Manual.                                                                                                                                                                                                                                                                                                   |

| USB 2.0 Full-Speed Module (USBFS)       | The USBFS is a USB controller that can operate as a host controller or device controller. The module supports full-speed and low-speed (only for the host controller) transfer as defined in the Universal Serial Bus specification 2.0. The module has an internal USB transceiver and supports all of the transfer types defined in the Universal Serial Bus specification 2.0. The USB has buffer memory for data transfer, providing a maximum of 10 pipes. Pipes 1 to 9 can be assigned any endpoint number based on the peripheral devices used for communication or based on the your system. The MCU supports revision 1.2 of the Battery Charging specification. Because the MCU can be powered at 5 V, the USB LDO regulator provides the internal USB transceiver power supply at 3.3 V. See section 28, USB 2.0 Full-Speed Module (USBFS) in the User's Manual. |

| SD/MMC Host Interface (SDHI)            | The Secure Digital Host Interface (SDHI) and MultiMediaCard (MMC) interface provide the functionality needed to connect a variety of external memory cards to the MCU. The SDHI supports both 1-bit and 4-bit buses for connecting different memory cards that support SD, SDHC, and SDXC formats. When developing host devices that are compliant with the SD specifications, you must comply with the SD Host/Ancillary Product License Agreement (SD HALA).<br>The MMC interface supports 1-bit, 4-bit, and 8-bit MMC buses that provide eMMC 4.51 (JEDEC Standard JESD 84-B451) device access. This interface also provides backward compatibility and support for high-speed SDR transfer modes. See section 36, SD/MMC Host Interface (SDHI) in the User's Manual.                                                                                                    |

Table 1.8Communication interfaces (2 of 2)

### Table 1.9 Analog

| Feature                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-bit A/D Converter (ADC14)            | A 14-bit successive approximation A/D converter is provided. Up to 28 analog input channels are selectable. Temperature sensor output and internal reference voltage are selectable for conversion. The A/D conversion accuracy is selectable from 12-bit and 14-bit conversion making it possible to optimize the tradeoff between speed and resolution in generating a digital value. See section 38, 14-Bit A/D Converter (ADC14) in the User's Manual.                                                                                                                                                                                                                                                                         |

| 12-bit D/A Converter (DAC12)            | The 12-bit D/A converts data and includes an output amplifier. See section 39, 12-Bit D/A Converter (DAC12) in the User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8-bit D/A Converter (DAC8) (for ACMPLP) | The 8-bit D/A converts data and does not include an output amplifier (DAC8). The DAC8 is used only as the reference voltage for ACMPLP. See section 43, 8-Bit D/A Converter (DAC8) in the User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Temperature Sensor (TSN)                | The on-chip temperature sensor determines and monitors the die temperature for reliable operation of the device. The sensor outputs a voltage directly proportional to the die temperature, and the relationship between the die temperature and the output voltage is linear. The output voltage is provided to the ADC14 for conversion and can be further used by the end application. See section 40, Temperature Sensor (TSN) in the User's Manual.                                                                                                                                                                                                                                                                           |

| Low-Power Analog Comparator<br>(ACMPLP) | The analog comparator compares the reference input voltage and analog input voltage. The comparison result can be read through software and also be output externally. The reference input voltage can be selected from an input to the CMPREFi (i = 0, 1) pin, an internal 8-bit D/A converter output, or the internal reference voltage (Vref) generated internally in the MCU. The ACMPLP response speed can be set before starting an operation. Setting the High-speed mode decreases the response delay time, but increases current consumption. Setting the Low-speed mode increases the response delay time, but decreases current consumption. See section 42, Low Power Analog Comparator (ACMPLP) in the User's Manual. |

| Operational Amplifier (OPAMP)           | The operational amplifier amplifies small analog input voltages and outputs the amplified voltages. A total of four differential operational amplifier units with two input pins and one output pin are provided. See section 41, Operational Amplifier (OPAMP) in the User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Feature                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Segment LCD Controller (SLCDC)          | <ul> <li>The SLCDC provides the following functions:</li> <li>Waveform A or B selectable</li> <li>The LCD driver voltage generator can switch between an internal voltage boosting method, a capacitor split method, and an external resistance division method</li> <li>Automatic output of segment and common signals based on automatic display data register read</li> <li>The reference voltage generated when operating the voltage boost circuit can be selected in 16 steps (contrast adjustment)</li> <li>The LCD can be made to blink.</li> <li>See section 48, Segment LCD Controller (SLCDC) in the User's Manual.</li> </ul> |

| Capacitive Touch Sensing Unit<br>(CTSU) | The Capacitive Touch Sensing Unit (CTSU) measures the electrostatic capacitance of the touch sensor. Changes in the electrostatic capacitance are determined by software, which enables the CTSU to detect whether a finger is in contact with the touch sensor. The electrode surface of the touch sensor is usually enclosed with an electrical insulator so that fingers do not come into direct contact with the electrodes. See section 44, Capacitive Touch Sensing Unit (CTSU) in the User's Manual.                                                                                                                               |

### Table 1.11 Data processing

| Feature                                     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Cyclic Redundancy Check (CRC)<br>Calculator | The CRC calculator generates CRC codes to detect errors in the data. The bit order of CRC calculation results can be switched for LSB-first or MSB-first communication. Additionally, various CRC-generating polynomials are available. The snoop function allows monitoring reads from and writes to specific addresses. This function is useful in applications that require CRC code to be generated automatically in certain events, such as monitoring writes to the serial transmit buffer and reads from the serial receive buffer. See section 34, Cyclic Redundancy Check (CRC) Calculator in the User's Manual. |  |  |  |  |

| Data Operation Circuit (DOC)                | The Data Operation Circuit (DOC) compares, adds, and subtracts 16-bit data. See section 45, Data Operation Circuit (DOC) in the User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

### Table 1.12 Security

| Feature                       | Functional description                                                                                                                                                                         |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secure Crypto Engine 5 (SCE5) | <ul> <li>Security algorithm:</li> <li>Symmetric algorithm: AES</li> <li>Other support features:</li> <li>TRNG (True Random Number Generator)</li> <li>Hash-value generation: GHASH.</li> </ul> |

# 2. Electrical Characteristics

Unless otherwise specified, the electrical characteristics of the MCU are defined under the following conditions:

$VCC^{*1} = AVCC0 = VCC\_USB^{*2} = VCC\_USB\_LDO^{*2} = 1.6 \text{ to } 5.5 \text{ V}, \text{VRERH} = \text{VREFH0} = 1.6 \text{ to } AVCC0, \text{VBATT} = 1.6 \text{ to } 3.6 \text{ V}, \text{VSS} = AVSS0 = \text{VREFL} = \text{VREFL0} = \text{VSS}\_USB = 0 \text{ V}, \text{Ta} = \text{T}_{opr}.$

Note 1. The typical condition is set to VCC = 3.3V.

Note 2. When USBFS is not used.

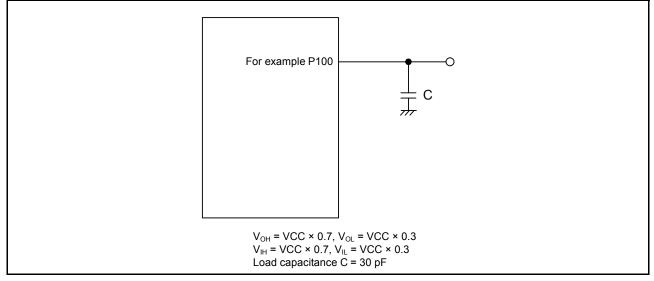

Figure 2.1 shows the timing conditions.

### Figure 2.1 Input or output timing measurement conditions

The measurement conditions of timing specifications in each peripheral are recommended for the best peripheral operation. However, make sure to adjust driving abilities of each pin to meet your conditions.

Each function pin used for the same function must select the same drive ability. If the I/O drive ability of each function pin is mixed, the AC specification of each function is not guaranteed.

Table 2.5

I/O V<sub>IH</sub>, V<sub>IL</sub> (2)

Conditions: VCC = AVCC0 = VCC\_USB = VCC\_USB\_LDO = 1.6 to 2.7 V, VBATT = 1.6 to 3.6 V, VSS = AVSS0 = 0 V

| Parameter                                    |                                                                       | Symbol          | Min                      | Тур | Мах                     | Unit | Test<br>conditions |

|----------------------------------------------|-----------------------------------------------------------------------|-----------------|--------------------------|-----|-------------------------|------|--------------------|

| 00                                           | RES, NMI                                                              | V <sub>IH</sub> | VCC × 0.8                | -   | -                       | V    | -                  |

| input voltage                                | Peripheral input pins                                                 | V <sub>IL</sub> | -                        | -   | VCC × 0.2               |      |                    |

|                                              |                                                                       | $\Delta V_T$    | VCC × 0.01               | -   | -                       |      |                    |

| Input voltage                                | 5V-tolerant ports*1                                                   | V <sub>IH</sub> | VCC × 0.8                | -   | 5.8                     |      |                    |

| (except for<br>Schmitt trigger<br>input pin) |                                                                       | V <sub>IL</sub> | -                        | -   | VCC × 0.2               |      |                    |

|                                              | P914, P915                                                            | V <sub>IH</sub> | VCC_USB × 0.8            | -   | VCC_USB + 0.3           | _    |                    |

|                                              |                                                                       | V <sub>IL</sub> | -                        | -   | VCC_USB × 0.2           |      |                    |

|                                              | P000 to P015                                                          | V <sub>IH</sub> | AVCC0 × 0.8              | -   | -                       |      |                    |

|                                              |                                                                       | V <sub>IL</sub> | -                        | -   | AVCC0 × 0.2             |      |                    |

|                                              | EXTAL                                                                 | V <sub>IH</sub> | VCC × 0.8                | -   | -                       |      |                    |

|                                              | D00 to D15<br>Input ports pins except for<br>P000 to P015, P914, P915 | V <sub>IL</sub> | -                        | -   | VCC × 0.2               |      |                    |

| When V <sub>BATT</sub>                       | P402, P403, P404                                                      | V <sub>IH</sub> | V <sub>BATT</sub> × 0.8  | -   | V <sub>BATT</sub> + 0.3 |      |                    |

| power supply is<br>selected                  |                                                                       | V <sub>IL</sub> | -                        | -   | V <sub>BATT</sub> × 0.2 |      |                    |

|                                              |                                                                       | $\Delta V_T$    | V <sub>BATT</sub> × 0.01 | -   | -                       |      |                    |

Note 1. P205, P206, P400 to P404, P407, P408, P511, P512 (total 11 pins)

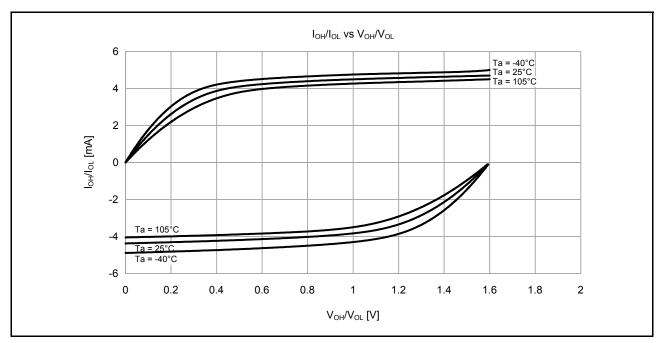

Figure 2.8 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> temperature characteristics at VCC = 1.6 V when middle drive output is selected (reference data)

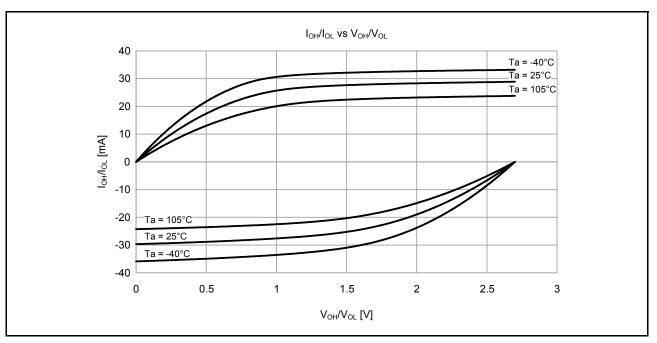

Figure 2.9 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> temperature characteristics at VCC = 2.7 V when middle drive output is selected (reference data)

RENESAS

#### Table 2.11 Operating and standby current (1) (2 of 2)

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter                       |                                        |             |                                                                                         |                   | Symbol          | Typ* <sup>10</sup> | Max   | Unit | Test<br>conditions |

|---------------------------------|----------------------------------------|-------------|-----------------------------------------------------------------------------------------|-------------------|-----------------|--------------------|-------|------|--------------------|

| Supply<br>current* <sup>1</sup> | Low-speed mode <sup>*3</sup>           | Normal mode | All peripheral clocks disabled, while (1) code executing from flash*5                   | ICLK = 1 MHz      | I <sub>CC</sub> | 0.4                | -     | mA   | *7                 |

|                                 |                                        |             | All peripheral clocks<br>disabled, CoreMark code<br>executing from flash* <sup>5</sup>  | ICLK = 1 MHz      |                 | 0.6                | -     |      |                    |

|                                 |                                        |             | All peripheral clocks<br>enabled, while (1) code<br>executing from flash* <sup>5</sup>  | ICLK = 1 MHz      |                 | 1.1                | -     |      | *8                 |

|                                 |                                        |             | All peripheral clocks<br>enabled, code executing<br>from SRAM* <sup>5</sup>             | ICLK = 1 MHz      |                 | -                  | 2.6   |      |                    |

|                                 |                                        | Sleep mode  | All peripheral clocks disabled*5                                                        | ICLK = 1 MHz      |                 | 0.3                | -     | -    | *7                 |

|                                 |                                        |             | All peripheral clocks enabled*5                                                         | ICLK = 1 MHz      |                 | 1.0                | -     |      | *8                 |

|                                 | Low-voltage mode <sup>*3</sup>         | Normal mode | All peripheral clocks<br>disabled, while (1) code<br>executing from flash* <sup>5</sup> | ICLK = 4 MHz      | Icc             | 2.2                | -     | mA   | *7                 |

|                                 |                                        |             | All peripheral clocks<br>disabled, CoreMark code<br>executing from flash*5              | ICLK = 4 MHz      |                 | 3.3                | -     |      |                    |

|                                 |                                        |             | All peripheral clocks<br>enabled, while (1) code<br>executing from flash*5              | ICLK = 4 MHz      |                 | 3.7                | -     |      | *8                 |

|                                 |                                        |             | All peripheral clocks<br>enabled, code executing<br>from SRAM* <sup>5</sup>             | ICLK = 4 MHz      |                 | -                  | 10.0  |      |                    |

|                                 |                                        | Sleep mode  | All peripheral clocks disabled*5                                                        | ICLK = 4 MHz      |                 | 1.7                | -     |      | *7                 |

|                                 |                                        |             | All peripheral clocks enabled*5                                                         | ICLK = 4 MHz      |                 | 3.2                | -     |      | *8                 |

|                                 | Subosc-<br>speed<br>mode <sup>*4</sup> | Normal mode | All peripheral clocks<br>disabled, while (1) code<br>executing from flash*5             | ICLK = 32.768 kHz | Icc             | 10.0               | -     | μA   | *8                 |

|                                 |                                        |             | All peripheral clocks<br>enabled, while (1) code<br>executing from flash*5              | ICLK = 32.768 kHz |                 | 17.9               | -     |      |                    |

|                                 |                                        |             | All peripheral clocks<br>enabled, code executing<br>from SRAM* <sup>5</sup>             | ICLK = 32.768 kHz |                 | -                  | 154.0 |      |                    |

|                                 |                                        | Sleep mode  | All peripheral clocks disabled*5                                                        | ICLK = 32.768 kHz |                 | 6.3                | -     |      |                    |

|                                 |                                        |             | All peripheral clocks enabled*5                                                         | ICLK = 32.768 kHz |                 | 14.0               | -     |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. The clock source is HOCO.

Note 3.The clock source is MOCO.Note 4.The clock source is the sub-clock oscillator.

Note 5. This does not include BGO operation.

Note 6. This is the increase for programming or erasure of the flash memory for data storage during program execution.

Note 7.

FCLK, BCLK, PCLKA, PCLKB, PCLKC, and PCLKD are set to divided by 64.

Note 8.

FCLK, BCLK, PCLKA, PCLKB, PCLKC, and PCLKD are the same frequency as that of ICLK.

Note 9.

FCLK, BCLK, and PCLKB are set to divided by 2 and PCLKA, PCLKC, and PCLKD are the same frequency as that of ICLK.

Note 10. VCC = 3.3 V.

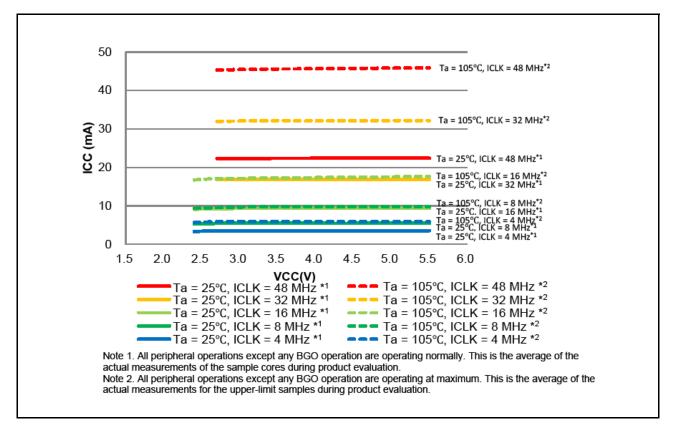

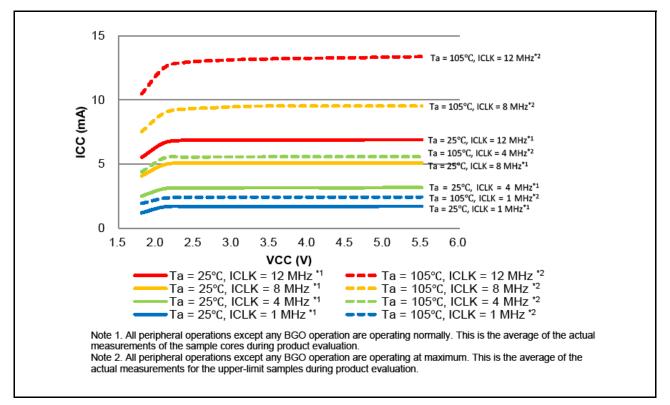

Figure 2.17 Voltage dependency in high-speed mode (reference data)

Figure 2.18 Voltage dependency in middle-speed mode (reference data)

RENESAS

## 2.3 AC Characteristics

### 2.3.1 Frequency

# Table 2.17Operation frequency value in high-speed operating modeConditions: VCC = AVCC0 = 2.4 to 5.5 V

| Parameter |                                       | Symbol       | Symbol Min | Тур      | Max* <sup>5</sup> | Unit |     |

|-----------|---------------------------------------|--------------|------------|----------|-------------------|------|-----|

| Operation | System clock (ICLK)*4                 | 2.7 to 5.5 V | f          | 0.032768 | -                 | 48   | MHz |

| frequency |                                       | 2.4 to 2.7 V |            | 0.032768 | -                 | 16   |     |

|           | FlashIF clock (FCLK)*1, *2, *4        | 2.7 to 5.5 V |            | 0.032768 | -                 | 32   |     |

|           |                                       | 2.4 to 2.7 V |            | 0.032768 | -                 | 16   |     |

|           | Peripheral module clock (PCLKA)*4     | 2.7 to 5.5 V |            | -        | -                 | 48   |     |

|           |                                       | 2.4 to 2.7 V |            | -        | -                 | 16   |     |

|           | Peripheral module clock (PCLKB)*4     | 2.7 to 5.5 V |            | -        | -                 | 32   |     |

|           |                                       | 2.4 to 2.7 V |            | -        | -                 | 16   |     |

|           | Peripheral module clock (PCLKC)*3, *4 | 2.7 to 5.5 V |            | -        | -                 | 64   |     |

|           |                                       | 2.4 to 2.7 V |            | -        | -                 | 16   |     |

|           | Peripheral module clock (PCLKD)*4     | 2.7 to 5.5 V |            | -        | -                 | 64   |     |

|           |                                       | 2.4 to 2.7 V |            | -        | -                 | 16   |     |

|           | External bus clock (BCLK)*4           | 2.7 to 5.5 V |            | -        | -                 | 24   |     |

|           |                                       | 2.4 to 2.7 V |            | -        | -                 | 16   |     |

|           | EBCLK pin output                      | 2.7 to 5.5 V |            | -        | -                 | 12   |     |

|           |                                       | 2.4 to 2.7 V |            | -        | -                 | 8    |     |

Note 1. The lower-limit frequency of FCLK is 1 MHz while programming or erasing the flash memory. When using FCLK for programming or erasing the flash memory at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note 2. The frequency accuracy of FCLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

Note 3. The lower-limit frequency of PCLKC is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the 14-bit A/D converter is in use.

Note 4. See section 9, Clock Generation Circuit in the User's Manual for the relationship of frequencies between ICLK, PCLKA, PCLKB, PCLKC, PCLKD, FCLK, and BCLK.

Note 5. The maximum value of operation frequency does not include the internal oscillator errors. The operation can be guaranteed with the errors of the internal oscillator. For details on the range for guaranteed operation, see Table 2.22, Clock timing.

- Note 3. See section 9, Clock Generation Circuit in the User's Manual for the relationship of frequencies between ICLK, PCLKA, PCLKB, PCLKB, PCLKD, FCLK, and BCLK.

- Note 4. The maximum value of operation frequency does not include the internal oscillator errors. The operation can be guaranteed with the errors of the internal oscillator. For details on the range for guaranteed operation, see Table 2.22, Clock timing.

| Table 2.20      | Operation frequency value in Low-voltage mode |

|-----------------|-----------------------------------------------|

| Conditions: VCC | C = AVCC0 = 1.6 to 5.5 V                      |

| Parameter |                                       |              | Symbol | Min      | Тур | Max*5 | Unit |

|-----------|---------------------------------------|--------------|--------|----------|-----|-------|------|

| Operation | System clock (ICLK)*4                 | 1.6 to 5.5 V | f      | 0.032768 | -   | 4     | MHz  |

| frequency | FlashIF clock (FCLK)*1, *2, *4        | 1.6 to 5.5 V |        | 0.032768 | -   | 4     |      |

|           | Peripheral module clock (PCLKA)*4     | 1.6 to 5.5 V |        | -        | -   | 4     |      |

|           | Peripheral module clock (PCLKB)*4     | 1.6 to 5.5 V |        | -        | -   | 4     |      |

|           | Peripheral module clock (PCLKC)*3, *4 | 1.6 to 5.5 V |        | -        | -   | 4     |      |

|           | Peripheral module clock (PCLKD)*4     | 1.6 to 5.5 V |        | -        | -   | 4     |      |

|           | External bus clock (BCLK)*4           | 1.6 to 5.5 V |        | -        | -   | 4     |      |

|           | EBCLK pin output                      | 1.8 to 5.5 V |        | -        | -   | 4     |      |

|           |                                       | 1.6 to 1.8 V |        | -        | -   | 2     |      |

Note 1. The lower-limit frequency of FCLK is 1 MHz while programming or erasing the flash memory. When using FCLK for programming or erasing the flash memory at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note 3. The lower-limit frequency of PCLKC is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the 14-bit A/D converter is in use.

Note 4. See section 9, Clock Generation Circuit in the User's Manual for the relationship of frequencies between ICLK, PCLKA, PCLKB, PCLKC, PCLKD, FCLK, and BCLK.

Note 5. The maximum value of operation frequency does not include errors of the internal oscillator. The operation can be guaranteed with the errors of the internal oscillator. For details on the range for guaranteed operation, see Table 2.22, Clock timing.

# Table 2.21 Operation frequency value in Subosc-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter              | Parameter                             |              |   | Min     | Тур    | Мах     | Unit |

|------------------------|---------------------------------------|--------------|---|---------|--------|---------|------|

| Operation<br>frequency | System clock (ICLK)*3                 | 1.8 to 5.5 V | f | 27.8528 | 32.768 | 37.6832 | kHz  |

|                        | FlashIF clock (FCLK)*1, *3            | 1.8 to 5.5 V |   | 27.8528 | 32.768 | 37.6832 |      |

|                        | Peripheral module clock (PCLKA)*3     | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|                        | Peripheral module clock (PCLKB)*3     | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|                        | Peripheral module clock (PCLKC)*2, *3 | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|                        | Peripheral module clock (PCLKD)*3     | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|                        | External bus clock (BCLK)*3           | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|                        | EBCLK pin output                      | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

Note 1. Programming and erasing the flash memory are not possible.

Note 2. The 14-bit A/D converter cannot be used.

Note 3. See section 9, Clock Generation Circuit in the User's Manual for the relationship of frequencies between ICLK, PCLKA, PCLKB, PCLKC, PCLKD, FCLK, and BCLK.

Note 2. The frequency accuracy of FCLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

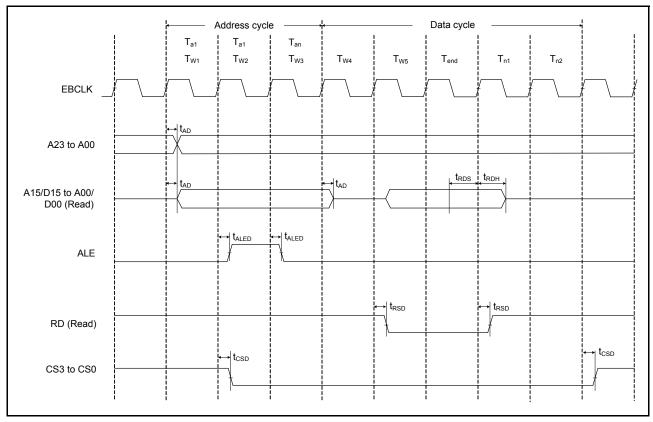

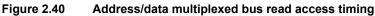

Figure 2.41 Address/data multiplexed bus write access timing

RENESAS

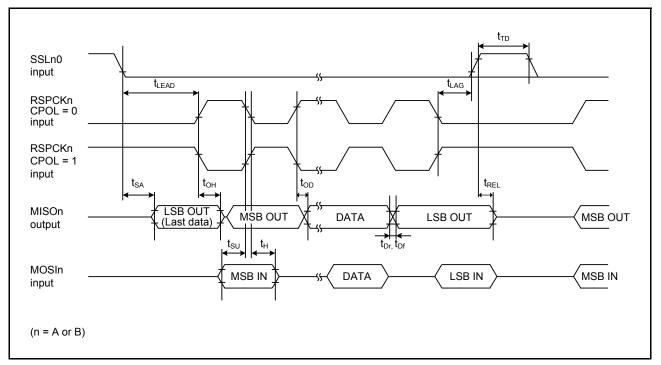

#### **SPI** Timing 2.3.10

Table 2.40

SPI timing (1 of 2)

Conditions: Middle drive output is selected in the Port Drive Capability in PmnPFS register

-

| arar | neter                             |                                           |                | Symbol              | Min                                                                        | Max  | Unit <sup>*1</sup> | Test condition |

|------|-----------------------------------|-------------------------------------------|----------------|---------------------|----------------------------------------------------------------------------|------|--------------------|----------------|

| PI   | RSPCK clock cycle                 | Master                                    |                | t <sub>SPcyc</sub>  | 2*4                                                                        | 4096 | t <sub>Pcyc</sub>  | Figure 2.61    |

|      |                                   | Slave                                     |                |                     | 6                                                                          | 4096 |                    |                |

|      | RSPCK clock high<br>pulse width   | Master                                    |                | t <sub>SPCKWH</sub> | (t <sub>SPcyc</sub> – t <sub>SPCKR</sub><br>– t <sub>SPCKF</sub> ) / 2 – 3 | -    | ns                 |                |

|      |                                   | Slave                                     |                |                     | 3 × t <sub>Pcyc</sub>                                                      | -    |                    |                |

|      | RSPCK clock low<br>pulse width    | Master                                    |                | t <sub>SPCKWL</sub> | (t <sub>SPcyc</sub> – t <sub>SPCKR</sub><br>– t <sub>SPCKF</sub> ) / 2 – 3 | -    | ns                 |                |

|      |                                   | Slave                                     |                |                     | 3 × t <sub>Pcyc</sub>                                                      | -    |                    |                |

|      | RSPCK clock rise<br>and fall time | Output                                    | 2.7 V or above | t <sub>SPCKr,</sub> | -                                                                          | 10   | ns                 |                |

|      |                                   |                                           | 2.4 V or above | t <sub>SPCKf</sub>  | -                                                                          | 15   |                    |                |

|      |                                   |                                           | 1.8 V or above |                     | -                                                                          | 20   |                    |                |

|      |                                   |                                           | 1.6 V or above |                     | -                                                                          | 30   |                    |                |

|      |                                   | Input                                     |                |                     | -                                                                          | 1    | μs                 |                |

|      | Data input setup<br>time          | Master                                    |                | t <sub>SU</sub>     | 10                                                                         | -    | ns                 | Figure 2.62 to |

|      |                                   | Slave                                     | 2.4 V or above | -                   | 10                                                                         | -    |                    | Figure 2.67    |

|      |                                   |                                           | 1.8 V or above |                     | 15                                                                         | -    |                    |                |

|      |                                   |                                           | 1.6 V or above |                     | 20                                                                         | -    |                    |                |

|      | Data input hold time              | ime Master<br>(RSPCK is PCLKA/2)          |                | t <sub>HF</sub>     | 0                                                                          | -    | ns                 |                |

|      |                                   | Master<br>(RSPCK is other than<br>above.) |                | t <sub>H</sub>      | t <sub>Pcyc</sub>                                                          | -    |                    |                |

|      |                                   | Slave                                     |                | t <sub>H</sub>      | 20                                                                         | -    |                    |                |

|      | SSL setup time                    | Master                                    | 1.8 V or above | t <sub>LEAD</sub>   | $-30 + N \times t_{Spcyc}^{*2}$                                            | -    | ns                 |                |

|      |                                   |                                           | 1.6 V or above |                     | $-50 + N \times t_{Spcyc}^{*2}$                                            | -    |                    |                |

|      |                                   | Slave                                     |                | 1                   | 6 × t <sub>Pcyc</sub>                                                      | -    |                    |                |

|      | SSL hold time                     | Master                                    |                | t <sub>LAG</sub>    | $-30 + N \times t_{Spcyc}^{*3}$                                            | -    |                    |                |

|      |                                   | Slave                                     |                | ]                   | 6 × t <sub>Pcyc</sub>                                                      | -    |                    |                |

#### Table 2.40 SPI timing (2 of 2)

Conditions: Middle drive output is selected in the Port Drive Capability in PmnPFS register -

| ran | neter                            |        |                | Symbol                           | Min                          | Мах                                               | Unit <sup>*1</sup> | Test conditions |  |

|-----|----------------------------------|--------|----------------|----------------------------------|------------------------------|---------------------------------------------------|--------------------|-----------------|--|

| I   | Data output delay                | Master | 2.7 V or above | t <sub>OD</sub>                  | -                            | 14                                                | ns                 | Figure 2.62 to  |  |

|     |                                  |        | 2.4 V or above |                                  | -                            | 20                                                |                    | Figure 2.67     |  |

|     |                                  |        | 1.8 V or above |                                  | -                            | 25                                                |                    |                 |  |

|     |                                  |        | 1.6 V or above |                                  | -                            | 30                                                |                    |                 |  |

|     |                                  | Slave  | 2.7 V or above |                                  | -                            | 50                                                |                    |                 |  |

|     |                                  |        | 2.4 V or above |                                  | -                            | 60                                                |                    |                 |  |

|     |                                  |        | 1.8 V or above |                                  | -                            | 85                                                |                    |                 |  |

|     |                                  |        | 1.6 V or above |                                  | -                            | 110                                               |                    |                 |  |

|     | Data output hold                 | Master |                | t <sub>OH</sub>                  | 0                            | -                                                 | ns                 | ]               |  |

|     | time                             | Slave  |                |                                  | 0                            | -                                                 |                    |                 |  |

| _   | Successive transmission delay    |        |                | t <sub>TD</sub>                  | $t_{SPcyc}$ + 2 × $t_{Pcyc}$ | 8 × t <sub>SPcyc</sub><br>+ 2 × t <sub>Pcyc</sub> | ns                 |                 |  |

|     |                                  | Slave  |                |                                  | 6 × t <sub>Pcyc</sub>        | -                                                 |                    |                 |  |

|     | MOSI and MISO rise and fall time | Output | 2.7 V or above | t <sub>Dr,</sub> t <sub>Df</sub> | -                            | 10                                                | ns                 |                 |  |

|     |                                  |        | 2.4 V or above | -                                | -                            | 15                                                |                    |                 |  |

|     |                                  |        | 1.8 V or above |                                  | -                            | 20                                                |                    |                 |  |

|     |                                  |        | 1.6 V or above |                                  | -                            | 30                                                |                    |                 |  |

|     |                                  | Input  |                |                                  | -                            | 1                                                 | μs                 |                 |  |

|     | SSL rise and fall                | Output | 2.7 V or above | t <sub>SSLr,</sub>               | -                            | 10                                                | ns                 |                 |  |

|     | time                             |        | 2.4 V or above | t <sub>SSLf</sub>                | -                            | 15                                                |                    |                 |  |

|     |                                  |        | 1.8 V or above |                                  | -                            | 20                                                |                    |                 |  |

|     |                                  |        | 1.6 V or above |                                  | -                            | 30                                                |                    |                 |  |

|     |                                  | Input  |                |                                  | -                            | 1                                                 | μs                 |                 |  |

|     | Slave access time                |        | 2.4 V or above | t <sub>SA</sub>                  | -                            | 2 × t <sub>Pcyc</sub> + 100                       | ns                 | Figure 2.66 and |  |

|     |                                  |        | 1.8 V or above |                                  | -                            | 2 × t <sub>Pcyc</sub> + 140                       |                    | Figure 2.67     |  |

|     |                                  |        | 1.6 V or above |                                  | -                            | 2 × t <sub>Pcyc</sub> + 180                       |                    |                 |  |

|     | Slave output release time        |        | 2.4 V or above | t <sub>REL</sub>                 | -                            | 2 × t <sub>Pcyc</sub> + 100                       | ns                 |                 |  |

|     |                                  |        | 1.8 V or above | ]                                | -                            | 2 × t <sub>Pcyc</sub> + 140                       |                    |                 |  |

|     |                                  |        | 1.6 V or above |                                  | -                            | 2 × t <sub>Pcyc</sub> + 180                       |                    |                 |  |

Note 1.  $t_{Pcyc}$ : PCLKA cycle. Note 2. N is set as an integer from 1 to 8 by the SPCKD register.

Note 3. N is set as an integer from 1 to 8 by the SSLND register.

Note 4. The upper limit of RSPCK is 16 MHz.

### Figure 2.67 SPI timing (slave, CPHA = 1)

## 2.3.11 QSPI Timing

### Table 2.41 QSPI timing

Conditions: VCC = 1.8 to 5.5 V Conditions: Middle drive output is selected in the Port Drive Capability bit in PmnPFS register

| Param | eter                   |                    | Symbol                                               | Min                                     | Max                                     | Unit*1             | Test conditions |

|-------|------------------------|--------------------|------------------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------|-----------------|

| QSPI  | QSPCLK clock cycle     | t <sub>QScyc</sub> | 2* <sup>4</sup>                                      | 48                                      | t <sub>Pcyc</sub>                       | Figure 2.68        |                 |

|       | QSPCLK clock high-lev  | t <sub>QSWH</sub>  | t <sub>QScyc</sub> × 0.4                             | -                                       | ns                                      |                    |                 |

|       | QSPCLK clock low-leve  | el pulse width     | t <sub>QSWL</sub>                                    | t <sub>QScyc</sub> × 0.4                | -                                       | ns                 |                 |

|       | Data input setup time  | t <sub>SU</sub>    | 25                                                   | -                                       | ns                                      | Figure 2.69        |                 |

|       | Data input hold time   | t <sub>IH</sub>    | 2                                                    | -                                       | ns                                      |                    |                 |

|       | SSL setup time         | t <sub>LEAD</sub>  | (N + 0.5) ×<br>t <sub>Qscyc</sub> - 15* <sup>2</sup> | $(N + 0.5) \times t_{Qscyc} + 100^{*2}$ | ns                                      |                    |                 |

|       | SSL hold time          | SSL hold time      |                                                      |                                         | $(N + 0.5) \times t_{Qscyc} + 100^{*3}$ | ns                 |                 |

|       | Data output delay      | 2.7 V or above     | t <sub>OD</sub>                                      | -                                       | 14                                      | ns                 |                 |

|       |                        | 2.4 V or above     | -                                                    | -                                       | 20                                      |                    |                 |

|       |                        | 1.8 V or above     |                                                      | -                                       | 30                                      |                    |                 |

|       | Data output hold time  | 2.7 V or above     | t <sub>OH</sub>                                      | -3.3                                    | -                                       | ns                 |                 |

|       |                        | 1.8 V or above     |                                                      | -10                                     | -                                       |                    |                 |

|       | Successive transmissio | n delay            | t <sub>TD</sub>                                      | 1                                       | 16                                      | t <sub>Qscyc</sub> |                 |

Note 1. t<sub>Pcvc</sub>: PCLKA cycle.

Note 2. N is set to 0 or 1 in SFMSLD.

Note 3. N is set to 0 or 1 in SFMSHD.

Note 4. The upper limit of QSPCLK is 16MHz.

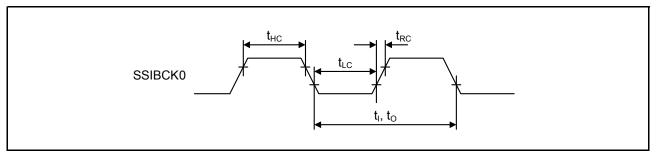

#### SSIE Timing 2.3.13

# Table 2.43SSIE timingConditions: VCC = 1.6 to 5.5 V

| Paramet | ter                                        |                     | Symbol             | Min | Мах | Unit | Test conditions             |  |

|---------|--------------------------------------------|---------------------|--------------------|-----|-----|------|-----------------------------|--|

| SSIE    | AUDIO_CLK input                            | 2.7 V or above      | t <sub>AUDIO</sub> | -   | 25  | MHz  | -                           |  |

|         | frequency                                  | 1.6 V or above      |                    | -   | 4   |      |                             |  |

|         | Output clock period                        | Output clock period |                    |     | -   | ns   | Figure 2.71                 |  |

|         | Input clock period                         |                     | t <sub>l</sub>     | 250 | -   | ns   | 7                           |  |

|         | Clock high pulse                           | 1.8 V or above      | t <sub>HC</sub>    | 100 | -   | ns   | 7                           |  |

|         | width                                      | 1.6 V or above      |                    | 200 | -   |      |                             |  |

|         | Clock low pulse                            | 1.8 V or above      | t <sub>LC</sub>    | 100 | -   | ns   |                             |  |

|         | width                                      | 1.6 V or above      |                    | 200 | -   |      |                             |  |

|         | Clock rise time                            |                     | t <sub>RC</sub>    | -   | 25  | ns   | 7                           |  |

|         | Data delay                                 | 2.7 V or above      | t <sub>DTR</sub>   | -   | 65  | ns   | Figure 2.72,<br>Figure 2.73 |  |

|         |                                            | 1.8 V or above      | _                  | -   | 105 |      |                             |  |

|         |                                            | 1.6 V or above      |                    | -   | 140 |      |                             |  |

|         | Set-up time                                | 2.7 V or above      | t <sub>SR</sub>    | 65  | -   | ns   |                             |  |

|         |                                            | 1.8 V or above      |                    | 90  | -   |      |                             |  |

|         |                                            | 1.6 V or above      |                    | 140 | -   |      |                             |  |

|         | Hold time                                  | Hold time           |                    | 40  | -   | ns   | 7                           |  |

|         | SSITXD0 output                             | 1.8 V or above      | t <sub>DTRW</sub>  | -   | 105 | ns   | Figure 2.74                 |  |

|         | delay from<br>SSILRCK/SSIFS<br>change time | 1.6 V or above      |                    | -   | 140 |      |                             |  |

Figure 2.71 SSIE clock input/output timing

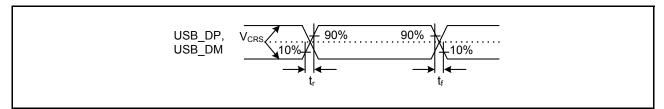

## 2.4 USB Characteristics

# 2.4.1 USBFS Timing

### Table 2.46USB characteristics

Conditions: VCC = VCC\_USB = 3.0 to 3.6 V, Ta = -20 to +85°C (USBCLKSEL = 1), Ta = -40 to +105°C (USBCLKSEL = 0)

| Parameter                |                                |        | Symbol                         | Min       | Max       | Unit | Test conditions                                                        |  |

|--------------------------|--------------------------------|--------|--------------------------------|-----------|-----------|------|------------------------------------------------------------------------|--|

| Input                    | Input high level volt          | age    | V <sub>IH</sub>                | 2.0       | -         | V    | -                                                                      |  |

| characteristics          | Input low level volta          | ige    | V <sub>IL</sub>                | -         | 0.8       | V    | -                                                                      |  |

|                          | Differential input sensitivity |        | V <sub>DI</sub>                | 0.2       | -         | V    | USB_DP - USB_DM                                                        |  |

|                          | Differential common<br>range   | n mode | V <sub>CM</sub>                | 0.8       | 2.5       | V    | -                                                                      |  |

| Output                   | Output high level vo           | oltage | V <sub>OH</sub>                | 2.8       | VCC_USB   | V    | I <sub>OH</sub> = –200 μA                                              |  |

| characteristics          | Output low level vo            | ltage  | V <sub>OL</sub>                | 0.0       | 0.3       | V    | I <sub>OL</sub> = 2 mA                                                 |  |

|                          | Cross-over voltage             |        | V <sub>CRS</sub>               | 1.3       | 2.0       | V    | Figure 2.77,                                                           |  |

|                          | Rise time                      | FS     | t <sub>r</sub>                 | 4         | 20        | ns   | Figure 2.78,<br>Figure 2.79                                            |  |

|                          |                                | LS     |                                | 75        | 300       |      |                                                                        |  |

|                          | Fall time                      | FS     | t <sub>f</sub>                 | 4         | 20        | ns   |                                                                        |  |

|                          |                                | LS     |                                | 75        | 300       |      |                                                                        |  |

|                          | Rise/fall time ratio           | FS     | t <sub>r</sub> /t <sub>f</sub> | 90        | 111.11    | %    |                                                                        |  |

|                          |                                | LS     |                                | 80        | 125       |      |                                                                        |  |

|                          | Output resistance              |        | Z <sub>DRV</sub>               | 28        | 44        | Ω    | (Adjusting the resistance<br>of external elements is not<br>required.) |  |

| VBUS                     | VBUS input voltage             | ;      | V <sub>IH</sub>                | VCC × 0.8 | -         | V    | -                                                                      |  |

| characteristics          |                                |        | V <sub>IL</sub>                | -         | VCC × 0.2 | V    | -                                                                      |  |

| Pull-up,                 | Pull-down resistor             |        | R <sub>PD</sub>                | 14.25     | 24.80     | kΩ   | -                                                                      |  |

| pull-down                | Pull-up resistor               |        | R <sub>PUI</sub>               | 0.9       | 1.575     | kΩ   | During idle state                                                      |  |

|                          |                                |        | R <sub>PUA</sub>               | 1.425     | 3.09      | kΩ   | During reception                                                       |  |

| Battery Charging         | D+ sink current                |        | I <sub>DP_SINK</sub>           | 25        | 175       | μA   | -                                                                      |  |

| Specification<br>Ver 1.2 | D- sink current                |        | I <sub>DM_SINK</sub>           | 25        | 175       | μA   | -                                                                      |  |

|                          | DCD source current             |        | I <sub>DP_SRC</sub>            | 7         | 13        | μA   | -                                                                      |  |

|                          | Data detection volta           | age    | V <sub>DAT_REF</sub>           | 0.25      | 0.4       | V    | -                                                                      |  |

|                          | D+ source voltage              |        | V <sub>DP_SRC</sub>            | 0.5       | 0.7       | V    | Output current = 250 µA                                                |  |

|                          | D- source voltage              |        | V <sub>DM_SRC</sub>            | 0.5       | 0.7       | V    | Output current = 250 µA                                                |  |

# 2.7 TSN Characteristics

### Table 2.60 TSN characteristics

```

Conditions: VCC = AVCC0 = 2.0 to 5.5 V

```

| Parameter                     | Symbol             | Min | Тур   | Max | Unit  | Test conditions |

|-------------------------------|--------------------|-----|-------|-----|-------|-----------------|

| Relative accuracy             | -                  | -   | ±1.5  | -   | °C    | 2.4 V or above  |

|                               | -                  | -   | ±2.0  | -   | °C    | Below 2.4 V     |

| Temperature slope             | -                  | -   | -3.65 | -   | mV/°C | -               |

| Output voltage (at 25°C)      | -                  | -   | 1.05  | -   | V     | VCC = 3.3 V     |

| Temperature sensor start time | t <sub>START</sub> | -   | -     | 5   | μs    | -               |

| Sampling time                 | -                  | 5   | -     | -   | μs    | -               |

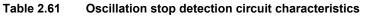

# 2.8 OSC Stop Detect Characteristics

| Parameter      | Symbol          | Min | Тур | Max | Unit | Test conditions |

|----------------|-----------------|-----|-----|-----|------|-----------------|

| Detection time | t <sub>dr</sub> | -   | -   | 1   | ms   | Figure 2.84     |

Figure 2.84 Oscillation stop detection timing

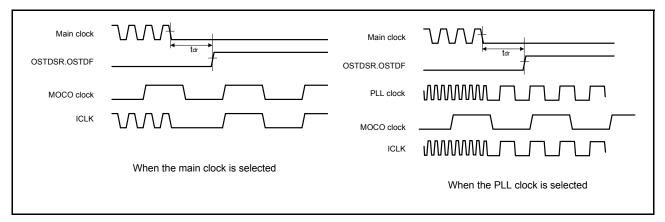

# 2.9 POR and LVD Characteristics

| Parameter                                |                                    | Symbol              | Min  | Тур  | Max  | Unit | Test conditions             |

|------------------------------------------|------------------------------------|---------------------|------|------|------|------|-----------------------------|

| Voltage detection<br>level* <sup>1</sup> | Power-on reset (POR)               | V <sub>POR</sub>    | 1.27 | 1.42 | 1.57 | V    | Figure 2.85,<br>Figure 2.86 |

|                                          | Voltage detection circuit (LVD0)*2 | V <sub>det0_0</sub> | 3.68 | 3.85 | 4.00 | V    | Figure 2.87                 |

|                                          |                                    | V <sub>det0_1</sub> | 2.68 | 2.85 | 2.96 |      | At falling edge<br>VCC      |

|                                          |                                    | V <sub>det0_2</sub> | 2.38 | 2.53 | 2.64 |      |                             |

|                                          |                                    | V <sub>det0_3</sub> | 1.78 | 1.90 | 2.02 |      |                             |

|                                          |                                    | V <sub>det0_4</sub> | 1.60 | 1.69 | 1.82 |      |                             |

|                                          | Voltage detection circuit (LVD1)*3 | V <sub>det1_0</sub> | 4.13 | 4.29 | 4.45 | V    | Figure 2.88                 |

|                                          |                                    | V <sub>det1_1</sub> | 3.98 | 4.16 | 4.30 |      | At falling edge<br>VCC      |

|                                          |                                    | V <sub>det1_2</sub> | 3.86 | 4.03 | 4.18 |      |                             |

|                                          |                                    | V <sub>det1_3</sub> | 3.68 | 3.86 | 4.00 |      |                             |

|                                          |                                    | V <sub>det1_4</sub> | 2.98 | 3.10 | 3.22 |      |                             |

|                                          |                                    | V <sub>det1_5</sub> | 2.89 | 3.00 | 3.11 |      |                             |

|                                          |                                    | V <sub>det1_6</sub> | 2.79 | 2.90 | 3.01 |      |                             |

|                                          |                                    | V <sub>det1_7</sub> | 2.68 | 2.79 | 2.90 |      |                             |

|                                          |                                    | V <sub>det1_8</sub> | 2.58 | 2.68 | 2.78 |      |                             |

|                                          |                                    | V <sub>det1_9</sub> | 2.48 | 2.58 | 2.68 |      |                             |

|                                          |                                    | V <sub>det1_A</sub> | 2.38 | 2.48 | 2.58 |      |                             |

|                                          |                                    | V <sub>det1_B</sub> | 2.10 | 2.20 | 2.30 |      |                             |

|                                          |                                    | V <sub>det1_C</sub> | 1.84 | 1.96 | 2.05 |      |                             |

|                                          |                                    | V <sub>det1_D</sub> | 1.74 | 1.86 | 1.95 |      |                             |

|                                          |                                    | V <sub>det1_E</sub> | 1.63 | 1.75 | 1.84 |      |                             |

|                                          |                                    | V <sub>det1_F</sub> | 1.60 | 1.65 | 1.73 |      |                             |

|                                          | Voltage detection circuit (LVD2)*4 | V <sub>det2_0</sub> | 4.11 | 4.31 | 4.48 | V    | Figure 2.89                 |

|                                          |                                    | V <sub>det2_1</sub> | 3.97 | 4.17 | 4.34 |      | At falling edge<br>VCC      |

|                                          |                                    | V <sub>det2_2</sub> | 3.83 | 4.03 | 4.20 |      |                             |

|                                          |                                    | V <sub>det2_3</sub> | 3.64 | 3.84 | 4.01 | 7    |                             |

| Table 2.62 | Power-on reset circuit and voltage detection circuit characteristics (1) |

|------------|--------------------------------------------------------------------------|

|------------|--------------------------------------------------------------------------|

Note 1. These characteristics apply when noise is not superimposed on the power supply. When a setting causes this voltage detection level to overlap with that of the voltage detection circuit, it cannot be specified whether LVD1 or LVD2 is used for voltage detection.

Note 2. # in the symbol Vdet0\_# denotes the value of the OFS1.VDSEL1[2:0] bits.

Note 3. # in the symbol Vdet1\_# denotes the value of the LVDLVLR.LVD1LVL[4:0] bits.

Note 4. # in the symbol Vdet2\_# denotes the value of the LVDLVLR.LVD2LVL[2:0] bits.

| Parameter                                   |                    | Symbol                | Min | Тур | Max | Unit | Test conditions                                     |

|---------------------------------------------|--------------------|-----------------------|-----|-----|-----|------|-----------------------------------------------------|

| Wait time after power-on reset cancellation | LVD0: enable       | t <sub>POR</sub>      | -   | 1.7 | -   | ms   | -                                                   |

|                                             | LVD0: disable      | t <sub>POR</sub>      | -   | 1.3 | -   | ms   | -                                                   |

| Wait time after voltage                     | LVD0: enable*1     | t <sub>LVD0,1,2</sub> | -   | 0.6 | -   | ms   | -                                                   |

| monitor 0, 1, 2 reset cancellation          | LVD0: disable*2    | t <sub>LVD1,2</sub>   | -   | 0.2 | -   | ms   | -                                                   |

| Response delay*3                            |                    | t <sub>det</sub>      | -   | -   | 350 | μs   | Figure 2.85,<br>Figure 2.86                         |

| Minimum VCC down time                       |                    | t <sub>VOFF</sub>     | 450 | -   | -   | μs   | Figure 2.85,<br>VCC = 1.0 V or above                |

| Power-on reset enable tim                   | е                  | t <sub>W(POR)</sub>   | 1   | -   | -   | ms   | Figure 2.86,<br>VCC = below 1.0 V                   |

| LVD operation stabilization enabled)        | time (after LVD is | t <sub>d(E-A)</sub>   | -   | -   | 300 | μs   | Figure 2.88,<br>Figure 2.89                         |

| Hysteresis width (POR)                      |                    | V <sub>PORH</sub>     | -   | 110 | -   | mV   | -                                                   |

| Hysteresis width (LVD0, LV                  | /D1, and LVD2)     | V <sub>LVH</sub>      | -   | 60  | -   | mV   | LVD0 selected                                       |

|                                             |                    |                       | -   | 100 | -   |      | V <sub>det1_0</sub> to V <sub>det1_2</sub> selected |

|                                             |                    |                       | -   | 60  | -   |      | V <sub>det1_3</sub> to V <sub>det1_9</sub> selected |

|                                             |                    |                       | -   | 50  | -   | 1    | V <sub>det1_A</sub> or V <sub>det1_B</sub> selected |

|                                             |                    |                       | -   | 40  | -   | 1    | V <sub>det1_C</sub> or V <sub>det1_F</sub> selected |

|                                             |                    |                       | -   | 60  | -   |      | LVD2 selected                                       |

### Table 2.63 Power-on reset circuit and voltage detection circuit characteristics (2)

Note 1. When OFS1.LVDAS = 0.

Note 2. When OFS1.LVDAS = 1.

Note 3. The minimum VCC down time indicates the time when VCC is below the minimum value of voltage detection levels V<sub>POR</sub>, Vdet0, Vdet1, and Vdet2 for the POR/LVD.

Figure 2.85 Voltage detection reset timing

# 2.12.2 Internal Voltage Boosting Method

[1/3 Bias Method]

### Table 2.70 Internal voltage boosting method LCD characteristics

Conditions: VCC = 1.8 V to 5.5 V

| Parameter                                  | Symbol            | Conditions           |            | Min                        | Тур               | Max               | Unit | Test<br>conditions |

|--------------------------------------------|-------------------|----------------------|------------|----------------------------|-------------------|-------------------|------|--------------------|

| LCD output voltage                         | V <sub>L1</sub>   | C1 to C4*1 = 0.47 µF | VLCD = 04h | 0.90                       | 1.0               | 1.08              | V    | -                  |

| variation range                            |                   |                      | VLCD = 05h | 0.95                       | 1.05              | 1.13              | V    | -                  |

|                                            |                   |                      | VLCD = 06h | 1.00                       | 1.10              | 1.18              | V    | -                  |

|                                            |                   |                      | VLCD = 07h | 1.05                       | 1.15              | 1.23              | V    | -                  |

|                                            |                   |                      | VLCD = 08h | 1.10                       | 1.20              | 1.28              | V    | -                  |

|                                            |                   |                      | VLCD = 09h | 1.15                       | 1.25              | 1.33              | V    | -                  |