Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | HC05                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 2.1MHz                                                       |

| Connectivity               | SCI, SPI                                                     |

| Peripherals                | POR, WDT                                                     |

| Number of I/O              | 24                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | OTP                                                          |

| EEPROM Size                | -                                                            |

| RAM Size                   | 352 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-QFP                                                       |

| Supplier Device Package    | 44-QFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc705c9acfb |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

List of Chapters

General Description

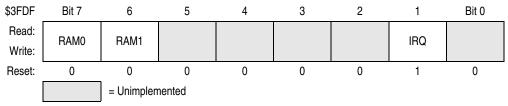

# 1.5 Software-Programmable Options (MC68HC05C9A Mode Only)

The C9A option register (OR), shown in Figure 1-4, is enabled only if configured in C9A mode. This register contains the programmable bits for the following options:

- Map two different areas of memory between RAM and EPROM, one of 48 bytes and one of 128 bytes

- Edge-triggered only or edge- and level-triggered external interrupt (IRQ pin and any port B pin configured for interrupt)

This register must be written to by user software during operation of the microcontroller.

Figure 1-4. C9A Option Register

### RAM0 — Random Access Memory Control Bit 0

This read/write bit selects between RAM or EPROM in location \$0020 to \$004F. This bit can be read or written at any time.

1 = RAM selected

0 = EPROM selected

#### RAM1— Random Access Memory Control Bit 1

This read/write bit selects between RAM or EPROM in location \$0100 to \$017F. This bit can be read or written at any time.

- 1 = RAM selected

- 0 = EPROM selected

#### IRQ — Interrupt Request Bit

This bit selects between an edge-triggered only or edge- and level- triggered external interrupt pin. This bit is set by reset, but can be cleared by software. This bit can be written only once.

- 1 = Edge and level interrupt option selected

- 0 = Edge-only interrupt option selected

**Functional Pin Descriptions**

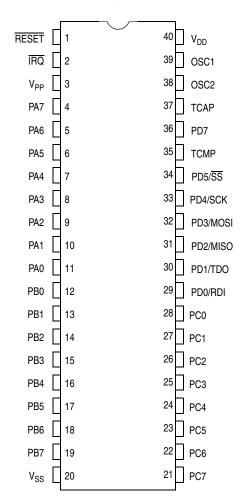

# **1.6 Functional Pin Descriptions**

Figure 1-5, Figure 1-6, Figure 1-7, and Figure 1-8 show the pin assignments for the available packages. A functional description of the pins follows.

**NOTE** A line over a signal name indicates an active low signal. For example, RESET is active high and RESET is active low.

Figure 1-5. 40-Pin PDIP Pin Assignments

**General Description**

| \$0000           |                      |                        |                |                                              | \$0000           |

|------------------|----------------------|------------------------|----------------|----------------------------------------------|------------------|

|                  | I/O REGIS            | STERS                  |                | PORT A DATA REGISTER<br>PORT B DATA REGISTER | \$0000           |

|                  | 32 BY                |                        |                | PORT C DATA REGISTER                         | \$0002           |

|                  |                      |                        |                | PORT D DATA REGISTER                         | \$0003           |

| \$001F           | l                    | ··· <del>p</del> ····· | ·····;, ······ | PORT A DATA DIRECTION REGISTER               | \$0004           |

| \$0020           | USER EPROM           | RAM                    |                | PORT & DATA DIRECTION REGISTER               | \$0005           |

|                  | 48 BYTES<br>RAM0 = 0 | 48 BYTES<br>RAM0 = 1   |                | PORT C DATA DIRECTION REGISTER               | \$0006           |

| \$004F           | 1 // (1/) = 0        |                        | \              | PORT D DATA DIRECTION REGISTER               | \$0007           |

| \$0050           | <b>≜</b>             |                        |                | UNUSED                                       | \$0008           |

|                  | RAM                  |                        | $\setminus$    | UNUSED                                       | \$0009           |

|                  | 176 BYTES            |                        |                | SPI CONTROL REGISTER                         | \$000A           |

|                  |                      |                        | $\setminus$    | SPI STATUS REGISTER                          | \$000B           |

| \$00BF<br>\$00C0 |                      |                        |                | SPI DATA REGISTER                            | \$000C           |

| ψυυου            |                      | Ť                      | $\setminus$    | SCI BAUD RATE REGISTER                       | \$000D           |

|                  |                      | (STACK)                |                | SCI CONTROL REGISTER 1                       | \$000E           |

| \$00FF           | •                    | 64 BYTES               |                | SCI CONTROL REGISTER 2                       | \$000F           |

| \$0100           | JSER EPROM           | RAM                    |                | SCI STATUS REGISTER                          | \$0010           |

| L L              | 128 BYTES            | 128 BYTES              |                | SCI DATA REGISTER                            | \$0011           |

|                  |                      |                        |                | TIMER CONTROL REGISTER                       | \$0012           |

| \$017F           | RAM1 = 0             | RAM1 = 1               |                | TIMER STATUS REGISTER                        | \$0013           |

| \$0170           |                      | L                      |                | INPUT CAPTURE REGISTER (HIGH)                | \$0014           |

|                  |                      |                        | $\setminus$    | INPUT CAPTURE REGISTER (LOW)                 | \$0015           |

|                  |                      |                        | $\setminus$    | OUTPUT COMPARE REGISTER (HIGH)               | \$0016           |

|                  |                      |                        | $\setminus$    | OUTPUT COMPARE REGISTER (LOW)                | \$0017           |

|                  |                      |                        |                | TIMER COUNTER REGISTER (HIGH)                | \$0018           |

|                  |                      |                        |                | TIMER COUNTER REGISTER (LOW)                 | \$0019           |

|                  |                      | EPROM<br>BYTES         |                | ALTERNATE COUNTER REGISTER (HIGH)            | \$001A           |

|                  | 15,744               | DIILO                  | $\setminus$    | ALTERNATE COUNTER REGISTER (LOW)             | \$001B           |

|                  |                      |                        | $\setminus$    | UNUSED                                       | \$001C           |

|                  |                      |                        | $\setminus$    | COP RESET REGISTER                           | \$001D           |

|                  |                      |                        | $\setminus$    | COP CONTROL REGISTER                         | \$001E           |

|                  |                      |                        | \              | UNUSED                                       | \$001F           |

|                  |                      |                        | ١L             |                                              |                  |

| \$3EFF           |                      |                        |                |                                              |                  |

| \$3F00           |                      |                        | 1              | PORT B MASK OPTION REGISTER                  |                  |

|                  |                      |                        | /              | MASK OPTION REGISTER 2                       | \$3FF0<br>\$3FF1 |

|                  |                      |                        |                | MASK OF HOM REDISTENZ                        | \$3FF1<br>\$3FF2 |

|                  |                      |                        |                | UNUSED (2 BYTES)                             | \$3FF3           |

|                  | BOOTL                | OADER                  |                |                                              | \$3FF4           |

|                  |                      | OM                     |                | SPI VECTOR (HIGH)                            | \$3FF5           |

|                  |                      | ECTORS<br>BYTES        |                | SPI VECTOR (LOW)<br>SCI VECTOR (HIGH)        | \$3FF6           |

|                  | 2001                 | 51120                  |                |                                              | \$3FF7           |

|                  |                      |                        |                | SCI VECTOR (LOW)<br>TIMER VECTOR (HIGH)      | \$3FF8           |

|                  | r                    | i                      |                | TIMER VECTOR (HIGH)                          | \$3FF9           |

| \$3FDF           | C9A OPTION           | REGISTER               |                | IRQ VECTOR (HIGH)                            | \$3FF9<br>\$3FFA |

| \$3FEF           | l                    |                        | /              | IRQ VECTOR (LOW)                             | \$3FFA<br>\$3FFB |

| \$3FF0           | MASK OPTION          |                        | r              | SWI VECTOR (LOW)                             | \$3FFD<br>\$3FFC |

| \$3FF1           |                      | I NEGISTENS            |                | SWI VECTOR (HIGH)<br>SWI VECTOR (LOW)        | \$3FFC<br>\$3FFD |

| \$3FF2           | USER EPRU            |                        |                | RESET VECTOR (LOW)                           | \$3FFD<br>\$3FFE |

| \$3FFF           | 14 B                 | YTES                   |                | RESET VECTOR (HIGH BYTE)                     | \$3FFE<br>\$3FFF |

| ψΟΓΓΓ            |                      |                        |                | RESET VEVIOR (LOW DITE)                      | φορηγ            |

Figure 2-1. C9A Memory Map

#### I/O Registers

| Addr.  | Register Name                          |                 | Bit 7  | 6          | 5      | 4        | 3           | 2      | 1          | Bit 0 |

|--------|----------------------------------------|-----------------|--------|------------|--------|----------|-------------|--------|------------|-------|

| \$000D | SCI Baud Rate Register<br>BAUD         | Read:<br>Write: |        |            | SCP1   | SCP0     |             | SCR2   | SCR1       | SCR0  |

|        | See page 69.                           | Reset:          | _      | _          | 0      | 0        | —           | U      | U          | U     |

| \$000E | SCI Control Register 1<br>(SCCR1)      | Read:<br>Write: | R8     | T8         |        | М        | WAKE        |        |            |       |

|        | See page 65.                           | Reset:          | U      | U          | 0      | U        | U           | 0      | 0          | 0     |

| \$000F | SCI Control Register 2<br>(SCCR2)      | Read:<br>Write: | TIE    | TCIE       | RIE    | ILIE     | TE          | RE     | RWU        | SBK   |

|        | See page 66.                           | Reset:          | 0      | 0          | 0      | 0        | 0           | 0      | 0          | 0     |

|        | SCI Status Register                    | Read:           | TDRE   | TC         | RDRF   | IDLE     | OR          | NF     | FE         |       |

| \$0010 | (SČSR)                                 | Write:          |        |            |        |          |             |        |            |       |

|        | See page 68.                           | Reset:          | 1      | 1          | 0      | 0        | 0           | 0      | 0          | _     |

| \$0011 | SCI Data Register<br>(SCDR)            | Read:<br>Write: | SCD7   | SDC6       | SCD5   | SCD4     | SCD3        | SCD2   | SCD1       | SCD0  |

|        | See page 65.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

| \$0012 | Timer Control Register<br>(TCR)        | Read:<br>Write: | ICIE   | OCIE       | TOIE   | 0        | 0           | 0      | IEDG       | OLVL  |

|        | See page 53.                           | Reset:          | 0      | 0          | 0      | 0        | 0           | 0      | U          | 0     |

|        | Timer Status Register                  | Read:           | ICF    | OCF        | TOF    | 0        | 0           | 0      | 0          | 0     |

| \$0013 | (TSR)                                  | Write:          |        |            |        |          |             |        |            |       |

|        | See page 54.                           | Reset:          | U      | U          | U      | 0        | 0           | 0      | 0          | 0     |

|        | Input Capture Register High            | Read:           | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10 | Bit 9      | Bit 8 |

| \$0014 | (ICRH)                                 | Write:          |        |            |        |          |             |        |            |       |

|        | See page 56.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

|        | Input Capture Register Low             | Read:           | Bit 7  | Bit 6      | Bit 5  | Bit 4    | Bit 3       | Bit 2  | Bit 1      | Bit 0 |

| \$0015 | (ICRL)                                 | Write:          |        |            |        |          |             |        |            |       |

|        | See page 56.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

| \$0016 | Output Compare Register<br>High (OCRH) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10 | Bit 9      | Bit 8 |

|        | See page 56. Res                       |                 |        |            |        | Unaffect | ed by reset |        |            |       |

| \$0017 | Output Compare Register<br>Low (OCRL)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4    | Bit 3       | Bit 2  | Bit 1      | Bit 0 |

|        | See page 56.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

|        | Timer Register High                    | Read:           | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10 | Bit 9      | Bit 8 |

| \$0018 | (TRH)                                  | Write:          |        |            |        |          |             |        |            |       |

|        | See page 55.                           | Reset:          | 1      | 1          | 1      | 1        | 1           | 1      | 1          | 1     |

|        |                                        | [               |        | = Unimpler | mented | R        | = Reserved  |        | U = Unaffe | cted  |

Figure 2-4. Input/Output Registers (Sheet 2 of 3)

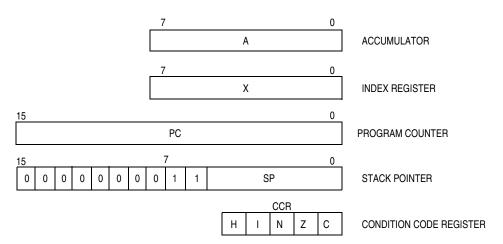

# Chapter 3 Central Processor Unit (CPU)

# 3.1 Introduction

This section contains the basic programmers model and the registers contained in the CPU.

# 3.2 CPU Registers

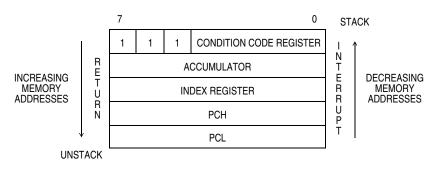

The MCU contains five registers as shown in the programming model of Figure 3-1. The interrupt stacking order is shown in Figure 3-2.

Figure 3-1. Programming Model

Figure 3-2. Interrupt Stacking Order

# Chapter 5 Resets

# 5.1 Introduction

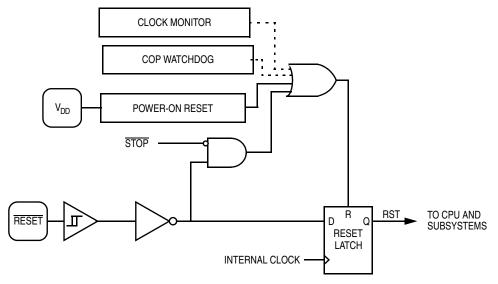

The MCU can be reset four ways: by the initial power-on reset function, by an active low input to the RESET pin, by the COP, or by the clock monitor. A reset immediately stops the operation of the instruction being executed, initializes some control bits, and loads the program counter with a user-defined reset vector address. Figure 5-1 is a block diagram of the reset sources.

Figure 5-1. Reset Sources

# 5.2 Power-On Reset (POR)

A power-on-reset occurs when a positive transition is detected on  $V_{DD}$ . The power-on reset is strictly for power turn-on conditions and should not be used to detect a drop in the power supply voltage. There is a 4064 internal processor clock cycle ( $t_{cyc}$ ) oscillator stabilization delay after the oscillator becomes active. (When configured as a C9A, the RESET pin will output a logic 0 during the 4064-cycle delay.) If the RESET pin is low after the end of this 4064-cycle delay, the MCU will remain in the reset condition until RESET is driven high externally.

# 5.3 RESET Pin

The function of the RESET pin is dependent on whether the device is configured as an MC68HC05C9A or an MC68HC05C12A. When it is in the MC68HC05C12A configuration, the pin is input only. When in MC68HC05C9A configuration the pin is bidirectional. In both cases the MCU is reset when a logic 0 is applied to the RESET pin for a period of one and one-half machine cycles ( $t_{RL}$ ). For the MC68HC05C9A configuration, the RESET pin will be driven low by a COP, clock monitor, or power-on reset.

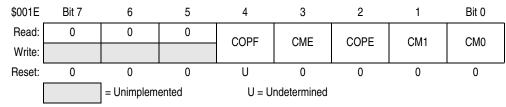

Figure 5-5. COP Control Register (COPCR)

### **COPF** — Computer Operating Properly Flag

Reading the COP control register clears COPF.

1 = COP or clock monitor reset has occurred.

0 = No COP or clock monitor reset has occurred.

#### CME — Clock Monitor Enable Bit

This bit is readable any time, but may be written only once.

1 = Clock monitor enabled

0 = Clock monitor disabled

#### COPE — COP Enable Bit

This bit is readable any time. COPE, CM1, and CM0 together may be written with a single write, only once, after reset. This bit is cleared by reset.

1 = COP enabled

0 = COP disabled

#### CM1 — COP Mode Bit 1

Used in conjunction with CM0 to establish the COP timeout period, this bit is readable any time. COPE, CM1, and CM0 together may be written with a single write, only once, after reset. This bit is cleared by reset.

#### CM0 — COP Mode Bit 0

Used in conjunction with CM1 to establish the COP timeout period, this bit is readable any time. COPE, CM1, and CM0 together may be written with a single write, only once, after reset. This bit is cleared by reset.

#### Bits 7–5 — Not Used

These bits always read as 0.

| CM1 | СМО | f <sub>op</sub> /2 <sup>15</sup> Divide By | Timeout Period<br>(f <sub>osc</sub> = 2.0 MHz) | Timeout Period<br>(f <sub>osc</sub> = 4.0 MHz) |

|-----|-----|--------------------------------------------|------------------------------------------------|------------------------------------------------|

| 0   | 0   | 1                                          | 32.77 ms                                       | 16.38 ms                                       |

| 0   | 1   | 4                                          | 131.07 ms                                      | 65.54 ms                                       |

| 1   | 0   | 16                                         | 524.29 ms                                      | 262.14 ms                                      |

| 1   | 1   | 64                                         | 2.097 sec                                      | 1.048 sec                                      |

Table 5-1. COP Timeout Period

# 5.6 MC68HC05C12A Compatible COP

This COP is implemented with an 18-bit ripple counter. This provides a timeout period of 64 milliseconds at a bus rate ( $f_{op}$ ) of 2 MHz. If the COP should time out, a system reset will occur and the device will be re-initialized in the same fashion as a power-on reset or reset.

Capture/Compare Timer

# 8.2 Timer Operation

The core of the capture/compare timer is a 16-bit free-running counter. The counter provides the timing reference for the input capture and output compare functions. The input capture and output compare functions provide a means to latch the times at which external events occur, to measure input waveforms, and to generate output waveforms and timing delays. Software can read the value in the 16-bit free-running counter at any time without affecting the counter sequence.

Because of the 16-bit timer architecture, the I/O registers for the input capture and output compare functions are pairs of 8-bit registers.

Because the counter is 16 bits long and preceded by a fixed divide-by-4 prescaler, the counter rolls over every 262,144 internal clock cycles. Timer resolution with a 4-MHz crystal is 2  $\mu$ s.

### 8.2.1 Input Capture

The input capture function is a means to record the time at which an external event occurs. When the input capture circuitry detects an active edge on the TCAP pin, it latches the contents of the timer registers into the input capture registers. The polarity of the active edge is programmable.

Latching values into the input capture registers at successive edges of the same polarity measures the period of the input signal on the TCAP pin. Latching values into the input capture registers at successive edges of opposite polarity measures the pulse width of the signal.

### 8.2.2 Output Compare

The output compare function is a means of generating an output signal when the 16-bit counter reaches a selected value. Software writes the selected value into the output compare registers. On every fourth internal clock cycle the output compare circuitry compares the value of the counter to the value written in the output compare registers. When a match occurs, the timer transfers the programmable output level bit (OLVL) from the timer control register to the TCMP pin.

The programmer can use the output compare register to measure time periods, to generate timing delays, or to generate a pulse of specific duration or a pulse train of specific frequency and duty cycle on the TCMP pin.

## 8.3 Timer I/O Registers

The following I/O registers control and monitor timer operation:

- Timer control register (TCR)

- Timer status register (TSR)

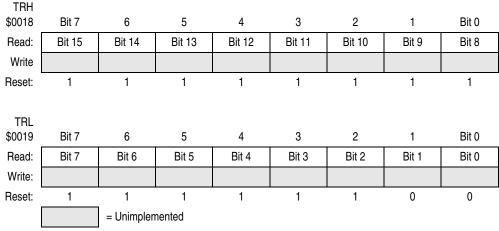

- Timer registers (TRH and TRL)

- Alternate timer registers (ATRH and ATRL)

- Input capture registers (ICRH and ICRL)

- Output compare registers (OCRH and OCRL)

### 8.3.3 Timer Registers

The timer registers (TRH and TRL), shown in Figure 8-4, contains the current high and low bytes of the 16-bit counter. Reading TRH before reading TRL causes TRL to be latched until TRL is read. Reading TRL after reading the timer status register clears the timer overflow flag (TOF). Writing to the timer registers has no effect.

Figure 8-4. Timer Registers (TRH and TRL)

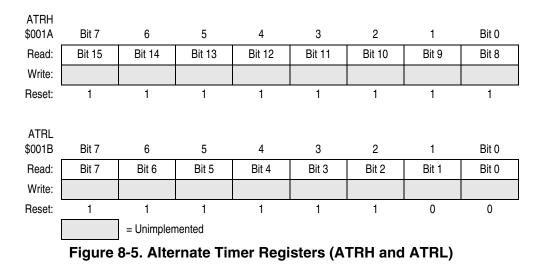

### 8.3.4 Alternate Timer Registers

The alternate timer registers (ATRH and ATRL), shown in Figure 8-5, contain the current high and low bytes of the 16-bit counter. Reading ATRH before reading ATRL causes ATRL to be latched until ATRL is read. Reading ATRL has no effect on the timer overflow flag (TOF). Writing to the alternate timer registers has no effect.

NOTE

To prevent interrupts from occurring between readings of ATRH and ATRL, set the interrupt flag in the condition code register before reading ATRH, and clear the flag after reading ATRL.

Capture/Compare Timer

#### Serial Peripheral Interface (SPI)

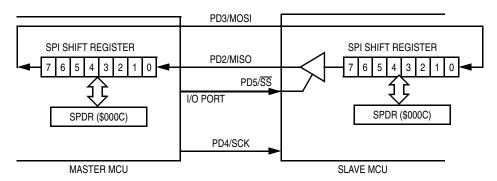

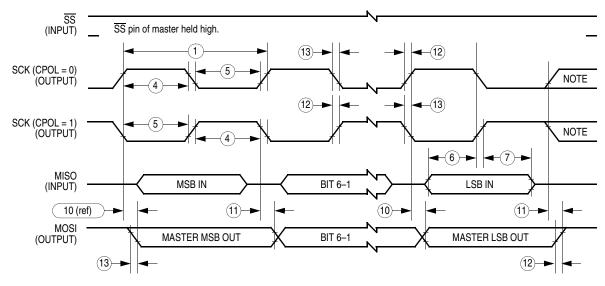

The SPI is double buffered on read, but not on write. If a write is performed during data transfer, the transfer occurs uninterrupted, and the write will be unsuccessful. This condition will cause the write collision (WCOL) status bit in the SPSR to be set. After a data byte is shifted, the SPIF flag of the SPSR is set.

In the master mode, the SCK pin is an output. It idles high or low, depending on the CPOL bit in the SPCR, until data is written to the shift register, at which point eight clocks are generated to shift the eight bits of data and then SCK goes idle again.

In a slave mode, the slave select start logic receives a logic low at the  $\overline{SS}$  pin and a clock at the SCK pin. Thus, the slave is synchronized with the master. Data from the master is received serially at the MOSI line and loads the 8-bit shift register. After the 8-bit shift register is loaded, its data is parallel transferred to the read buffer. During a write cycle, data is written into the shift register, then the slave waits for a clock train from the master to shift the data out on the slave's MISO line.

Figure 10-3 illustrates the MOSI, MISO, SCK, and SS master-slave interconnections.

Figure 10-3. Serial Peripheral Interface Master-Slave Interconnection

# 10.5 SPI Registers

Three registers in the SPI provide control, status, and data storage functions. These registers are called the serial peripheral control register (SPCR), serial peripheral status register (SPSR), and serial peripheral data I/O register (SPDR) and are described in the following paragraphs.

### 10.5.1 Serial Peripheral Control Register

The SPI control register (SPCR), shown in Figure 10-4, controls these functions:

- Enables SPI interrupts

- Enables the SPI system

- Selects between standard CMOS or open drain outputs for port D (C9A mode only)

- Selects between master mode and slave mode

- · Controls the clock/data relationship between master and slave

- Determines the idle level of the clock pin

### 11.2.4 Extended

Extended instructions use three bytes and can access any address in memory. The first byte is the opcode; the second and third bytes are the high and low bytes of the operand address.

When using the Freescale assembler, the programmer does not need to specify whether an instruction is direct or extended. The assembler automatically selects the shortest form of the instruction.

### 11.2.5 Indexed, No Offset

Indexed instructions with no offset are 1-byte instructions that can access data with variable addresses within the first 256 memory locations. The index register contains the low byte of the effective address of the operand. The CPU automatically uses \$00 as the high byte, so these instructions can address locations \$0000-\$00FF.

Indexed, no offset instructions are often used to move a pointer through a table or to hold the address of a frequently used random-access memory (RAM) or input/output (I/O) location.

### 11.2.6 Indexed, 8-Bit Offset

Indexed, 8-bit offset instructions are 2-byte instructions that can access data with variable addresses within the first 511 memory locations. The CPU adds the unsigned byte in the index register to the unsigned byte following the opcode. The sum is the effective address of the operand. These instructions can access locations \$0000-\$01FE.

Indexed 8-bit offset instructions are useful for selecting the kth element in an n-element table. The table can begin anywhere within the first 256 memory locations and could extend as far as location 510 (\$01FE). The k value is typically in the index register, and the address of the beginning of the table is in the byte following the opcode.

### 11.2.7 Indexed, 16-Bit Offset

Indexed, 16-bit offset instructions are 3-byte instructions that can access data with variable addresses at any location in memory. The CPU adds the unsigned byte in the index register to the two unsigned bytes following the opcode. The sum is the effective address of the operand. The first byte after the opcode is the high byte of the 16-bit offset; the second byte is the low byte of the offset.

Indexed, 16-bit offset instructions are useful for selecting the kth element in an n-element table anywhere in memory.

As with direct and extended addressing, the Freescale assembler determines the shortest form of indexed addressing.

### 11.2.8 Relative

Relative addressing is only for branch instructions. If the branch condition is true, the CPU finds the effective branch destination by adding the signed byte following the opcode to the contents of the program counter. If the branch condition is not true, the CPU goes to the next instruction. The offset is a signed, two's complement byte that gives a branching range of -128 to +127 bytes from the address of the next location after the branch instruction.

When using the Freescale assembler, the programmer does not need to calculate the offset, because the assembler determines the proper offset and verifies that it is within the span of the branch.

Instruction Set

| Source<br>Form                                                     | Operation                             | Description                                                                                                                                                                    |          |   | Effect<br>on CCR |   |   | Address<br>Mode                                                                                          | Opcode                           | Operand                                            | Cycles                                         |

|--------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|------------------|---|---|----------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------|------------------------------------------------|

| Form                                                               | ·                                     |                                                                                                                                                                                | Η        | I | Ν                | Z | С | Ado<br>Me                                                                                                | ď                                | Ope                                                | S                                              |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT ,X | Bit Test Accumulator with Memory Byte | (A) ∧ (M)                                                                                                                                                                      |          |   | ţ                | ţ |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                                                    | A5<br>B5<br>C5<br>D5<br>E5<br>F5 | dd<br>hh ll                                        |                                                |

| BLO rel                                                            | Branch if Lower (Same as BCS)         | PC ← (PC) + 2 + <i>rel</i> ? C = 1                                                                                                                                             |          |   | —                |   |   | REL                                                                                                      | 25                               | rr                                                 | 3                                              |

| BLS rel                                                            | Branch if Lower or Same               | $PC \leftarrow (PC) + 2 + \mathit{rel} ? C \lor Z = 1$                                                                                                                         |          | — | —                |   | — | REL                                                                                                      | 23                               | rr                                                 | 3                                              |

| BMC rel                                                            | Branch if Interrupt Mask Clear        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? I = 0$                                                                                                                                | —        | — | —                | — | — | REL                                                                                                      | 2C                               | rr                                                 | 3                                              |

| BMI <i>rel</i>                                                     | Branch if Minus                       | PC ← (PC) + 2 + <i>rel</i> ? N = 1                                                                                                                                             | —        | — | —                | — | — | REL                                                                                                      | 2B                               | rr                                                 | 3                                              |

| BMS rel                                                            | Branch if Interrupt Mask Set          | PC ← (PC) + 2 + <i>rel</i> ? I = 1                                                                                                                                             | -        | — | —                | — | — | REL                                                                                                      | 2D                               | rr                                                 | 3                                              |

| BNE <i>rel</i>                                                     | Branch if Not Equal                   | $PC \leftarrow (PC) + 2 + \mathit{rel} ? Z = 0$                                                                                                                                | 1—       | — | —                | — |   | REL                                                                                                      | 26                               | rr                                                 | 3                                              |

| BPL <i>rel</i>                                                     | Branch if Plus                        | $PC \leftarrow (PC) + 2 + rel ? N = 0$                                                                                                                                         | —        | — | —                |   | — | REL                                                                                                      | 2A                               | rr                                                 | 3                                              |

| BRA rel                                                            | Branch Always                         | PC ← (PC) + 2 + <i>rel</i> ? 1 = 1                                                                                                                                             |          | — | —                |   |   | REL                                                                                                      | 20                               | rr                                                 | 3                                              |

| BRCLR n opr rel                                                    | Branch if Bit n Clear                 | PC ← (PC) + 2 + <i>rel</i> ? Mn = 0                                                                                                                                            |          |   |                  |   | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b5)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 05<br>07<br>09<br>0B<br>0D       | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BRN <i>rel</i>                                                     | Branch Never                          | $PC \leftarrow (PC) + 2 + \mathit{rel} ? 1 = 0$                                                                                                                                | <b> </b> | — | -                |   | — | REL                                                                                                      | 21                               | rr                                                 | 3                                              |

| BRSET n opr rel                                                    | Branch if Bit n Set                   | PC ← (PC) + 2 + <i>rel</i> ? Mn = 1                                                                                                                                            |          |   |                  |   | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 04<br>06<br>08<br>0A<br>0C       | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BSET n opr                                                         | Set Bit n                             | Mn ← 1                                                                                                                                                                         |          |   |                  |   |   | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 12<br>14<br>16<br>18<br>1A<br>1C | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd             | 5 5 5 5 5 5 5 5                                |

| BSR rel                                                            | Branch to Subroutine                  | $\begin{array}{c} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$ | _        | _ |                  | _ | _ | REL                                                                                                      | AD                               | rr                                                 | 6                                              |

| CLC                                                                | Clear Carry Bit                       | $C \leftarrow 0$                                                                                                                                                               | —        |   | —                | — | 0 | INH                                                                                                      | 98                               |                                                    | 2                                              |

| CLI                                                                | Clear Interrupt Mask                  | l ← 0                                                                                                                                                                          |          | 0 | —                | — | - | INH                                                                                                      | 9A                               |                                                    | 2                                              |

# Table 11-6. Instruction Set Summary (Sheet 2 of 6)

| Source<br>Form                                                     | Operation                                           | Description                                                                                                                                                                                                                                                                                                                                              |   |   | Effect<br>on CCR |   |   | Effect<br>on CCR<br>I N Z C P<br>V V V |                                  |                                  | Opcode                | Operand | Cycles |

|--------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|---|---|----------------------------------------|----------------------------------|----------------------------------|-----------------------|---------|--------|

| Form                                                               |                                                     |                                                                                                                                                                                                                                                                                                                                                          | н | I | Ν                | z | С | Ado                                    | opo                              | Ope                              | Š                     |         |        |

| RTI                                                                | Return from Interrupt                               | $\begin{array}{c} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ \qquad SP \leftarrow (SP) + 1;  Pull  (A) \\ \qquad SP \leftarrow (SP) + 1;  Pull  (X) \\ \qquad SP \leftarrow (SP) + 1;  Pull  (PCH) \\ \qquad SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$                                                                                              | ţ | ţ | ţ                | ţ | ţ | INH                                    | 80                               |                                  | 9                     |         |        |

| RTS                                                                | Return from Subroutine                              | $SP \leftarrow (SP) + 1$ ; Pull (PCH)<br>$SP \leftarrow (SP) + 1$ ; Pull (PCL)                                                                                                                                                                                                                                                                           | _ | _ |                  | _ |   | INH                                    | 81                               |                                  | 6                     |         |        |

| SBC #opr<br>SBC opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC ,X | Subtract Memory Byte and Carry Bit from Accumulator | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                                                                                                                                           |   |   | ţ                | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX  | A2<br>B2<br>C2<br>D2<br>E2<br>F2 | ii<br>dd<br>hh II<br>ee ff<br>ff |                       |         |        |

| SEC                                                                | Set Carry Bit                                       | C ← 1                                                                                                                                                                                                                                                                                                                                                    |   | — | _                |   | 1 | INH                                    | 99                               |                                  | 2                     |         |        |

| SEI                                                                | Set Interrupt Mask                                  | l ← 1                                                                                                                                                                                                                                                                                                                                                    |   | 1 |                  |   |   | INH                                    | 9B                               |                                  | 2                     |         |        |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X             | Store Accumulator in Memory                         | M ← (A)                                                                                                                                                                                                                                                                                                                                                  | _ | _ | ţ                | ţ | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX         | B7<br>C7<br>D7<br>E7<br>F7       | dd<br>hh II<br>ee ff<br>ff       |                       |         |        |

| STOP                                                               | Stop Oscillator and Enable IRQ Pin                  |                                                                                                                                                                                                                                                                                                                                                          | — | 0 |                  | — | — | INH                                    | 8E                               |                                  | 2                     |         |        |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX ,X             | Store Index Register In Memory                      | $M \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                       |   |   | ţ                | ţ |   | DIR<br>EXT<br>IX2<br>IX1<br>IX         | BF<br>CF<br>DF<br>EF<br>FF       | dd<br>hh ll<br>ee ff<br>ff       |                       |         |        |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB ,X | Subtract Memory Byte from Accumulator               | A ← (A) − (M)                                                                                                                                                                                                                                                                                                                                            |   |   | ţ                | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX  | A0<br>B0<br>C0<br>D0<br>E0<br>F0 | ii<br>dd<br>hh II<br>ee ff<br>ff |                       |         |        |

| SWI                                                                | Software Interrupt                                  | $\begin{array}{c} PC \leftarrow (PC) + 1; Push (PCL) \\ SP \leftarrow (SP) - 1; Push (PCH) \\ SP \leftarrow (SP) - 1; Push (X) \\ SP \leftarrow (SP) - 1; Push (A) \\ SP \leftarrow (SP) - 1; Push (CCR) \\ SP \leftarrow (SP) - 1; I \leftarrow 1 \\ PCH \leftarrow Interrupt Vector High Byte \\ PCL \leftarrow Interrupt Vector Low Byte \end{array}$ |   | 1 |                  |   |   | INH                                    | 83                               |                                  | 1<br>0                |         |        |

| ТАХ                                                                | Transfer Accumulator to Index Register              | $X \gets (A)$                                                                                                                                                                                                                                                                                                                                            | _ | — |                  | _ |   | INH                                    | 97                               |                                  | 2                     |         |        |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X                     | Test Memory Byte for Negative or Zero               | (M) – \$00                                                                                                                                                                                                                                                                                                                                               |   |   | ţ                | ţ |   | DIR<br>INH<br>INH<br>IX1<br>IX         | 3D<br>4D<br>5D<br>6D<br>7D       | dd<br>ff                         | 4<br>3<br>3<br>5<br>4 |         |        |

### Table 11-6. Instruction Set Summary (Sheet 5 of 6)

## 12.5 5.0-Vdc Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                                                                              | Symbol                              | Min                                                                  | Typ <sup>(2)</sup>       | Max                          | Unit                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|--------------------------|------------------------------|----------------------|

| Output voltage<br>$I_{Load} = 10.0 \ \mu A$<br>$I_{Load} = -10.0 \ \mu A$                                                                                                                                                  | V <sub>OL</sub><br>V <sub>OH</sub>  | <br>V <sub>DD</sub> –0.1                                             |                          | 0.1                          | V                    |

| Output high voltage<br>$(I_{Load} = -0.8 \text{ mA}) \text{ PA7-PA0}, \text{ PB7-PB0}, \text{ PC6-PC0},$<br>TCMP, PD7, PD0<br>$(I_{Load} = -1.6 \text{ mA}) \text{ PD5-PD1}$<br>$(I_{Load} = -5.0 \text{ mA}) \text{ PC7}$ | V <sub>OH</sub>                     | V <sub>DD</sub> -0.8<br>V <sub>DD</sub> -0.8<br>V <sub>DD</sub> -0.8 |                          | <br>                         | V                    |

| Output low voltage<br>(I <sub>Load</sub> = 1.6 mA) PA7–PA0, PB7–PB0, PC6–PC0,<br>PD7, PD5–PD0, TCMP<br>(I <sub>Load</sub> = 10 mA) PC7                                                                                     | V <sub>OL</sub>                     |                                                                      |                          | 0.4<br>0.4                   | v                    |

| Input high voltage<br>PA7–PA0, PB7–PB0, PC7–PC0, PD7,<br>PD5–PD0, TCAP, IRQ, RESET, OSC1                                                                                                                                   | V <sub>IH</sub>                     | $0.7 	imes V_{DD}$                                                   | _                        | V <sub>DD</sub>              | V                    |

| Input low voltage<br>PA7–PA0, PB7–PB0, PC7–PC0, PD7,<br>PD5–PD0, TCAP, IRQ, RESET, OSC1                                                                                                                                    | V <sub>IL</sub>                     | V <sub>SS</sub>                                                      | _                        | $0.2 \times V_{DD}$          | V                    |

| Supply current (4.5–5.5 Vdc @ f <sub>OP</sub> = 2.1 MHz)<br>Run <sup>(3)</sup><br>Wait <sup>(4)</sup><br>Stop <sup>(5)</sup><br>25°C<br>-40 to 85 °C                                                                       | I <sub>DD</sub>                     | <br>                                                                 | 3.5<br>1.0<br>1.0<br>7.0 | 5.25<br>3.25<br>20.0<br>50.0 | mA<br>mA<br>μA<br>μA |

| I/O ports hi-Z leakage current<br>PA7–PA0, PB7–PB0 (without pullup)<br>PC7–PC0, PD7, PD5–PD0                                                                                                                               | I <sub>OZ</sub>                     | _                                                                    | _                        | 10                           | μA                   |

| Input current<br>RESET, IRQ, OSC1, TCAP, PD7, PD5–PD0                                                                                                                                                                      | l <sub>in</sub>                     | —                                                                    | _                        | 1                            | μA                   |

| Input pullup current <sup>(6)</sup><br>PB7–PB0 (with pullup)                                                                                                                                                               | l <sub>in</sub>                     | 5                                                                    | —                        | 60                           | μA                   |

| Capacitance<br>Ports (as input or output)<br>RESET, IRQ, OSC1, TCAP, PD7, PD5, PD0                                                                                                                                         | C <sub>Out</sub><br>C <sub>In</sub> |                                                                      | _                        | 12<br>8                      | pF                   |

| Programming voltage (25°C)                                                                                                                                                                                                 | V <sub>PP</sub>                     | 15.0                                                                 | 16.0                     | 17.0                         | V                    |

| Programming current (25°C)                                                                                                                                                                                                 | I <sub>PP</sub>                     | —                                                                    | —                        | 200                          | mA                   |

1.  $V_{\text{DD}}$  = 5.0 Vdc  $\pm$  10%,  $V_{\text{SS}}$  = 0 Vdc,  $T_{\text{A}}$  = –40 to +85 °C, unless otherwise noted

Typical values reflect measurements taken on average processed devices at the midpoint of voltage range, 25 °C only.

Run (operating) I<sub>DD</sub> measured using external square wave clock source; all I/O pins configured as inputs, port B = V<sub>DD</sub>, all other inputs V<sub>IL</sub> = 0.2 V, V<sub>IH</sub> = V<sub>DD</sub>-0.2 V; no DC loads; less than 50 pF on all outputs; C<sub>L</sub> = 20 pF on OSC2

4. Wait  $I_{DD}$  measured using external square wave clock source; all I/O pins configured as inputs, port B = V<sub>DD</sub>, all other inputs  $V_{IL} = 0.2 \text{ V}$ ,  $V_{IH} = V_{DD} - 0.2 \text{ V}$ ; no DC loads; less than 50 pF on all outputs;  $C_L = 20 \text{ pF}$  on OSC2. Wait  $I_{DD}$  is affected linearly by the OSC2 capacitance.

5. Stop I<sub>DD</sub> measured with OSC1 = 0.2 V; all I/O pins configured as inputs, port B = V<sub>DD</sub>, all other inputs V<sub>IL</sub> = 0.2 V,  $V_{IH} = V_{DD} - 0.2 V$ .

6. Input pullup current measured with  $V_{IL} = 0.2 V$ .

**Electrical Specifications**

# 12.7 5.0-Vdc Control Timing

| Characteristic <sup>(1)</sup>                                                                 | Symbol                                                                      | Min               | Max        | Unit                                       |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------|------------|--------------------------------------------|

| Frequency of operation<br>Crystal<br>External clock                                           | fosc                                                                        | <br>DC            | 4.2<br>4.2 | MHz                                        |

| Internal pperating frequency (f <sub>OSC</sub> ÷ 2)<br>Crystal<br>External clock              | f <sub>OP</sub>                                                             | <br>DC            | 2.1<br>2.1 | MHz                                        |

| Cycle time                                                                                    | t <sub>CYC</sub>                                                            | 480               | —          | ns                                         |

| Crystal oscillator startup time                                                               | toxov                                                                       | —                 | 100        | ms                                         |

| Stop recovery startup time (crystal oscillator)                                               | t <sub>ILCH</sub>                                                           | —                 | 100        | ms                                         |

| RESET pulse width                                                                             | t <sub>RL</sub>                                                             | 1.5               | —          | t <sub>CYC</sub>                           |

| Timer<br>Resolution <sup>(2)</sup><br>Input capture pulse width<br>Input capture pulse period | t <sub>RESL</sub><br>t <sub>TH</sub> , t <sub>TL</sub><br>t <sub>TLTL</sub> | 4.0<br>125<br>(3) |            | t <sub>CYC</sub><br>ns<br>t <sub>CYC</sub> |

| Interrupt pulse width low (edge-triggered)                                                    | t <sub>ILIH</sub>                                                           | 125               | —          | ns                                         |

| Interrupt pulse period                                                                        | t <sub>ILIL</sub>                                                           | (4)               | —          | t <sub>CYC</sub>                           |

| OSC1 pulse width                                                                              | t <sub>OH</sub> ,t <sub>OL</sub>                                            | 90                | _          | ns                                         |

1.  $V_{DD}$  = 5.0 Vdc ± 10%,  $V_{SS}$  = 0 Vdc,  $T_A$  = -40 to +85 °C, unless otherwise noted 2. Because a 2-bit prescaler in the timer must count four internal cycles ( $t_{CYC}$ ), this is the limiting minimum factor in determining the timer resolution.

3. The minimum period t<sub>TLTL</sub> should not be less than the number of cycle times it takes to execute the capture interrupt service

routine plus 24  $t_{CYC}$ . 4. The minimum  $t_{ILIL}$  should not be less than the number of cycle times it takes to execute the interrupt service routine plus 19 t<sub>CYC</sub>.

#### **Electrical Specifications**

#### Note:

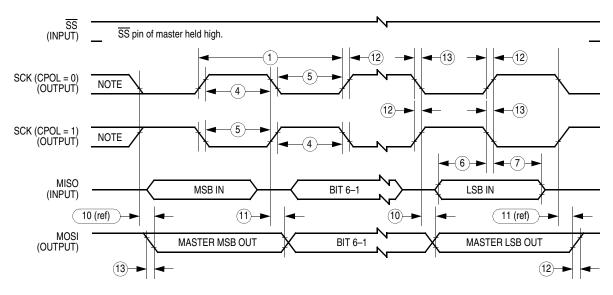

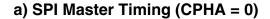

This first clock edge is generated internally, but is not seen at the SCK pin.

Note: This last clock edge is generated internally, but is not seen at the SCK pin.

b) SPI Master Timing (CPHA = 1)

Figure 12-9. SPI Master Timing Diagram