Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC05                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 2.1MHz                                                                  |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 24                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 352 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc705c9acfn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr.  | Register Name                          |                 | Bit 7  | 6          | 5      | 4        | 3           | 2      | 1          | Bit 0 |

|--------|----------------------------------------|-----------------|--------|------------|--------|----------|-------------|--------|------------|-------|

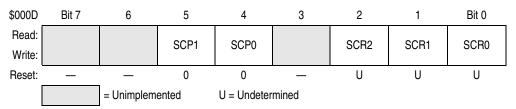

| \$000D | SCI Baud Rate Register<br>BAUD         | Read:<br>Write: |        |            | SCP1   | SCP0     |             | SCR2   | SCR1       | SCR0  |

|        | See page 69.                           | Reset:          | _      | _          | 0      | 0        | _           | U      | U          | U     |

| \$000E | SCI Control Register 1 (SCCR1)         | Read:<br>Write: | R8     | T8         |        | М        | WAKE        |        |            |       |

|        | See page 65.                           | Reset:          | U      | U          | 0      | U        | U           | 0      | 0          | 0     |

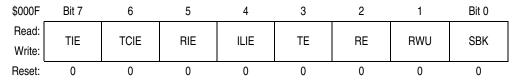

| \$000F | SCI Control Register 2<br>(SCCR2)      | Read:<br>Write: | TIE    | TCIE       | RIE    | ILIE     | TE          | RE     | RWU        | SBK   |

|        | See page 66.                           | Reset:          | 0      | 0          | 0      | 0        | 0           | 0      | 0          | 0     |

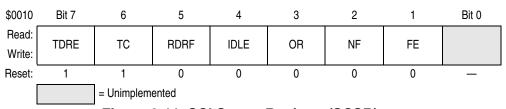

|        | SCI Status Register                    | Read:           | TDRE   | TC         | RDRF   | IDLE     | OR          | NF     | FE         |       |

| \$0010 | (SCSR)                                 | Write:          |        |            |        |          |             |        |            |       |

|        | See page 68.                           | Reset:          | 1      | 1          | 0      | 0        | 0           | 0      | 0          | _     |

| \$0011 | SCI Data Register<br>(SCDR)            | Read:<br>Write: | SCD7   | SDC6       | SCD5   | SCD4     | SCD3        | SCD2   | SCD1       | SCD0  |

|        | See page 65.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

|        | Timer Control Register                 | Read:           | ICIE   | OCIE       | TOIE   | 0        | 0           | 0      | IEDG       | OLVL  |

| \$0012 | (TCR)                                  | Write:          | IOIL   | OOIL TOIL  | TOIL   |          |             |        | ILDU       | OLVL  |

|        | See page 53.                           | Reset:          | 0      | 0          | 0      | 0        | 0           | 0      | U          | 0     |

|        | Timer Status Register                  | Read:           | ICF    | OCF        | TOF    | 0        | 0           | 0      | 0          | 0     |

| \$0013 | (TSR)                                  | Write:          |        |            |        |          |             |        |            |       |

|        | See page 54.                           | Reset:          | U      | U          | U      | 0        | 0           | 0      | 0          | 0     |

|        | Input Capture Register High            | Read:           | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10 | Bit 9      | Bit 8 |

| \$0014 | \$0014 (ICRH)                          |                 |        |            |        |          |             |        |            |       |

|        | See page 56.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

|        | Input Capture Register Low             | Read:           | Bit 7  | Bit 6      | Bit 5  | Bit 4    | Bit 3       | Bit 2  | Bit 1      | Bit 0 |

| \$0015 | (ICRL)                                 | Write:          |        |            |        |          |             |        |            |       |

|        | See page 56.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

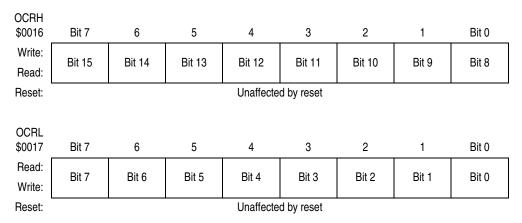

| \$0016 | Output Compare Register<br>High (OCRH) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10 | Bit 9      | Bit 8 |

|        | See page 56.                           | Reset:          |        |            | •      | Unaffect | ed by reset |        | •          |       |

| \$0017 | Output Compare Register<br>Low (OCRL)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4    | Bit 3       | Bit 2  | Bit 1      | Bit 0 |

|        | See page 56.                           | Reset:          |        |            |        | Unaffect | ed by reset |        |            |       |

|        | Timer Register High                    | Read:           | Bit 15 | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10 | Bit 9      | Bit 8 |

| \$0018 | (TRH)                                  | Write:          |        |            |        |          |             |        |            |       |

|        | See page 55.                           | Reset:          | 1      | 1          | 1      | 1        | 1           | 1      | 1          | 1     |

|        |                                        | [               |        | = Unimpler | mented | R        | = Reserved  |        | U = Unaffe | cted  |

Figure 2-4. Input/Output Registers (Sheet 2 of 3)

# Chapter 5 Resets

#### 5.1 Introduction

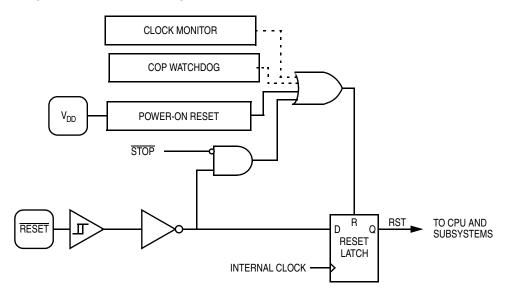

The MCU can be reset four ways: by the initial power-on reset function, by an active low input to the RESET pin, by the COP, or by the clock monitor. A reset immediately stops the operation of the instruction being executed, initializes some control bits, and loads the program counter with a user-defined reset vector address. Figure 5-1 is a block diagram of the reset sources.

Figure 5-1. Reset Sources

# 5.2 Power-On Reset (POR)

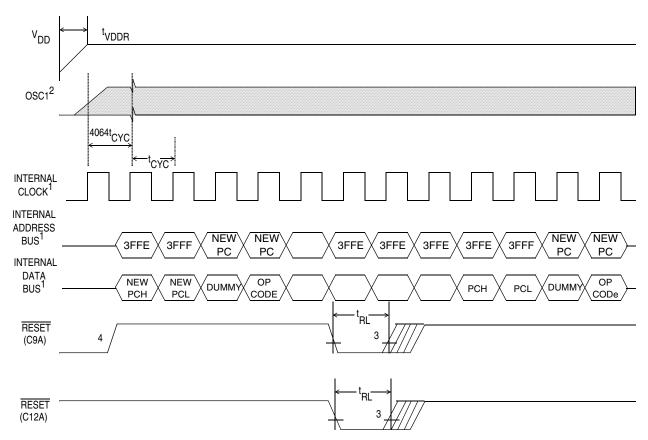

A power-on-reset occurs when a positive transition is detected on  $V_{DD}$ . The power-on reset is strictly for power turn-on conditions and should not be used to detect a drop in the power supply voltage. There is a 4064 internal processor clock cycle  $(t_{cyc})$  oscillator stabilization delay after the oscillator becomes active. (When configured as a C9A, the  $\overline{RESET}$  pin will output a logic 0 during the 4064-cycle delay.) If the  $\overline{RESET}$  pin is low after the end of this 4064-cycle delay, the MCU will remain in the reset condition until  $\overline{RESET}$  is driven high externally.

# 5.3 RESET Pin

The function of the RESET pin is dependent on whether the device is configured as an MC68HC05C9A or an MC68HC05C12A. When it is in the MC68HC05C12A configuration, the pin is input only. When in MC68HC05C9A configuration the pin is bidirectional. In both cases the MCU is reset when a logic 0 is applied to the RESET pin for a period of one and one-half machine cycles (t<sub>RL</sub>). For the MC68HC05C9A configuration, the RESET pin will be driven low by a COP, clock monitor, or power-on reset.

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

#### Resets

#### Notes:

- 1. Internal timing signal and bus information are not available externally.

- 2. OSC1 line is not meant to represent frequency. It is only meant to represent time.

- 3. The next rising edge of the internal processor clock following the rising edge of RESET initiates the reset sequence.

- 4.  $\overline{\text{RESET}}$  outputs  $V_{\text{OL}}$  during 4064 power-on reset cycles when in C9A mode only.

Figure 5-2. Power-On Reset and RESET

# 5.4 Computer Operating Properly (COP) Reset

This device includes a watchdog COP feature which guards against program run-away failures. A timeout of the computer operating properly (COP) timer generates a COP reset. The COP watchdog is a software error detection system that automatically times out and resets the MCU if not cleared periodically by a program sequence.

This device includes two COP types, one for C12A compatibility and the other for C9A compatibility. When configured as a C9A the COP can be enabled by user software by setting COPE in the C9A COP control register (C9ACOPCR). When configured as a C12A, the COP is enabled prior to operation by programming the C12COPE bit in the C12A mask option register (C12MOR). The function and control of both COPs is detailed below.

# **Low-Power Modes**

#### 6.3 Wait Mode

The WAIT instruction places the MCU in a low-power consumption mode, but the wait mode consumes more power than the stop mode. All CPU action is suspended, but the timer, serial communications interface (SCI), serial peripheral interface (SPI), and the oscillator remain active. Any interrupt or reset will cause the MCU to exit the wait mode.

During wait mode, the I bit in the CCR is cleared to enable interrupts. All other registers, memory, and input/output lines remain in their previous state. The timer, SCI, and SPI may be enabled to allow a periodic exit from the wait mode.

Input/Output (I/O) Ports

### **7.3 Port B**

Port B is an 8-bit bidirectional port. The port B data register is at \$0001 and the data direction register (DDR) is at \$0005. The contents of the port B data register are indeterminate at initial powerup and must be initialized by user software. Reset does not affect the data registers, but clears the data direction registers, thereby returning the ports to inputs. Writing a 1 to a DDR bit sets the corresponding port pin to output mode. Each of the port B pins has an optional external interrupt capability that can be enabled by programming the corresponding bit in the port B mask option register (\$3FF0).

The interrupt option also enables a pullup device when the pin is configured as an input. The edge or edge- and level-sensitivity of the  $\overline{\text{IRQ}}$  pin will also pertain to the enabled port B pins. Care needs to be taken when using port B pins that have the pullup enabled. Before switching from an output to an input, the data should be preconditioned to a 1 to prevent an interrupt from occurring. The port B logic is shown in Figure 7-2.

#### 7.4 Port C

Port C is an 8-bit bidirectional port. The port C data register is at \$0002 and the data direction register (DDR) is at \$0006. The contents of the port C data register are indeterminate at initial powerup and must be initialized by user software. Reset does not affect the data registers, but clears the data direction registers, thereby returning the ports to inputs. Writing a 1 to a DDR bit sets the corresponding port bit to output mode. PC7 has a high current sink and source capability. Figure 7-1 is also applicable to port C.

#### **7.5 Port D**

When configured as a C9A, port D is a 7-bit bidirectional port; when configured as a C12A, port D is a 7-bit fixed input port. Four of its pins are shared with the SPI subsystem and two more are shared with the SCI subsystem. The contents of the port D data register are indeterminate at initial powerup and must be initialized by user software. During reset all seven bits become valid input ports because the C9A DDR bits are cleared and the special function output drivers associated with the SCI and SPI subsystems are disabled, thereby returning the ports to inputs. Writing a 1 to a DDR bit sets the corresponding port bit to output mode only when configured as a C9A.

#### Capture/Compare Timer

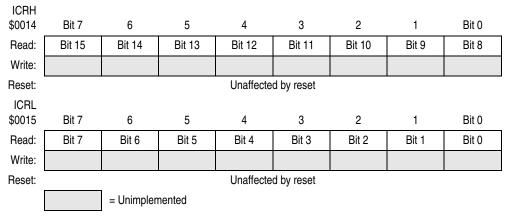

### 8.3.5 Input Capture Registers

When a selected edge occurs on the TCAP pin, the current high and low bytes of the 16-bit counter are latched into the input capture registers (ICRH and ICRL). Reading ICRH before reading ICRL inhibits further capture until ICRL is read. Reading ICRL after reading the status register clears the input capture flag (ICF). Writing to the input capture registers has no effect.

Figure 8-6. Input Capture Registers (ICRH and ICRL)

#### NOTE

To prevent interrupts from occurring between readings of ICRH and ICRL, set the interrupt flag in the condition code register before reading ICRH, and clear the flag after reading ICRL.

# 8.3.6 Output Compare Registers

When the value of the 16-bit counter matches the value in the output compare registers (OCRH and OCRL), the planned TCMP pin action takes place. Writing to OCRH before writing to OCRL inhibits timer compares until OCRL is written. Reading or writing to OCRL after the timer status register clears the output compare flag (OCF).

Figure 8-7. Output Compare Registers (OCRH and OCRL)

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1 56 Freescale Semiconductor

To prevent OCF from being set between the time it is read and the time the output compare registers are updated, use this procedure:

- 1. Disable interrupts by setting the I bit in the condition code register.

- 2. Write to OCRH. Compares are now inhibited until OCRL is written.

- 3. Clear bit OCF by reading timer status register (TSR).

- 4. Enable the output compare function by writing to OCRL.

- 5. Enable interrupts by clearing the I bit in the condition code register.

# 8.4 Timer During Wait Mode

The CPU clock halts during the wait mode, but the timer remains active. If interrupts are enabled, a timer interrupt will cause the processor to exit the wait mode.

# 8.5 Timer During Stop Mode

In the stop mode, the timer stops counting and holds the last count value if STOP is exited by an interrupt. If STOP is exited by reset, the counters are forced to \$FFFC. During STOP, if at least one valid input capture edge occurs at the TCAP pins, the input capture detect circuit is armed. This does not set any timer flags or wake up the MCU, but if an interrupt is used to exit stop mode, there is an active input capture flag and data from the first valid edge that occurred during the stop mode. If reset is used to exit stop mode, then no input capture flag or data remains, even if a valid input capture edge occurred.

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1 Freescale Semiconductor 57

#### **Serial Communications Interface (SCI)**

#### T8 — Bit 8 (Transmitted)

When the SCI is transmitting 9-bit characters, T8 is the ninth bit of the transmitted character. T8 is loaded into the transmit shift register at the same time that the SCDR is loaded into the transmit register. Resets have no effect on the T8 bit.

#### M — Character Length Bit

This read/write bit determines whether SCI characters are 8 bits long or 9 bits long. The ninth bit can be used as an extra stop bit, as a receiver wakeup signal, or as a mark or space parity bit. Resets have no effect on the M bit.

- 1 = 9-bit SCI characters

- 0 = 8-bit SCI characters

## WAKE — Wakeup Method Bit

This read/write bit determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit (MSB) position of a received character or an idle condition on the PD0/RDI pin. Resets have no effect on the WAKE bit.

- 1 = Address mark wakeup

- 0 = Idle line wakeup

# 9.13.3 SCI Control Register 2

SCI control register 2 (SCCR2), shown in Figure 9-10, has these functions:

- Enables the SCI receiver and SCI receiver interrupts

- Enables the SCI transmitter and SCI transmitter interrupts

- Enables SCI receiver idle interrupts

- Enables SCI transmission complete interrupts

- Enables SCI wakeup

- Transmits SCI break characters

Figure 9-10. SCI Control Register 2 (SCCR2)

#### **TIE** — Transmit Interrupt Enable Bit

This read/write bit enables SCI interrupt requests when the TDRE flag becomes set. Resets clear the TIE bit.

- 1 = TDRE interrupt requests enabled

- 0 = TDRE interrupt requests disabled

#### TCIE — Transmission Complete Interrupt Enable Bit

This read/write bit enables SCI interrupt requests when the TC flag becomes set. Resets clear the TCIE bit.

- 1 = TC interrupt requests enabled

- 0 = TC interrupt requests disabled

#### **Serial Communications Interface (SCI)**

Figure 9-11. SCI Status Register (SCSR)

#### TDRE — Transmit Data Register Empty Flag

This clearable, read-only flag is set when the data in the SCDR transfers to the transmit shift register. TDRE generates an interrupt request if the TIE bit in SCCR2 is also set. Clear the TDRE bit by reading the SCSR with TDRE set and then writing to the SCDR. Reset sets the TDRE bit. Software must initialize the TDRE bit to logic 0 to avoid an instant interrupt request when turning the transmitter on.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

#### TC — Transmission Complete Flag

This clearable, read-only flag is set when the TDRE bit is set, and no data, preamble, or break character is being transmitted. TDRE generates an interrupt request if the TCIE bit in SCCR2 is also set. Clear the TC bit by reading the SCSR with TC set, and then writing to the SCDR. Reset sets the TC bit. Software must initialize the TC bit to logic 0 to avoid an instant interrupt request when turning the transmitter on.

- 1 = No transmission in progress

- 0 = Transmission in progress

#### RDRF — Receive Data Register Full Flag

This clearable, read-only flag is set when the data in the receive shift register transfers to the SCI data register. RDRF generates an interrupt request if the RIE bit in the SCCR2 is also set. Clear the RDRF bit by reading the SCSR with RDRF set and then reading the SCDR.

- 1 = Received data available in SCDR

- 0 = Received data not available in SCDR

#### IDLE — Receiver Idle Flag

This clearable, read-only flag is set when 10 or 11 consecutive logic 1s appear on the receiver input. IDLE generates an interrupt request if the ILIE bit in the SCCR2 is also set. Clear the ILIE bit by reading the SCSR with IDLE set and then reading the SCDR.

- 1 = Receiver input idle

- 0 = Receiver input not idle

#### **OR** — Receiver Overrun Flag

This clearable, read-only flag is set if the SCDR is not read before the receive shift register receives the next word. OR generates an interrupt request if the RIE bit in the SCCR2 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading the SCSR with OR set and then reading the SCDR.

- 1 = Receive shift register full and RDRF = 1

- 0 = No receiver overrun

## NF — Receiver Noise Flag

This clearable, read-only flag is set when noise is detected in data received in the SCI data register. Clear the NF bit by reading the SCSR and then reading the SCDR.

- 1 = Noise detected in SCDR

- 0 = No noise detected in SCDR

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

#### FE — Receiver Framing Error Flag

This clearable, read-only flag is set when there is a logic 0 where a stop bit should be in the character shifted into the receive shift register. If the received word causes both a framing error and an overrun error, the OR flag is set and the FE flag is not set. Clear the FE bit by reading the SCSR and then reading the SCDR.

- 1 = Framing error

- 0 = No framing error

# 9.13.5 Baud Rate Register

The baud rate register (BAUD), shown in Figure 9-12, selects the baud rate for both the receiver and the transmitter.

Figure 9-12. Baud Rate Register (BAUD)

#### SCP1 — SCP0-SCI Prescaler Select Bits

These read/write bits control prescaling of the baud rate generator clock, as shown in Table 9-1. Reset clears both SCP1 and SCP0.

| SCP[1:0] | Baud Rate Generator Clock |

|----------|---------------------------|

| 00       | Internal Clock ÷ 1        |

| 01       | Internal Clock ÷ 3        |

| 10       | Internal Clock ÷ 4        |

| 11       | Internal Clock ÷ 13       |

**Table 9-1. Baud Rate Generator Clock Prescaling**

#### SCR2 — SCR0-SCI Baud Rate Select Bits

These read/write bits select the SCI baud rate, as shown in Table 9-2. Resets have no effect on the SCR2–SCR0 bits.

| SCR[2:0] | SCI Baud Rate (Baud)  |

|----------|-----------------------|

| 000      | Prescaled Clock ÷ 1   |

| 001      | Prescaled Clock ÷ 2   |

| 010      | Prescaled Clock ÷ 4   |

| 011      | Prescaled Clock ÷ 8   |

| 100      | Prescaled Clock ÷ 16  |

| 101      | Prescaled Clock ÷ 32  |

| 110      | Prescaled Clock ÷ 64  |

| 111      | Prescaled Clock ÷ 128 |

Table 9-2. Baud Rate Selection

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

#### Instruction Set

#### 11.2.4 Extended

Extended instructions use three bytes and can access any address in memory. The first byte is the opcode; the second and third bytes are the high and low bytes of the operand address.

When using the Freescale assembler, the programmer does not need to specify whether an instruction is direct or extended. The assembler automatically selects the shortest form of the instruction.

#### 11.2.5 Indexed, No Offset

Indexed instructions with no offset are 1-byte instructions that can access data with variable addresses within the first 256 memory locations. The index register contains the low byte of the effective address of the operand. The CPU automatically uses \$00 as the high byte, so these instructions can address locations \$0000–\$00FF.

Indexed, no offset instructions are often used to move a pointer through a table or to hold the address of a frequently used random-access memory (RAM) or input/output (I/O) location.

#### 11.2.6 Indexed, 8-Bit Offset

Indexed, 8-bit offset instructions are 2-byte instructions that can access data with variable addresses within the first 511 memory locations. The CPU adds the unsigned byte in the index register to the unsigned byte following the opcode. The sum is the effective address of the operand. These instructions can access locations \$0000–\$01FE.

Indexed 8-bit offset instructions are useful for selecting the kth element in an n-element table. The table can begin anywhere within the first 256 memory locations and could extend as far as location 510 (\$01FE). The k value is typically in the index register, and the address of the beginning of the table is in the byte following the opcode.

#### 11.2.7 Indexed, 16-Bit Offset

Indexed, 16-bit offset instructions are 3-byte instructions that can access data with variable addresses at any location in memory. The CPU adds the unsigned byte in the index register to the two unsigned bytes following the opcode. The sum is the effective address of the operand. The first byte after the opcode is the high byte of the 16-bit offset; the second byte is the low byte of the offset.

Indexed, 16-bit offset instructions are useful for selecting the kth element in an n-element table anywhere in memory.

As with direct and extended addressing, the Freescale assembler determines the shortest form of indexed addressing.

#### 11.2.8 Relative

Relative addressing is only for branch instructions. If the branch condition is true, the CPU finds the effective branch destination by adding the signed byte following the opcode to the contents of the program counter. If the branch condition is not true, the CPU goes to the next instruction. The offset is a signed, two's complement byte that gives a branching range of –128 to +127 bytes from the address of the next location after the branch instruction.

When using the Freescale assembler, the programmer does not need to calculate the offset, because the assembler determines the proper offset and verifies that it is within the span of the branch.

# 11.4 Instruction Set Summary

Table 11-6. Instruction Set Summary (Sheet 1 of 6)

| Source                                                              | Operation                             | Description                                   | Effe<br>on C |   |   |          | ł | Address<br>Mode                                                         | Opcode                           | Operand                                | Cycles                     |

|---------------------------------------------------------------------|---------------------------------------|-----------------------------------------------|--------------|---|---|----------|---|-------------------------------------------------------------------------|----------------------------------|----------------------------------------|----------------------------|

| Form                                                                | 51111                                 |                                               | Н            | I | N | Z        | С | Adc                                                                     | ob                               | obe                                    | Ş                          |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC ,X  | Add with Carry                        | A ← (A) + (M) + (C)                           | ‡            | _ | ‡ | ‡        | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A9<br>B9<br>C9<br>D9<br>E9<br>F9 | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| ADD #opr<br>ADD opr<br>ADD opr,<br>ADD opr,X<br>ADD opr,X<br>ADD ,X | Add without Carry                     | A ← (A) + (M)                                 | 1            |   | 1 | 1        | Î | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | AB<br>BB<br>CB<br>DB<br>EB<br>FB | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X  | Logical AND                           | $A \leftarrow (A) \wedge (M)$                 |              | _ | ‡ | <b>‡</b> |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A4<br>B4<br>C4<br>D4<br>E4<br>F4 | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X                      | Arithmetic Shift Left (Same as LSL)   | —————————————————————————————————————         |              | _ | ‡ | ‡        | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 38<br>48<br>58<br>68<br>78       | dd<br>ff                               | 5<br>3<br>6<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR ,X                      | Arithmetic Shift Right                | b7 b0                                         | _            | _ | ‡ | ‡        | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 37<br>47<br>57<br>67<br>77       | dd<br>ff                               | 5<br>3<br>3<br>6<br>5      |

| BCC rel                                                             | Branch if Carry Bit Clear             | $PC \leftarrow (PC) + 2 + rel ? C = 0$        | _            | _ | _ | _        | _ | REL                                                                     | 24                               | rr                                     | 3                          |

| BCLR n opr                                                          | Clear Bit n                           | Mn ← 0                                        |              |   |   |          |   | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 15<br>17<br>19<br>1B<br>1D       | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 5 5 5 5 5 5 5              |

| BCS rel                                                             | Branch if Carry Bit Set (Same as BLO) | PC ← (PC) + 2 + rel ? C = 1                   | _            | _ | _ | _        | _ | REL                                                                     | 25                               | rr                                     | 3                          |

| BEQ rel                                                             | Branch if Equal                       | PC ← (PC) + 2 + rel? Z = 1                    | _            | _ | _ |          | _ | REL                                                                     | 27                               | rr                                     | 3                          |

| BHCC rel                                                            | Branch if Half-Carry Bit Clear        | PC ← (PC) + 2 + <i>rel</i> ? H = 0            |              | _ | _ | _        | _ | REL                                                                     | 28                               | rr                                     | 3                          |

| BHCS rel                                                            | Branch if Half-Carry Bit Set          | PC ← (PC) + 2 + <i>rel</i> ? H = 1            |              |   | _ |          | _ | REL                                                                     | 29                               | rr                                     | 3                          |

| BHI rel                                                             | Branch if Higher                      | $PC \leftarrow (PC) + 2 + rel ? C \lor Z = 0$ | _            | _ | _ | _        | _ | REL                                                                     | 22                               | rr                                     | 3                          |

| BHS rel                                                             | Branch if Higher or Same              | $PC \leftarrow (PC) + 2 + rel ? C = 0$        | _            | _ | _ | _        | _ | REL                                                                     | 24                               | rr                                     | 3                          |

| BIH rel                                                             | Branch if IRQ Pin High                | PC ← (PC) + 2 + <i>rel</i> ? IRQ = 1          |              | _ | _ | _        |   | REL                                                                     | 2F                               | rr                                     | 3                          |

| BIL rel                                                             | Branch if IRQ Pin Low                 | $PC \leftarrow (PC) + 2 + rel ? IRQ = 0$      | _            | _ | _ | _        | _ | REL                                                                     | 2E                               | rr                                     | 3                          |

#### **Electrical Specifications**

# 12.6 3.3-Vdc Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                           | Symbol                              | Min                                                                  | Typ <sup>(2)</sup>       | Max                   | Unit                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|--------------------------|-----------------------|----------------------|

| Output voltage $I_{Load} = 10.0 \ \mu A$ $I_{Load} = -10.0 \ \mu A$                                                                                                     | V <sub>OL</sub><br>V <sub>OH</sub>  | <br>V <sub>DD</sub> -0.1                                             |                          | 0.1<br>—              | V                    |

| Output high voltage  (I <sub>Load</sub> = -0.2 mA) PA7-PA0, PB7-PB0, PC6-PC0,  TCMP, PD7, PD0  (I <sub>Load</sub> = -0.4 mA) PD5-PD1  (I <sub>Load</sub> = -1.5 mA) PC7 | V <sub>ОН</sub>                     | V <sub>DD</sub> -0.3<br>V <sub>DD</sub> -0.3<br>V <sub>DD</sub> -0.3 | _<br>_<br>_              | _<br>_<br>_           | V                    |

| Output low voltage (I <sub>Load</sub> = 0.4mA) PA7–PA0, PB7–PB0, PC6–PC0, PD7, PD5–PD0, TCMP (I <sub>Load</sub> = 6 mA) PC7                                             | V <sub>OL</sub>                     |                                                                      |                          | 0.3<br>0.3            | <b>V</b>             |

| Input high voltage PA7–PA0, PB7–PB0, PC7–PC0, PD7, PD5–PD0, TCAP, IRQ, RESET, OSC1                                                                                      | V <sub>IH</sub>                     | $0.7 \times V_{DD}$                                                  | _                        | V <sub>DD</sub>       | V                    |

| Input low voltage PA7-PA0, PB7-PB0, PC7-PC0, PD7, PD5-PD0, TCAP, IRQ, RESET, OSC1                                                                                       | V <sub>IL</sub>                     | V <sub>SS</sub>                                                      | _                        | $0.2 \times V_{DD}$   | V                    |

| Supply current (3.0–3.6 Vdc @ $f_{OP}$ = 1.0 MHz)  Run <sup>(3)</sup> Wait <sup>(4)</sup> Stop <sup>(5)</sup> 25°C  -40 to 85°C                                         | I <sub>DD</sub>                     |                                                                      | 1.0<br>500<br>1.0<br>2.5 | 1.6<br>900<br>8<br>20 | mΑ<br>μΑ<br>μΑ<br>μΑ |

| I/O ports hi-Z leakage current PA7–PA0, PB7–PB0 (without pullup) PC7–PC0, PD7, PD5–PD0                                                                                  | I <sub>OZ</sub>                     | _                                                                    | _                        | 10                    | μΑ                   |

| Input current RESET, IRQ, OSC1, TCAP, PD7, PD5–PD0                                                                                                                      | I <sub>In</sub>                     | _                                                                    | _                        | 1                     | μА                   |

| Input pullup current <sup>(6)</sup> PB7–PB0 (with pullup)                                                                                                               | I <sub>In</sub>                     | 0.5                                                                  | _                        | 20                    | μΑ                   |

| Capacitance Ports (as input or output) RESET, IRQ, OSC1, TCAP, PD7, PD5, PD0                                                                                            | C <sub>Out</sub><br>C <sub>In</sub> |                                                                      | _<br>_                   | 12<br>8               | pF                   |

<sup>1.</sup>  $V_{DD}$  = 3.3 Vdc  $\pm$  0.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  = -40 to +85 °C, unless otherwise noted

6. Input pullup current measured with  $V_{\parallel} = 0.2 \text{ V}$ .

<sup>2.</sup> Typical values reflect measurements taken on average processed devices at the midpoint of voltage range, 25 °C only.

<sup>3.</sup> Run (operating) I<sub>DD</sub> measured using external square wave clock source; all I/O pins configured as inputs, port B = V<sub>DD</sub>, all other inputs V<sub>IL</sub> = 0.2 V, V<sub>IH</sub> = V<sub>DD</sub>-0.2 V; no DC loads; less than 50 pF on all outputs; C<sub>L</sub> = 20 pF on OSC2

4. Wait I<sub>DD</sub> measured using external square wave clock source; all I/O pins configured as inputs, port B = V<sub>DD</sub>, all other inputs V<sub>IL</sub> = 0.2 V, V<sub>IH</sub> = V<sub>DD</sub>-0.2 V; no DC loads; less than 50 pF on all outputs; C<sub>L</sub> = 20 pF on OSC2. Wait I<sub>DD</sub> is affected linearly by the OSC2 capacitance. by the OSC2 capacitance.

<sup>5.</sup> Stop  $I_{DD}$  measured with OSC1 = 0.2 V; all I/O pins configured as inputs, port B =  $V_{DD}$ , all other inputs  $V_{IL}$  = 0.2 V,  $V_{IH} = V_{DD} - 0.2 \text{ V}.$

# **Electrical Specifications**

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

# **Chapter 13 Mechanical Specifications**

# 13.1 Introduction

This section describes the dimensions of the plastic dual in-line package (DIP), plastic shrink dual in-line package (SDIP), plastic leaded chip carrier (PLCC), and quad flat pack (QFP) MCU packages.

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Sales Office.

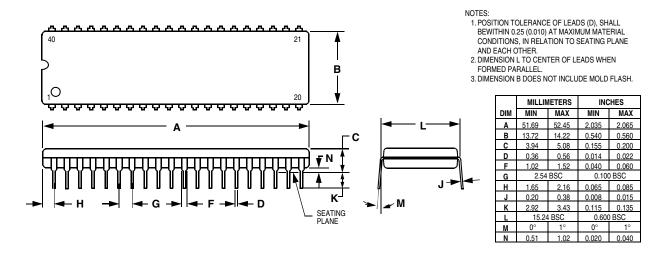

# 13.2 40-Pin Plastic Dual In-Line (DIP) Package (Case 711-03)

Figure 13-1. 40-Pin Plastic DIP Package (Case 711-03)

#### **Mechanical Specifications**

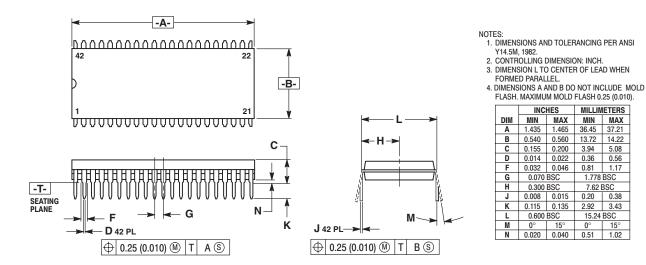

# 13.3 42-Pin Plastic Shrink Dual In-Line (SDIP) Package (Case 858-01)

Figure 13-2. 42-Pin Plastic SDIP Package (Case 858-01)

MILLIMETERS

MIN MAX

36.45 37.21

13.72 14.22

3.94 5.08 0.36 0.81 1.17

1.778 BSC

7.62 BSC

2.92 3.43

15.24 BSC

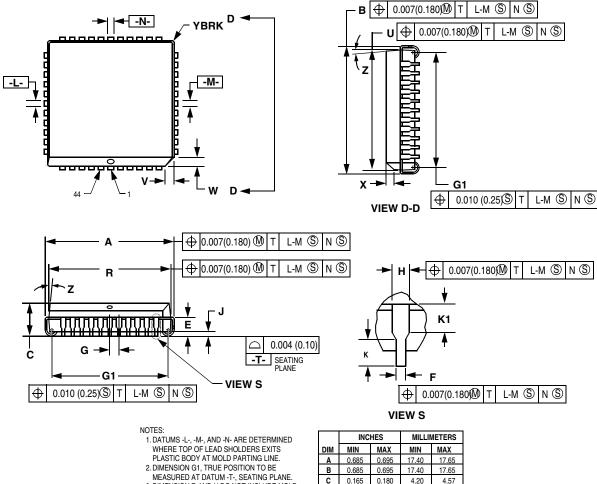

# 13.4 44-Lead Plastic Leaded Chip Carrier (PLCC) (Case 777-02)

- 3. DIMENSION R AND U DO NOT INCLUDE MOLD

- FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.25) PER SIDE. 4. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982 5. CONTROLLING DIMENSION: INCH.

- 6. THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U ARE DETER-

- AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF THE MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- 7. DIMINSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTUSION(S) SHALL NOT CAUSE THE H DIMINSION TO BE GREATER THAN 0.037 (0.940110). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMINISION TO SMALLER THAN 0.025 (0.635).

|     | INC   | HES   | MILLII   | METERS |  |  |

|-----|-------|-------|----------|--------|--|--|

| DIM | MIN   | MAX   | MIN      | MAX    |  |  |

| Α   | 0.685 | 0.695 | 17.40    | 17.65  |  |  |

| В   | 0.685 | 0.695 | 17.40    | 17.65  |  |  |

| c   | 0.165 | 0.180 | 4.20     | 4.57   |  |  |

| Е   | 0.090 | 0.110 | 2.29     | 2.79   |  |  |

| F   | 0.013 | 0.019 | 0.33     | 0.48   |  |  |

| G   | 0.050 | BSC   | 1.27 BSC |        |  |  |

| Н   | 0.026 | 0.032 | 0.66     | 0.81   |  |  |

| 7   | 0.020 |       | 0.51     | _      |  |  |

| K   | 0.025 | _     | 0.64     | _      |  |  |

| R   | 0.650 | 0.656 | 16.51    | 16.66  |  |  |

| U   | 0.650 | 0.656 | 16.51    | 16.66  |  |  |

| ٧   | 0.042 | 0.048 | 1.07     | 1.21   |  |  |

| W   | 0.042 | 0.048 | 1.07     | 1.21   |  |  |

| X   | 0.042 | 0.056 | 1.07     | 1.42   |  |  |

| Υ   | _     | 0.020 | _        | 0.50   |  |  |

| Z   | 2°    | 10°   | 2°       | 10°    |  |  |

| G1  | 0.610 | 0.630 | 15.50    | 16.00  |  |  |

| K1  | 0.040 | _     | 1.02     | _      |  |  |

Figure 13-3. 44-Lead PLCC (Case 777-02)

**Ordering Information**

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

# Appendix A EPROM Programming

#### A.1 Introduction

This section describes programming of the EPROM.

#### A.2 Bootloader Mode

**Table A-1. Operating Modes**

| RESET | ĪRQ                                     | TCAP                       | Mode               |  |  |

|-------|-----------------------------------------|----------------------------|--------------------|--|--|

|       | $ m V_{SS}$ to $ m V_{DD}$ $ m V_{TST}$ | $ m V_{SS}$ to $ m V_{DD}$ | User<br>Bootloader |  |  |

Bootloader mode is entered upon the rising edge of  $\overline{\text{RESET}}$  if the  $\overline{\text{IRQ}}$  is at  $V_{\text{TST}}$  and the TCAP pin is at logic one. The bootloader code resides in the ROM from \$3F00 to \$3FEF. This program handles copying of user code from an external EPROM into the on-chip EPROM. The bootload function does not have to be done from an external EPROM, but it may be done from a host.

The user code must be a one-to-one correspondence with the internal EPROM addresses.

#### A.3 Bootloader Functions

Three pins are used to select various bootloader functions: PD5, PD4, and PD3. Two other pins, PC6 and PC7, are used to drive the PROG LED and the VERF LED, respectively. The programming modes are shown in Table A-2.

**Table A-2. Bootloader Functions**

| PD5 | PD4 | PD3 | Mode                 |

|-----|-----|-----|----------------------|

| 0   | 0   | 0   | Program/verify       |

| 0   | 0   | 1   | Verify only          |

| 0   | 1   | 0   | Load RAM and execute |

| 1   | Х   | Х   | Secure               |