## NXP USA Inc. - MC68HC705C9ACP Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC05                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 2.1MHz                                                                 |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | POR, WDT                                                               |

| Number of I/O              | 24                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 352 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc705c9acp |

|                            |                                                                        |

Email: info@E-XFL.COM

#### **General Description**

- The port D data direction register (\$0007) is disabled and the seven port D pins become input only.

- SPI output signals (MOSI, MISO, and SCK) do not require the data direction register control for output capability.

- The port D wire-OR mode control bit (bit 5 of SPCR \$000A) is disabled, preventing open-drain configuration of port D.

- The RESET pin becomes input only.

# 1.4 Mask Options

The following two mask option registers are used to select features controlled by mask changes on the MC68HC05C9A and the MC68HC05C12A:

- Port B mask option register (PBMOR)

- C12 mask option register (C12MOR)

The mask option registers are EPROM locations which must be programmed prior to operation of the microcontroller.

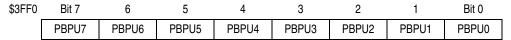

# 1.4.1 Port B Mask Option Register (PBMOR)

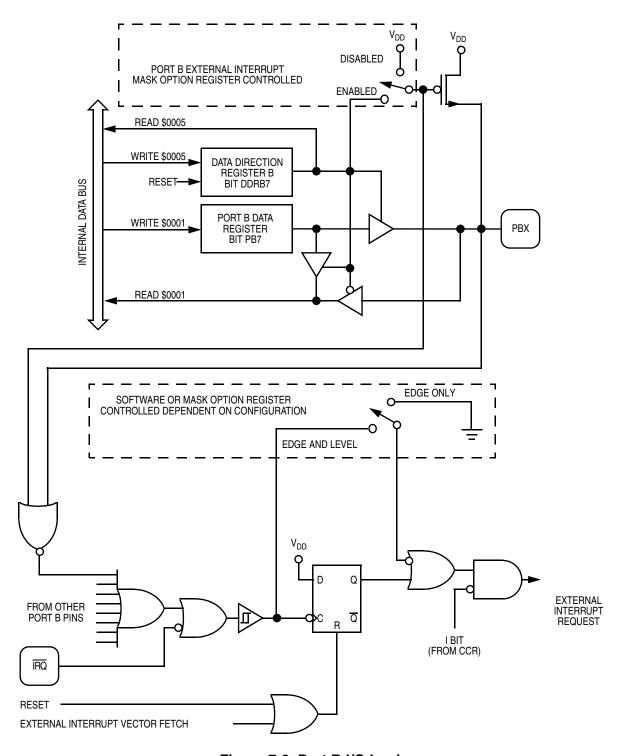

The PBMOR register, shown in Figure 1-2, contains eight programmable bits which determine whether each port B bit (when in input mode) has the pullup and interrupt enabled. The port B interrupts share the vector and edge/edge-level sensitivity with the IRQ pin. For more details, (see 4.3 External Interrupt (IRQ or Port B)).

Figure 1-2. Port B Mask Option Register

PBPU7-PBPU0 — Port B Pullup/Interrupt Enable Bits

- 1 = Pullup and CPU interrupt enabled

- 0 = Pullup and CPU interrupt disabled

#### NOTE

The current capability of the port B pullup devices is equivalent to the MC68HC05C9A, which is less than the MC68HC05C12A.

## 1.4.2 C12 Mask Option Register (C12MOR)

The C12MOR register, shown in Figure 1-3, controls the following options:

- Select between MC68HC05C9A/C12A configuration

- Enable/disable stop mode (C12A mode only)

- Enable/disable COP (C12A mode only)

- Edge-triggered only or edge- and level-triggered external interrupt pin (IRQ pin) (C12A mode only).

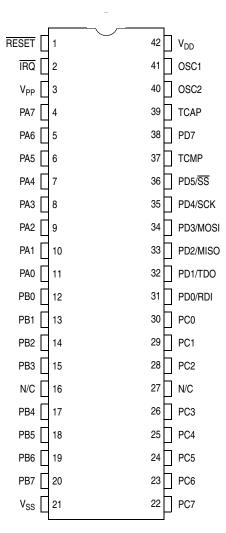

#### **General Description**

Figure 1-6. 42-Pin SDIP Pin Assignments

# Chapter 2 Memory

#### 2.1 Introduction

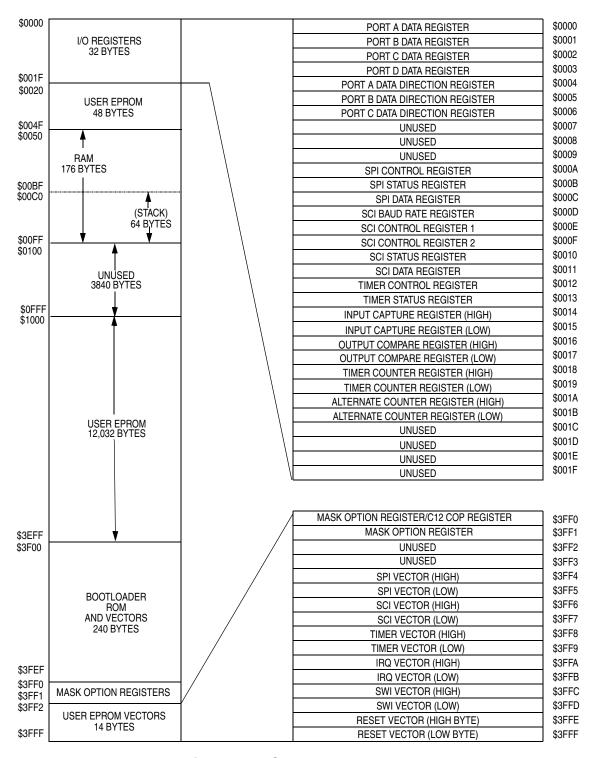

The MCU has a 16-Kbyte memory map when configured as either an MC68HC05C9A or an MC68HC05C12A. The memory map consists of registers (I/O, control, and status), user RAM, user EPROM, bootloader ROM, and reset and interrupt vectors as shown in Figure 2-1 and Figure 2-2.

When configured as an MC68HC05C9A, two control bits in the option register (\$3FDF) allow the user to switch between RAM and EPROM at any time in two special areas of the memory map, \$0020-\$004F (48 bytes) and \$0100-\$017F (128 bytes). When configured as an MC68HC05C12A, the section of the memory map from \$0020 to \$004F is fixed as EPROM and the section from \$0100 to \$0FFF becomes unused.

#### **2.2 RAM**

The main user RAM consists of 176 bytes at \$0050–\$00FF. This RAM area is always present in the memory map and includes a 64-byte stack area. The stack pointer can access 64 bytes of RAM in the range \$00FF down to \$00CO.

#### NOTE

Using the stack area for data storage or temporary work locations requires care to prevent it from being overwritten due to stacking from an interrupt or subroutine call.

In MC68HC05C9A configuration, two additional RAM areas are available at \$0020–\$004F (48 bytes) and \$0100–\$017F (128 bytes) (see Figure 2-1 and Figure 2-2.) These may be accessed at any time by setting the RAM0 and RAM1 bits, respectively, in the C9A option register. Refer to 1.5 Software-Programmable Options (MC68HC05C9A Mode Only) for additional information.

#### 2.3 EPROM

When configured as a C12A the main user EPROM consists of 48 bytes of page zero EPROM from \$0020 to \$004F, 12,032 bytes of EPROM from \$1000 to \$3EFF, and 14 bytes of user vectors from \$3FF4 to \$3FFF. When configured as a C9A, an additional 3,840 bytes of user EPROM from \$0100 to \$0FFF are enabled.

Locations \$3FF0 and \$3FF1 are the mask option registers (MOR) (see 1.4 Mask Options).

For detailed information on programming the EPROM see Appendix A EPROM Programming.

Figure 2-2. C12A Memory Map

#### Memory

| Addr.  | Register Name                                            |                 | Bit 7 | 6          | 5             | 4        | 3           | 2     | 1          | Bit 0 |

|--------|----------------------------------------------------------|-----------------|-------|------------|---------------|----------|-------------|-------|------------|-------|

| \$0000 | Port A Data Register<br>(PORTA)                          | Read:<br>Write: | PA7   | PA6        | PA5           | PA4      | PA3         | PA2   | PA1        | PA0   |

|        | See page 47.                                             | Reset:          |       | l.         | l.            | Unaffect | ed by reset |       |            |       |

| \$0001 | Port B Data Register<br>(PORTB)                          | Read:<br>Write: | PB7   | PB6        | PB5           | PB4      | PB3         | PB2   | PB1        | PB0   |

|        | See page 48.                                             | Reset:          |       | l .        | l .           | Unaffect | ed by reset |       |            |       |

| \$0002 | Port C Data Register<br>(PORTC)                          | Read:<br>Write: | PC7   | PC6        | PC5           | PC4      | PC3         | PC2   | PC1        | PC0   |

|        | See page 48.                                             | Reset:          |       |            |               | Unaffect | ed by reset |       |            |       |

| \$0003 | Port D Data Register<br>(PORTD)                          | Read:<br>Write: | PD7   |            | PD5           | PD4      | PD3         | PD2   | PD1        | PD0   |

|        | See page 48.                                             | Reset:          |       |            |               | Unaffect | ed by reset |       |            |       |

| \$0004 | Port A Data Direction Register (DDRA)                    | Read:<br>Write: | DDRA7 | DDRA6      | DDRA5         | DDRA4    | DDRA3       | DDRA2 | DDRA1      | DDRA0 |

|        | See page 47.                                             | Reset:          | 0     | 0          | 0             | 0        | 0           | 0     | 0          | 0     |

| \$0005 | Port B Data Direction Register (DDRB)                    | Read:<br>Write: | DDRB7 | DDRB6      | DDRB5         | DDRB4    | DDRB3       | DDRB2 | DDRB1      | DDRB0 |

|        | See page 48.                                             | Reset:          | 0     | 0          | 0             | 0        | 0           | 0     | 0          | 0     |

| \$0006 | Port C Data Direction Register (DDRC)                    | Read:<br>Write: | DDRC7 | DDRC6      | DDRC5         | DDRC4    | DDRC3       | DDRC2 | DDRC1      | DDRC0 |

|        | See page 48.                                             | Reset:          | 0     | 0          | 0             | 0        | 0           | 0     | 0          | 0     |

| \$0007 | Port D Data Direction Register<br>(DDRD) <b>C9A Only</b> | Read:<br>Write: | DDRC7 |            | DDRC5         | DDRC4    | DDRC3       | DDRC2 | DDRC1      | DDRC0 |

|        | See page 48.                                             | Reset:          | 0     | 0          | 0             | 0        | 0           | 0     | 0          | 0     |

| \$0008 | Unimplemented                                            |                 |       |            |               |          |             |       |            |       |

|        |                                                          | ı               |       |            |               | I        |             |       |            |       |

| \$0009 | Unimplemented                                            |                 |       |            |               |          |             |       |            |       |

| \$000A | SPI Control Register<br>(SPCR)                           | Read:<br>Write: | SPIE  | SPE        | DWOM<br>(C9A) | MSTR     | CPOL        | СРНА  | SPR1       | SPR0  |

|        | See page 75.                                             | Reset:          | 0     | 0          | 0             | 0        | 0           | 1     | U          | U     |

|        | SPI Status Register                                      | Read:           | SPIF  | WCOL       |               | MODF     |             |       |            |       |

| \$000B | (SPSR)                                                   | Write:          |       |            |               |          |             |       |            |       |

|        | See page 76.                                             | Reset:          | 0     | 0          | 0             | 0        | 0           | 0     | 0          | 0     |

| \$000C | SPI Data Register<br>(SPDR)                              | Read:<br>Write: | SPD7  | SPD6       | SPD5          | SPD4     | SPD3        | SPD2  | SPD1       | SPD0  |

|        | See page 77.                                             | Reset:          |       | 1          |               |          | ed by reset |       |            |       |

|        |                                                          |                 |       | = Unimpler | mented        | R        | = Reserved  |       | U = Unaffe | cted  |

Figure 2-4. Input/Output Registers (Sheet 1 of 3)

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

#### Memory

| Addr.                   | Register Name                 |        | Bit 7  | 6          | 5      | 4      | 3           | 2      | 1          | Bit 0   |

|-------------------------|-------------------------------|--------|--------|------------|--------|--------|-------------|--------|------------|---------|

|                         | Timer Register Low            | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3       | Bit 2  | Bit 1      | Bit 0   |

| \$0019                  | (TRL)<br>See page 55.         | Write: |        |            |        |        |             |        |            |         |

|                         | occ page oo.                  | Reset: | 1      | 1          | 1      | 1      | 1           | 1      | 0          | 0       |

|                         | Alternate Timer Register High | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11      | Bit 10 | Bit 9      | Bit 8   |

| \$001A                  | (ATRH)                        | Write: |        |            |        |        |             |        |            |         |

|                         | See page 55.                  | Reset: | 1      | 1          | 1      | 1      | 1           | 1      | 1          | 1       |

|                         | Alternate Timer Register Lov  | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3       | Bit 2  | Bit 1      | Bit 0   |

| \$001B                  | (ATRL)                        | Write: |        |            |        |        |             |        |            |         |

|                         | See page 55.                  | Reset: | 1      | 1          | 1      | 1      | 1           | 1      | 0          | 0       |

| EPROM Program<br>\$001C | EPROM Programming Register    | Read:  |        |            |        |        |             | LATCH  |            | EPGM    |

|                         | (EPR)                         | Write: |        |            |        |        |             | Brion  |            | LI GIVI |

|                         |                               | Reset: | 0      | 0          | 0      | 0      | 0           | 0      | 0          | 0       |

|                         | COP Reset Register            | Read:  |        |            |        |        |             |        |            |         |

| \$001D                  | (COPRST) C9A Only             | Write: | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3       | Bit 2  | Bit 1      | Bit 0   |

|                         | See page 41.                  | Reset: | 0      | 0          | 0      | 0      | 0           | 0      | 0          | 0       |

|                         | COP Control Register          | Read:  | 0      | 0          | 0      | COPF   | CME         | COPE   | CM1        | CM0     |

| \$001E                  | (COPCR) C9A Only              | Write: |        |            |        | 0011   | OIVIL       | 001    | OWIT       | OWIO    |

|                         | See page 42.                  | Reset: | 0      | 0          | 0      | U      | 0           | 0      | 0          | 0       |

| \$001F                  | Reserved                      |        | R      | R          | R      | R      | R           | R      | R          | R       |

|                         |                               |        |        |            |        |        | <del></del> |        |            |         |

|                         |                               |        |        | = Unimpler | mented | R      | = Reserved  |        | U = Unaffe | cted    |

Figure 2-4. Input/Output Registers (Sheet 3 of 3)

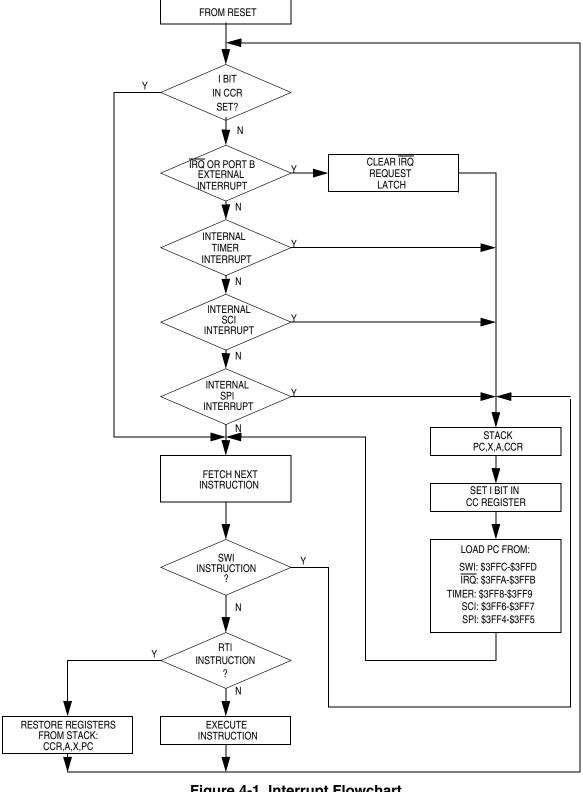

Figure 4-1. Interrupt Flowchart

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

#### Interrupts

# 4.4 Timer Interrupt

Three different timer interrupt flags cause a timer interrupt whenever they are set and enabled. The interrupt flags are in the timer status register (TSR), and the enable bits are in the timer control register (TCR). Any of these interrupts will vector to the same interrupt service routine, located at the address specified by the contents of memory locations \$3FF8 and \$3FF9.

# 4.5 SCI Interrupt

Five different SCI interrupt flags cause an SCI interrupt whenever they are set and enabled. The interrupt flags are in the SCI status register (SCSR), and the enable bits are in the SCI control register 2 (SCCR2). Any of these interrupts will vector to the same interrupt service routine, located at the address specified by the contents of memory locations \$3FF6 and \$3FF7.

# 4.6 SPI Interrupt

Two different SPI interrupt flags cause an SPI interrupt whenever they are set and enabled. The interrupt flags are in the SPI status register (SPSR), and the enable bits are in the SPI control register (SPCR). Either of these interrupts will vector to the same interrupt service routine, located at the address specified by the contents of memory locations \$3FF4 and \$3FF5.

Figure 7-2. Port B I/O Logic

#### FE — Receiver Framing Error Flag

This clearable, read-only flag is set when there is a logic 0 where a stop bit should be in the character shifted into the receive shift register. If the received word causes both a framing error and an overrun error, the OR flag is set and the FE flag is not set. Clear the FE bit by reading the SCSR and then reading the SCDR.

- 1 = Framing error

- 0 = No framing error

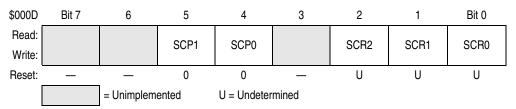

## 9.13.5 Baud Rate Register

The baud rate register (BAUD), shown in Figure 9-12, selects the baud rate for both the receiver and the transmitter.

Figure 9-12. Baud Rate Register (BAUD)

#### SCP1 — SCP0-SCI Prescaler Select Bits

These read/write bits control prescaling of the baud rate generator clock, as shown in Table 9-1. Reset clears both SCP1 and SCP0.

| SCP[1:0] | Baud Rate Generator Clock |

|----------|---------------------------|

| 00       | Internal Clock ÷ 1        |

| 01       | Internal Clock ÷ 3        |

| 10       | Internal Clock ÷ 4        |

| 11       | Internal Clock ÷ 13       |

**Table 9-1. Baud Rate Generator Clock Prescaling**

#### SCR2 — SCR0-SCI Baud Rate Select Bits

These read/write bits select the SCI baud rate, as shown in Table 9-2. Resets have no effect on the SCR2–SCR0 bits.

| SCR[2:0] | SCI Baud Rate (Baud)  |

|----------|-----------------------|

| 000      | Prescaled Clock ÷ 1   |

| 001      | Prescaled Clock ÷ 2   |

| 010      | Prescaled Clock ÷ 4   |

| 011      | Prescaled Clock ÷ 8   |

| 100      | Prescaled Clock ÷ 16  |

| 101      | Prescaled Clock ÷ 32  |

| 110      | Prescaled Clock ÷ 64  |

| 111      | Prescaled Clock ÷ 128 |

Table 9-2. Baud Rate Selection

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

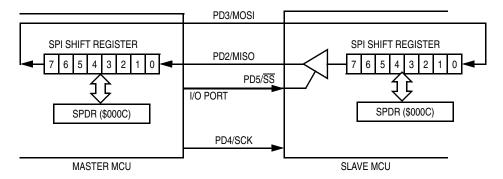

#### Serial Peripheral Interface (SPI)

The SPI is double buffered on read, but not on write. If a write is performed during data transfer, the transfer occurs uninterrupted, and the write will be unsuccessful. This condition will cause the write collision (WCOL) status bit in the SPSR to be set. After a data byte is shifted, the SPIF flag of the SPSR is set.

In the master mode, the SCK pin is an output. It idles high or low, depending on the CPOL bit in the SPCR, until data is written to the shift register, at which point eight clocks are generated to shift the eight bits of data and then SCK goes idle again.

In a slave mode, the slave select start logic receives a logic low at the  $\overline{SS}$  pin and a clock at the SCK pin. Thus, the slave is synchronized with the master. Data from the master is received serially at the MOSI line and loads the 8-bit shift register. After the 8-bit shift register is loaded, its data is parallel transferred to the read buffer. During a write cycle, data is written into the shift register, then the slave waits for a clock train from the master to shift the data out on the slave's MISO line.

Figure 10-3 illustrates the MOSI, MISO, SCK, and SS master-slave interconnections.

Figure 10-3. Serial Peripheral Interface Master-Slave Interconnection

# 10.5 SPI Registers

Three registers in the SPI provide control, status, and data storage functions. These registers are called the serial peripheral control register (SPCR), serial peripheral status register (SPSR), and serial peripheral data I/O register (SPDR) and are described in the following paragraphs.

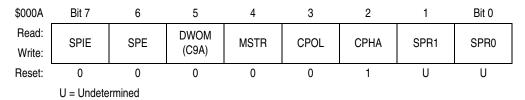

# 10.5.1 Serial Peripheral Control Register

The SPI control register (SPCR), shown in Figure 10-4, controls these functions:

- Enables SPI interrupts

- Enables the SPI system

- Selects between standard CMOS or open drain outputs for port D (C9A mode only)

- Selects between master mode and slave mode

- Controls the clock/data relationship between master and slave

- Determines the idle level of the clock pin

Figure 10-4. SPI Control Register (SPCR)

#### SPIE — Serial Peripheral Interrupt Enable Bit

This read/write bit enables SPI interrupts. Reset clears the SPIE bit.

- 1 = SPI interrupts enabled

- 0 = SPI interrupts disabled

#### SPE — Serial Peripheral System Enable Bit

This read/write bit enables the SPI. Reset clears the SPE bit.

- 1 = SPI system enabled

- 0 = SPI system disabled

### **DWOM** — Port D Wire-OR Mode Option Bit

This read/write bit disables the high side driver transistors on port D outputs so that port D outputs become open-drain drivers. DWOM affects all seven port D pins together. This option is only available when configured as a C9A.

- 1 = Port D outputs act as open-drain outputs.

- 0 = Port D outputs are normal CMOS outputs.

#### MSTR — Master Mode Select Bit

This read/write bit selects master mode operation or slave mode operation. Reset clears the MSTR bit.

- 1 = Master mode

- 0 = Slave mode

#### **CPOL** — Clock Polarity Bit

When the clock polarity bit is cleared and data is not being transferred, a steady state low value is produced at the SCK pin of the master device. Conversely, if this bit is set, the SCK pin will idle high. This bit is also used in conjunction with the clock phase control bit to produce the desired clock-data relationship between master and slave. See Figure 10-1.

#### **CPHA** — Clock Phase Bit

The clock phase bit, in conjunction with the CPOL bit, controls the clock-data relationship between master and slave. The CPOL bit can be thought of as simply inserting an inverter in series with the SCK line. The CPHA bit selects one of two fundamentally different clocking protocols. When CPHA = 0, the shift clock is the OR of SCK with SS. As soon as SS goes low, the transaction begins and the first edge on SCK invokes the first data sample. When CPHA=1, the SS pin may be thought of as a simple output enable control. See Figure 10-1.

#### SPR1 and SPR0 — SPI Clock Rate Selects

These read/write bits select one of four master mode serial clock rates, as shown in Table 10-1. They have no effect in the slave mode.

#### Serial Peripheral Interface (SPI)

| Table 10-1  | SPI Clock  | Rate Selection  |  |

|-------------|------------|-----------------|--|

| Table IU-I. | OI I OIOUK | Tiale Selection |  |

| SPR[1:0] | SPI Clock Rate      |

|----------|---------------------|

| 00       | Internal Clock ÷ 2  |

| 01       | Internal Clock ÷ 4  |

| 10       | Internal Clock ÷ 16 |

| 11       | Internal Clock ÷ 32 |

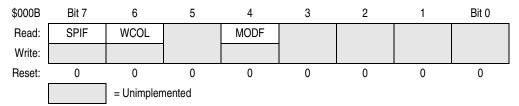

#### 10.5.2 Serial Peripheral Status Register

The SPI status register (SPSR), shown in Figure 10-5, contains flags to signal the following conditions:

- SPI transmission complete

- Write collision

- Mode fault

Figure 10-5. SPI Status Register

#### SPIF — SPI Transfer Complete Flag

The serial peripheral data transfer flag bit is set upon completion of data transfer between the processor and external device. If SPIF goes high, and if SPIE is set, a serial peripheral interrupt is generated. Clearing the SPIF bit is accomplished by reading the SPSR (with SPIF set) followed by an access of the SPDR. Following the initial transfer, unless SPSR is read (with SPIF set) first, attempts to write to SPDR are inhibited.

#### WCOL — Write Collision Bit

The write collision bit is set when an attempt is made to write to the serial peripheral data register while data transfer is taking place. If CPHA is 0, a transfer is said to begin when  $\overline{SS}$  goes low and the transfer ends when  $\overline{SS}$  goes high after eight clock cycles on SCK. When CPHA is 1, a transfer is said to begin the first time SCK becomes active while  $\overline{SS}$  is low and the transfer ends when the SPIF flag gets set. Clearing the WCOL bit is accomplished by reading the SPSR (with WCOL set) followed by an access to SPDR.

#### MODF — Mode Fault

The mode fault flag indicates that there may have been a multi-master conflict for system control and allows a proper exit from system operation to a reset or default system state. The MODF bit is normally clear, and is set only when the master device has its  $\overline{SS}$  pin pulled low. Setting the MODF bit affects the internal serial peripheral interface system in the following ways.

- An SPI interrupt is generated if SPIE = 1.

- The SPE bit is cleared. This disables the SPI.

- 3. The MSTR bit is cleared, thus forcing the device into the slave mode.

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

Serial Peripheral Interface (SPI)

# 11.4 Instruction Set Summary

Table 11-6. Instruction Set Summary (Sheet 1 of 6)

| Source                                                              | Operation                             | Description                                  | Effect on CCR |          |          |   | ł        | Address<br>Mode                                                         | Opcode                           | Operand                                | Cycles                     |

|---------------------------------------------------------------------|---------------------------------------|----------------------------------------------|---------------|----------|----------|---|----------|-------------------------------------------------------------------------|----------------------------------|----------------------------------------|----------------------------|

| Form                                                                |                                       | P. C.                                        | Н             | I        | N        | Z | С        | Adc                                                                     | ob                               | obe                                    | Ş                          |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC ,X  | Add with Carry                        | $A \leftarrow (A) + (M) + (C)$               | 1             | _        | ‡        | ‡ | 1        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A9<br>B9<br>C9<br>D9<br>E9<br>F9 | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| ADD #opr<br>ADD opr<br>ADD opr,<br>ADD opr,X<br>ADD opr,X<br>ADD ,X | Add without Carry                     | A ← (A) + (M)                                | 1             | _        | 1        | 1 | 1        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | AB<br>BB<br>CB<br>DB<br>EB<br>FB | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X  | Logical AND                           | $A \leftarrow (A) \land (M)$                 |               | _        | Î        | 1 |          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A4<br>B4<br>C4<br>D4<br>E4<br>F4 | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X                      | Arithmetic Shift Left (Same as LSL)   | G ← 0 b0 b0                                  |               | _        | ‡        | ‡ | ‡        | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 38<br>48<br>58<br>68<br>78       | dd<br>ff                               | 5<br>3<br>6<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR ,X                      | Arithmetic Shift Right                | b7 b0                                        | _             | _        | ‡        | ‡ | 1        | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 37<br>47<br>57<br>67<br>77       | dd<br>ff                               | 5<br>3<br>3<br>6<br>5      |

| BCC rel                                                             | Branch if Carry Bit Clear             | $PC \leftarrow (PC) + 2 + rel ? C = 0$       | _             | _        | _        | _ | _        | REL                                                                     | 24                               | rr                                     | 3                          |

| BCLR n opr                                                          | Clear Bit n                           | Mn ← 0                                       |               | _        |          |   |          | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 15<br>17<br>19<br>1B<br>1D       | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 5 5 5 5 5 5 5              |

| BCS rel                                                             | Branch if Carry Bit Set (Same as BLO) | PC ← (PC) + 2 + rel ? C = 1                  | _             | _        | _        | _ | _        | REL                                                                     | 25                               | rr                                     | 3                          |

| BEQ rel                                                             | Branch if Equal                       | PC ← (PC) + 2 + rel? Z = 1                   |               |          |          | _ |          | REL                                                                     | 27                               | rr                                     | 3                          |

| BHCC rel                                                            | Branch if Half-Carry Bit Clear        | PC ← (PC) + 2 + rel ? H = 0                  | _             |          |          |   | _        | REL                                                                     | 28                               | rr                                     | 3                          |

| BHCS rel                                                            | Branch if Half-Carry Bit Set          | PC ← (PC) + 2 + <i>rel</i> ? H = 1           |               |          | _        |   |          | REL                                                                     | 29                               | rr                                     | 3                          |

| BHI rel                                                             | Branch if Higher                      | $PC \leftarrow (PC) + 2 + rel? C \lor Z = 0$ | _             | _        | _        | _ | <u> </u> | REL                                                                     | 22                               | rr                                     | 3                          |

| BHS rel                                                             | Branch if Higher or Same              | $PC \leftarrow (PC) + 2 + rel? C = 0$        | <u> </u>      | <u> </u> | <u> </u> |   | <u> </u> | REL                                                                     | 24                               | rr                                     | 3                          |

| BIH rel                                                             | Branch if IRQ Pin High                | PC ← (PC) + 2 + <i>rel</i> ? IRQ = 1         | <u> </u>      | <u> </u> |          |   |          | REL                                                                     | 2F                               | rr                                     | 3                          |

| BIL rel                                                             | Branch if IRQ Pin Low                 | $PC \leftarrow (PC) + 2 + rel ? IRQ = 0$     | _             | _        | _        | _ | -        | REL                                                                     | 2E                               | rr                                     | 3                          |

#### **Instruction Set**

# Table 11-6. Instruction Set Summary (Sheet 2 of 6)

| Source<br>Form                                                     | Operation                             | Description                                                                                                                                                                |   |   | Effect<br>on CCR |   |   | Address<br>Mode                                                         | Opcode                           | Operand                                      | Cycles                     |

|--------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|---|---|-------------------------------------------------------------------------|----------------------------------|----------------------------------------------|----------------------------|

| Form                                                               | ·                                     | ·                                                                                                                                                                          | Н | I | N                | Z | С | Adc                                                                     | ď                                | Ope                                          | င်                         |

| BIT #opr<br>BIT opr<br>BIT opr,<br>BIT opr,X<br>BIT opr,X<br>BIT,X | Bit Test Accumulator with Memory Byte | (A) ∧ (M)                                                                                                                                                                  | _ | _ | ‡                | 1 |   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A5<br>B5<br>C5<br>D5<br>E5<br>F5 | ii<br>dd<br>hh II<br>ee ff<br>ff             | 2<br>3<br>4<br>5<br>4<br>3 |

| BLO rel                                                            | Branch if Lower (Same as BCS)         | PC ← (PC) + 2 + rel ? C = 1                                                                                                                                                | _ | _ | _                | _ | _ | REL                                                                     | 25                               | rr                                           | 3                          |

| BLS rel                                                            | Branch if Lower or Same               | $PC \leftarrow (PC) + 2 + rel ? C \lor Z = 1$                                                                                                                              | _ | _ | _                | _ | _ | REL                                                                     | 23                               | rr                                           | 3                          |

| BMC rel                                                            | Branch if Interrupt Mask Clear        | PC ← (PC) + 2 + rel? I = 0                                                                                                                                                 | _ | _ | _                | _ | _ | REL                                                                     | 2C                               | rr                                           | 3                          |

| BMI rel                                                            | Branch if Minus                       | PC ← (PC) + 2 + rel ? N = 1                                                                                                                                                | _ | _ | _                | _ | _ | REL                                                                     | 2B                               | rr                                           | 3                          |

| BMS rel                                                            | Branch if Interrupt Mask Set          | PC ← (PC) + 2 + rel? I = 1                                                                                                                                                 | _ | _ | _                | _ | _ | REL                                                                     | 2D                               | rr                                           | 3                          |

| BNE rel                                                            | Branch if Not Equal                   | $PC \leftarrow (PC) + 2 + rel ? Z = 0$                                                                                                                                     | _ | _ | _                | _ | _ | REL                                                                     | 26                               | rr                                           | 3                          |

| BPL rel                                                            | Branch if Plus                        | $PC \leftarrow (PC) + 2 + rel ? N = 0$                                                                                                                                     | _ | _ | _                | _ | _ | REL                                                                     | 2A                               | rr                                           | 3                          |

| BRA rel                                                            | Branch Always                         | PC ← (PC) + 2 + rel? 1 = 1                                                                                                                                                 | _ | _ | _                | _ | _ | REL                                                                     | 20                               | rr                                           | 3                          |

| BRCLR n opr rel                                                    | Branch if Bit n Clear                 | PC ← (PC) + 2 + <i>rel</i> ? Mn = 0                                                                                                                                        |   |   |                  |   | ţ | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 03<br>05<br>07<br>09<br>0B<br>0D | dd rr                                        | 5 5 5 5 5 5                |

| BRN rel                                                            | Branch Never                          | PC ← (PC) + 2 + rel? 1 = 0                                                                                                                                                 | _ | _ | _                | _ | _ | REL                                                                     | 21                               | rr                                           | 3                          |

| BRSET n opr rel                                                    | Branch if Bit n Set                   | PC ← (PC) + 2 + <i>rel</i> ? Mn = 1                                                                                                                                        | _ |   |                  |   | 1 | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 02<br>04<br>06<br>08<br>0A<br>0C |                                              | 5 5 5 5 5                  |

| BSET n opr                                                         | Set Bit n                             | Mn ← 1                                                                                                                                                                     | _ | _ |                  |   |   | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 12<br>14<br>16<br>18<br>1A<br>1C | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 5 5 5 5 5 5 5              |

| BSR rel                                                            | Branch to Subroutine                  | $\begin{array}{c} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$ | _ | _ | _                | _ | _ | REL                                                                     | AD                               | rr                                           | 6                          |

| CLC                                                                | Clear Carry Bit                       | C ← 0                                                                                                                                                                      |   | _ |                  |   | 0 | INH                                                                     | 98                               |                                              | 2                          |

| CLI                                                                | Clear Interrupt Mask                  | I ← 0                                                                                                                                                                      | _ | 0 | _                | _ | _ | INH                                                                     | 9A                               |                                              | 2                          |

MC68HC05C9A Advance Information Data Sheet, Rev. 4.1

# Table 11-7. Opcode Map

|            | Bit Mani             | oulation            | Branch                |                   | Read               | I-Modify-W                | /rite             |                 | Con               |              |                      |                   |              |                   |                   |             |            |

|------------|----------------------|---------------------|-----------------------|-------------------|--------------------|---------------------------|-------------------|-----------------|-------------------|--------------|----------------------|-------------------|--------------|-------------------|-------------------|-------------|------------|

|            | DIR                  | DIR                 | REL                   | DIR               | INH                | INH                       | IX1               | IX              | INH               | INH          | IMM                  | DIR               | EXT          | IX2               | IX1               | IX          |            |

| MSB<br>LSB | 0                    | 1                   | 2                     | 3                 | 4                  | 5                         | 6                 | 7               | 8                 | 9            | Α                    | В                 | С            | D                 | Е                 | F           | MSB<br>LSB |

| 0          | BRSET0<br>3 DIR      | BSET0<br>2 DIR      | BRA<br>2 REL          | 5<br>NEG<br>2 DIR | 3<br>NEGA<br>1 INH | NEGX<br>1 INH 2           | 6<br>NEG<br>2 IX1 | NEG 1 IX        | 9<br>RTI<br>1 INH |              | SUB<br>2 IMM         | SUB<br>2 DIR      | SUB<br>3 EXT | SUB<br>3 IX2      | 4<br>SUB<br>2 IX1 | SUB 1       | 0          |

| 1          | 5<br>BRCLR0<br>3 DIR | 5<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL     |                   |                    |                           |                   |                 | 6<br>RTS<br>1 INH |              | CMP<br>2 IMM         | 3<br>CMP<br>2 DIR | CMP<br>3 EXT | 5<br>CMP<br>3 IX2 | 4<br>CMP<br>2 IX1 | CMP<br>1 IX | 1          |

| 2          | 5<br>BRSET1<br>3 DIR | 5<br>BSET1<br>2 DIR | 3<br>BHI<br>2 REL     |                   | 11<br>MUL<br>1 INH |                           |                   |                 |                   |              | SBC<br>2 IMM         | 3<br>SBC<br>2 DIR | SBC<br>3 EXT | SBC<br>3 IX2      | 4<br>SBC<br>2 IX1 | SBC 1 IX    | 2          |

| 3          | 5<br>BRCLR1<br>3 DIR | 5<br>BCLR1<br>2 DIR |                       | COM<br>2 DIR      | COMA<br>1 INH      | COMX<br>1 INH 2           | COM<br>2 IX1      | COM 1 IX        | SWI<br>1 INH      |              | CPX<br>2 IMM         | CPX<br>2 DIR      | CPX<br>3 EXT | 5<br>CPX<br>3 IX2 | 4<br>CPX<br>2 IX1 | CPX<br>1 IX | 3          |

| 4          | BRSET2<br>3 DIR      | BSET2<br>2 DIR      | BCC<br>2 REL          | LSR<br>2 DIR      | 3<br>LSRA<br>1 INH | LSRX<br>1 INH 2           | 6<br>LSR<br>2 IX1 | LSR<br>1 IX     |                   |              | AND<br>2 IMM         | 3<br>AND<br>2 DIR | AND<br>3 EXT | AND<br>3 IX2      | 4<br>AND<br>2 IX1 | AND<br>1 IX | 4          |

| 5          | 5<br>BRCLR2<br>3 DIR |                     | 3<br>BCS/BLO<br>2 REL |                   |                    |                           |                   |                 |                   |              | BIT<br>2 IMM         | 3<br>BIT<br>2 DIR | BIT<br>3 EXT | 5<br>BIT<br>3 IX2 | BIT<br>2 IX1      | BIT<br>1 IX | 5          |

| 6          | BRSET3<br>3 DIR      | BSET3<br>2 DIR      | BNE<br>2 REL          | ROR<br>2 DIR      | RORA<br>1 INH      | RORX<br>1 INH 2           | ROR<br>2 IX1      | ROR 1 IX        |                   |              | LDA<br>2 IMM         | LDA<br>2 DIR      |              | LDA<br>3 IX2      | LDA<br>2 IX1      | LDA<br>1 IX | 6          |

| 7          | BRCLR3<br>3 DIR      | BCLR3<br>2 DIR      | BEQ<br>2 REL          | ASR<br>2 DIR      | ASRA<br>1 INH      | ASRX<br>1 INH 2           | ASR<br>2 IX1      | ASR<br>1 IX     |                   | TAX<br>1 INH |                      | STA<br>2 DIR      | STA<br>3 EXT | STA<br>3 IX2      | STA<br>2 IX1      | STA<br>1 IX | 7          |

| 8          | BRSET4<br>3 DIR      | BSET4<br>2 DIR      |                       |                   |                    | 3<br>ASLX/LSLX<br>1 INH 2 | 2 IX1             | ASL/LSL<br>1 IX |                   | CLC<br>1 INH | EOR<br>EOR<br>12 IMM |                   | EOR<br>3 EXT | EOR<br>3 IX2      | EOR<br>2 IX1      | EOR<br>1 IX | 8          |

| 9          | BRCLR4<br>3 DIR      |                     |                       |                   |                    | ROLX<br>1 INH 2           | ROL<br>2 IX1      | ROL<br>1 IX     |                   | SEC<br>1 INH |                      |                   |              |                   | 4<br>ADC<br>2 IX1 | ADC<br>1 IX | 9          |

| Α          | BRSET5<br>3 DIR      | BSET5<br>2 DIR      | BPL                   | DEC<br>2 DIR      | 3<br>DECA<br>1 INH | DECX<br>1 INH 2           | DEC IX1           | DEC 1 IX        |                   | CLI<br>1 INH | ORA<br>12 IMM        | 3<br>ORA<br>2 DIR | ORA<br>3 EXT | ORA               | ORA<br>2 IX1      | ORA<br>1 IX | Α          |

| В          | BRCLR5<br>3 DIR      | BCLR5<br>2 DIR      | BMI<br>2 REL          |                   |                    |                           |                   |                 |                   | SEI<br>1 INH | ADD<br>I IMM         | 3<br>ADD<br>2 DIR |              | ADD<br>3 IX2      | 4<br>ADD<br>2 IX1 | ADD<br>1 IX | В          |

| С          | BRSET6<br>3 DIR      | BSET6<br>2 DIR      | BMC<br>2 REL          | INC<br>2 DIR      |                    |                           |                   | INC 1 IX        |                   | RSP<br>1 INH |                      | JMP<br>2 DIR      |              | JMP<br>3 IX2      | JMP<br>2 IX1      | JMP<br>1 IX | С          |

| D          | BRCLR6<br>3 DIR      | BCLR6<br>2 DIR      | BMS<br>2 REL          | TST<br>2 DIR      | 3<br>TSTA<br>1 INH | TSTX<br>1 INH 2           | 5<br>TST<br>2 IX1 | TST 1 IX        |                   | NOP<br>1 INH | BSR<br>BSR<br>REL    | JSR<br>2 DIR      | JSR<br>3 EXT | JSR<br>3 IX2      | JSR<br>2 IX1      | JSR<br>1 IX | D          |

| E          | BRSET7<br>3 DIR      | 5<br>BSET7<br>2 DIR | 3<br>BIL<br>2 REL     |                   |                    |                           |                   |                 | STOP<br>1 INH     |              | LDX<br>2 IMM         | 3<br>LDX<br>2 DIR | LDX<br>3 EXT | 5<br>LDX<br>3 IX2 | LDX<br>2 IX1      | LDX<br>1 IX | E          |

| F          | 5<br>BRCLR7<br>3 DIR | BCLR7<br>2 DIR      | 3<br>BIH<br>2 REL     | 5<br>CLR<br>2 DIR | 3<br>CLRA<br>1 INH | CLRX<br>1 INH 2           | 6<br>CLR<br>2 IX1 | CLR<br>1 IX     | WAIT<br>1 INH     | TXA<br>1 INH |                      | STX<br>2 DIR      | STX<br>3 EXT | 6<br>STX<br>3 IX2 | 5<br>STX<br>2 IX1 | STX 1       | F          |

INH = Inherent

REL = Relative

IMM = Immediate DIR = Direct

IX = Indexed, No Offset IX1 = Indexed, 8-Bit Offset

EXT = Extended

IX2 = Indexed, 16-Bit Offset

LSB of Opcode in Hexadecimal

MSB 0 LSB BRSET0 3 DIR 0

MSB of Opcode in Hexadecimal

# **Chapter 12 Electrical Specifications**

# 12.1 Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it

The MCU contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in the table below. Keep  $V_{In}$  and  $V_{Out}$  within the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Connect unused inputs to the appropriate voltage level, either  $V_{SS}$  or  $V_{DD}$ .

| Rating                                                        | Symbol           | Value                                                               | Unit |

|---------------------------------------------------------------|------------------|---------------------------------------------------------------------|------|

| Supply voltage                                                | $V_{DD}$         | -0.3 to +7.0                                                        | V    |

| Input voltage Normal operation Bootloader mode (IRQ pin only) | V <sub>In</sub>  | $V_{SS}$ =0.3 to $V_{DD}$ + 0.3 $V_{SS}$ =0.3 to 2 x $V_{DD}$ + 0.3 | V    |

| Current drain per pin (Excluding $V_{DD}$ and $V_{SS}$ )      | I                | 25                                                                  | mA   |

| Storage temperature range                                     | T <sub>STG</sub> | -65 to +150                                                         | °C   |

#### NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 12.5 5.0-Vdc Electrical Characteristics for guaranteed operating conditions.

# 12.2 Operating Temperature

| Characteristic              | Symbol         | Value      | Unit |

|-----------------------------|----------------|------------|------|

| Operating temperature range | T <sub>A</sub> | -40 to +85 | °C   |

## 12.3 Thermal Characteristics

| Characteristic                                        | Symbol        | Value | Unit |

|-------------------------------------------------------|---------------|-------|------|

| Thermal resistance plastic dual in-line (PDIP)        | $\theta_{JA}$ | 60    | °C/W |

| Thermal resistance plastic leaded chip carrier (PLCC) | $\theta_{JA}$ | 70    | °C/W |

| Thermal resistance quad flat pack (QFP)               | $\theta_{JA}$ | 95    | °C/W |

| Thermal resistance plastic shrink DIP (SDIP)          | $\theta_{JA}$ | 60    | °C/W |