# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC G2                                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 200MHz                                                                  |

| Co-Processors/DSP               | Communications; RISC CPM                                                |

| RAM Controllers                 | DRAM, SDRAM                                                             |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100Mbps (3)                                                          |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 3.3V                                                                    |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 480-LBGA Exposed Pad                                                    |

| Supplier Device Package         | 480-TBGA (37.5x37.5)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8264azupibb |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- 32-bit address decodes with programmable bank size

- Three user programmable machines, general-purpose chip-select machine, and page-mode pipeline SDRAM machine

- Byte selects for 64 bus width (60x) and byte selects for 32 bus width (local)

- Dedicated interface logic for SDRAM

- CPU core can be disabled and the device can be used in slave mode to an external core

- Communications processor module (CPM)

- Embedded 32-bit communications processor (CP) uses a RISC architecture for flexible support for communications protocols

- Interfaces to G2 core through on-chip 32-Kbyte dual-port RAM and DMA controller

- Serial DMA channels for receive and transmit on all serial channels

- Parallel I/O registers with open-drain and interrupt capability

- Virtual DMA functionality executing memory-to-memory and memory-to-I/O transfers

- Three fast communications controllers supporting the following protocols (only FCC1 and FCC2 on the MPC8255):

- 10/100-Mbit Ethernet/IEEE Std. 802.3® CDMA/CS interface through media independent interface (MII)

- ATM—Full-duplex SAR protocols at 155 Mbps, through UTOPIA interface, AAL5, AAL1, AAL0 protocols, TM 4.0 CBR, VBR, UBR, ABR traffic types, up to 16 K external connections

- Transparent

- HDLC—Up to T3 rates (clear channel)

- Two multichannel controllers (MCCs) (only MCC2 on the MPC8255)

- Each MCC handles 128 serial, full-duplex, 64-Kbps data channels.Each MCC can be split into four subgroups of 32 channels each.

- Almost any combination of subgroups can be multiplexed to single or multiple TDM interfaces up to four TDM interfaces per MCC

- Four serial communications controllers (SCCs) identical to those on the MPC860, supporting the digital portions of the following protocols:

- Ethernet/IEEE 802.3 CDMA/CS

- HDLC/SDLC and HDLC bus

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Binary synchronous (BISYNC) communications

- Transparent

- Two serial management controllers (SMCs), identical to those of the MPC860

- Provide management for BRI devices as general circuit interface (GCI) controllers in timedivision-multiplexed (TDM) channels

- Transparent

- UART (low-speed operation)

- One serial peripheral interface identical to the MPC860 SPI

- One inter-integrated circuit ( $I^2C$ ) controller (identical to the MPC860  $I^2C$  controller)

- Microwire compatible

- Multiple-master, single-master, and slave modes

- Up to eight TDM interfaces (four on the MPC8255)

- Supports two groups of four TDM channels for a total of eight TDMs

- 2,048 bytes of SI RAM

- Bit or byte resolution

- Independent transmit and receive routing, frame synchronization

- Supports T1, CEPT, T1/E1, T3/E3, pulse code modulation highway, ISDN basic rate, ISDN primary rate, Freescale interchip digital link (IDL), general circuit interface (GCI), and user-defined TDM serial interfaces

- Eight independent baud rate generators and 20 input clock pins for supplying clocks to FCCs, SCCs, SMCs, and serial channels

- Four independent 16-bit timers that can be interconnected as two 32-bit timers

Additional features of the MPC826xA family are as follows:

- CPM

- 32-Kbyte dual-port RAM

- Additional MCC host commands

- Eight transfer transmission convergence (TC) layers between the TDMs and FCC2 to support inverse multiplexing for ATM capabilities (IMA) (MPC8264 and MPC8266 only)

- CPM multiplexing

- FCC2 can also be connected to the TC layer.

- TC layer (MPC8264 and MPC8266 only)

- Each of the 8 TDM channels is routed in hardware to a TC layer block

- Protocol-specific overhead bits may be discarded or routed to other controllers by the SI

- Performing ATM TC layer functions (according to ITU-T I.432)

- Transmit (Tx) updates

- Cell HEC generation

- Payload scrambling using self synchronizing scrambler (programmable by the user)

- Coset generation (programmable by the user)

- Cell rate by inserting idle/unassigned cells

- Receive (Rx) updates

- Cell delineation using bit by bit HEC checking and programmable ALPHA and DELTA parameters for the delineation state machine

- Payload descrambling using self synchronizing scrambler (programmable by the user)

Features

- Coset removing (programmable by the user)

- Filtering idle/unassigned cells (programmable by the user)

- Performing HEC error detection and single bit error correction (programmable by user)

- Generating loss of cell delineation status/interrupt (LOC/LCD)

- Operates with FCC2 (UTOPIA 8)

- Provides serial loop back mode

- Cell echo mode is provided

- Supports both FCC transmit modes

- External rate mode—Idle cells are generated by the FCC (microcode) to control data rate.

- Internal rate mode (sub-rate)—FCC transfers only the data cells using the required data rate. The TC layer generates idle/unassigned cells to maintain the line bit rate.

- Supports TC-layer and PMD-WIRE interface (according to the ATM-Forum af-phy-0063.000)

- Cell counters for performance monitoring

- 16-bit counters count

- HEC error cells

- HEC single bit error and corrected cells

- Idle/unassigned cells filtered

- Idle/unassigned cells transmitted

- Transmitted ATM cells

- Received ATM cells

- Maskable interrupt is sent to the host when a counter expires

- Overrun (Rx cell FIFO) and underrun (Tx cell FIFO) condition produces maskable interrupt

- May be operated at E1 and DS-1 rates. In addition, xDSL applications at bit rates up to 10 Mbps are supported

- PCI bridge (MPC8265 and MPC8266 only)

- PCI Specification Revision 2.2 compliant and supports frequencies up to 66 MHz

- On-chip arbitration

- Support for PCI to 60x memory and 60x memory to PCI streaming

- PCI Host Bridge or Peripheral capabilities

- Includes 4 DMA channels for the following transfers:

- PCI-to-60x to 60x-to-PCI

- 60x-to-PCI to PCI-to-60x

- PCI-to-60x to PCI-to-60x

- 60x-to-PCI to 60x-to-PCI

- Includes all of the configuration registers (which are automatically loaded from the EPROM and used to configure the MPC8265) required by the PCI standard as well as message and doorbell registers

- Supports the I<sub>2</sub>O standard

Table 3 shows DC electrical characteristics.

| Characteristic                                                                                                                                                                              | Symbol           | Min | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage, all inputs except CLKIN                                                                                                                                                 | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage                                                                                                                                                                           | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                                                    | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                                                     | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                                  | I <sub>IN</sub>  | —   | 10    | μA   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                       | I <sub>OZ</sub>  | _   | 10    | μA   |

| Signal low input current, V <sub>IL</sub> = 0.8 V                                                                                                                                           | ۱ <sub>L</sub>   |     | 1     | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                                                          | I <sub>Н</sub>   |     | 1     | μA   |

| Output high voltage, $I_{OH} = -2 \text{ mA}$<br>except XFC, UTOPIA mode, and open drain pins<br>In UTOPIA mode: $I_{OH} = -8.0 \text{ mA}$<br>PA[0-31]<br>PB[4-31]<br>PC[0-31]<br>PD[4-31] | V <sub>OH</sub>  | 2.4 |       | v    |

| In UTOPIA mode: I <sub>OL</sub> = 8.0 mA<br>PA[0-31]<br>PB[4-31]<br>PC[0-31]<br>PD[4-31]                                                                                                    | V <sub>OL</sub>  | _   | 0.5   | V    |

Table 3. DC Electrical Characteristics<sup>1</sup>

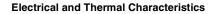

**Electrical and Thermal Characteristics**

# 2.4 AC Electrical Characteristics

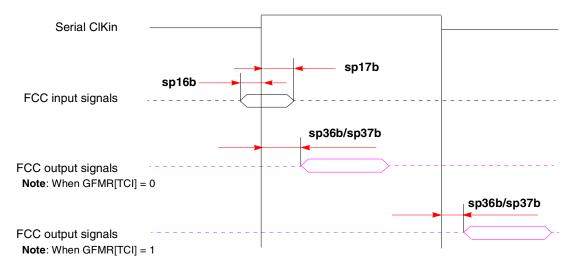

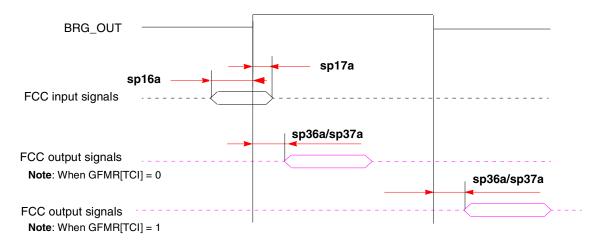

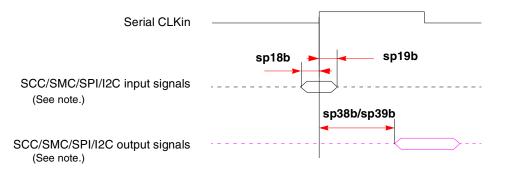

The following sections include illustrations and tables of clock diagrams, signals, and CPM outputs and inputs for the 66 MHz MPC826xA device. Note that AC timings are based on a 50-pf load. Typical output buffer impedances are shown in Table 6.

| Output Buffers    | Typical Impedance ( $\Omega$ ) |

|-------------------|--------------------------------|

| 60x bus           | 40                             |

| Local bus         | 40                             |

| Memory controller | 40                             |

| Parallel I/O      | 46                             |

| PCI               | 25                             |

| Table 6. Output Buffer | Impedances <sup>1</sup> |

|------------------------|-------------------------|

|------------------------|-------------------------|

<sup>1</sup> These are typical values at  $65^{\circ}$  C. The impedance may vary by  $\pm 25\%$  with process and temperature.

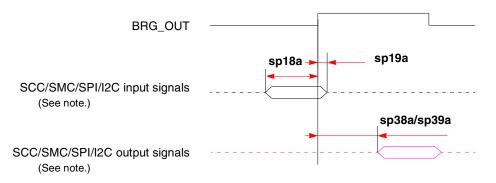

### Table 7 lists CPM output characteristics.

| Table 7. | AC | Characteristics | for CPI | M Outputs <sup>1</sup> |

|----------|----|-----------------|---------|------------------------|

|----------|----|-----------------|---------|------------------------|

| Spec N | lumber | Characteristic                                   |        | Max Delay (ns) |        | Min Delay (ns) |  |

|--------|--------|--------------------------------------------------|--------|----------------|--------|----------------|--|

| Max    | Min    | Characteristic                                   | 66 MHz | 83 MHz         | 66 MHz | 83 MHz         |  |

| sp36a  | sp37a  | FCC outputs—internal clock (NMSI)                | 6      | 5.5            | 1      | 1              |  |

| sp36b  | sp37b  | FCC outputs—external clock (NMSI)                | 14     | 12             | 2      | 1              |  |

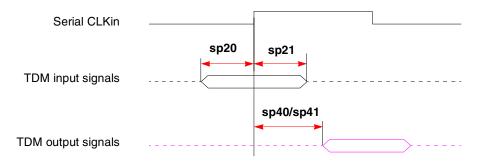

| sp40   | sp41   | TDM outputs/SI                                   | 25     | 16             | 5      | 4              |  |

| sp38a  | sp39a  | SCC/SMC/SPI/I2C outputs—internal clock (NMSI)    | 19     | 16             | 1      | 0.5            |  |

| sp38b  | sp39b  | Ex_SCC/SMC/SPI/I2C outputs—external clock (NMSI) | 19     | 16             | 2      | 1              |  |

| sp42   | sp43   | TIMER/IDMA outputs                               | 14     | 11             | 1      | 0.5            |  |

| sp42a  | sp43a  | PIO outputs                                      | 14     | 11             | 0.5    | 0.5            |  |

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

Table 8 lists CPM input characteristics.

| Spec N | lumber | Characteristic                               |        | Setup (ns) |        | Hold (ns) |  |

|--------|--------|----------------------------------------------|--------|------------|--------|-----------|--|

| Max    | Min    |                                              | 66 MHz | 83 MHz     | 66 MHz | 83 MHz    |  |

| sp16a  | sp17a  | FCC inputs—internal clock (NMSI)             | 10     | 8          | 0      | 0         |  |

| sp16b  | sp17b  | FCC inputs—external clock (NMSI)             | 3      | 2.5        | 3      | 2         |  |

| sp20   | sp21   | TDM inputs/SI                                | 15     | 12         | 12     | 10        |  |

| sp18a  | sp19a  | SCC/SMC/SPI/I2C inputs—internal clock (NMSI) | 20     | 16         | 0      | 0         |  |

| sp18b  | sp19b  | SCC/SMC/SPI/I2C inputs—external clock (NMSI) | 5      | 4          | 5      | 4         |  |

| sp22   | sp23   | PIO/TIMER/IDMA inputs                        | 10     | 8          | 3      | 3         |  |

| Tahla 8  | AC | Characteristics | for | CPM | Innute <sup>1</sup> |

|----------|----|-----------------|-----|-----|---------------------|

| Table o. | AC | Characteristics | 101 |     | mputs               |

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

Note that although the specifications generally reference the rising edge of the clock, the following AC timing diagrams also apply when the falling edge is the active edge.

Figure 3 shows the FCC external clock.

Figure 3. FCC External Clock Diagram

#### **Electrical and Thermal Characteristics**

# Figure 4 shows the FCC internal clock.

Figure 4. FCC Internal Clock Diagram

Figure 5 shows the SCC/SMC/SPI/I<sup>2</sup>C external clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

### Figure 5. SCC/SMC/SPI/I<sup>2</sup>C External Clock Diagram

# Figure 6 shows the SCC/SMC/SPI/I<sup>2</sup>C internal clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

Figure 7 shows TDM input and output signals.

Note: There are four possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

#### Figure 7. TDM Signal Diagram

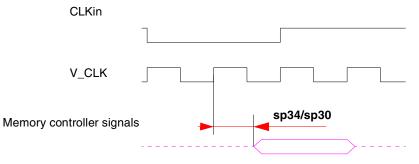

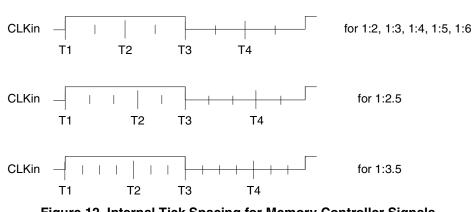

Figure 11 shows signal behavior in MEMC mode.

1:2, 1:3, 1:4, 1:5, 1:6

1:2.5

1:3.5

Figure 11. MEMC Mode Diagram

### NOTE

Generally, all MPC826xA bus and system output signals are driven from the rising edge of the input clock (CLKin). Memory controller signals, however, trigger on four points within a CLKin cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and T3 at the falling edge, of CLKin. However, the spacing of T2 and T4 depends on the PLL clock ratio selected, as shown in Table 11.

| PLL Clock Ratio | Tick Spacing (T1 Occurs at the Rising Edge of CLKin) |    |    |  |  |

|-----------------|------------------------------------------------------|----|----|--|--|

|                 | Т2                                                   | Т3 | Τ4 |  |  |

1/2 CLKin

1/2 CLKin

1/2 CLKin

3/4 CLKin

8/10 CLKin

11/14 CLKin

1/4 CLKin

3/10 CLKin

4/14 CLKin

Figure 12 is a graphical representation of Table 11.

| Table 11. | Tick Spacing for I | Memory Controller Signals |

|-----------|--------------------|---------------------------|

|-----------|--------------------|---------------------------|

Figure 12. Internal Tick Spacing for Memory Controller Signals

#### **Electrical and Thermal Characteristics**

## Table 12 lists the JTAG timings.

Table 12. JTAG Timings<sup>1</sup>

| Parameter                                                                 | Symbol <sup>2</sup>                        | Min      | Max      | Unit     | Notes        |

|---------------------------------------------------------------------------|--------------------------------------------|----------|----------|----------|--------------|

| JTAG external clock frequency of operation                                | f <sub>JTG</sub>                           | 0        | 25       | MHz      | —            |

| JTAG external clock cycle time                                            | t <sub>JTG</sub>                           | 40       |          | ns       | —            |

| JTAG external clock pulse width measured at 1.4V                          | t <sub>JTKHKL</sub>                        | 20       | _        | ns       | —            |

| JTAG external clock rise and fall times                                   | t <sub>JTGR</sub> and<br>t <sub>JTGF</sub> | 0        | 5        | ns       | 6            |

| TRST assert time                                                          | t <sub>TRST</sub>                          | 25       |          | ns       | 3, 6         |

| Input setup times<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   | _        | ns<br>ns | 4, 7<br>4, 7 |

| Input hold times<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns<br>ns | 4, 7<br>4, 7 |

| Output valid times<br>Boundary-scan data<br>TDO                           | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> |          | 25<br>25 | ns<br>ns | 5, 7<br>5. 7 |

| Output hold times<br>Boundary-scan data<br>TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 1<br>1   |          | ns<br>ns | 5, 7<br>5, 7 |

| JTAG external clock to output high impedance<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 1<br>1   | 25<br>25 | ns<br>ns | 5, 6<br>5, 6 |

<sup>1</sup> All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load. Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

<sup>2</sup> The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t((first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- <sup>3</sup> TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- <sup>4</sup> Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- <sup>5</sup> Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- <sup>6</sup> Guaranteed by design.

- <sup>7</sup> Guaranteed by design and device characterization.

### NOTE

The UPM machine outputs change on the internal tick determined by the memory controller programming; the AC specifications are relative to the internal tick. Note that SDRAM and GPCM machine outputs change on CLKin's rising edge.

# **3** Clock Configuration Modes

To configure the main PLL multiplication factor and the core, CPM, and 60x bus frequencies, the MODCK[1–3] pins are sampled while HRESET is asserted. Table 13 lists the eight basic configuration modes. Table 14 lists the other modes that are available by using the configuration pin (RSTCONF) and driving four bits from hardware configuration word on the data bus.

Note that the MPC8265 and the MPC8266 have two additional clocking modes—PCI agent and PCI host. Refer to Section 3.2, "PCI Mode" on page 26 for information.

### NOTE

Clock configurations change only after  $\overline{POR}$  is asserted.

# 3.1 Local Bus Mode

Table 13 describes default clock modes for the MPC826xA.

| MODCK[1-3] | Input Clock<br>Frequency | CPM Multiplication<br>Factor | CPM<br>Frequency | Core Multiplication<br>Factor | Core<br>Frequency |

|------------|--------------------------|------------------------------|------------------|-------------------------------|-------------------|

| 000        | 33 MHz                   | 3                            | 100 MHz          | 4                             | 133 MHz           |

| 001        | 33 MHz                   | 3                            | 100 MHz          | 5                             | 166 MHz           |

| 010        | 33 MHz                   | 4                            | 133 MHz          | 4                             | 133 MHz           |

| 011        | 33 MHz                   | 4                            | 133 MHz          | 5                             | 166 MHz           |

| 100        | 66 MHz                   | 2                            | 133 MHz          | 2.5                           | 166 MHz           |

| 101        | 66 MHz                   | 2                            | 133 MHz          | 3                             | 200 MHz           |

| 110        | 66 MHz                   | 2.5                          | 166 MHz          | 2.5                           | 166 MHz           |

| 111        | 66 MHz                   | 2.5                          | 166 MHz          | 3                             | 200 MHz           |

### Table 13. Clock Default Modes

Table 14 describes all possible clock configurations when using the hard reset configuration sequence. Note that basic modes are shown in boldface type. The frequencies listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device.

| Table 14. C | lock Configuration Modes <sup>1</sup> |

|-------------|---------------------------------------|

|-------------|---------------------------------------|

| MODCK_H-MODCK[1-3] | Input Clock<br>Frequency <sup>2,3</sup> | CPM Multiplication<br>Factor <sup>2</sup> | CPM<br>Frequency <sup>2</sup> | Core Multiplication<br>Factor <sup>2</sup> | Core<br>Frequency <sup>2</sup> |

|--------------------|-----------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------|

| 0001_000           | 33 MHz                                  | 2                                         | 66 MHz                        | 4                                          | 133 MHz                        |

| 0001_001           | 33 MHz                                  | 2                                         | 66 MHz                        | 5                                          | 166 MHz                        |

| 0001_010           | 33 MHz                                  | 2                                         | 66 MHz                        | 6                                          | 200 MHz                        |

| 0001_011           | 33 MHz                                  | 2                                         | 66 MHz                        | 7                                          | 233 MHz                        |

| 0001_100           | 33 MHz                                  | 2                                         | 66 MHz                        | 8                                          | 266 MHz                        |

**Clock Configuration Modes**

|                    |                                         |                                           |                               | ,                                          | 0.0 m                          |

|--------------------|-----------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------|

| MODCK_H-MODCK[1-3] | Input Clock<br>Frequency <sup>2,3</sup> | CPM Multiplication<br>Factor <sup>2</sup> | CPM<br>Frequency <sup>2</sup> | Core Multiplication<br>Factor <sup>2</sup> | Core<br>Frequency <sup>2</sup> |

|                    |                                         |                                           |                               |                                            |                                |

| 0001_101           | 33 MHz                                  | 3                                         | 100 MHz                       | 4                                          | 133 MHz                        |

| 0001_110           | 33 MHz                                  | 3                                         | 100 MHz                       | 5                                          | 166 MHz                        |

| 0001_111           | 33 MHz                                  | 3                                         | 100 MHz                       | 6                                          | 200 MHz                        |

| 0010_000           | 33 MHz                                  | 3                                         | 100 MHz                       | 7                                          | 233 MHz                        |

| 0010_001           | 33 MHz                                  | 3                                         | 100 MHz                       | 8                                          | 266 MHz                        |

| 0010_010           | 33 MHz                                  | 4                                         | 133 MHz                       | 4                                          | 133 MHz                        |

| 0010_010           | 33 MHz                                  | 4                                         | 133 MHz                       | 5                                          | 166 MHz                        |

| 0010_100           | 33 MHz                                  | 4                                         | 133 MHz                       | 6                                          | 200 MHz                        |

| 0010_100           | 33 MHz                                  | 4                                         | 133 MHz                       | 7                                          | 233 MHz                        |

| 0010_101           |                                         | 4                                         |                               |                                            |                                |

| 0010_110           | 33 MHz                                  | 4                                         | 133 MHz                       | 8                                          | 266 MHz                        |

| 0010_111           | 33 MHz                                  | 5                                         | 166 MHz                       | 4                                          | 133 MHz                        |

| 0011_000           | 33 MHz                                  | 5                                         | 166 MHz                       | 5                                          | 166 MHz                        |

| 0011_001           | 33 MHz                                  | 5                                         | 166 MHz                       | 6                                          | 200 MHz                        |

| 0011_010           | 33 MHz                                  | 5                                         | 166 MHz                       | 7                                          | 233 MHz                        |

| 0011_011           | 33 MHz                                  | 5                                         | 166 MHz                       | 8                                          | 266 MHz                        |

|                    |                                         |                                           |                               |                                            |                                |

| 0011_100           | 33 MHz                                  | 6                                         | 200 MHz                       | 4                                          | 133 MHz                        |

| 0011_101           | 33 MHz                                  | 6                                         | 200 MHz                       | 5                                          | 166 MHz                        |

| 0011_110           | 33 MHz                                  | 6                                         | 200 MHz                       | 6                                          | 200 MHz                        |

| 0011_111           | 33 MHz                                  | 6                                         | 200 MHz                       | 7                                          | 233 MHz                        |

| 0100_000           | 33 MHz                                  | 6                                         | 200 MHz                       | 8                                          | 266 MHz                        |

| 0100_001           |                                         |                                           | Reserved                      |                                            |                                |

| 0100_001           | -                                       |                                           | I IESEI VEU                   |                                            |                                |

|                    |                                         |                                           |                               |                                            |                                |

| 0100_011           |                                         |                                           |                               |                                            |                                |

| 0100_100           | -                                       |                                           |                               |                                            |                                |

| 0100_101           | -                                       |                                           |                               |                                            |                                |

| 0100_110           |                                         |                                           |                               |                                            |                                |

# Table 14. Clock Configuration Modes<sup>1</sup> (continued)

| MODCK_H-MODCK[1-3] | Input Clock<br>Frequency <sup>2,3</sup> | CPM Multiplication<br>Factor <sup>2</sup> | CPM<br>Frequency <sup>2</sup> | Core Multiplication<br>Factor <sup>2</sup> | Core<br>Frequency <sup>2</sup> |

|--------------------|-----------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------|

| 0100_111           |                                         |                                           | Reserved                      |                                            |                                |

| 0101_000           | -                                       |                                           |                               |                                            |                                |

| 0101_001           | -                                       |                                           |                               |                                            |                                |

| 0101_010           | -                                       |                                           |                               |                                            |                                |

| 0101_011           | -                                       |                                           |                               |                                            |                                |

| 0101_100           |                                         |                                           |                               |                                            |                                |

| 0101_101           | 66 MHz                                  | 2                                         | 133 MHz                       | 2                                          | 133 MHz                        |

| 0101_110           | 66 MHz                                  | 2                                         | 133 MHz                       | 2.5                                        | 166 MHz                        |

| 0101_111           | 66 MHz                                  | 2                                         | 133 MHz                       | 3                                          | 200 MHz                        |

| 0110_000           | 66 MHz                                  | 2                                         | 133 MHz                       | 3.5                                        | 233 MHz                        |

| 0110_001           | 66 MHz                                  | 2                                         | 133 MHz                       | 4                                          | 266 MHz                        |

| 0110_010           | 66 MHz                                  | 2                                         | 133 MHz                       | 4.5                                        | 300 MHz                        |

|                    |                                         |                                           |                               |                                            | •                              |

| 0110_011           | 66 MHz                                  | 2.5                                       | 166 MHz                       | 2                                          | 133 MHz                        |

| 0110_100           | 66 MHz                                  | 2.5                                       | 166 MHz                       | 2.5                                        | 166 MHz                        |

| 0110_101           | 66 MHz                                  | 2.5                                       | 166 MHz                       | 3                                          | 200 MHz                        |

| 0110_110           | 66 MHz                                  | 2.5                                       | 166 MHz                       | 3.5                                        | 233 MHz                        |

| 0110_111           | 66 MHz                                  | 2.5                                       | 166 MHz                       | 4                                          | 266 MHz                        |

| 0111_000           | 66 MHz                                  | 2.5                                       | 166 MHz                       | 4.5                                        | 300 MHz                        |

|                    |                                         |                                           |                               |                                            |                                |

| 0111_001           | 66 MHz                                  | 3                                         | 200 MHz                       | 2                                          | 133 MHz                        |

| 0111_010           | 66 MHz                                  | 3                                         | 200 MHz                       | 2.5                                        | 166 MHz                        |

| 0111_011           | 66 MHz                                  | 3                                         | 200 MHz                       | 3                                          | 200 MHz                        |

| 0111_100           | 66 MHz                                  | 3                                         | 200 MHz                       | 3.5                                        | 233 MHz                        |

| 0111_101           | 66 MHz                                  | 3                                         | 200 MHz                       | 4                                          | 266 MHz                        |

| 0111_110           | 66 MHz                                  | 3                                         | 200 MHz                       | 4.5                                        | 300 MHz                        |

|                    |                                         |                                           |                               |                                            |                                |

| 0111_111           | 66 MHz                                  | 3.5                                       | 233 MHz                       | 2                                          | 133 MHz                        |

| 1000_000           | 66 MHz                                  | 3.5                                       | 233 MHz                       | 2.5                                        | 166 MHz                        |

# Table 14. Clock Configuration Modes<sup>1</sup> (continued)

**Clock Configuration Modes**

| MODCK_H –<br>MODCK[1–3] | Input Clock<br>Frequency<br>(PCI) <sup>1,2</sup> | CPM<br>Multiplication<br>Factor <sup>1</sup> | CPM<br>Frequency | Core<br>Multiplication<br>Factor | Core<br>Frequency <sup>3</sup> | Bus Division<br>Factor | 60x Bus<br>Frequency <sup>4</sup> |

|-------------------------|--------------------------------------------------|----------------------------------------------|------------------|----------------------------------|--------------------------------|------------------------|-----------------------------------|

| 1010_001                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3                                | 266 MHz                        | 3                      | 88 MHz                            |

| 1010_010                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3.5                              | 300 MHz                        | 3                      | 88 MHz                            |

| 1010_011                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 4                                | 350 MHz                        | 3                      | 88 MHz                            |

| 1010_100                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 4.5                              | 400 MHz                        | 3                      | 88 MHz                            |

|                         |                                                  |                                              |                  |                                  |                                |                        |                                   |

| 1011_000                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 2                                | 212MHz                         | 2.5                    | 106 MHz                           |

| 1011_001                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 2.5                              | 265 MHz                        | 2.5                    | 106 MHz                           |

| 1011_010                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3                                | 318 MHz                        | 2.5                    | 106 MHz                           |

| 1011_011                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3.5                              | 371 MHz                        | 2.5                    | 106 MHz                           |

| 1011_100                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 4                                | 424 MHz                        | 2.5                    | 106 MHz                           |

Table 19. Clock Configuration Modes in PCI Agent Mode (continued)

<sup>1</sup> The frequency depends on the value of PCI\_MODCK. If PCI\_MODCK is high (logic '1'), the PCI frequency is divided by 2 (33 instead of 66 MHz, etc.) and the CPM multiplication factor is multiplied by 2. Refer to Table 15.

<sup>2</sup> Input clock frequency is given only for the purpose of reference. User should set MODCK\_H–MODCK\_L so that the resulting configuration does not exceed the frequency rating of the user's part.

<sup>3</sup> Core frequency = (60x bus frequency)(core multiplication factor)

<sup>4</sup> Bus frequency = CPM frequency/bus division factor

<sup>5</sup> In this mode, PCI\_MODCK must be "1".

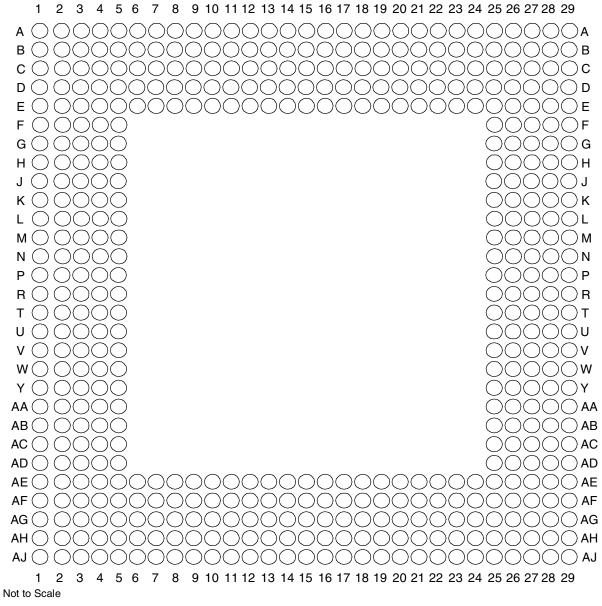

# 4 Pinout

This section provides the pin assignments and pinout list for the MPC826xA.

# 4.1 **Pin Assignments**

Figure 13 shows the pinout of the MPC826xA's 480 TBGA package as viewed from the top surface.

Figure 13. Pinout of the 480 TBGA Package as Viewed from the Top Surface

| Pin Name                   | Ball |

|----------------------------|------|

| D32                        | E18  |

| D33                        | B17  |

| D34                        | A15  |

| D35                        | A12  |

| D36                        | D11  |

| D37                        | C8   |

| D38                        | E7   |

| D39                        | A3   |

| D40                        | D18  |

| D41                        | A17  |

| D42                        | A14  |

| D43                        | B12  |

| D44                        | A10  |

| D45                        | D8   |

| D46                        | B6   |

| D47                        | C4   |

| D48                        | C18  |

| D49                        | E16  |

| D50                        | B14  |

| D51                        | C12  |

| D52                        | B10  |

| D53                        | A7   |

| D54                        | C6   |

| D55                        | D5   |

| D56                        | B18  |

| D57                        | B16  |

| D58                        | E14  |

| D59                        | D12  |

| D60                        | C10  |

| D61                        | E8   |

| D62                        | D6   |

| D63                        | C2   |

| DP0/RSRV/EXT_BR2           | B22  |

| IRQ1/DP1/EXT_BG2           | A22  |

| IRQ2/DP2/TLBISYNC/EXT_DBG2 | E21  |

# Table 21. Pinout List (continued)

| Pin Name                     | Ball |

|------------------------------|------|

| IRQ3/DP3/CKSTP_OUT/EXT_BR3   | D21  |

| IRQ4/DP4/CORE_SRESET/EXT_BG3 | C21  |

| IRQ5/DP5/TBEN/EXT_DBG3       | B21  |

| IRQ6/DP6/CSE0                | A21  |

| IRQ7/DP7/CSE1                | E20  |

| PSDVAL                       | V3   |

| ТА                           | C22  |

| TEA                          | V5   |

| GBL/IRQ1                     | W1   |

| CI/BADDR29/IRQ2              | U2   |

| WT/BADDR30/IRQ3              | U3   |

| L2_HIT/IRQ4                  | Y4   |

| CPU_BG/BADDR31/IRQ5          | U4   |

| CPU_DBG                      | R2   |

| CPU_BR                       | Y3   |

| CS0                          | F25  |

| CS1                          | C29  |

| CS2                          | E27  |

| CS3                          | E28  |

| CS4                          | F26  |

| CS5                          | F27  |

| CS6                          | F28  |

| CS7                          | G25  |

| CS8                          | D29  |

| CS9                          | E29  |

| CS10/BCTL1                   | F29  |

| CS11/AP0                     | G28  |

| BADDR27                      | T5   |

| BADDR28                      | U1   |

| ALE                          | T2   |

| BCTL0                        | A27  |

| PWE0/PSDDQM0/PBS0            | C25  |

| PWE1/PSDDQM1/PBS1            | E24  |

| PWE2/PSDDQM2/PBS2            | D24  |

| PWE3/PSDDQM3/PBS3            | C24  |

Pinout

# Table 21. Pinout List (continued)

| Pin Name                                                       | Ball              |

|----------------------------------------------------------------|-------------------|

| PA12/FCC1_UT8_RXD2/FCC1_UT16_RXD10/MSNUM3                      | AJ21 <sup>2</sup> |

| PA13/FCC1_UT8_RXD3/FCC1_UT16_RXD11/MSNUM2                      | AH20 <sup>2</sup> |

| PA14/FCC1_UT8_RXD4/FCC1_UT16_RXD12/FCC1_RXD3                   | AG19 <sup>2</sup> |

| PA15/FCC1_UT8_RXD5/FCC1_UT16_RXD13/FCC1_RXD2                   | AF18 <sup>2</sup> |

| PA16/FCC1_UT8_RXD6/FCC1_UT16_RXD14/FCC1_RXD1                   | AF17 <sup>2</sup> |

| PA17/FCC1_UT8_RXD7/FCC1_UT16_RXD15/FCC1_RXD0/FCC1_RXD          | AE16 <sup>2</sup> |

| PA18/FCC1_UT8_TXD7/FCC1_UT16_TXD15/FCC1_TXD0/FCC1_TXD          | AJ16 <sup>2</sup> |

| PA19/FCC1_UT8_TXD6/FCC1_UT16_TXD14/FCC1_TXD1                   | AG15 <sup>2</sup> |

| PA20/FCC1_UT8_TXD5/FCC1_UT16_TXD13/FCC1_TXD2                   | AJ13 <sup>2</sup> |

| PA21/FCC1_UT8_TXD4/FCC1_UT16_TXD12/FCC1_TXD3                   | AE13 <sup>2</sup> |

| PA22/FCC1_UT8_TXD3/FCC1_UT16_TXD11                             | AF12 <sup>2</sup> |

| PA23/FCC1_UT8_TXD2/FCC1_UT16_TXD10                             | AG11 <sup>2</sup> |

| PA24/FCC1_UT8_TXD1/FCC1_UT16_TXD9/MSNUM1                       | AH9 <sup>2</sup>  |

| PA25/FCC1_UT8_TXD0/FCC1_UT16_TXD8/MSNUM0                       | AJ8 <sup>2</sup>  |

| PA26/FCC1_UTM_RXCLAV/FCC1_UTS_RXCLAV/FCC1_MII_RX_ER            | AH7 <sup>2</sup>  |

| PA27/FCC1_UT_RXSOC/FCC1_MII_RX_DV                              | AF7 <sup>2</sup>  |

| PA28/FCC1_UTM_RXENB/FCC1_UTS_RXENB/FCC1_MII_TX_EN              | AD5 <sup>2</sup>  |

| PA29/FCC1_UT_TXSOC/FCC1_MII_TX_ER                              | AF1 <sup>2</sup>  |

| PA30/FCC1_UTM_TXCLAV/FCC1_UTS_TXCLAV/FCC1_MII_CRS/<br>FCC1_RTS | AD3 <sup>2</sup>  |

| PA31/FCC1_UTM_TXENB/FCC1_UTS_TXENB/FCC1_MII_COL                | AB5 <sup>2</sup>  |

| PB4/FCC3_TXD3/FCC2_UT8_RXD0/L1RSYNCA2/FCC3_RTS                 | AD28 <sup>2</sup> |

| PB5/FCC3_TXD2/FCC2_UT8_RXD1/L1TSYNCA2/L1GNTA2                  | AD26 <sup>2</sup> |

| PB6/FCC3_TXD1/FCC2_UT8_RXD2/L1RXDA2/L1RXD0A2                   | AD25 <sup>2</sup> |

| PB7/FCC3_TXD0/FCC3_TXD/FCC2_UT8_RXD3/L1TXDA2/L1TXD0A2          | AE26 <sup>2</sup> |

| PB8/FCC2_UT8_TXD3/FCC3_RXD0/FCC3_RXD/TXD3/L1RSYNCD1            | AH27 <sup>2</sup> |

| PB9/FCC2_UT8_TXD2/FCC3_RXD1/L1TXD2A2/L1TSYNCD1/L1GNTD1         | AG24 <sup>2</sup> |

| PB10/FCC2_UT8_TXD1/FCC3_RXD2/L1RXDD1                           | AH24 <sup>2</sup> |

| PB11/FCC3_RXD3/FCC2_UT8_TXD0/L1TXDD1                           | AJ24 <sup>2</sup> |

| PB12/FCC3_MII_CRS/L1CLKOB1/L1RSYNCC1/TXD2                      | AG22 <sup>2</sup> |

| PB13/FCC3_MII_COL/L1RQB1/L1TSYNCC1/L1GNTC1/L1TXD1A2            | AH21 <sup>2</sup> |

| PB14/FCC3_MII_TX_EN/RXD3/L1RXDC1                               | AG20 <sup>2</sup> |

| PB15/FCC3_MII_TX_ER/RXD2/L1TXDC1                               | AF19 <sup>2</sup> |

| PB16/FCC3_MII_RX_ER/L1CLKOA1/CLK18                             | AJ18 <sup>2</sup> |

| PB17/FCC3_MII_RX_DV/L1RQA1/CLK17                               | AJ17 <sup>2</sup> |

| Table 21 | Pinout List | (continued) |

|----------|-------------|-------------|

|----------|-------------|-------------|

| Pin Name                                                                   | Ball              |

|----------------------------------------------------------------------------|-------------------|

| PB18/FCC2_UT8_RXD4/FCC2_RXD3/L1CLKOD2/L1RXD2A2                             | AE14 <sup>2</sup> |

| PB19/FCC2_UT8_RXD5/FCC2_RXD2/L1RQD2/L1RXD3A2                               | AF13 <sup>2</sup> |

| PB20/FCC2_UT8_RXD6/FCC2_RXD1/L1RSYNCD2/L1TXD1A1                            | AG12 <sup>2</sup> |

| PB21/FCC2_UT8_RXD7/FCC2_RXD0/FCC2_RXD/L1TSYNCD2/L1GNTD2/<br>L1TXD2A1       | AH11 <sup>2</sup> |

| PB22/FCC2_UT8_TXD7/FCC2_TXD0/FCC2_TXD/L1RXD1A1/L1RXDD2                     | AH16 <sup>2</sup> |

| PB23/FCC2_UT8_TXD6/FCC2_TXD1/L1RXD2A1/L1TXDD2                              | AE15 <sup>2</sup> |

| PB24/FCC2_UT8_TXD5/FCC2_TXD2/L1RXD3A1/L1RSYNCC2                            | AJ9 <sup>2</sup>  |

| PB25/FCC2_UT8_TXD4/FCC2_TXD3/L1TSYNCC2/L1GNTC2/L1TXD3A1                    | AE9 <sup>2</sup>  |

| PB26/FCC2_MII_CRS/FCC2_UT8_TXD1/L1RXDC2                                    | AJ7 <sup>2</sup>  |

| PB27/FCC2_MII_COL/FCC2_UT8_TXD0/L1TXDC2                                    | AH6 <sup>2</sup>  |

| PB28/FCC2_MII_RX_ER/FCC2_RTS/L1TSYNCB2/L1GNTB2/TXD1                        | AE3 <sup>2</sup>  |

| PB29/FCC2_UTM_RXCLAV/FCC2_UTS_RXCLAV/L1RSYNCB2/<br>FCC2_MII_TX_EN          | AE2 <sup>2</sup>  |

| PB30/FCC2_MII_RX_DV/FCC2_UT_TXSOC/L1RXDB2                                  | AC5 <sup>2</sup>  |

| PB31/FCC2_MII_TX_ER/FCC2_UT_RXSOC/L1TXDB2                                  | AC4 <sup>2</sup>  |

| PC0/DREQ1/BRG07/SMSYN2/L1CLKOA2                                            | AB26 <sup>2</sup> |

| PC1/DREQ2/BRGO6/L1RQA2                                                     | AD29 <sup>2</sup> |

| PC2/FCC3_CD/FCC2_UT8_TXD3/DONE2                                            | AE29 <sup>2</sup> |

| PC3/FCC3_CTS/FCC2_UT8_TXD2/DACK2/CTS4                                      | AE27 <sup>2</sup> |

| PC4/FCC2_UTM_RXENB/FCC2_UTS_RXENB/SI2_L1ST4/FCC2_CD                        | AF27 <sup>2</sup> |

| PC5/FCC2_UTM_TXCLAV/FCC2_UTS_TXCLAV/SI2_L1ST3/FCC2_CTS                     | AF24 <sup>2</sup> |

| PC6/FCC1_CD/L1CLKOC1/FCC1_UTM_RXADDR2/FCC1_UTS_RXADDR/<br>FCC1_UTM_RXCLAV1 | AJ26 <sup>2</sup> |

| PC7/FCC1_CTS/L1RQC1/FCC1_UTM_TXADDR2/FCC1_UTS_TXADDR2/<br>FCC1_UTM_TXCLAV1 | AJ25 <sup>2</sup> |

| PC8/CD4/RENA4/FCC1_UT16_TXD0/SI2_L1ST2/CTS3                                | AF22 <sup>2</sup> |

| PC9/CTS4/CLSN4/FCC1_UT16_TXD1/SI2_L1ST1/L1TSYNCA2/L1GNTA2                  | AE21 <sup>2</sup> |

| PC10/CD3/RENA3/FCC1_UT16_TXD2/SI1_L1ST4/FCC2_UT8_RXD3                      | AF20 <sup>2</sup> |

| PC11/CTS3/CLSN3/L1CLKOD1/L1TXD3A2/FCC2_UT8_RXD2                            | AE19 <sup>2</sup> |

| PC12/CD2/RENA2/SI1_L1ST3/FCC1_UTM_RXADDR1/<br>FCC1_UTS_RXADDR1             | AE18 <sup>2</sup> |

| PC13/CTS2/CLSN2/L1RQD1/FCC1_UTM_TXADDR1/<br>FCC1_UTS_TXADDR1               | AH18 <sup>2</sup> |

| PC14/CD1/RENA1/FCC1_UTM_RXADDR0/FCC1_UTS_RXADDR0                           | AH17 <sup>2</sup> |

| PC15/CTS1/CLSN1/SMTXD2/FCC1_UTM_TXADDR0/<br>FCC1_UTS_TXADDR0               | AG16 <sup>2</sup> |

| Pin Name                                                                                | Ball                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD21/TXD4/FCC1_UT16_RXD3/L1RXD0A2/L1RXDA2                                               | AH13 <sup>2</sup>                                                                                                                                                                                                                                          |

| PD22/RXD4/FCC1_UT16_TXD5/L1TXD0A2/L1TXDA2                                               | AJ12 <sup>2</sup>                                                                                                                                                                                                                                          |

| PD23/RTS3/TENA3/FCC1_UT16_RXD4/L1RSYNCD1                                                | AE12 <sup>2</sup>                                                                                                                                                                                                                                          |

| PD24/TXD3/FCC1_UT16_RXD5/L1RXDD1                                                        | AF10 <sup>2</sup>                                                                                                                                                                                                                                          |

| PD25/RXD3/FCC1_UT16_TXD6/L1TXDD1                                                        | AG9 <sup>2</sup>                                                                                                                                                                                                                                           |

| PD26/RTS2/TENA2/FCC1_UT16_RXD6/L1RSYNCC1                                                | AH8 <sup>2</sup>                                                                                                                                                                                                                                           |

| PD27/TXD2/FCC1_UT16_RXD7/L1RXDC1                                                        | AG7 <sup>2</sup>                                                                                                                                                                                                                                           |

| PD28/RXD2/FCC1_UT16_TXD7/L1TXDC1                                                        | AE4 <sup>2</sup>                                                                                                                                                                                                                                           |

| PD29/RTS1/TENA1/FCC1_UTM_RXADDR3/FCC1_UTS_RXADDR3/<br>FCC1_UTM_RXCLAV2/FCC2_UTM_RXADDR4 | AG1 <sup>2</sup>                                                                                                                                                                                                                                           |

| PD30/FCC2_UTM_TXENB/FCC2_UTS_TXENB/TXD1                                                 | AD4 <sup>2</sup>                                                                                                                                                                                                                                           |

| PD31/RXD1                                                                               | AD2 <sup>2</sup>                                                                                                                                                                                                                                           |

| VCCSYN                                                                                  | AB3                                                                                                                                                                                                                                                        |

| VCCSYN1                                                                                 | B9                                                                                                                                                                                                                                                         |

| GNDSYN                                                                                  | AB1                                                                                                                                                                                                                                                        |

| CLKIN2 <sup>1,3</sup>                                                                   | AE11                                                                                                                                                                                                                                                       |

| SPARE4 <sup>4</sup>                                                                     | U5                                                                                                                                                                                                                                                         |

| PCI_MODE <sup>1,5</sup>                                                                 | AF25                                                                                                                                                                                                                                                       |

| SPARE6 <sup>4</sup>                                                                     | V4                                                                                                                                                                                                                                                         |

| THERMAL0 <sup>6</sup>                                                                   | AA1                                                                                                                                                                                                                                                        |

| THERMAL1 <sup>6</sup>                                                                   | AG4                                                                                                                                                                                                                                                        |

| I/O power                                                                               | AG21, AG14, AG8, AJ1, AJ2, AH1, AH2,<br>AG3, AF4, AE5, AC27, Y27, T27, P27,<br>K26, G27, AE25, AF26, AG27, AH28,<br>AH29, AJ28, AJ29, C7, C14, C16, C20,<br>C23, E10, A28, A29, B28, B29, C27,<br>D26, E25, H3, M4, T3, AA4, A1, A2, B1,<br>B2, C3, D4, E5 |

| Core Power                                                                              | U28, U29, K28, K29, A9, A19, B19, M1,<br>M2, Y1, Y2, AC1, AC2, AH19, AJ19,<br>AH10, AJ10, AJ5                                                                                                                                                              |

| Ground                                                                                  | AA5, AF21, AF14, AF8, AE7, AF11,<br>AE17, AE23, AC26, AB25, Y26, V25,<br>T26, R25, P26, M25, K27, H25, G26,<br>D7, D10, D14, D16, D20, D23, C9, E11,<br>E13, E15, E19, E22, B3, G5, H4, K5,<br>M3, P5, T4, Y5, AA2, AC3                                    |

<sup>1</sup> MPC8265 and MPC8266 only.

<sup>2</sup> The default configuration of the CPM pins (PA[0–31], PB[4–31], PC[0–31], PD[4–31]) is input. To prevent excessive DC current, it is recommended to either pull unused pins to GND or VDDH, or to configure them as outputs.