Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC G2                                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 300MHz                                                                  |

| Co-Processors/DSP               | Communications; RISC CPM                                                |

| RAM Controllers                 | DRAM, SDRAM                                                             |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100Mbps (3)                                                          |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 3.3V                                                                    |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 480-LBGA Exposed Pad                                                    |

| Supplier Device Package         | 480-TBGA (37.5x37.5)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8264azupjdb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Features**

- 32-bit address decodes with programmable bank size

- Three user programmable machines, general-purpose chip-select machine, and page-mode pipeline SDRAM machine

- Byte selects for 64 bus width (60x) and byte selects for 32 bus width (local)

- Dedicated interface logic for SDRAM

- CPU core can be disabled and the device can be used in slave mode to an external core

- Communications processor module (CPM)

- Embedded 32-bit communications processor (CP) uses a RISC architecture for flexible support for communications protocols

- Interfaces to G2 core through on-chip 32-Kbyte dual-port RAM and DMA controller

- Serial DMA channels for receive and transmit on all serial channels

- Parallel I/O registers with open-drain and interrupt capability

- Virtual DMA functionality executing memory-to-memory and memory-to-I/O transfers

- Three fast communications controllers supporting the following protocols (only FCC1 and FCC2 on the MPC8255):

- 10/100-Mbit Ethernet/IEEE Std. 802.3® CDMA/CS interface through media independent interface (MII)

- ATM—Full-duplex SAR protocols at 155 Mbps, through UTOPIA interface, AAL5, AAL1, AAL0 protocols, TM 4.0 CBR, VBR, UBR, ABR traffic types, up to 16 K external connections

- Transparent

- HDLC—Up to T3 rates (clear channel)

- Two multichannel controllers (MCCs) (only MCC2 on the MPC8255)

- Each MCC handles 128 serial, full-duplex, 64-Kbps data channels. Each MCC can be split

into four subgroups of 32 channels each.

- Almost any combination of subgroups can be multiplexed to single or multiple TDM interfaces up to four TDM interfaces per MCC

- Four serial communications controllers (SCCs) identical to those on the MPC860, supporting the digital portions of the following protocols:

- Ethernet/IEEE 802.3 CDMA/CS

- HDLC/SDLC and HDLC bus

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Binary synchronous (BISYNC) communications

- Transparent

- Two serial management controllers (SMCs), identical to those of the MPC860

- Provide management for BRI devices as general circuit interface (GCI) controllers in timedivision-multiplexed (TDM) channels

- Transparent

- UART (low-speed operation)

- One serial peripheral interface identical to the MPC860 SPI

- One inter-integrated circuit (I<sup>2</sup>C) controller (identical to the MPC860 I<sup>2</sup>C controller)

- Microwire compatible

- Multiple-master, single-master, and slave modes

- Up to eight TDM interfaces (four on the MPC8255)

- Supports two groups of four TDM channels for a total of eight TDMs

- 2,048 bytes of SI RAM

- Bit or byte resolution

- Independent transmit and receive routing, frame synchronization

- Supports T1, CEPT, T1/E1, T3/E3, pulse code modulation highway, ISDN basic rate, ISDN primary rate, Freescale interchip digital link (IDL), general circuit interface (GCI), and user-defined TDM serial interfaces

- Eight independent baud rate generators and 20 input clock pins for supplying clocks to FCCs, SCCs, SMCs, and serial channels

- Four independent 16-bit timers that can be interconnected as two 32-bit timers

## Additional features of the MPC826xA family are as follows:

### CPM

- 32-Kbyte dual-port RAM

- Additional MCC host commands

- Eight transfer transmission convergence (TC) layers between the TDMs and FCC2 to support inverse multiplexing for ATM capabilities (IMA) (MPC8264 and MPC8266 only)

- CPM multiplexing

- FCC2 can also be connected to the TC layer.

- TC layer (MPC8264 and MPC8266 only)

- Each of the 8 TDM channels is routed in hardware to a TC layer block

- Protocol-specific overhead bits may be discarded or routed to other controllers by the SI

- Performing ATM TC layer functions (according to ITU-T I.432)

- Transmit (Tx) updates

- Cell HEC generation

- Payload scrambling using self synchronizing scrambler (programmable by the user)

- Coset generation (programmable by the user)

- Cell rate by inserting idle/unassigned cells

- Receive (Rx) updates

- Cell delineation using bit by bit HEC checking and programmable ALPHA and DELTA parameters for the delineation state machine

- Payload descrambling using self synchronizing scrambler (programmable by the user)

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

#### **Features**

- Coset removing (programmable by the user)

- Filtering idle/unassigned cells (programmable by the user)

- Performing HEC error detection and single bit error correction (programmable by user)

- Generating loss of cell delineation status/interrupt (LOC/LCD)

- Operates with FCC2 (UTOPIA 8)

- Provides serial loop back mode

- Cell echo mode is provided

- Supports both FCC transmit modes

- External rate mode—Idle cells are generated by the FCC (microcode) to control data rate.

- Internal rate mode (sub-rate)—FCC transfers only the data cells using the required data rate.

The TC layer generates idle/unassigned cells to maintain the line bit rate.

- Supports TC-layer and PMD-WIRE interface (according to the ATM-Forum af-phy-0063.000)

- Cell counters for performance monitoring

- 16-bit counters count

- HEC error cells

- HEC single bit error and corrected cells

- Idle/unassigned cells filtered

- Idle/unassigned cells transmitted

- Transmitted ATM cells

- Received ATM cells

- Maskable interrupt is sent to the host when a counter expires

- Overrun (Rx cell FIFO) and underrun (Tx cell FIFO) condition produces maskable interrupt

- May be operated at E1 and DS-1 rates. In addition, xDSL applications at bit rates up to 10 Mbps are supported

- PCI bridge (MPC8265 and MPC8266 only)

- PCI Specification Revision 2.2 compliant and supports frequencies up to 66 MHz

- On-chip arbitration

- Support for PCI to 60x memory and 60x memory to PCI streaming

- PCI Host Bridge or Peripheral capabilities

- Includes 4 DMA channels for the following transfers:

- PCI-to-60x to 60x-to-PCI

- 60x-to-PCI to PCI-to-60x

- PCI-to-60x to PCI-to-60x

- 60x-to-PCI to 60x-to-PCI

- Includes all of the configuration registers (which are automatically loaded from the EPROM and used to configure the MPC8265) required by the PCI standard as well as message and doorbell registers

- Supports the I<sub>2</sub>O standard

#### **Electrical and Thermal Characteristics**

Table 2 lists recommended operational voltage conditions.

Table 2. Recommended Operating Conditions<sup>1</sup>

| Rating                         | Symbol         | Value                  |                      |                       | Unit |

|--------------------------------|----------------|------------------------|----------------------|-----------------------|------|

| Core supply voltage            | VDD            | 1.7 – 1.9 <sup>2</sup> | 1.7–2.1 <sup>3</sup> | 1.9 –2.2 <sup>4</sup> | V    |

| PLL supply voltage             | VCCSYN         | 1.7 – 1.9 <sup>2</sup> | 1.7–2.1 <sup>3</sup> | 1.9–2.2 <sup>4</sup>  | V    |

| I/O supply voltage             | VDDH           | 3.135 – 3.465          |                      |                       | V    |

| Input voltage                  | VIN            | GND (-0.3) - 3.465     |                      |                       | V    |

| Junction temperature (maximum) | Tj             | 105 <sup>5</sup>       |                      |                       | °C   |

| Ambient temperature            | T <sub>A</sub> | 0–70 <sup>5</sup>      |                      |                       | °C   |

Caution: These are the recommended and tested operating conditions. Proper device operating outside of these conditions is not guaranteed.

### NOTE: Core, PLL, and I/O Supply Voltages

VDDH, VCCSYN, and VDD must track each other and both must vary in the same direction—in the positive direction (+5% and +0.1 Vdc) or in the negative direction (-5% and -0.1 Vdc).

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (either GND or V<sub>CC</sub>).

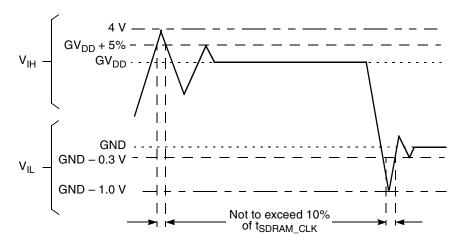

Figure 2 shows the undershoot and overshoot voltage of the 60x and local bus memory interface of the MPC8280. Note that in PCI mode the I/O interface is different.

Figure 2. Overshoot/Undershoot Voltage

<sup>&</sup>lt;sup>2</sup> CPU frequency less than or equal to 200 MHz.

<sup>&</sup>lt;sup>3</sup> CPU frequency greater than 200 MHz but less than 233 MHz.

<sup>&</sup>lt;sup>4</sup> CPU frequency greater than or equal to 233 MHz.

<sup>&</sup>lt;sup>5</sup> Note that for extended temperature parts the range is  $(-40)_{T_A}$  –  $105_{T_{\bar{1}}}$ .

# Table 3 shows DC electrical characteristics.

Table 3. DC Electrical Characteristics<sup>1</sup>

| Characteristic                                                                                                                                                                            | Symbol           | Min | Max   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage, all inputs except CLKIN                                                                                                                                               | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage                                                                                                                                                                         | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                                                  | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                                                   | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                                | I <sub>IN</sub>  | _   | 10    | μΑ   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                     | I <sub>OZ</sub>  | _   | 10    | μΑ   |

| Signal low input current, V <sub>IL</sub> = 0.8 V                                                                                                                                         | ΙL               | _   | 1     | μΑ   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                                                        | I <sub>H</sub>   | _   | 1     | μΑ   |

| Output high voltage, I <sub>OH</sub> = -2 mA<br>except XFC, UTOPIA mode, and open drain pins<br>In UTOPIA mode: I <sub>OH</sub> = -8.0 mA<br>PA[0-31]<br>PB[4-31]<br>PC[0-31]<br>PD[4-31] | V <sub>OH</sub>  | 2.4 | _     | V    |

| In UTOPIA mode: I <sub>OL</sub> = 8.0 mA<br>PA[0-31]<br>PB[4-31]<br>PC[0-31]<br>PD[4-31]                                                                                                  | V <sub>OL</sub>  | _   | 0.5   | V    |

#### **Electrical and Thermal Characteristics**

- <sup>2</sup> The leakage current is measured for nominal VDD, VCCSYN, and VDD.

- <sup>3</sup> MPC8265 and MPC8266 only.

## 2.2 Thermal Characteristics

Table 4 describes thermal characteristics.

Table 4. Thermal Characteristics for 480 TBGA Package

| Characteristics                | Symbol            | Value           | Unit | Air Flow        |

|--------------------------------|-------------------|-----------------|------|-----------------|

| Junction to ambient            |                   | 13 <sup>1</sup> |      | NC <sup>2</sup> |

|                                | $\theta_{\sf JA}$ | 10 <sup>1</sup> | °C/W | 1 m/s           |

|                                |                   | 11 <sup>3</sup> |      | NC              |

|                                |                   | 8 <sup>3</sup>  |      | 1 m/s           |

| Junction to board <sup>4</sup> | $\theta_{JB}$     | 4               | °C/W | _               |

| Junction to case <sup>5</sup>  | θ <sub>JC</sub>   | 1.1             | °C/W | _               |

Assumes a single layer board with no thermal vias

## 2.3 Power Considerations

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA}) \tag{1}$$

where

$T_A$  = ambient temperature °C

$\theta_{JA}$  = package thermal resistance, junction to ambient, °C/W

$$P_D = P_{INT} + P_{I/O}$$

$P_{INT} = I_{DD} \times V_{DD}$  Watts (chip internal power)

$P_{I/O}$  = power dissipation on input and output pins (determined by user)

For most applications  $P_{I/O} < 0.3$  x  $P_{INT}$ . If  $P_{I/O}$  is neglected, an approximate relationship between  $P_D$  and  $T_I$  is the following:

$$P_D = K/(T_I + 273^{\circ} C)$$

(2)

Solving equations (1) and (2) for K gives:

$$K = P_D x (T_A + 273^{\circ} C) + \theta_{JA} x P_D^2$$

(3)

<sup>&</sup>lt;sup>2</sup> Natural convection

<sup>&</sup>lt;sup>3</sup> Assumes a four layer board

Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $P_D$  and  $P_D$  can be obtained by solving equations (1) and (2) iteratively for any value of  $P_D$ .

# 2.3.1 Layout Practices

Each  $V_{CC}$  pin should be provided with a low-impedance path to the board's power supply. Each ground pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{CC}$  power supply should be bypassed to ground using at least four 0.1  $\mu F$  by-pass capacitors located as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{CC}$  and ground should be kept to less than half an inch per capacitor lead. A four-layer board is recommended, employing two inner layers as  $V_{CC}$  and GND planes.

All output pins on the MPC826xA have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize overdamped conditions and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{CC}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

Table 5 provides preliminary, estimated power dissipation for various configurations. Note that suitable thermal management is required for conditions above  $P_D = 3$  W (when the ambient temperature is 70 °C or greater) to ensure the junction temperature does not exceed the maximum specified value. Also note that the I/O power should be included when determining whether to use a heat sink.

|              |                   |                        |              |              |         | P <sub>INT</sub> | (W) <sup>2</sup> |          |

|--------------|-------------------|------------------------|--------------|--------------|---------|------------------|------------------|----------|

| Bus<br>(MHz) | CPM<br>Multiplier | Core CPU<br>Multiplier | CPM<br>(MHz) | CPU<br>(MHz) | Vddl 1  | .8 Volts         | VddI 2           | .0 Volts |

|              |                   |                        |              |              | Nominal | Maximum          | Nominal          | Maximum  |

| 66.66        | 2                 | 3                      | 133          | 200          | 1.2     | 2                | 1.8              | 2.3      |

| 66.66        | 2.5               | 3                      | 166          | 200          | 1.3     | 2.1              | 1.9              | 2.3      |

| 66.66        | 3                 | 4                      | 200          | 266          | _       | _                | 2.3              | 2.9      |

| 66.66        | 3                 | 4.5                    | 200          | 300          | _       | _                | 2.4              | 3.1      |

| 83.33        | 2                 | 3                      | 166          | 250          | _       | _                | 2.2              | 2.8      |

| 83.33        | 2                 | 3                      | 166          | 250          | _       | _                | 2.2              | 2.8      |

| 83.33        | 2.5               | 3.5                    | 208          | 291          | _       | _                | 2.4              | 3.1      |

Table 5. Estimated Power Dissipation for Various Configurations<sup>1</sup>

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

<sup>&</sup>lt;sup>1</sup> Test temperature = room temperature (25° C)

$<sup>^{2}</sup>$  P<sub>INT</sub> = I<sub>DD</sub> x V<sub>DD</sub> Watts

#### **Electrical and Thermal Characteristics**

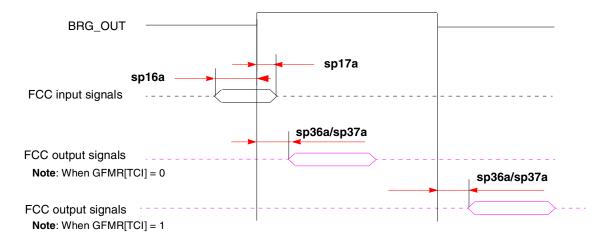

Figure 4 shows the FCC internal clock.

Figure 4. FCC Internal Clock Diagram

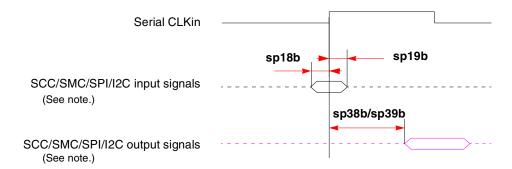

Figure 5 shows the SCC/SMC/SPI/I<sup>2</sup>C external clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 5. SCC/SMC/SPI/I<sup>2</sup>C External Clock Diagram

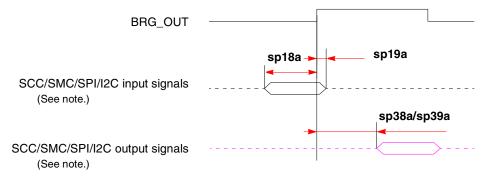

Figure 6 shows the SCC/SMC/SPI/I<sup>2</sup>C internal clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

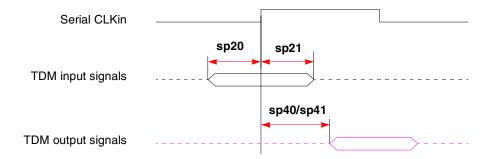

Figure 7 shows TDM input and output signals.

Note: There are four possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 7. TDM Signal Diagram

### **Electrical and Thermal Characteristics**

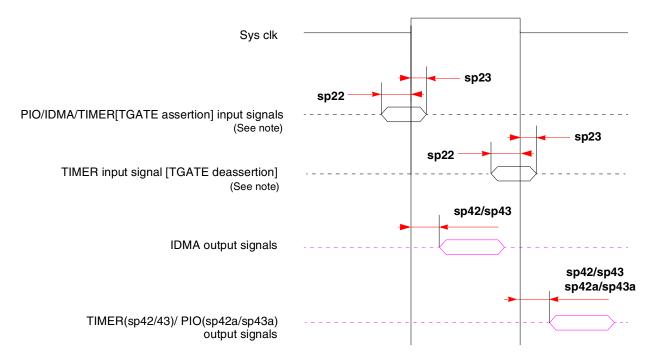

Figure 8 shows PIO, timer, and DMA signals.

Note: TGATE is asserted on the rising edge of the clock; it is deasserted on the falling edge.

Figure 8. PIO, Timer, and DMA Signal Diagram

Table 10 lists SIU input characteristics.

Table 9. AC Characteristics for SIU Inputs<sup>1</sup>

| Spec N | Number | Characteristic                   | Setu   | p (ns) | Hold (ns) |        |

|--------|--------|----------------------------------|--------|--------|-----------|--------|

| Max    | Min    | Characteristic                   | 66 MHz | 83 MHz | 66 MHz    | 83 MHz |

| sp11   | sp10   | AACK/ARTRY/TA/TS/TEA/DBG/BG/BR   | 6      | 5      | 0.5       | 0.5    |

| sp12   | sp10   | Data bus in normal mode          | 5      | 4      | 0.5       | 0.5    |

| sp13   | sp10   | Data bus in ECC and PARITY modes | 8      | 6      | 0.5       | 0.5    |

| sp14   | sp10   | DP pins                          | 7      | 6      | 0.5       | 0.5    |

| sp15   | sp10   | All other pins                   | 5      | 4      | 0.5       | 0.5    |

Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

### **Clock Configuration Modes**

Table 18. Clock Default Configurations in PCI Agent Mode (MODCK\_HI = 0000) (continued)

| MODCK[1-3] <sup>1</sup> | Input Clock<br>Frequency<br>(PCI) <sup>2</sup> | Multiplication | CPM<br>Frequency | Core<br>Multiplication<br>Factor | Core<br>Frequency <sup>3</sup> | Bus Division<br>Factor | 60x Bus<br>Frequency <sup>4</sup> |

|-------------------------|------------------------------------------------|----------------|------------------|----------------------------------|--------------------------------|------------------------|-----------------------------------|

| 100                     | 66/33 MHz                                      | 3/6            | 200 MHz          | 3                                | 240 MHz                        | 2.5                    | 80 MHz                            |

| 101                     | 66/33 MHz                                      | 3/6            | 200 MHz          | 3.5                              | 280 MHz                        | 2.5                    | 80 MHz                            |

| 110                     | 66/33 MHz                                      | 4/8            | 266 MHz          | 3.5                              | 300 MHz                        | 3                      | 88 MHz                            |

| 111                     | 66/33 MHz                                      | 4/8            | 266 MHz          | 3                                | 300 MHz                        | 2.5                    | 100 MHz                           |

<sup>1</sup> Assumes MODCK\_HI = 0000.

Table 19 describes all possible clock configurations when using the MPC8265 or the MPC8266's internal PCI bridge in agent mode.

Table 19. Clock Configuration Modes in PCI Agent Mode

| MODCK_H -<br>MODCK[1-3] | Input Clock<br>Frequency<br>(PCI) <sup>1,2</sup> | CPM<br>Multiplication<br>Factor <sup>1</sup> | CPM<br>Frequency | Core<br>Multiplication<br>Factor | Core<br>Frequency <sup>3</sup> | Bus Division<br>Factor | 60x Bus<br>Frequency <sup>4</sup> |

|-------------------------|--------------------------------------------------|----------------------------------------------|------------------|----------------------------------|--------------------------------|------------------------|-----------------------------------|

| 0001_001                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 5                                | 166 MHz                        | 4                      | 33 MHz                            |

| 0001_010                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 6                                | 200 MHz                        | 4                      | 33 MHz                            |

| 0001_011                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 7                                | 233 MHz                        | 4                      | 33 MHz                            |

| 0001_100                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 8                                | 266 MHz                        | 4                      | 33 MHz                            |

|                         |                                                  |                                              |                  |                                  |                                |                        |                                   |

| 0010_001                | 50/25 MHz                                        | 3/6                                          | 150 MHz          | 3                                | 180 MHz                        | 2.5                    | 60 MHz                            |

| 0010_010                | 50/25 MHz                                        | 3/6                                          | 150 MHz          | 3.5                              | 210 MHz                        | 2.5                    | 60 MHz                            |

| 0010_011                | 50/25 MHz                                        | 3/6                                          | 150 MHz          | 4                                | 240 MHz                        | 2.5                    | 60 MHz                            |

| 0010_100                | 50/25 MHz                                        | 3/6                                          | 150 MHz          | 4.5                              | 270 MHz                        | 2.5                    | 60 MHz                            |

|                         |                                                  |                                              |                  |                                  |                                |                        |                                   |

| 0011_000                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 2.5                              | 110MHz                         | 3                      | 44 MHz                            |

| 0011_001                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 3                                | 132 MHz                        | 3                      | 44 MHz                            |

| 0011_010                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 3.5                              | 154 MHz                        | 3                      | 44 MHz                            |

| 0011_011                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 4                                | 176MHz                         | 3                      | 44 MHz                            |

| 0011_100                | 66/33 MHz                                        | 2/4                                          | 133 MHz          | 4.5                              | 198 MHz                        | 3                      | 44 MHz                            |

|                         |                                                  |                                              |                  |                                  |                                |                        |                                   |

| 0100_000                | 66/33 MHz                                        | 3/6                                          | 200 MHz          | 2.5                              | 166 MHz                        | 3                      | 66 MHz                            |

| 0100_001                | 66/33 MHz                                        | 3/6                                          | 200 MHz          | 3                                | 200 MHz                        | 3                      | 66 MHz                            |

| 0100_010                | 66/33 MHz                                        | 3/6                                          | 200 MHz          | 3.5                              | 233 MHz                        | 3                      | 66 MHz                            |

| 0100_011                | 66/33 MHz                                        | 3/6                                          | 200 MHz          | 4                                | 266 MHz                        | 3                      | 66 MHz                            |

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

<sup>&</sup>lt;sup>2</sup> The frequency depends on the value of PCI\_MODCK. If PCI\_MODCK is high (logic '1'), the PCI frequency is divided by 2 (33 instead of 66 MHz, etc.) and the CPM multiplication factor is multiplied by 2. Refer to Table 15.

<sup>&</sup>lt;sup>3</sup> Core frequency = (60x bus frequency)(core multiplication factor)

<sup>&</sup>lt;sup>4</sup> Bus frequency = CPM frequency/bus division factor

### **Clock Configuration Modes**

Table 19. Clock Configuration Modes in PCI Agent Mode (continued)

| MODCK_H -<br>MODCK[1-3] | Input Clock<br>Frequency<br>(PCI) <sup>1,2</sup> | CPM<br>Multiplication<br>Factor <sup>1</sup> | CPM<br>Frequency | Core<br>Multiplication<br>Factor | Core<br>Frequency <sup>3</sup> | Bus Division<br>Factor | 60x Bus<br>Frequency <sup>4</sup> |

|-------------------------|--------------------------------------------------|----------------------------------------------|------------------|----------------------------------|--------------------------------|------------------------|-----------------------------------|

| 1010_001                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3                                | 266 MHz                        | 3                      | 88 MHz                            |

| 1010_010                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3.5                              | 300 MHz                        | 3                      | 88 MHz                            |

| 1010_011                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 4                                | 350 MHz                        | 3                      | 88 MHz                            |

| 1010_100                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 4.5                              | 400 MHz                        | 3                      | 88 MHz                            |

|                         |                                                  |                                              |                  |                                  |                                |                        |                                   |

| 1011_000                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 2                                | 212MHz                         | 2.5                    | 106 MHz                           |

| 1011_001                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 2.5                              | 265 MHz                        | 2.5                    | 106 MHz                           |

| 1011_010                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3                                | 318 MHz                        | 2.5                    | 106 MHz                           |

| 1011_011                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 3.5                              | 371 MHz                        | 2.5                    | 106 MHz                           |

| 1011_100                | 66/33 MHz                                        | 4/8                                          | 266 MHz          | 4                                | 424 MHz                        | 2.5                    | 106 MHz                           |

The frequency depends on the value of PCI\_MODCK. If PCI\_MODCK is high (logic '1'), the PCI frequency is divided by 2 (33 instead of 66 MHz, etc.) and the CPM multiplication factor is multiplied by 2. Refer to Table 15.

<sup>&</sup>lt;sup>2</sup> Input clock frequency is given only for the purpose of reference. User should set MODCK\_H-MODCK\_L so that the resulting configuration does not exceed the frequency rating of the user's part.

<sup>&</sup>lt;sup>3</sup> Core frequency = (60x bus frequency)(core multiplication factor)

<sup>&</sup>lt;sup>4</sup> Bus frequency = CPM frequency/bus division factor

<sup>&</sup>lt;sup>5</sup> In this mode, PCI\_MODCK must be "1".

# 4 Pinout

This section provides the pin assignments and pinout list for the MPC826xA.

# 4.1 Pin Assignments

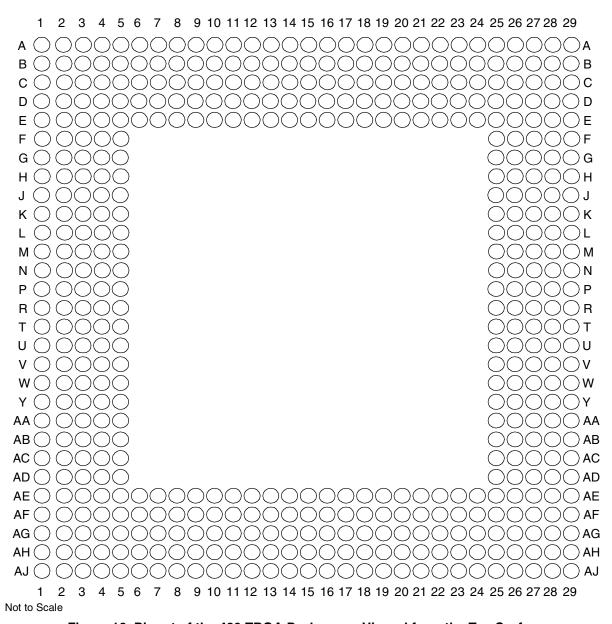

Figure 13 shows the pinout of the MPC826xA's 480 TBGA package as viewed from the top surface.

Figure 13. Pinout of the 480 TBGA Package as Viewed from the Top Surface

### **Pinout**

Table 21. Pinout List (continued)

| Pin Name                     | Ball |

|------------------------------|------|

| IRQ3/DP3/CKSTP_OUT/EXT_BR3   | D21  |

| IRQ4/DP4/CORE_SRESET/EXT_BG3 | C21  |

| IRQ5/DP5/TBEN/EXT_DBG3       | B21  |

| ĪRQ6/DP6/CSE0                | A21  |

| IRQ7/DP7/CSE1                | E20  |

| PSDVAL                       | V3   |

| TA                           | C22  |

| TEA                          | V5   |

| GBL/IRQ1                     | W1   |

| CI/BADDR29/IRQ2              | U2   |

| WT/BADDR30/IRQ3              | U3   |

| L2_HIT/IRQ4                  | Y4   |

| CPU_BG/BADDR31/IRQ5          | U4   |

| CPU_DBG                      | R2   |

| CPU_BR                       | Y3   |

| CS0                          | F25  |

| CS1                          | C29  |

| CS2                          | E27  |

| CS3                          | E28  |

| CS4                          | F26  |

| CS5                          | F27  |

| CS6                          | F28  |

| CS7                          | G25  |

| CS8                          | D29  |

| CS9                          | E29  |

| CS10/BCTL1                   | F29  |

| CS11/AP0                     | G28  |

| BADDR27                      | T5   |

| BADDR28                      | U1   |

| ALE                          | T2   |

| BCTL0                        | A27  |

| PWE0/PSDDQM0/PBS0            | C25  |

| PWE1/PSDDQM1/PBS1            | E24  |

| PWE2/PSDDQM2/PBS2            | D24  |

| PWE3/PSDDQM3/PBS3            | C24  |

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

Table 21. Pinout List (continued)

| Pin Name                                     | Ball |

|----------------------------------------------|------|

| PWE4/PSDDQM4/PBS4                            | B26  |

| PWE5/PSDDQM5/PBS5                            | A26  |

| PWE6/PSDDQM6/PBS6                            | B25  |

| PWE7/PSDDQM7/PBS7                            | A25  |

| PSDA10/PGPL0                                 | E23  |

| PSDWE/PGPL1                                  | B24  |

| POE/PSDRAS/PGPL2                             | A24  |

| PSDCAS/PGPL3                                 | B23  |

| PGTA/PUPMWAIT/PGPL4/PPBS                     | A23  |

| PSDAMUX/PGPL5                                | D22  |

| LWE0/LSDDQM0/LBS0/PCI_CFG0 <sup>1</sup>      | H28  |

| LWE1/LSDDQM1/LBS1/PCI_CFG1 <sup>1</sup>      | H27  |

| LWE2/LSDDQM2/LBS2/PCI_CFG2 <sup>1</sup>      | H26  |

| LWE3/LSDDQM3/LBS3/PCI_CFG3 <sup>1</sup>      | G29  |

| LSDA10/LGPL0/PCI_MODCKH0 <sup>1</sup>        | D27  |

| LSDWE/LGPL1/PCI_MODCKH1 <sup>1</sup>         | C28  |

| LOE/LSDRAS/LGPL2/PCI_MODCKH2 <sup>1</sup>    | E26  |

| LSDCAS/LGPL3/PCI_MODCKH3 <sup>1</sup>        | D25  |

| LGTA/LUPMWAIT/LGPL4/LPBS                     | C26  |

| LGPL5/LSDAMUX/PCI_MODCK <sup>1</sup>         | B27  |

| LWR                                          | D28  |

| L_A14/PAR <sup>1</sup>                       | N27  |

| L_A15/FRAME <sup>1</sup> /SMI                | T29  |

| L_A16/TRDY <sup>1</sup>                      | R27  |

| L_A17/IRDY <sup>1</sup> /CKSTP_OUT           | R26  |

| L_A18/STOP1                                  | R29  |

| L_A19/DEVSEL <sup>1</sup>                    | R28  |

| L_A20/IDSEL <sup>1</sup>                     | W29  |

| L_A21/PERR <sup>1</sup>                      | P28  |

| L_A22/SERR <sup>1</sup>                      | N26  |

| L_A23/REQ0 <sup>1</sup>                      | AA27 |

| L_A24/REQ1 <sup>1</sup> /HSEJSW <sup>1</sup> | P29  |

| L_A25/GNT0 <sup>1</sup>                      | AA26 |

| L_A26/GNT1 <sup>1</sup> /HSLED <sup>1</sup>  | N25  |

| L_A27/GNT2 <sup>1</sup> /HSENUM <sup>1</sup> | AA25 |

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

Table 21. Pinout List (continued)

| Pin Name                                                   | Ball              |

|------------------------------------------------------------|-------------------|

| PA12/FCC1_UT8_RXD2/FCC1_UT16_RXD10/MSNUM3                  | AJ21 <sup>2</sup> |

| PA13/FCC1_UT8_RXD3/FCC1_UT16_RXD11/MSNUM2                  | AH20 <sup>2</sup> |

| PA14/FCC1_UT8_RXD4/FCC1_UT16_RXD12/FCC1_RXD3               | AG19 <sup>2</sup> |

| PA15/FCC1_UT8_RXD5/FCC1_UT16_RXD13/FCC1_RXD2               | AF18 <sup>2</sup> |

| PA16/FCC1_UT8_RXD6/FCC1_UT16_RXD14/FCC1_RXD1               | AF17 <sup>2</sup> |

| PA17/FCC1_UT8_RXD7/FCC1_UT16_RXD15/FCC1_RXD0/FCC1_RXD      | AE16 <sup>2</sup> |

| PA18/FCC1_UT8_TXD7/FCC1_UT16_TXD15/FCC1_TXD0/FCC1_TXD      | AJ16 <sup>2</sup> |

| PA19/FCC1_UT8_TXD6/FCC1_UT16_TXD14/FCC1_TXD1               | AG15 <sup>2</sup> |

| PA20/FCC1_UT8_TXD5/FCC1_UT16_TXD13/FCC1_TXD2               | AJ13 <sup>2</sup> |

| PA21/FCC1_UT8_TXD4/FCC1_UT16_TXD12/FCC1_TXD3               | AE13 <sup>2</sup> |

| PA22/FCC1_UT8_TXD3/FCC1_UT16_TXD11                         | AF12 <sup>2</sup> |

| PA23/FCC1_UT8_TXD2/FCC1_UT16_TXD10                         | AG11 <sup>2</sup> |

| PA24/FCC1_UT8_TXD1/FCC1_UT16_TXD9/MSNUM1                   | AH9 <sup>2</sup>  |

| PA25/FCC1_UT8_TXD0/FCC1_UT16_TXD8/MSNUM0                   | AJ8 <sup>2</sup>  |

| PA26/FCC1_UTM_RXCLAV/FCC1_UTS_RXCLAV/FCC1_MII_RX_ER        | AH7 <sup>2</sup>  |

| PA27/FCC1_UT_RXSOC/FCC1_MII_RX_DV                          | AF7 <sup>2</sup>  |

| PA28/FCC1_UTM_RXENB/FCC1_UTS_RXENB/FCC1_MII_TX_EN          | AD5 <sup>2</sup>  |

| PA29/FCC1_UT_TXSOC/FCC1_MII_TX_ER                          | AF1 <sup>2</sup>  |

| PA30/FCC1_UTM_TXCLAV/FCC1_UTS_TXCLAV/FCC1_MII_CRS/FCC1_RTS | AD3 <sup>2</sup>  |

| PA31/FCC1_UTM_TXENB/FCC1_UTS_TXENB/FCC1_MII_COL            | AB5 <sup>2</sup>  |

| PB4/FCC3_TXD3/FCC2_UT8_RXD0/L1RSYNCA2/FCC3_RTS             | AD28 <sup>2</sup> |

| PB5/FCC3_TXD2/FCC2_UT8_RXD1/L1TSYNCA2/L1GNTA2              | AD26 <sup>2</sup> |

| PB6/FCC3_TXD1/FCC2_UT8_RXD2/L1RXDA2/L1RXD0A2               | AD25 <sup>2</sup> |

| PB7/FCC3_TXD0/FCC3_TXD/FCC2_UT8_RXD3/L1TXDA2/L1TXD0A2      | AE26 <sup>2</sup> |

| PB8/FCC2_UT8_TXD3/FCC3_RXD0/FCC3_RXD/TXD3/L1RSYNCD1        | AH27 <sup>2</sup> |

| PB9/FCC2_UT8_TXD2/FCC3_RXD1/L1TXD2A2/L1TSYNCD1/L1GNTD1     | AG24 <sup>2</sup> |

| PB10/FCC2_UT8_TXD1/FCC3_RXD2/L1RXDD1                       | AH24 <sup>2</sup> |

| PB11/FCC3_RXD3/FCC2_UT8_TXD0/L1TXDD1                       | AJ24 <sup>2</sup> |

| PB12/FCC3_MII_CRS/L1CLKOB1/L1RSYNCC1/TXD2                  | AG22 <sup>2</sup> |

| PB13/FCC3_MII_COL/L1RQB1/L1TSYNCC1/L1GNTC1/L1TXD1A2        | AH21 <sup>2</sup> |

| PB14/FCC3_MII_TX_EN/RXD3/L1RXDC1                           | AG20 <sup>2</sup> |

| PB15/FCC3_MII_TX_ER/RXD2/L1TXDC1                           | AF19 <sup>2</sup> |

| PB16/FCC3_MII_RX_ER/L1CLKOA1/CLK18                         | AJ18 <sup>2</sup> |

| PB17/FCC3_MII_RX_DV/L1RQA1/CLK17                           | AJ17 <sup>2</sup> |

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

Table 21. Pinout List (continued)

| Pin Name                                                                            | Ball                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD21/TXD4/FCC1_UT16_RXD3/L1RXD0A2/L1RXDA2                                           | AH13 <sup>2</sup>                                                                                                                                                                                                                        |

| PD22/RXD4/FCC1_UT16_TXD5/L1TXD0A2/L1TXDA2                                           | AJ12 <sup>2</sup>                                                                                                                                                                                                                        |

| PD23/RTS3/TENA3/FCC1_UT16_RXD4/L1RSYNCD1                                            | AE12 <sup>2</sup>                                                                                                                                                                                                                        |

| PD24/TXD3/FCC1_UT16_RXD5/L1RXDD1                                                    | AF10 <sup>2</sup>                                                                                                                                                                                                                        |

| PD25/RXD3/FCC1_UT16_TXD6/L1TXDD1                                                    | AG9 <sup>2</sup>                                                                                                                                                                                                                         |

| PD26/RTS2/TENA2/FCC1_UT16_RXD6/L1RSYNCC1                                            | AH8 <sup>2</sup>                                                                                                                                                                                                                         |

| PD27/TXD2/FCC1_UT16_RXD7/L1RXDC1                                                    | AG7 <sup>2</sup>                                                                                                                                                                                                                         |

| PD28/RXD2/FCC1_UT16_TXD7/L1TXDC1                                                    | AE4 <sup>2</sup>                                                                                                                                                                                                                         |

| PD29/RTS1/TENA1/FCC1_UTM_RXADDR3/FCC1_UTS_RXADDR3/FCC1_UTM_RXCLAV2/FCC2_UTM_RXADDR4 | AG1 <sup>2</sup>                                                                                                                                                                                                                         |

| PD30/FCC2_UTM_TXENB/FCC2_UTS_TXENB/TXD1                                             | AD4 <sup>2</sup>                                                                                                                                                                                                                         |

| PD31/RXD1                                                                           | AD2 <sup>2</sup>                                                                                                                                                                                                                         |

| VCCSYN                                                                              | AB3                                                                                                                                                                                                                                      |

| VCCSYN1                                                                             | B9                                                                                                                                                                                                                                       |

| GNDSYN                                                                              | AB1                                                                                                                                                                                                                                      |

| CLKIN2 <sup>1,3</sup>                                                               | AE11                                                                                                                                                                                                                                     |

| SPARE4 <sup>4</sup>                                                                 | U5                                                                                                                                                                                                                                       |

| PCI_MODE <sup>1,5</sup>                                                             | AF25                                                                                                                                                                                                                                     |

| SPARE6 <sup>4</sup>                                                                 | V4                                                                                                                                                                                                                                       |

| THERMAL0 <sup>6</sup>                                                               | AA1                                                                                                                                                                                                                                      |

| THERMAL1 <sup>6</sup>                                                               | AG4                                                                                                                                                                                                                                      |

| I/O power                                                                           | AG21, AG14, AG8, AJ1, AJ2, AH1, AH2, AG3, AF4, AE5, AC27, Y27, T27, P27, K26, G27, AE25, AF26, AG27, AH28, AH29, AJ28, AJ29, C7, C14, C16, C20, C23, E10, A28, A29, B28, B29, C27, D26, E25, H3, M4, T3, AA4, A1, A2, B1, B2, C3, D4, E5 |

| Core Power                                                                          | U28, U29, K28, K29, A9, A19, B19, M1, M2, Y1, Y2, AC1, AC2, AH19, AJ19, AH10, AJ10, AJ5                                                                                                                                                  |

| Ground                                                                              | AA5, AF21, AF14, AF8, AE7, AF11,<br>AE17, AE23, AC26, AB25, Y26, V25,<br>T26, R25, P26, M25, K27, H25, G26,<br>D7, D10, D14, D16, D20, D23, C9, E11,<br>E13, E15, E19, E22, B3, G5, H4, K5,<br>M3, P5, T4, Y5, AA2, AC3                  |

<sup>&</sup>lt;sup>1</sup> MPC8265 and MPC8266 only.

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

<sup>&</sup>lt;sup>2</sup> The default configuration of the CPM pins (PA[0–31], PB[4–31], PC[0–31], PD[4–31]) is input. To prevent excessive DC current, it is recommended to either pull unused pins to GND or VDDH, or to configure them as outputs.

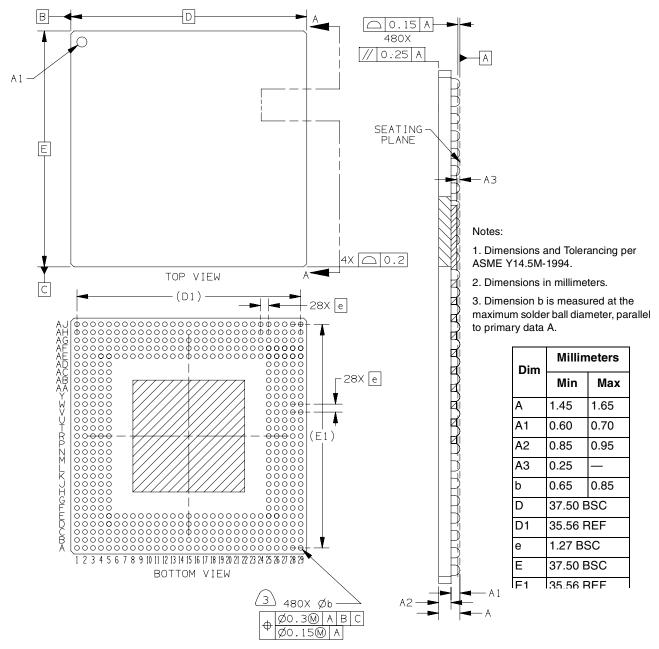

# 5.2 Mechanical Dimensions

Figure 15 provides the mechanical dimensions and bottom surface nomenclature of the 480 TBGA package.

Figure 15. Mechanical Dimensions and Bottom Surface Nomenclature

**Ordering Information**

# 6 Ordering Information

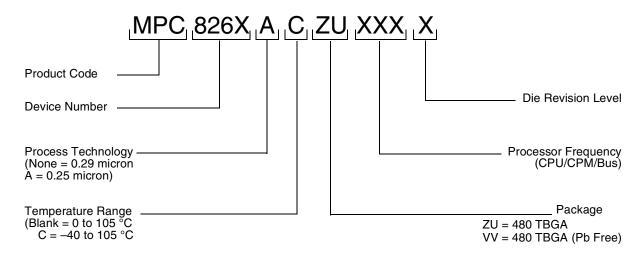

Figure 16 provides an example of the Freescale part numbering nomenclature for the MPC826xA. In addition to the processor frequency, the part numbering scheme also consists of a part modifier that indicates any enhancement(s) in the part from the original production design. Each part number also contains a revision code that refers to the die mask revision number and is specified in the part numbering scheme for identification purposes only. For more information, contact your local Freescale sales office.

Figure 16. Freescale Part Number Key

# 7 Document Revision History

Table 23 lists significant changes in each revision of this document.

**Table 23. Document Revision History**

| Revision | Date    | Substantive Changes                  |

|----------|---------|--------------------------------------|

| 2        | 06/2009 | Updated package values in Figure 16. |

| 1.1      | 02/2006 | Addition of Table 12.                |

| 1.0      | 9/2005  | Document template update             |

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0

# **Table 23. Document Revision History (continued)**

| Revision | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.9      | 8/2003  | <ul> <li>Note: In revision 0.3, sp30 (Table 10) was changed. This change was not previously recorded in this "Document Revision History" Table.</li> <li>Removal of "HiP4 PowerQUICC II Documentation" table. These supplemental specifications have been replaced by revision 1 of the MPC8260 PowerQUICC II™ Family Reference Manual.</li> <li>Figure 1 and Section 1, "Features": Addition of MPC8255 notes</li> <li>Addition of Figure 2</li> <li>Addition of VCCSYN to "Note: Core, PLL, and I/O Supply Voltages" following Table 2</li> <li>Addition of note 1 to Table 3</li> <li>Table 4: Changes to θ<sub>JA</sub> and θ<sub>JB</sub> and θ<sub>JC</sub>.</li> <li>Addition of notes or modifications to Figure 6, Figure 7, and Figure 8</li> <li>Table 9: Change of sp10.</li> <li>Addition of Table 15.</li> <li>Addition of note 2 to Table 21</li> <li>Table 21: Addition of FCC2 Rx and Tx [3,4] to CPM pins PD7, PD18, PD19, and PD29. Also, the addition of SPICLK to PC19. They are documented correctly in the parallel I/O ports chapter in the MPC8260 PowerQUICC II™ Family Reference Manual but had previously been omitted from Table 21.</li> </ul> |

| 0.8      | 1/2003  | <ul> <li>Table 2: Modification to supply voltage ranges reflected in notes 2, 3, and 4.</li> <li>Table 4: Addition of θ<sub>JB</sub> and θ<sub>JC</sub>.</li> <li>Table 7, Figure 8: Addition of sp42a/sp43a.</li> <li>Figure 3, Figure 4: Addition of note for FCC output.</li> <li>Figure 5, Figure 6, Figure 7: Addition of notes.</li> <li>Table 14, Table 17, and Table 19: Removal of PLL bypass mode from clock tables.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.7      | 5/2002  | <ul> <li>Section 1, "Features": minimum supported core frequency of 150 MHz</li> <li>Section 1, "Features": updated performance values (under "Dual-issue integer core")</li> <li>Table 2: Note 2 (changes in italics): "less than or equal to 233 MHz, 166 MHz CPM"</li> <li>Table 2: Addition of note 3.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0.6      | 3/2002  | Table 21: Modified notes to pins AE11 and AF25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0.5      | 3/2002  | <ul> <li>Table 21: Modified notes to pins AE11 and AF25.</li> <li>Table 21: Addition of note to pins AA1 and AG4 (Therm0 and Therm1).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0.4      | 2/2002  | <ul> <li>Note 2 for Table 2 (changes in italics): "greater than or equal to 266 MHz, 200 MHz CPM"</li> <li>Table 19: Core and bus frequency values for the following ranges of MODCK_HMODCK: 0011_000 to 0011_100 and 1011_000 to 1011_1000</li> <li>Table 21: Notes added to pins at AE11, AF25, U5, and V4.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0.3      | 11/2001 | <ul> <li>Table 1: note 3</li> <li>Section 2.1: Removal of "Warning" recommending use of bootstrap diodes. They are not needed.</li> <li>Table 9: Change to sp12.</li> <li>Table 10: Change to sp32.</li> <li>Note 2 for Table 16 and Table 17</li> <li>Addition of note at beginning of Section 3.2</li> <li>Note 1 for Table 18 and Table 19</li> <li>Table 21: Additions to B27, C28, D25, D27, E26, G29, H26–28, N25, P29, AF25, AA25, AB27</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.2      | 11/2001 | <ul> <li>Revision of Table 5, "Power Dissipation"</li> <li>Modifications to Figure 9, Table 2, Table 10, Table 11, and Table 18</li> <li>Modification to pinout diagram, Figure 13</li> <li>Additional revisions to text and figures throughout</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0.1      | 8/2001  | Table 8: Change to sp20/sp21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0        | _       | Initial version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

MPC8260A PowerQUICC™ II Integrated Communications Processor Hardware Specifications, Rev. 2.0