Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 20MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 84                                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 16K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                          |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3738gc-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address   | Function Register Name                       | Symbol               | R/W | Manip        | oulatabl     | le Bits      | Default Value |

|-----------|----------------------------------------------|----------------------|-----|--------------|--------------|--------------|---------------|

|           |                                              |                      |     | 1            | 8            | 16           |               |

| FFFFF712H | Port 9 function control expansion register   | PFCE9                | R/W |              |              | $\checkmark$ | 0000H         |

| FFFFF712H | Port 9 function control expansion register L | PFCE9L               |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF713H | Port 9 function control expansion register H | PFCE9H               |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF802H | System status register                       | SYS                  |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF80CH | Internal oscillation mode register           | RCM                  |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF810H | DMA trigger factor register 0                | DTFR0                |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF812H | DMA trigger factor register 1                | DTFR1                |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF814H | DMA trigger factor register 2                | DTFR2                |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF816H | DMA trigger factor register 3                | DTFR3                |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF820H | Power save mode register                     | PSMR                 |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF822H | Clock control register                       | СКС                  |     | $\checkmark$ | $\checkmark$ |              | 0AH           |

| FFFFF824H | Lock register                                | LOCKR                | R   | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF828H | Processor clock control register             | PCC <sup>Note</sup>  | R/W | $\checkmark$ | $\checkmark$ |              | 03H           |

| FFFFF82CH | PLL control register                         | PLLCTL               |     | $\checkmark$ | $\checkmark$ |              | 01H           |

| FFFFF82EH | CPU operation clock status register          | CCLS                 | R   | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF870H | Clock monitor mode register                  | CLM                  | R/W | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF888H | Reset source flag register                   | RESF                 |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF890H | Low-voltage detection register               | LVIM                 |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF891H | Low-voltage detection level select register  | LVIS                 |     |              | $\checkmark$ |              | 00H           |

| FFFFF8B0H | Prescaler mode register 0                    | PRSM0                |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFF8B1H | Prescaler compare register 0                 | PRSCM0               |     |              | $\checkmark$ |              | 00H           |

| FFFF9FCH  | On-chip debug mode register                  | OCDM <sup>Note</sup> |     | $\checkmark$ | $\checkmark$ |              | 01H           |

| FFFFFA00H | UARTA0 control register 0                    | UA0CTL0              |     | $\checkmark$ | $\checkmark$ |              | 10H           |

| FFFFFA01H | UARTA0 control register 1                    | UA0CTL1              |     |              | $\checkmark$ |              | 00H           |

| FFFFFA02H | UARTA0 control register 2                    | UA0CTL2              |     |              | $\checkmark$ |              | FFH           |

| FFFFFA03H | UARTA0 option control register 0             | UA0OPT0              |     | $\checkmark$ | $\checkmark$ |              | 14H           |

| FFFFFA04H | UARTA0 status register                       | UA0STR               |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFFA06H | UARTA0 receive data register                 | UA0RX                | R   |              | $\checkmark$ |              | FFH           |

| FFFFFA07H | UARTA0 transmit data register                | UA0TX                | R/W |              | $\checkmark$ |              | FFH           |

| FFFFFA10H | UARTA1 control register 0                    | UA1CTL0              |     | $\checkmark$ | $\checkmark$ |              | 10H           |

| FFFFFA11H | UARTA1 control register 1                    | UA1CTL1              |     |              | $\checkmark$ |              | 00H           |

| FFFFFA12H | UARTA1 control register 2                    | UA1CTL2              |     |              | $\checkmark$ |              | FFH           |

| FFFFFA13H | UARTA1 option control register 0             | UA1OPT0              |     | $\checkmark$ | $\checkmark$ |              | 14H           |

| FFFFFA14H | UARTA1 status register                       | UA1STR               |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFFA16H | UARTA1 receive data register                 | UA1RX                | R   |              | $\checkmark$ |              | FFH           |

| FFFFFA17H | UARTA1 transmit data register                | UA1TX                | R/W |              | $\checkmark$ |              | FFH           |

| FFFFFA20H | UARTA2 control register 0                    | UA2CTL0              |     | $\checkmark$ | $\checkmark$ |              | 10H           |

| FFFFFA21H | UARTA2 control register 1                    | UA2CTL1              |     |              | $\checkmark$ |              | 00H           |

| FFFFFA22H | UARTA2 control register 2                    | UA2CTL2              |     |              | $\checkmark$ |              | FFH           |

| FFFFFA23H | UARTA2 option control register 0             | UA2OPT0              |     | $\checkmark$ | $\checkmark$ |              | 14H           |

| FFFFFA24H | UARTA2 status register                       | UA2STR               |     | $\checkmark$ | $\checkmark$ |              | 00H           |

| FFFFFA26H | UARTA2 receive data register                 | UA2RX                | R   |              | $\checkmark$ |              | FFH           |

| FFFFFA27H | UARTA2 transmit data register                | UA2TX                | R/W |              |              |              | FFH           |

Note This is a special register.

# (2) Port 0 mode register (PM0)

| After res | et: FFH | R/W       | Address: F                       | FFFF420H | 4    |      |   |   |

|-----------|---------|-----------|----------------------------------|----------|------|------|---|---|

|           | 7       | 6         | 5                                | 4        | 3    | 2    | 1 | 0 |

| PM0       | 1       | PM06      | PM05                             | PM04     | PM03 | PM02 | 1 | 1 |

|           |         |           |                                  |          |      |      |   |   |

|           | PM0n    |           | I/O mode control ( $n = 2$ to 6) |          |      |      |   |   |

|           | 0       | Output mo | utput mode                       |          |      |      |   |   |

|           | 1       | Input mod | e                                |          |      |      |   |   |

|           | 1       | · ·       |                                  |          |      |      |   |   |

# <R> (3) Port 0 mode control register (PMC0)

|      | 7     | 6           | 5                              | 4                   | 3           | 2                    | 1 | 0 |

|------|-------|-------------|--------------------------------|---------------------|-------------|----------------------|---|---|

| PMC0 | 0     | PMC06       | PMC05                          | PMC04               | PMC03       | PMC02                | 0 | 0 |

|      |       |             |                                |                     |             |                      |   | · |

|      | PMC06 |             |                                | Specifica           | tion of pin | operation            |   |   |

|      | 0     | I/O port (p | 06)                            |                     |             |                      |   |   |

|      | 1     | INTP3 inp   | ut                             |                     |             |                      |   |   |

|      | PMC05 |             | Specification of pin operation |                     |             |                      |   |   |

|      | 0     | I/O port (p | port (p05)                     |                     |             |                      |   |   |

|      | 1     | INTP2 inp   | TP2 input                      |                     |             |                      |   |   |

|      | PMC04 |             |                                | Specifica           | tion of pin | operation            |   |   |

|      | 0     | I/O port (p | 04)                            |                     |             |                      |   |   |

|      | 1     | INTP1 inp   | out (/RTCD                     | IV output/F         | RTCCL outp  | out) <sup>Note</sup> |   |   |

|      | PMC03 |             |                                | Specifica           | tion of pin | operation            |   |   |

|      | 0     | I/O port (p | 03)                            |                     |             |                      |   |   |

|      | 1     | INTP0 inp   | ut/ADTRG                       | input (/RT          | C1HZ outp   | ut) <sup>Note</sup>  |   |   |

|      | PMC02 |             |                                | Specifica           | tion of pin | operation            |   |   |

|      | 0     | I/O port (p | 02)                            |                     |             |                      |   |   |

|      | 1     | NMI input   | (/A21 outp                     | ut) <sup>Note</sup> |             |                      |   |   |

Caution The P05/INTP2/DRST pin becomes the DRST pin regardless of the value of the PMC05 bit when the OCDM.OCDM0 bit is 1.

# 4.3.6 Port 7

Port 7 is a 12-bit port for which I/O settings can be controlled in 1-bit units. Port 7 includes the following alternate-function pins.

|     | Pin No. |    | Function | Alternate Fu | inction | Remark | Block Type |

|-----|---------|----|----------|--------------|---------|--------|------------|

| GF  | GC      | F1 | Name     | Name         | I/O     |        |            |

| 2   | 100     | A3 | P70      | ANIO         | Input   | -      | A-1        |

| 1   | 99      | B3 | P71      | ANI1         | Input   |        | A-1        |

| 100 | 98      | C3 | P72      | ANI2         | Input   |        | A-1        |

| 99  | 97      | D3 | P73      | ANI3         | Input   |        | A-1        |

| 98  | 96      | A4 | P74      | ANI4         | Input   |        | A-1        |

| 97  | 95      | B4 | P77      | ANI5         | Input   |        | A-1        |

| 96  | 94      | C4 | P76      | ANI6         | Input   |        | A-1        |

| 95  | 93      | D4 | P77      | ANI7         | Input   |        | A-1        |

| 94  | 92      | A5 | P78      | ANI8         | Input   |        | A-1        |

| 93  | 91      | B5 | P79      | ANI9         | Input   |        | A-1        |

| 92  | 90      | C5 | P710     | ANI10        | Input   |        | A-1        |

| 91  | 89      | D5 | P711     | ANI11        | Input   |        | A-1        |

# Table 4-9. Port 7 Alternate-Function Pins

**Remark** GF: 100-pin plastic LQFP (14 × 20) (*µ*PD70F3737, 70F3738 only)

GC: 100-pin plastic LQFP (fine pitch) ( $14 \times 14$ )

F1: 121-pin plastic FBGA ( $8 \times 8$ )

# (7) Port 9 function register (PF9)

| After re      | set: 0000H                                                                                | R/W                        | Address                  | PF9 FFF<br>PF9L FF       | ,                       | PF9H FFF    | FFC73H       |                           |  |  |

|---------------|-------------------------------------------------------------------------------------------|----------------------------|--------------------------|--------------------------|-------------------------|-------------|--------------|---------------------------|--|--|

|               | 15                                                                                        | 14                         | 13                       | 12                       | 11                      | 10          | 9            | 8                         |  |  |

| PF9 (PF9H)    | PF915                                                                                     | PF914                      | PF913                    | PF912                    | PF911                   | PF910       | PF99         | PF98                      |  |  |

|               | 7                                                                                         | 6                          | 5                        | 4                        | 3                       | 2           | 1            | 0                         |  |  |

| (PF9L)        | PF97                                                                                      | PF96                       | PF95                     | PF94                     | PF93                    | PF92        | PF91         | PF90                      |  |  |

|               |                                                                                           |                            |                          |                          |                         |             |              |                           |  |  |

|               | PF9n Specification of normal output (CMOS output) or N-ch open-drain output (n = 0 to 15) |                            |                          |                          |                         |             |              |                           |  |  |

|               | 0 Normal output (CMOS output)                                                             |                            |                          |                          |                         |             |              |                           |  |  |

|               | 1                                                                                         | N-ch oper                  | n-drain outp             | out                      |                         |             |              |                           |  |  |

| 1.<br>Pull up |                                                                                           | ns P97 to                  | P915 to t                |                          |                         | •           |              | o set the F<br>en they ar |  |  |

|               | ever, wher<br>s as the Pl                                                                 | n using the<br>=9L registe | e higher 8<br>er, PF9 ca | bits of the<br>n be read | e PF9 reg<br>or writter | ister as th | or 1-bit uni |                           |  |  |

#### 5.6 Wait Function

#### 5.6.1 Programmable wait function

#### (1) Data wait control register 0 (DWC0)

To realize interfacing with a low-speed memory or I/O device, up to seven data wait states can be inserted in the bus cycle that is executed for each memory block space.

The number of wait states can be programmed by using the DWC0 register. Immediately after system reset, 7 data wait states are inserted for all the memory block areas.

The DWC0 register can be read or written in 16-bit units.

Reset sets this register to 7777H.

- Cautions 1. The internal ROM and internal RAM areas are not subject to programmable wait, and are always accessed without a wait state. The on-chip peripheral I/O area is also not subject to programmable wait, and only wait control from each peripheral function is performed.

- 2. Write to the DWC0 register after reset, and then do not change the set values. Also, when changing the initial values of the DWC0 register, do not access an external memory area until the settings are complete.

| г    | 15                                                  | 14        | 13          | 12            | 11              | 10             | 9               | 8              |  |

|------|-----------------------------------------------------|-----------|-------------|---------------|-----------------|----------------|-----------------|----------------|--|

| DWC0 | 0                                                   | DW32      | DW31        | DW30          | 0               | DW22           | DW21            | DW20           |  |

| Memo | ry block n                                          | signal Me | emory blocl | <b>&lt;</b> 3 |                 | Μ              | emory bloc      | k 2            |  |

| -    | 7                                                   | 6         | 5           | 4             | 3               | 2              | 1               | 0              |  |

|      | 0                                                   | DW12      | DW11        | DW10          | 0               | DW02           | DW01            | DW00           |  |

| Memo | 1emory block n signal Memory block 1 Memory block 0 |           |             |               |                 |                |                 |                |  |

|      | DWn2                                                | DWn1      | DWn0        | Number of w   | ait states inse | rted in memory | y block n space | e (n = 0 to 3) |  |

|      | 0                                                   | 0         | 0           | None          |                 |                |                 |                |  |

|      | 0                                                   | 0         | 1           | 1             |                 |                |                 |                |  |

|      | 0                                                   | 1         | 0           | 2             |                 |                |                 |                |  |

|      | 0                                                   | 1         | 1           | 3             |                 |                |                 |                |  |

|      | 1                                                   | 0         | 0           | 4             |                 |                |                 |                |  |

|      | 1                                                   | 0         | 1           | 5             |                 |                |                 |                |  |

|      | 1                                                   | 1         | 0           | 6             |                 |                |                 |                |  |

|      | 1                                                   | 1         | 1           | 7             |                 |                |                 |                |  |

| L    |                                                     |           |             |               |                 |                |                 |                |  |

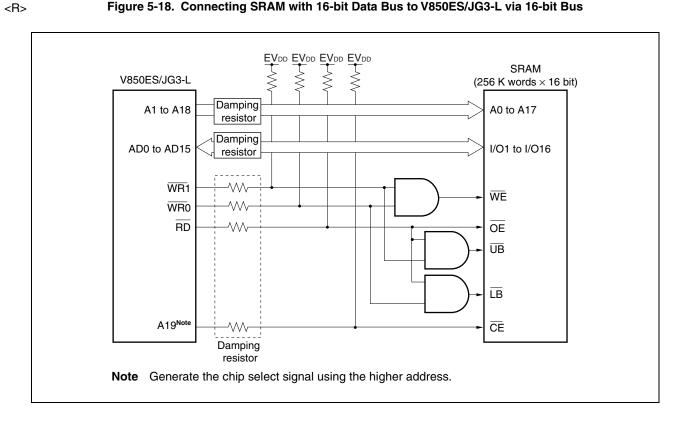

## Figure 5-18. Connecting SRAM with 16-bit Data Bus to V850ES/JG3-L via 16-bit Bus

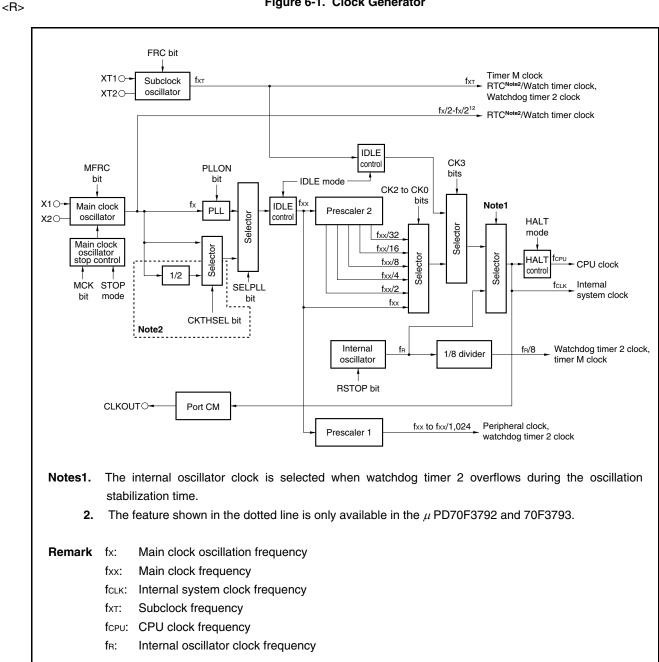

## 6.2 Configuration

# 7.4 Operations

TMPn can execute the following operations:

## Table 7-5. TMPn Operating Modes

| Operating Mode                                       | TPnCTL1.TPnEST<br>Bit<br>(Software Trigger Bit) | TIPn0 Pin<br>(External Trigger<br>Input) | Capture/Compare<br>Register Setting | Compare Register<br>Write | Count Clock       |

|------------------------------------------------------|-------------------------------------------------|------------------------------------------|-------------------------------------|---------------------------|-------------------|

| Interval timer mode                                  | Invalid                                         | Invalid                                  | Compare only                        | Anytime write             | Internal/external |

| External event count mode <sup>Note 1</sup>          | Invalid                                         | Invalid                                  | Compare only                        | Anytime write             | External          |

| External trigger pulse output mode <sup>Note 2</sup> | Valid                                           | Valid                                    | Compare only                        | Batch write               | Internal          |

| One-shot pulse output<br>mode <sup>Note 2</sup>      | Valid                                           | Valid                                    | Compare only                        | Anytime write             | Internal          |

| PWM output mode                                      | Invalid                                         | Invalid                                  | Compare only                        | Batch write               | Internal/external |

| Free-running timer mode                              | Invalid                                         | Invalid                                  | Can be switched                     | Anytime write             | Internal/external |

| Pulse width<br>measurement mode <sup>Note 2</sup>    | Invalid                                         | Invalid                                  | Capture only                        | Not applicable            | Internal          |

- **Notes 1.** When using the external event count mode, specify that the valid edge of the TIPn0 pin capture trigger input is not detected (by clearing the TPnIOC1.TPnIS1 and TPnIOC1.TPnIS0 bits to 0).

- 2. When using the external trigger pulse output mode, one-shot pulse output mode, and pulse width measurement mode, select the internal clock as the count clock (by clearing the TPnCTL1.TPnEEE bit to 0).

**Remark** n = 0 to 5

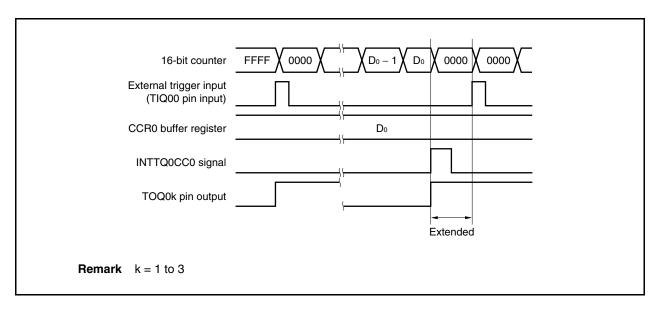

## (d) Detection of trigger immediately before or after INTTQ0CC0 generation

If the trigger is detected immediately after the INTTQ0CC0 signal is generated, the 16-bit counter is cleared to 0000H and continues incrementing. Therefore, the active period of the TOQ0k pin is extended by the amount of time between the generation of the INTTQ0CC0 signal and the detection of the trigger.

Figure 8-35. Detection of Trigger Immediately After INTTQ0CC0 Signal Was Generated

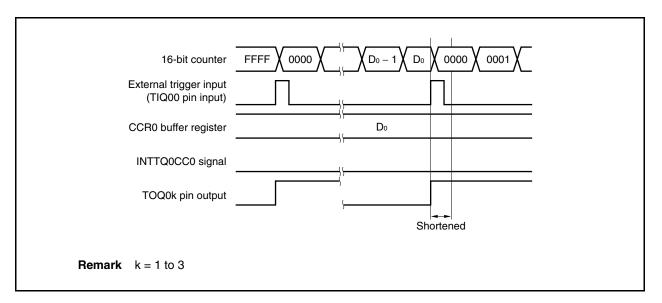

If the trigger is detected immediately before the INTTQ0CC0 signal is generated, the INTTQ0CC0 signal is not generated. The 16-bit counter is cleared to 0000H, the TOQ0k pin output is set to the active level, and the counter continues incrementing. Consequently, the inactive period of the PWM waveform is shortened.

Figure 8-36. Detection of Trigger Immediately Before INTTQ0CC0 Signal Is Generated

Figure 8-46. Register Settings in PWM Output Mode (3/3)

#### (f) TMQ0 capture/compare registers 0 to 3 (TQ0CCR0 to TQ0CCR3)

If the TQ0CCR0 register is set to  $D_0$  and the TQ0CCRk register is set to  $D_k$ , the PWM waveform is as follows:

$\label{eq:pwm} \begin{array}{l} \text{PWM waveform cycle} = (D_0 + 1) \times \text{Count clock cycle} \\ \\ \text{PWM waveform active level width} = D_{k} \times \text{Count clock cycle} \end{array}$

# **Remarks 1.** TMQ0 I/O control register 1 (TQ0IOC1) and TMQ0 option register 0 (TQ0OPT0) are not used in the PWM output mode.

Updating TMQ0 capture/compare register 2 (TQ0CCR2) and TMQ0 capture/compare register 3 (TQ0CCR3) is enabled by writing to TMQ0 capture/compare register 1 (TQ0CCR1).

| JC0SLS2    | UC0SLS1     | UC0SLS0       | SBF transmit length selection                                                      |

|------------|-------------|---------------|------------------------------------------------------------------------------------|

| 1          | 0           | 1             | 13-bit output (initial value)                                                      |

| 1          | 1           | 0             | 14-bit output                                                                      |

| 1          | 1           | 1             | 15-bit output                                                                      |

| 0          | 0           | 0             | 16-bit output                                                                      |

| 0          | 0           | 1             | 17-bit output                                                                      |

| 0          | 1           | 0             | 18-bit output                                                                      |

| 0          | 1           | 1             | 19-bit output                                                                      |

| 1          | 0           | 0             | 20-bit output                                                                      |

| This regis | ster can be | set when th   | ne UC0PWR bit or the UC0TXE bit is 0.                                              |

|            |             |               |                                                                                    |

| JCOTDL     |             |               | Transmit data level bit                                                            |

| 0          | Normal or   | utput of trar | sfer data                                                                          |

| 1          | Inverted of | output of tra | nsfer data                                                                         |

|            |             |               | pin can be inverted by using the UC0TDL bit the UC0PWR bit or the UC0TXE bit is 0. |

| UCORDL     |             |               | Receive data level bit                                                             |

| 0          | Normal in   | put of trans  | fer data                                                                           |

| 0          |             |               | sfer data                                                                          |

| IICX0 |               | IICCL0    |           | Selection Clock                     | Transfer | Settable Main Clock                                      | Operating      |

|-------|---------------|-----------|-----------|-------------------------------------|----------|----------------------------------------------------------|----------------|

|       | Dit 0         |           | Rit O     | Selection Clock                     | Clock    | Frequency (fxx) Range                                    | Mode           |

| Bit 0 | Bit 3<br>SMC0 | Bit 1     | Bit 0     |                                     |          |                                                          |                |

| CLX0  | 0<br>0        | CL01<br>0 | CL00<br>0 | $f_{\rm ex}$ (when OCKS0 - 19H act) | fxx/44   | 2 50 MHz < free < 1 10 MHz                               | Standard       |

| 0     | 0             | 0         | 0         | fxx (when OCKS0 = 18H set)          |          | $2.50 \text{ MHz} \le f_{xx} \le 4.19 \text{ MHz}$       | mode           |

|       |               |           |           | fxx/2 (when OCKS0 = 10H set)        | fxx/88   | 4.00 MHz $\leq$ fxx $\leq$ 8.38 MHz                      | (SMC0 bit = 0) |

|       |               |           |           | fxx/3 (when OCKS0 = 11H set)        | fxx/132  | 6.00 MHz ≤ fxx ≤ 12.57 MHz                               | -              |

|       |               |           |           | fxx/4 (when OCKS0 = 12H set)        | fxx/176  | 8.00 MHz ≤ fxx ≤ 16.76 MHz                               |                |

|       |               |           |           | fxx/5 (when OCKS0 = 13H set)        | fxx/220  | 10.00 MHz $\leq$ fxx $\leq$ 20.00 MHz                    | -              |

| 0     | 0             | 0         | 1         | fxx (when OCKS0 = 18H set)          | fxx/86   | 4.19 MHz $\leq$ fxx $\leq$ 8.38 MHz                      | -              |

|       |               |           |           | fxx/2 (when OCKS0 = 10H set)        | fxx/172  | 8.38 MHz ≤ fxx ≤ 16.76 MHz                               |                |

|       |               |           |           | fxx/3 (when OCKS0 = 11H set)        | fxx/258  | 12.57 MHz $\leq$ fxx $\leq$ 20.00 MHz                    | -              |

|       |               |           |           | fxx/4 (when OCKS0 = 12H set)        | fxx/344  | 16.76 MHz $\leq$ fxx $\leq$ 20.00 MHz                    |                |

| 0     | 0             | 1         | 0         | fxx <sup>Note</sup>                 | fxx/86   | $4.19 \text{ MHz} \leq \text{fxx} \leq 8.38 \text{ MHz}$ |                |

| 0     | 0             | 1         | 1         | fxx (when OCKS0 = 18H set)          | fxx/66   | fxx = 6.40 MHz                                           |                |

|       |               |           |           | fxx/2 (when OCKS0 = 10H set)        | fxx/132  | fxx = 12.80 MHz                                          |                |

|       |               |           |           | fxx/3 (when OCKS0 = 11H set)        | fxx/198  | fxx = 19.20 MHz                                          |                |

| 0     | 1             | 0         | ×         | fxx (when OCKS0 = 18H set)          | fxx/24   | 4.19 MHz ≤ fxx ≤ 8.38 MHz                                | High-speed     |

|       |               |           |           | fxx/2 (when OCKS0 = 10H set)        | fxx/48   | 8.00 MHz ≤ fxx ≤ 16.76 MHz                               | mode           |

|       |               |           |           | fxx/3 (when OCKS0 = 11H set)        | fxx/72   | 12.00 MHz $\leq$ fxx $\leq$ 20.00 MHz                    | (SMC0 bit = 1) |

|       |               |           |           | fxx/4 (when OCKS0 = 12H set)        | fxx/96   | $16.00 \text{ MHz} \le \text{fxx} \le 20.00 \text{ MHz}$ |                |

| 0     | 1             | 1         | 0         | fxx <sup>Note</sup>                 | fxx/24   | $4.00 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   |                |

| 0     | 1             | 1         | 1         | fxx (when OCKS0 = 18H set)          | fxx/18   | fxx = 6.40 MHz                                           |                |

|       |               |           |           | fxx/2 (when OCKS0 = 10H set)        | fxx/36   | fxx = 12.80 MHz                                          |                |

|       |               |           |           | fxx/3 (when OCKS0 = 11H set)        | fxx/54   | fxx = 19.20 MHz                                          |                |

| 1     | 1             | 0         | ×         | fxx (when OCKS0 = 18H set)          | fxx/12   | $4.00 \text{ MHz} \le f_{xx} \le 4.19 \text{ MHz}$       |                |

|       |               |           |           | fxx/2 (when OCKS0 = 10H set)        | fxx/24   | 8.00 MHz ≤ fxx ≤ 8.38 MHz                                | -              |

|       |               |           |           | fxx/3 (when OCKS0 = 11H set)        | fxx/36   | 12.00 MHz ≤ fxx ≤ 12.57 MHz                              |                |

|       |               |           |           | fxx/4 (when OCKS0 = 12H set)        | fxx/48   | 16.00 MHz ≤ fxx ≤ 16.67 MHz                              | 1              |

|       |               |           |           | fxx/5 (when OCKS0 = 13H set)        | fxx/60   | fxx = 20.00 MHz                                          | 1              |

| 1     | 1             | 1         | 0         | fxx <sup>Note</sup>                 | fxx/12   | 4.00 MHz ≤ fxx ≤ 4.19 MHz                                | 1              |

|       | Other tha     | an above  |           | Setting prohibited                  | _        | _                                                        | _              |

Table 19-2. Clock Settings (1/2)

**Note** Since the selection clock is fxx regardless of the value set to the OCKS0 register, clear the OCKS0 register to 00H (l<sup>2</sup>C division clock stopped status).

Remark ×: don't care

(8) When arbitration loss occurs due to low level of SDA0n pin when attempting to generate a stop condition

## 22.4 Cautions

- (1) If a low level is input to any of the KR0 to KR7 pins, the INTKR signal is not generated even if the falling edge is input to another pin.

- (2) The RXDA1 and KR7 pins must not be used at the same time. When using the RXDA1 pin, do not use the KR7 pin. When using the KR7 pin, do not use the RXDA1 pin (it is recommended to set the PFC91 bit to 1 and clear PFCE91 bit to 0).

- (3) If the KRM register is changed, an interrupt request signal (INTKR) may be generated. To prevent this, change the KRM register after disabling (DI) or masking interrupts, then clear the interrupt request flag (KRIC.KRIF bit) to 0, and enable (EI) or unmask interrupts.

- (4) To use the key interrupt function, be sure to set the function of the port pin to "key return pin" and then enable the key interrupt function by using the KRM register. To switch the pin function from key return pin to port pin, disable the key interrupt function by using the KRM register and then set pin function to "port pin".

<R>

## Table 23-7. Operating Status in IDLE2 Mode

|                      | Setting of IDLE2 Mode                    | Operatin                                                                                            | ig Status                                                                        |  |  |  |  |  |

|----------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Item                 |                                          | When Subclock Is Not Used                                                                           | When Subclock Is Used                                                            |  |  |  |  |  |

| LVI                  |                                          | Operable                                                                                            |                                                                                  |  |  |  |  |  |

| Main clock oscillat  | or                                       | Oscillates                                                                                          |                                                                                  |  |  |  |  |  |

| Subclock oscillator  |                                          | _                                                                                                   | Oscillates                                                                       |  |  |  |  |  |

| Internal oscillator  |                                          | Oscillation enabled                                                                                 |                                                                                  |  |  |  |  |  |

| PLL                  |                                          | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| CPU                  |                                          | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| DMA                  |                                          | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| Interrupt controller |                                          | Stops operation (but standby mode release                                                           | e is possible)                                                                   |  |  |  |  |  |

| Timer P (TMP0 to     | TMP5)                                    | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| Timer Q (TMQ0)       |                                          | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| Timer M (TMM0)       |                                          | Operable when $f_{\mbox{\scriptsize F}}/8$ is selected as the count clock                           | Operable when $f_{\text{R}}/8$ or $f_{\text{XT}}$ is selected as the count clock |  |  |  |  |  |

| Watch timer(/RTC)    | Note1                                    | Operable when fx (divided BRG) is selected as the count clock                                       | Operable                                                                         |  |  |  |  |  |

| Watchdog timer 2     |                                          | Operable when fn/8 is selected as the count clock                                                   | Operable when $f_{\text{R}}/8$ or $f_{\text{XT}}$ is selected as the count clock |  |  |  |  |  |

| Serial interface     | CSIB0 to CSIB4                           | Operable when the $\overline{\text{SCKBn}}$ input clock is selected as the count clock (n = 0 to 4) |                                                                                  |  |  |  |  |  |

|                      | l <sup>2</sup> C00 to l <sup>2</sup> C02 | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

|                      | UARTA0 to UARTA5                         | Stops operation (but UARTA0 is operable when the ASCKA0 input clock is selected)                    |                                                                                  |  |  |  |  |  |

|                      | UARTC0 <sup>Note1</sup>                  | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| A/D converter        |                                          | Holds operation (conversion result held) <sup>Note</sup>                                            | 2                                                                                |  |  |  |  |  |

| D/A converter        |                                          | Holds operation (output held <sup>Note2</sup> )                                                     |                                                                                  |  |  |  |  |  |

| Real-time output fu  | unction (RTO)                            | Stops operation (output held)                                                                       |                                                                                  |  |  |  |  |  |

| Key interrupt funct  | ion (KR)                                 | Operable                                                                                            |                                                                                  |  |  |  |  |  |

| CRC operation cire   | cuit                                     | Stops operation                                                                                     |                                                                                  |  |  |  |  |  |

| External bus interf  | ace                                      | See 2.2 Pin States.                                                                                 |                                                                                  |  |  |  |  |  |

| Port function        |                                          | Retains status before IDLE2 mode was set                                                            | t                                                                                |  |  |  |  |  |

| CPU register set     |                                          | Retains status before IDLE2 mode was set                                                            | t                                                                                |  |  |  |  |  |

| Internal RAM         |                                          |                                                                                                     |                                                                                  |  |  |  |  |  |

**Notes1.** *μ* PD70F3792, 70F3793 only

2. To realize low power consumption, stop the A/D and D/A converters before shifting to the IDLE2 mode.

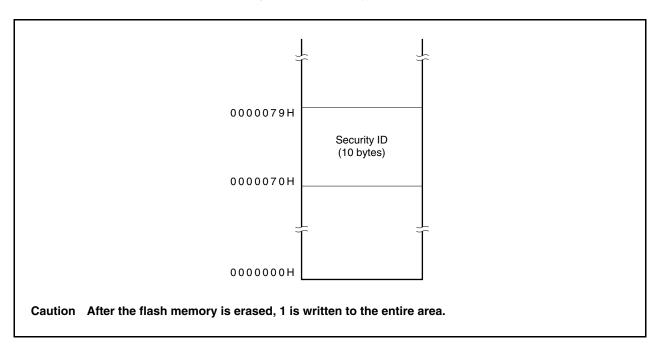

## 31.3 ROM Security Function

#### 31.3.1 Security ID

The flash memory versions of the V850ES/JG3-L perform authentication using a 10-byte ID code to prevent the contents of the flash memory from being read by an unauthorized person during on-chip debugging by the on-chip debug emulator.

Set the ID code in the 10-byte internal flash memory area from 0000070H to 0000079H to allow the debugger perform ID authentication.

If the IDs match, the security is released and reading the flash memory and using the on-chip debug emulator are enabled.

- Set the 10-byte ID code to 0000070H to 0000079H.

- Bit 7 of 0000079H is the on-chip debug emulator enable flag.

(0: Disable, 1: Enable)

- When the on-chip debug emulator is started, the debugger requests ID input. When the ID code input to the debugger and the ID code set in 0000070H to 0000079H match, the debugger starts.

- Debugging cannot be performed if the on-chip debug emulator enable flag is 0, even if the ID codes match.

#### Figure 31-6. Security ID Area

# 32.6 DC Characteristics

# 32.6.1 Pin characteristics

| Parameter                    | Symbol | Conditions                                                                            | MIN.      | TYP. | MAX.                | Unit |

|------------------------------|--------|---------------------------------------------------------------------------------------|-----------|------|---------------------|------|

| Input voltage, high          | VIH1   | RESET, FLMD0, P97 to P915                                                             | 0.8EVDD   |      | EVDD                | V    |

|                              | VIH2   | P02 to P06, P30 to P37, P42, P50 to P55,<br>P92 to P96                                | 0.8EVDD   |      | 5.5                 | V    |

|                              | VIH3   | P38, P39, P40, P41, P90, P91                                                          | 0.7EVDD   |      | 5.5                 | V    |

|                              | VIH4   | PCM0 to PCM3, PCT0, PCT1, PCT4,<br>PCT6, PDH0 to PDH5, PDL0 to PDL15                  | 0.7EVDD   |      | EV <sub>DD</sub>    | V    |

|                              | VIH5   | P70 to P711                                                                           | 0.7AVREF0 |      | AV <sub>REF0</sub>  | V    |

|                              | VIH6   | P10, P11                                                                              | 0.7AVREF1 |      | AV <sub>REF1</sub>  | V    |

| Input voltage, low           | VIL1   | RESET, FLMD0, P97 to P915                                                             | EVss      |      | 0.2EV <sub>DD</sub> | V    |

|                              | VIL2   | P02 to P06, P30 to P37, P42, P50 to P55,<br>P92 to P96                                | EVss      |      | 0.2EV <sub>DD</sub> | V    |

|                              | VIL3   | P38, P39, P40, P41, P90, P91                                                          | EVss      |      | 0.3EVDD             | V    |

|                              | VIL4   | PCM0 to PCM3, PCT0, PCT1, PCT4,<br>PCT6, PDH0 to PDH5, PDL0 to PDL15                  | EVss      |      | 0.3EV <sub>DD</sub> | V    |

|                              | VIL5   | P70 to P711                                                                           | AVss      |      | 0.3AVREF0           | V    |

|                              | VIL6   | P10, P11                                                                              | AVss      |      | 0.3AVREF1           | V    |

| Input leakage current, high  | Іцн    | $V_1 = V_{DD} = EV_{DD} = AV_{REF0} = AV_{REF1}$                                      |           |      | 5                   | μA   |

| Input leakage current, low   | Ilil   | V1 = 0 V                                                                              |           |      | -5                  | μA   |

| Output leakage current, high | Ігон   | $V_{\text{O}} = V_{\text{DD}} = EV_{\text{DD}} = AV_{\text{REF0}} = AV_{\text{REF1}}$ |           |      | 5                   | μA   |

| Output leakage current, low  | Ilol   | Vo = 0 V                                                                              |           |      | -5                  | μA   |

# (TA = -40 to +85°C, VDD = EVDD = AVREF0 = AVREF1 = 2.2 to 3.6 V, Vss = EVss = AVss = 0 V) (1/2)

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

| Symbol | Name                                                                                                                  | Unit             | (4/1<br>Page |

|--------|-----------------------------------------------------------------------------------------------------------------------|------------------|--------------|

| DTFR2  |                                                                                                                       | DMAC             | 765          |

|        | DMA trigger factor register 2                                                                                         |                  |              |

| DTFR3  | DMA trigger factor register 3                                                                                         | DMAC             | 765          |

| DWC0   | Data wait control register 0                                                                                          | BCU              | 197          |

| ECR    | Interrupt source register                                                                                             | CPU              | 59           |

| EIPC   | Interrupt status saving register                                                                                      | CPU              | 58           |

| EIPSW  | Interrupt status saving register                                                                                      | CPU              | 58           |

| EXIMC  | External bus interface mode control register                                                                          | BCU              | 187          |

| FEPC   | NMI status saving register                                                                                            | CPU              | 59           |

| FEPSW  | NMI status saving register                                                                                            | CPU              | 59           |

| IIC0   | IIC shift register 0                                                                                                  | I <sup>2</sup> C | 700          |

| IIC1   | IIC shift register 1                                                                                                  | I <sup>2</sup> C | 700          |

| IIC2   | IIC shift register 2                                                                                                  | I <sup>2</sup> C | 700          |

| IICC0  | IIC control register 0                                                                                                | I <sup>2</sup> C | 686          |

| IICC1  | IIC control register 1                                                                                                | I <sup>2</sup> C | 686          |

| IICC2  | IIC control register 2                                                                                                | I <sup>2</sup> C | 686          |

| IICCL0 | IIC clock select register 0                                                                                           | l <sup>2</sup> C | 696          |

| IICCL1 | IIC clock select register 1                                                                                           | I <sup>2</sup> C | 696          |

| IICCL2 | IIC clock select register 2                                                                                           | l <sup>2</sup> C | 696          |

| IICF0  | IIC flag register 0                                                                                                   | I <sup>2</sup> C | 694          |

| IICF1  | IIC flag register 1                                                                                                   | I <sup>2</sup> C | 694          |

| IICF2  | IIC flag register 2                                                                                                   | I <sup>2</sup> C | 694          |

| IICIC0 | Interrupt control register                                                                                            | INTC             | 799          |

| IICIC1 | Interrupt control register                                                                                            | INTC             | 799          |

| IICIC2 | Interrupt control register                                                                                            | INTC             | 799          |

| IICS0  | IIC status register 0                                                                                                 | I <sup>2</sup> C | 691          |

| IICS1  | IIC status register 1                                                                                                 | I <sup>2</sup> C | 691          |

| IICS2  | IIC status register 2                                                                                                 | l <sup>2</sup> C | 691          |

| IICX0  | IIC function expansion register 0                                                                                     | l <sup>2</sup> C | 697          |

| IICX1  | IIC function expansion register 1                                                                                     | l <sup>2</sup> C | 697          |

| IICX2  | IIC function expansion register 2                                                                                     | l <sup>2</sup> C | 697          |

| IMR0   | Interrupt mask register 0                                                                                             | INTC             | 801          |

| IMR0H  | Interrupt mask register 0H                                                                                            | INTC             | 801          |

| IMR0L  | Interrupt mask register 0L                                                                                            | INTC             | 801          |

| IMR1   | Interrupt mask register 1                                                                                             | INTC             | 801          |

| IMR1H  | Interrupt mask register 1H                                                                                            | INTC             | 801          |

| IMR1L  | Interrupt mask register 1L                                                                                            | INTC             | 801          |

| IMR2   | Interrupt mask register 2                                                                                             | INTC             | 801          |

| IMR2H  | Interrupt mask register 2H                                                                                            | INTC             | 801          |

| IMR2L  | Interrupt mask register 2L                                                                                            | INTC             | 801          |

| IMR3   | Interrupt mask register 3                                                                                             | INTC             | 801          |

| IMR3H  | Interrupt mask register 3H                                                                                            | INTC             | 801          |

| IMR3L  | Interrupt mask register 3L                                                                                            | INTC             | 801          |

| INTF0  | External interrupt falling edge specification register 0                                                              | INTC             | 815          |

|        |                                                                                                                       |                  |              |

| INTF3  | External interrupt falling edge specification register 3<br>External interrupt falling edge specification register 9H |                  | 816<br>817   |

| Edition | Description                                                                                                                                                    | Applied to:                                                          |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| 3rd     | <ul> <li>Addition of products<br/>μPD70F3737F1-GC-CAH-A, 70F3738F1-CAH-A</li> </ul>                                                                            | Throughout                                                           |  |

|         | Modification of Table 1-1. V850ES/Jx3-L Product List                                                                                                           | CHAPTER 1<br>INTRODUCTION                                            |  |

|         | Addition of Figure 3-10 Sign Extension in Data Space                                                                                                           | CHAPTER 3 CPU<br>FUNCTION                                            |  |

|         | Modification of Table 5-3 Pin Statuses When Internal ROM, Internal RAM, or On-Chip Peripheral I/O Is Accessed                                                  | CHAPTER 5 BUS<br>CONTROL<br>FUNCTION<br>CHAPTER 6 CLOCK<br>GENERATOR |  |

|         | Addition of 5.11 SRAM Connection Examples                                                                                                                      |                                                                      |  |

|         | Addition of 6.4.3 External clock signal input                                                                                                                  |                                                                      |  |

|         | Addition of 6.6 How to Connect a Resonator                                                                                                                     |                                                                      |  |

|         | Addition of 7.2.1 Pins used by TMPn                                                                                                                            | CHAPTER 7 16-BIT<br>TIMER/EVENT                                      |  |

|         | Addition of 7.2.2 Interrupts                                                                                                                                   |                                                                      |  |

|         | Addition of 7.4 (1) Basic counter operation                                                                                                                    | COUNTER P (TMP)                                                      |  |

|         | Addition of 7.4 (2) Anytime write and batch write                                                                                                              |                                                                      |  |

|         | Addition of 7.4.1 (3) Operation of interval timer based on input of external event count                                                                       | -                                                                    |  |

|         | Modification of Figure 7-28 Register Settings in External Trigger Pulse Output Mode                                                                            | -                                                                    |  |

|         | Modification of Figure 7-40 Register Settings in One-Shot Pulse Output Mode                                                                                    |                                                                      |  |

|         | Addition of 8.2.1 Pins used by TMQ0                                                                                                                            | CHAPTER 8 16-BIT                                                     |  |

|         | Addition of 8.2.2 Interrupts                                                                                                                                   | TIMER/EVENT                                                          |  |

|         | Addition of 8.4 (1) Basic counter operation                                                                                                                    | COUNTER Q (TMQ)                                                      |  |

|         | Addition of 8.4 (2) Anytime write and batch write                                                                                                              |                                                                      |  |

|         | Addition of 8.4.1 (3) Operation of interval timer based on input of external event count                                                                       | -                                                                    |  |

|         | Modification of Figure 8-28 Register Settings in External Trigger Pulse Output Mode                                                                            | 1                                                                    |  |

|         | Modification of Figure 8-40 Register Settings in One-Shot Pulse Output Mode                                                                                    | -                                                                    |  |

|         | Modification of Figure 13-4 Example of Timing in Continuous Select Mode (ADA0S Register = 01H)                                                                 | CHAPTER 13 A/D<br>CONVERTER                                          |  |

|         | Modification of Figure 13-5 Example of Timing in Continuous Scan Mode (ADA0S<br>Register = 03H)                                                                |                                                                      |  |

|         | Modification of Figure 13-6 Example of Timing in One-Shot Select Mode (ADA0S<br>Register = 01H)                                                                |                                                                      |  |

|         | Modification of Figure 13-7 Example of Timing in One-Shot Scan Mode (ADA0S Register = 03H)                                                                     |                                                                      |  |

|         | Modification of Figure 13-8 Example of Timing in Continuous Select Mode<br>(When Power-Fail Comparison Is Made: ADA0PFM.ADA0PFC bit = 0, ADA0S Register = 01H) |                                                                      |  |

|         | Modification of Figure 13-9 Example of Timing in Continuous Scan Mode<br>(When Power-Fail Comparison Is Made: ADA0PFM.ADA0PFC bit = 0, ADA0S Register = 03H)   |                                                                      |  |

|         | Modification of Figure 13-10 Example of Timing in One-Shot Select Mode<br>(When Power-Fail Comparison Is Made: ADA0PFM.ADA0PFC bit = 1, ADA0S Register = 01H)  |                                                                      |  |

|         | Modification of Figure 13-11 Example of Timing in One-Shot Scan Mode<br>(When Power-Fail Comparison Is Made: ADA0PFM.ADA0PFC bit = 0, ADA0S Register = 03H)    |                                                                      |  |