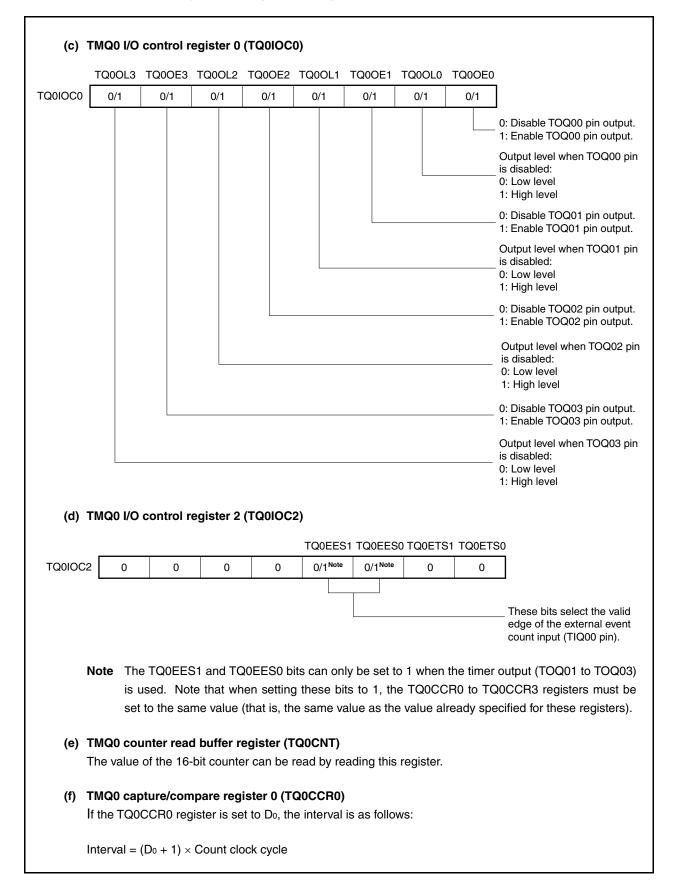

# E. Renesas Electronics America Inc - UPD70F3792GC-UEU-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 20MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 83                                                                                   |

| Program Memory Size        | 384KB (384K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 32K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                            |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3792gc-ueu-ax |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| CHAPIER                         | R 26 LOW-VOLTAGE DETECTOR (LVI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26.1                            | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| 26.2                            | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| 26.3                            | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| 26.4                            | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

|                                 | 26.4.1 To use for internal reset signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

|                                 | 26.4.2 To use for interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

| СНАРТЕ                          | R 27 CRC FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 887                                                                                                                                                    |

| 27.1                            | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| 27.1                            | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| 27.2                            | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| 27.3                            | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| 27.5                            | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |

|                                 | j-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |

| CHAPTER                         | R 28 REGULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                        |

| 28.1                            | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

| 28.2                            | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 894                                                                                                                                                    |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

| CHAPTER                         | R 29 OPTION BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |

| 29.1                            | Program Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 897                                                                                                                                                    |

|                                 | R 30 FLASH MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 000                                                                                                                                                    |

|                                 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| 30.1                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 898                                                                                                                                                    |

|                                 | Mamary Continuiration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 000                                                                                                                                                    |

| 30.2                            | Memory Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |

| 30.3                            | Functional Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 901                                                                                                                                                    |

|                                 | Functional Outline<br>Rewriting by Dedicated Flash Memory Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                     | 901<br>904                                                                                                                                             |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment                                                                                                                                                                                                                                                                                                                                                                                                     | 901<br>904<br>904                                                                                                                                      |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode                                                                                                                                                                                                                                                                                                                                                                         | 901<br>904<br>904<br>905                                                                                                                               |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface                                                                                                                                                                                                                                                                                                                                                      | 901<br>904<br>904<br>905<br>907                                                                                                                        |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control                                                                                                                                                                                                                                                                                                                        | 901<br>904<br>904<br>905<br>907<br>914                                                                                                                 |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode                                                                                                                                                                                                                                                                               | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915                                                                                                   |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode                                                                                                                                                                                                                                                                               | 901<br>904<br>904<br>905<br>907<br>907<br>914<br>915<br>916                                                                                            |

| 30.3                            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands                                                                                                                                                                                                                                               | 901<br>904<br>904<br>905<br>907<br>914<br>915<br>916<br>917                                                                                            |

| 30.3<br>30.4                    | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming                                                                                                                                                                                               | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915<br>916<br>917<br>917                                                                              |

| 30.3<br>30.4                    | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming                                                                                                                                                               | 901<br>904<br>904<br>905<br>907<br>914<br>915<br>916<br>917<br>917<br>921                                                                              |

| 30.3<br>30.4                    | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming   30.5.1 Overview                                                                                                                                             | 901<br>904<br>904<br>905<br>907<br>914<br>915<br>916<br>917<br>917<br>921<br>921                                                                       |

| 30.3<br>30.4                    | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming   30.5.1 Overview   30.5.2 Features                                                                                                                           | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915<br>916<br>917<br>917<br>921<br>921<br>922<br>923                                                  |

| 30.3<br>30.4                    | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming   30.5.1 Overview   30.5.2 Features   30.5.3 Standard self programming flow                                                                                   | 901<br>904<br>904<br>905<br>907<br>914<br>915<br>916<br>916<br>917<br>921<br>921<br>922<br>923<br>923                                                  |

| 30.3<br>30.4                    | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming   30.5.1 Overview   30.5.2 Features   30.5.3 Standard self programming flow   30.5.4 Flash functions                                                          | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915<br>916<br>917<br>921<br>921<br>922<br>922<br>923<br>924                                           |

| 30.3<br>30.4<br>30.5            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming 30.5.1   30.5.2 Features   30.5.3 Standard self programming flow   30.5.4 Flash functions   30.5.5 Pin processing   30.5.6 Internal resources used            | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915<br>916<br>917<br>921<br>921<br>921<br>922<br>923<br>923<br>924<br>924<br>925                      |

| 30.3<br>30.4<br>30.5<br>CHAPTEF | Functional Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915<br>916<br>917<br>921<br>921<br>922<br>922<br>923<br>924<br>924<br>924<br>924                      |

| 30.3<br>30.4<br>30.5            | Functional Outline   Rewriting by Dedicated Flash Memory Programmer   30.4.1 Programming environment   30.4.2 Communication mode   30.4.3 Interface   30.4.4 Flash memory control   30.4.5 Selection of communication mode   30.4.6 Communication commands   30.4.7 Pin connection in on-board programming   Rewriting by Self Programming   30.5.1 Overview   30.5.2 Features   30.5.3 Standard self programming flow   30.5.4 Flash functions   30.5.5 Pin processing   30.5.6 Internal resources used | 901<br>904<br>904<br>905<br>905<br>907<br>914<br>915<br>916<br>917<br>921<br>921<br>921<br>922<br>923<br>923<br>924<br>924<br>924<br>925<br>926<br>928 |

| 30.3<br>30.4<br>30.5<br>CHAPTEF | Functional Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 901<br>904<br>904<br>905<br>907<br>914<br>915<br>916<br>917<br>921<br>921<br>922<br>923<br>923<br>924<br>924<br>924<br>925<br>928                      |

## **CHAPTER 1 INTRODUCTION**

The V850ES/JG3-L is one of the products in the NEC Electronics V850 single-chip microcontroller series designed for low-power operation for real-time control applications.

# 1.1 General

The V850ES/JG3-L is a 32-bit single-chip microcontroller that includes the V850ES CPU core and peripheral functions such as ROM/RAM, timer/counters, serial interfaces, an A/D converter, and a D/A converter.

In addition to high real-time response characteristics and 1-clock-pitch basic instructions, the V850ES/JG3-L features multiply instructions, saturated operation instructions, bit manipulation instructions, etc., realized by a hardware multiplier, as optimum instructions for digital servo control applications. Moreover, as a real-time control system, the V850ES/JG3-L enables an extremely high cost-performance for applications that require super low power consumption, such as digital cameras, electrical power meters, and mobile terminals.

Table 1-1 lists the products of the V850ES/JG3-L and V850ES/JF3-L.

The V850ES/JF3-L is a model of the V850ES/JG3-L with reduced I/O, timer/counter, and serial interface functions.

## <R> (2) Non-port functions

| Function |    | Pin N | 0.                         | I/O    | Description                                         | Alternate Function                                |

|----------|----|-------|----------------------------|--------|-----------------------------------------------------|---------------------------------------------------|

|          | GF | GC    | F1                         |        |                                                     |                                                   |

| A0       | 45 | 43    | H8                         | Output | Address bus for external memory                     | P90/KR6/TXDA1/SDA02                               |

| A1       | 46 | 44    | L9                         |        | (when using separate bus)                           | P91/KR7/RXDA1/SCL02                               |

| A2       | 47 | 45    | K9                         |        | N-ch open-drain output selectable.<br>5 V tolerant. | P92/TIP41/TOP41 (/TXDA4)                          |

| A3       | 48 | 46    | J9                         |        |                                                     | P93/TIP40/TOP40 (/RXDA4)                          |

| A4       | 49 | 47    | L10                        |        |                                                     | P94/TIP31/TOP31(/TXDA5) <sup>Note1</sup>          |

| A5       | 50 | 48    | K10                        |        |                                                     | P95/TIP30/TOP30 (/RXDA5)                          |

| A6       | 51 | 49    | K11                        |        |                                                     | P96 (/TXDC0) <sup>Note1</sup> /TIP21/TOP21        |

| A7       | 52 | 50    | J11                        |        |                                                     | P97/SIB1 (/RXDC0) /TIP20/TOP20                    |

| A8       | 53 | 51    | J10                        |        |                                                     | P98/SOB1                                          |

| A9       | 54 | 52    | H11                        |        |                                                     | P99/SCKB1                                         |

| A10      | 55 | 53    | H10                        |        |                                                     | P910/SIB3                                         |

| A11      | 56 | 54    | H9                         |        |                                                     | P911/SOB3                                         |

| A12      | 57 | 55    | G11                        |        |                                                     | P912/SCKB3                                        |

| A13      | 58 | 56    | G10                        |        |                                                     | P913/INTP4                                        |

| A14      | 59 | 57    | G9                         |        |                                                     | P914/INTP5/TIP51/TOP51                            |

| A15      | 60 | 58    | G8                         |        |                                                     | P915/INTP6/TIP50/TOP50                            |

| A16      | 89 | 87    | C6                         | Output | Address bus for external memory                     | PDH0                                              |

| A17      | 90 | 88    | D6                         |        |                                                     | PDH1                                              |

| A18      | 61 | 59    | F9                         |        |                                                     | PDH2                                              |

| A19      | 62 | 60    | F8                         |        |                                                     | PDH3                                              |

| A20      | 8  | 6     | F4                         |        |                                                     | PDH4                                              |

| A21      | 9  | 7     | J2,<br>G4 <sup>Note1</sup> |        |                                                     | P02/NMI <sup>Note1</sup><br>PDH5 <sup>Note2</sup> |

| AD0      | 73 | 71    | C11                        | I/O    | Address bus/data bus for external memory            | PDL0                                              |

| AD1      | 74 | 72    | C10                        |        |                                                     | PDL1                                              |

| AD2      | 75 | 73    | C9                         |        |                                                     | PDL2                                              |

| AD3      | 76 | 74    | B11                        |        |                                                     | PDL3                                              |

| AD4      | 77 | 75    | B10                        |        |                                                     | PDL4                                              |

| AD5      | 78 | 76    | A10                        |        |                                                     | PDL5/FLMD1                                        |

| AD6      | 79 | 77    | A9                         |        |                                                     | PDL6                                              |

| AD7      | 80 | 78    | B9                         |        |                                                     | PDL7                                              |

| AD8      | 81 | 79    | A8                         |        |                                                     | PDL8                                              |

| AD9      | 82 | 80    | B8                         |        |                                                     | PDL9                                              |

| AD10     | 83 | 81    | C8                         | 1      |                                                     | PDL10                                             |

| AD11     | 84 | 82    | A7                         | 1      |                                                     | PDL11                                             |

| AD12     | 85 | 83    | B7                         | 1      |                                                     | PDL12                                             |

| AD13     | 86 | 84    | C7                         | 1      |                                                     | PDL13                                             |

| AD14     | 87 | 85    | D7                         | 1      |                                                     | PDL14                                             |

| AD15     | 88 | 86    | B6                         | 1      |                                                     | PDL15                                             |

**Notes1.** *μ*PD70F3792, 70F3793 only.

**2.** μPD70F3737, 70F3738 only.

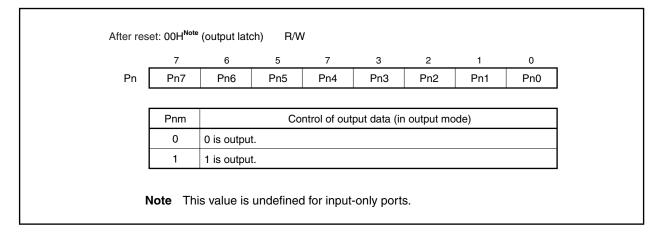

# (1) Port n register (Pn)

Data I/O with external devices is performed by writing to and reading from the Pn register. The Pn register is made up of a port latch that retains the output data and a circuit that reads the pin status.

Each bit of the Pn register corresponds to one pin of port n and can be read or written in 1-bit units.

The operation when writing or reading the Pn register differs depending on the specified mode.

| PMCn Register Setting                      | PMn Register Setting          | Writing Pn Register                                                                                                                        | Reading Pn Register                    |

|--------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Port mode<br>(PMCnm bit = 0)               | Output mode<br>(PMnm bit = 0) | Write to the output latch <sup>Note</sup> .<br>The contents of the output latch are output<br>from the pin.                                | The value of the output latch is read. |

|                                            | Input mode<br>(PMnm bit = 1)  | Write to the output latch <sup>Note</sup> .<br>The status of the pin is not affected.                                                      | The pin status is read.                |

| Alternate-function mode<br>(PMCnm bit = 1) | Output mode<br>(PMnm bit = 0) | Write to the output latch <sup>Note</sup> .<br>The status of the pin is not affected.<br>The pin operates as an alternate-function<br>pin. | The value of the output latch is read. |

|                                            | Input mode<br>(PMnm bit = 1)  | Write to the output latch <sup>Note</sup> .<br>The status of the pin is not affected.<br>The pin operates as an alternate-function<br>pin. | The pin status is read.                |

**Note** The value written to the output latch is retained until a new value is written to the output latch. The output latch value is cleared by a reset.

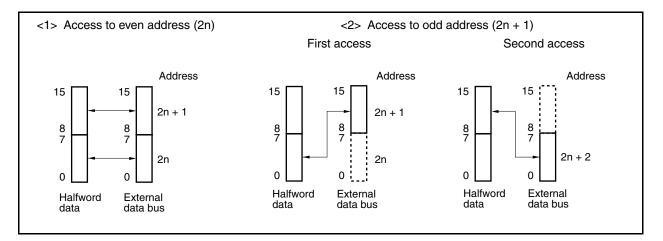

## (3) Halfword access (16 bits)

# (a) 16-bit data bus width

16-bit data is transmitted/received via a 16-bit bus. Therefore, if an even address is specified, the lower and higher bytes of the external data bus address are accessed at the same time. If an odd address is specified, the lower byte of the data is transmitted/received to/from an odd address via the higher byte of the external data bus address in the first access. In the second access, the higher byte of the data is transmitted/received to/from an odd address.

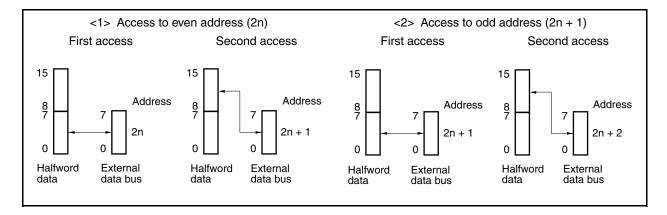

#### (b) 8-bit data bus width

16-bit data is transmitted/received via an 8-bit bus. Therefore, the data is transmitted/received in two accesses. The lower/higher byte of the data is transmitted/received to/from the corresponding lower/higher byte of the external bus address.

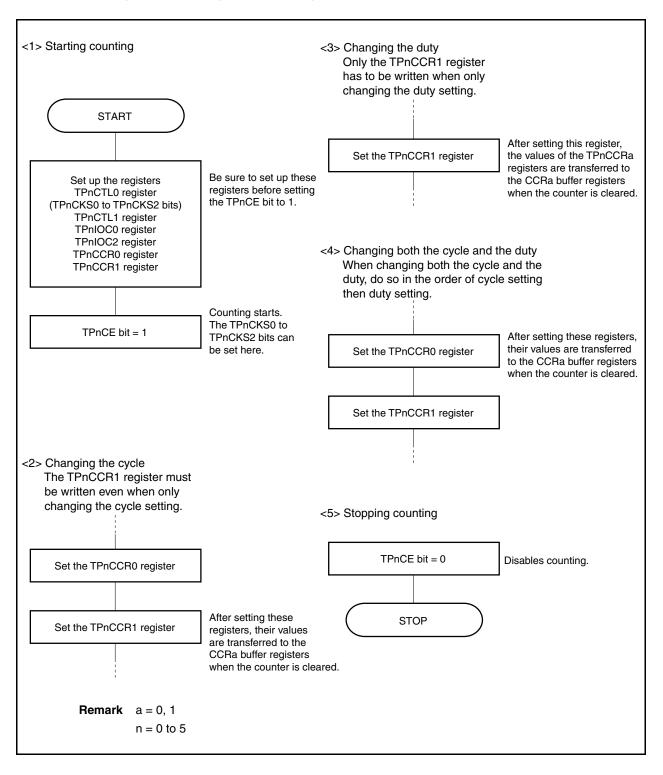

# (1) TMPn control register 0 (TPnCTL0)

The TPnCTL0 register is an 8-bit register that controls the operation of TMPn.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

The same value can always be written to the TPnCTL0 register by software.

| Aller ie     | eset: 00H                                                               | R/W               | Address:             |                      |                    | 590H, TP1C<br>5B0H, TP3C                           |                     | -                      |

|--------------|-------------------------------------------------------------------------|-------------------|----------------------|----------------------|--------------------|----------------------------------------------------|---------------------|------------------------|

|              |                                                                         |                   |                      |                      |                    | 5D0H, TP5C                                         |                     |                        |

|              |                                                                         |                   |                      | 11 4010              | 5 11111            | JD011, 11 50                                       |                     | 1 SEOIT                |

|              | <7>                                                                     | 6                 | 5                    | 4                    | 3                  | 2                                                  | 1                   | 0                      |

| TPnCTL0      | TPnCE                                                                   | 0                 | 0                    | 0                    | 0                  | TPnCKS2                                            | TPnCKS1             | TPnCKS                 |

| (n = 0 to 5) |                                                                         |                   |                      |                      |                    |                                                    |                     |                        |

|              | TPnCE                                                                   |                   |                      | TMPn                 | operation          | n control                                          |                     |                        |

|              | 0 TMPn operation disabled (TMPn reset asynchronously <sup>Note</sup> ). |                   |                      |                      |                    |                                                    |                     |                        |

|              | 1                                                                       | TMPn ope          | eration enab         | oled. TMP            | n operatio         | on started.                                        |                     |                        |

|              |                                                                         |                   |                      |                      |                    |                                                    |                     |                        |

|              | TPnCKS2                                                                 | TPnCKS1           | TPnCKS0              |                      | Interna            | l count clock                                      | selection           |                        |

|              |                                                                         |                   |                      | n                    | = 0, 2, 4          |                                                    | n = 1, 3            | , 5                    |

|              | 0                                                                       | 0                 | 0                    | fxx                  |                    |                                                    |                     |                        |

|              | 0                                                                       | 0                 | 1                    | fxx/2                |                    |                                                    |                     |                        |

|              | 0                                                                       | 1                 | 0                    | fxx/4                |                    |                                                    |                     |                        |

|              | 0                                                                       | 1                 | 1                    | fxx/8                |                    |                                                    |                     |                        |

|              | 1                                                                       | 0                 | 0                    | fxx/16               |                    |                                                    |                     |                        |

|              | 1                                                                       | 0                 | 1                    | fxx/32               |                    |                                                    |                     |                        |

|              | 1                                                                       | 1                 | 0                    | fxx/64               |                    | fx                                                 | √256                |                        |

|              | 1                                                                       | 1                 | 1                    | fxx/128              |                    | fx                                                 | <i>√</i> 512        |                        |

|              |                                                                         | 1. Set ti<br>Whei | heTPnCK<br>n the val | S2 to TP<br>ue of th | nCKS0 I<br>he TPnC | mer output<br>bits when<br>CE bit is<br>be set sir | the TPnC<br>changed | E bit = 0.<br>I from 0 |

#### Figure 8-8. Register Settings in Interval Timer Mode (2/3)

#### (2) Using interval timer mode

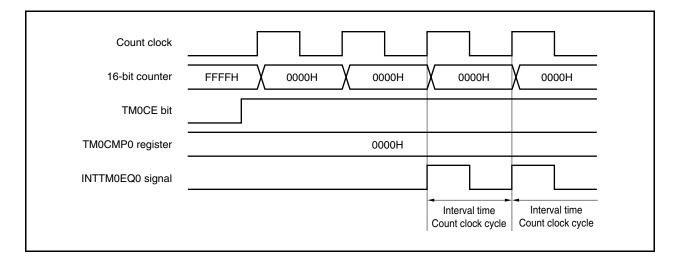

## (a) Operation when TM0CMP0 register is set to 0000H

When the TM0CMP0 register is set to 0000H, the INTTM0EQ0 signal is generated for each count clock cycle.

The value of the 16-bit counter is always 0000H.

#### Figure 9-6. Operation of Interval Timer When TM0CMP0 Register Is Set to 0000H

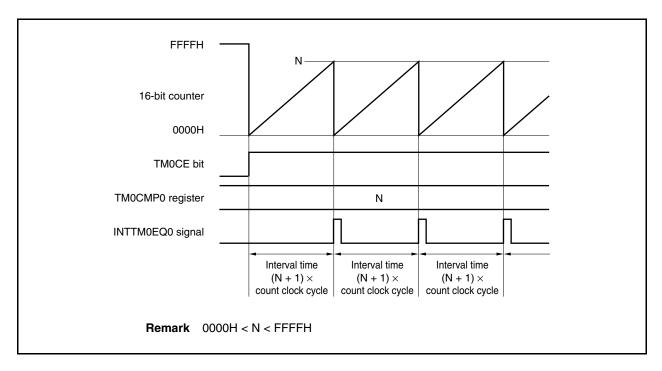

#### (b) Operation when TM0CMP0 register is set to N

When the TM0CMP0 register is set to N, the 16-bit counter increments up to N and is reset to 0000H in synchronization with the next increment timing. The INTTM0EQ0 signal is then generated.

# CHAPTER 10 WATCH TIMER

## 10.1 Functions

The watch timer has the following functions.

- Watch timer: An interrupt request signal (INTWT) is generated at intervals of 0.5 or 0.25 seconds by using the main clock or subclock.

- Interval timer: An interrupt request signal (INTWTI) is generated at set intervals.

The watch timer and interval timer functions can be used at the same time.

Caution INTWTI interrupt of the watch timer and INTRTC2 interrupt of RTC, and INTWT interrupt of the watch timer and INTRTC0 interrupt of RTC are alternate interrupt signals, and therefore cannot be used simultaneously. ( $\mu$  PD70F3792, 70F3793 only.)

# 16.3.3 UARTA2 and I<sup>2</sup>C00 mode switching

In the V850ES/JG3-L, UARTA2 and I<sup>2</sup>C00 share pins and therefore cannot be used simultaneously. To use the UARTA2 function, specify the UARTA2 mode in advance by using the PMC3 and PFC3 registers.

Switching the operation mode between UARTA2 and  $l^2C00$  are described below.

Caution Transmission and reception by UARTA2 and I<sup>2</sup>C00 are not guaranteed if these operation modes are switched during transmission or reception. Be sure to stop the serial interface that is not being used.

|           | 15         | 14     | 13         | 12    | 11        | 10     | 9     | 8           |  |  |  |  |  |  |  |  |

|-----------|------------|--------|------------|-------|-----------|--------|-------|-------------|--|--|--|--|--|--|--|--|

| PMC3      | 0          | 0      | 0          | 0     | 0         | 0      | PMC39 | PMC38       |  |  |  |  |  |  |  |  |

|           | 7          | 6      | 5          | 4     | 3         | 2      | 1     | 0           |  |  |  |  |  |  |  |  |

|           | 0          | 0      | PMC35      | PMC34 | PMC33     | PMC32  | PMC31 | PMC30       |  |  |  |  |  |  |  |  |

| After res | set: 0000H |        |            |       | 6H, FFFFF |        |       |             |  |  |  |  |  |  |  |  |

|           | 15         | 14     | 13         | 12    | 11        | 10     | 9     | 8           |  |  |  |  |  |  |  |  |

| PFC3      | 0          | 0      | 0          | 0     | 0         | 0      | PFC39 | PFC38       |  |  |  |  |  |  |  |  |

|           | 7          | 6      | 5          | 4     | 3         | 2      | 1     | 0           |  |  |  |  |  |  |  |  |

|           | 0          | 0      | PFC35      | PFC34 | PFC33     | PFC32  | PFC31 | PFC30       |  |  |  |  |  |  |  |  |

|           | PMC3n      | PFC3n  |            |       | Operatio  | n mode |       |             |  |  |  |  |  |  |  |  |

|           |            |        |            |       |           |        |       |             |  |  |  |  |  |  |  |  |

|           | 0          | ×      | Port I/O m | ode   |           |        |       | UARTA2 mode |  |  |  |  |  |  |  |  |

|           | 0          | ×<br>0 |            |       |           |        |       |             |  |  |  |  |  |  |  |  |

|           |            |        |            | node  |           |        |       |             |  |  |  |  |  |  |  |  |

Figure 16-4. Switching UARTA2 and I<sup>2</sup>C00 Operation Modes

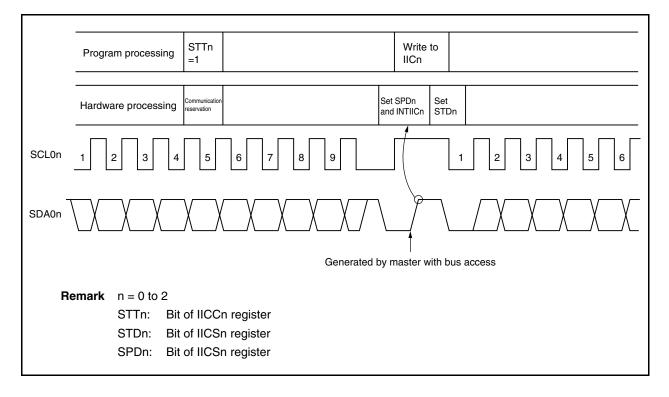

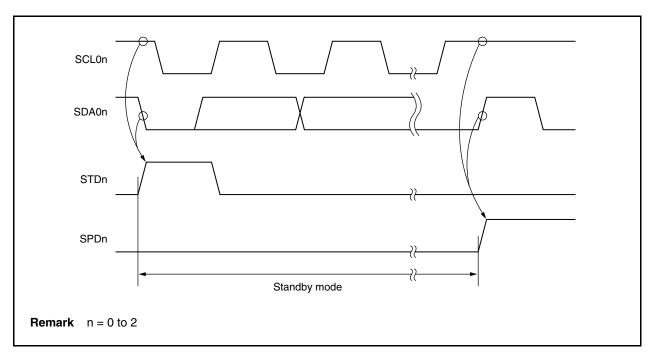

## Figure 19-15. Communication Reservation Timing

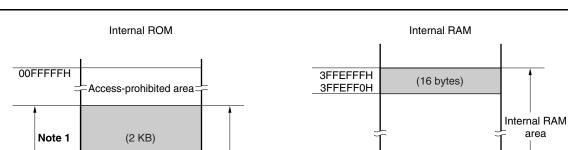

Communication reservations are accepted at the following timing. After the IICSn.STDn bit is set to 1, a communication reservation can be made by setting the IICCn.STTn bit to 1 before a stop condition is detected (n = 0 to 2).

Figure 19-16. Timing for Accepting Communication Reservations

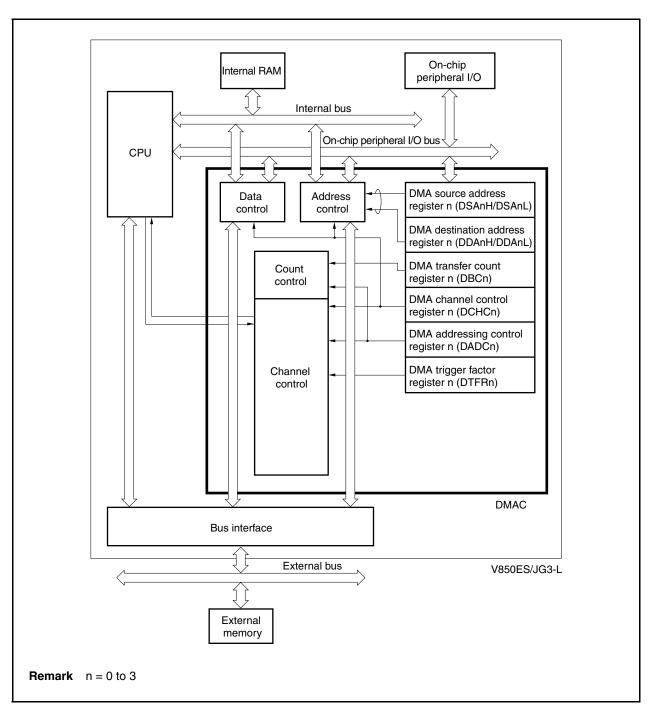

# 20.2 Configuration

The block diagram of the DMAC is shown below.

Figure 20-1. Block Diagram of DMAC

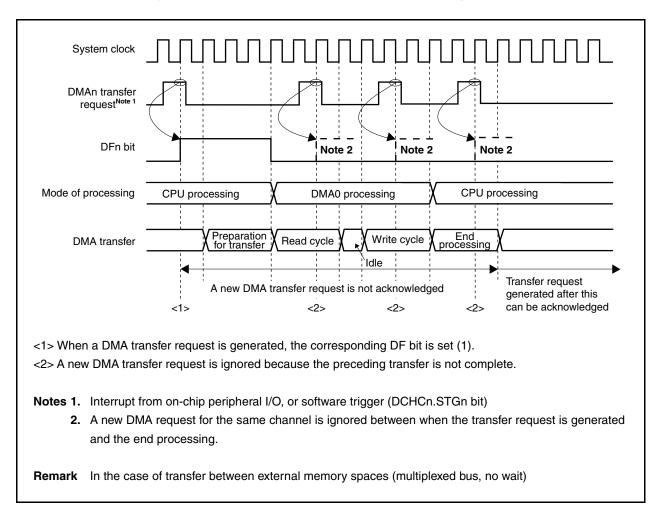

## Figure 20-6. Period in Which DMA Transfer Request Is Ignored (1)

## 27.3 Registers

## (1) CRC input register (CRCIN)

The CRCIN register is an 8-bit register for setting data. This register can be read or written in 8-bit units. Reset sets this register to 00H.

| 7 6 5 4 3 2 1 0 |

|-----------------|

|                 |

## (2) CRC data register (CRCD)

The CRCD register is a 16-bit register that stores the CRC-CCITT operation results. This register can be read or written in 16-bit units. Reset sets this register to 0000H.

- Caution Accessing the CRCD register is prohibited in the following statuses. If a wait cycle is generated, it can only be cleared by a reset. For details, see 3.4.9 (1) Accessing specific onchip peripheral I/O registers.

- When the CPU operates on the subclock and main clock oscillation is stopped

- When the CPU operates on the internal oscillator clock

| After rea | set: 0 | 000H |    | R/W | Ac | ddress | : FF | FFF3 <sup>-</sup> | 12H |   |   |   |   |   |   |   |

|-----------|--------|------|----|-----|----|--------|------|-------------------|-----|---|---|---|---|---|---|---|

|           | 15     | 14   | 13 | 12  | 11 | 10     | 9    | 8                 | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CRCD      |        |      |    |     |    |        |      |                   |     |   |   |   |   |   |   |   |

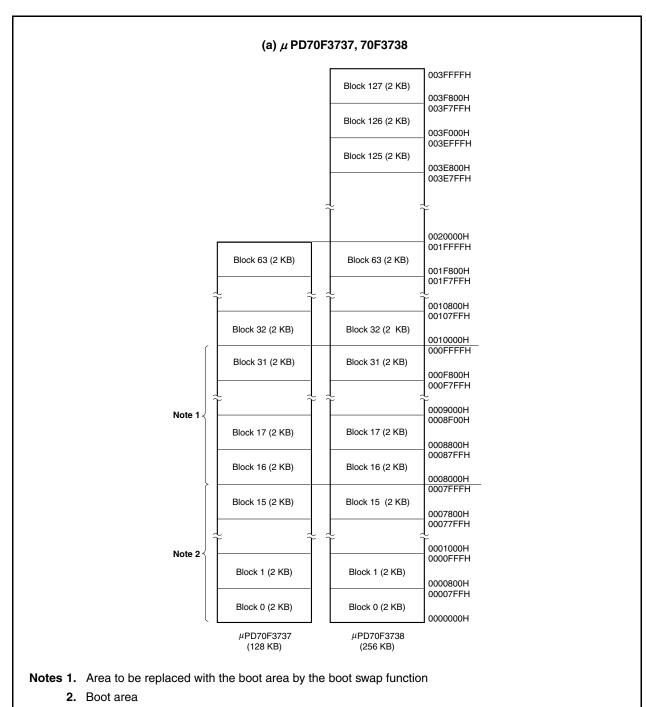

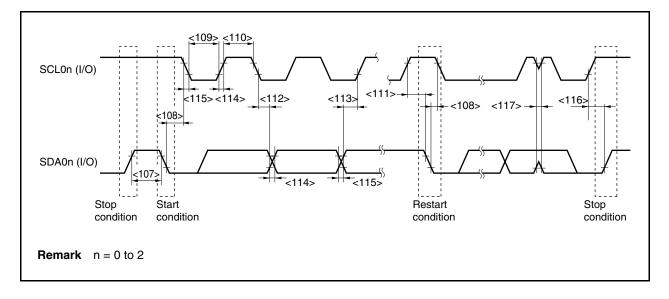

## 30.2 Memory Configuration

The V850ES/JG3-L internal flash memory area is divided into 64 or 96 or 128 blocks and can be erased in block units. All the blocks can also be erased at once.

When the boot swap function is used, the physical memory located at the addresses of blocks 0 to 15 is replaced by the physical memory located at the addresses of blocks 16 to 31. For details of the boot swap function, see **30.5 Rewriting by Self Programming**.

Figure 30-1. Flash Memory Mapping (1/2)

# 31.1.5 Operation

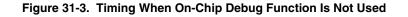

The on-chip debug function is made invalid under the conditions shown in the table below. When this function is not used, keep the  $\overline{\text{DRST}}$  pin low until the OCDM.OCDM0 flag is cleared to 0.

| OCDM0 Flag | 0       | 1       |

|------------|---------|---------|

| DRST Pin   |         |         |

| L          | Invalid | Invalid |

| Н          | Invalid | Valid   |

Remark L: Low-level input

H: High-level input

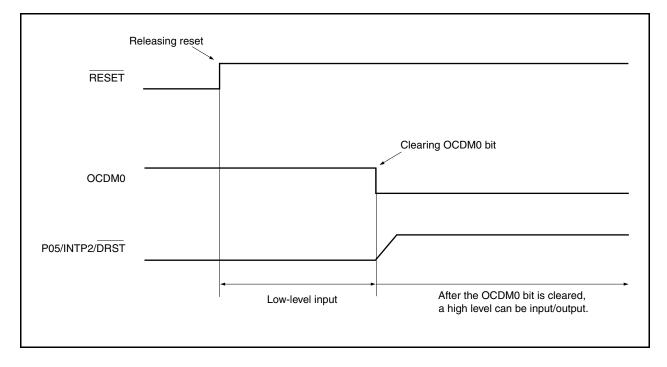

Note 3

Access-prohibited area

: Debugging area

#### Figure 31-5. Memory Spaces Where Debug Monitor Programs Are Allocated

| 00000    | 00H (4 by        | tes)              | -                    |

|----------|------------------|-------------------|----------------------|

| Notes 1. | The address valu | es vary depending | on the product.      |

|          |                  | Internal ROM Size | Address Value        |

|          | UPD70E3737       | 128 KB            | 001E800H to 001EEEEH |

CSI/UART receive

interrupt vector (4 bytes)

Security ID area (10 bytes)

Interrupt vector for debugging

(4 bytes)

Reset vector

0000290HNote 2

0000070H

0000060H

| μPD70F3737 | 128 KB | 001F800H to 001FFFFH |

|------------|--------|----------------------|

| μPD70F3738 | 256 KB | 003F800H to 003FFFFH |

| μPD70F3792 | 384 KB | 005F800H to 005FFFFH |

| μPD70F3793 | 512 KB | 007F800H to 007FFFFH |

Internal ROM area

**2.** This is the address when CSIB0 is used. This value is 00002F0H when CSIB3 is used, and 0000310H when UARTA0 is used.

3. The address values vary depending on the product.

|            | Internal RAM Size | Address Value |  |

|------------|-------------------|---------------|--|

| μPD70F3737 | 8 KB              | 3FFD000H      |  |

| μPD70F3738 | 16 KB             | 3FFB000H      |  |

| μPD70F3792 | 32 KB             | 3FF7000H      |  |

| μPD70F3793 | 40 KB             | 3FF5000H      |  |

938

<R>

# I<sup>2</sup>C Bus Timing

## 33.8.7 A/D converter

| pF)                           |                    |                                          |      |      |                    |      |

|-------------------------------|--------------------|------------------------------------------|------|------|--------------------|------|

| Parameter                     | Symbol             | Conditions                               | MIN. | TYP. | MAX.               | Unit |

| Resolution                    |                    |                                          |      |      | 10                 | bit  |

| Overall error <sup>Note</sup> |                    | $2.7~V \leq AV_{\text{REF0}} \leq 3.6~V$ |      |      | ±0.6               | %FSR |

| A/D conversion time           | <b>t</b> CONV      | $3.0~V \leq AV_{\text{REF0}} \leq 3.6~V$ | 2.6  |      | 24                 | μS   |

|                               |                    | $2.7~V \leq AV_{\text{REF0}} \leq 3.0~V$ | 3.9  |      | 24                 | μs   |

| Zero scale error              |                    |                                          |      |      | ±0.5               | %FSR |

| Full scale error              |                    |                                          |      |      | ±0.5               | %FSR |

| Non-linearity error           |                    |                                          |      |      | ±4.0               | LSB  |

| Differential linearity error  |                    |                                          |      |      | ±4.0               | LSB  |

| Analog input voltage          | VIAN               |                                          | AVss |      | AV <sub>REF0</sub> | v    |

| Reference voltage             | AV <sub>REF0</sub> |                                          | 2.7  |      | 3.6                | V    |

| AVREFO current                | AIREFO             | Normal conversion mode                   |      | 3    | 6.5                | mA   |

|                               |                    | High-speed conversion mode               |      | 4    | 10                 | mA   |

|                               |                    | When A/D converter unused                |      |      | 5                  | μA   |

| (TA = -40 to +85°C, VDD = EVDD = AVREF0 = AVREF1, 2.7 V ≤ AVREF0 = AVREF1 ≤ 3.6 V, VSS = EVSS = AVSS = 0 V, CL = 50 |  |

|---------------------------------------------------------------------------------------------------------------------|--|

| pF)                                                                                                                 |  |

**Note** Excluding quantization error (±0.05 %FSR).

Caution Do not set (read/write) alternate-function ports during A/D conversion; otherwise the conversion resolution may be degraded.

Remark LSB: Least Significant Bit FSR: Full Scale Range

| Major Difference                     |                      | μ PD70F3792 | μ PD70F3793                 | μ PD70F3737 | μ PD70F3738                 |        |  |

|--------------------------------------|----------------------|-------------|-----------------------------|-------------|-----------------------------|--------|--|

| Internal                             | Flash mem            | ory         | 384 KB                      | 512 KB      | 128 KB                      | 256 KB |  |

| memory                               | RAM                  |             | 32 KB                       | 40 KB       | 8 KB                        | 16 KB  |  |

| Port number                          |                      | 83          |                             | 84          |                             |        |  |

| Interrupt<br>request signal          | Interrupt number     |             | 64 (External interrupt : 9) |             | 57 (External interrupt : 9) |        |  |

|                                      | RTC INTRTC0          |             | Available                   |             | None                        |        |  |

|                                      |                      | INTRCT1     | Available                   |             | None                        |        |  |

|                                      |                      | INTRTC2     | Available                   |             | None                        |        |  |

|                                      | UARTA3               | INTTUA3R    | Available                   |             | None                        |        |  |

|                                      |                      | INTTUA3T    | Available                   |             | None                        |        |  |

|                                      | UARTA4               | INTTUA4R    | Available                   |             | None                        |        |  |

|                                      |                      | INTTUA4T    | Available                   |             | None                        |        |  |

|                                      | UARTA5               | INTTUA5R    | Available                   |             | None                        |        |  |

|                                      |                      | INTTUA5T    | Available                   |             | None                        |        |  |

|                                      | UARTC1               | INTTUC1R    | Available                   |             | None                        |        |  |

|                                      |                      | INTTUC1T    | Available                   |             | None                        |        |  |

| RTC                                  |                      | Available   |                             | None        |                             |        |  |

| RTC backup mode                      |                      | Available   |                             | None        |                             |        |  |

| UARTA                                |                      | 6 channels  |                             | 3 channels  |                             |        |  |

| UARTC                                |                      | Available   |                             | None        |                             |        |  |

| DMA Start                            | INTRTC1              |             | Available                   |             | None                        |        |  |

| Factors                              | INTUA3R              |             | Available                   |             | None                        |        |  |

|                                      | INTUA3T              |             | Available                   |             | None                        |        |  |

|                                      | INTUA4R              |             | Available                   |             | None                        |        |  |

|                                      | INTUA4T              |             | Available                   |             | None                        |        |  |

|                                      | INTUA5R              |             | Available                   |             | None                        |        |  |

|                                      | INTUA5T              |             | Available                   |             | None                        |        |  |

| LVI detection level                  |                      | 3 levels    |                             | 2 levels    |                             |        |  |

| Package                              | 100-pinQFP (14x20)   |             | None                        |             | Available                   |        |  |

| Operation<br>power supply<br>voltage | 2.0 to 3.6 V@2.5 MHz |             | Available                   |             | None                        |        |  |

| Table B-3. | Major Differences Between V850ES/JG3-L Products |

|------------|-------------------------------------------------|