Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 20MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 83                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 40K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                            |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3793gc-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (7) Port 0 function register (PF0)

|     |      | 6            | 5            | 4           | 3            | 2            | 1            | 0            |

|-----|------|--------------|--------------|-------------|--------------|--------------|--------------|--------------|

| PF0 | 0    | PF06         | PF05         | PF04        | PF03         | PF02         | 0            | 0            |

|     |      |              |              |             |              |              |              |              |

|     | PF0n | Specificatio | n of normal  | output (CMC | S output) or | r N-ch open- | drain output | (n = 2 to 6) |

| Γ   | 0    | Normal ou    | utput (CMO   | S output)   |              |              |              |              |

|     | 1    | N-ch oper    | n-drain outp | out         |              |              |              |              |

# (7) Port 3 function register (PF3)

| After re              | set: 0000H             | H R/W        | Address               | PF3 FFFI<br>PF3L FFI        | FC66H,<br>FFC66H,      | PF3H FFF    | FFC67H       |                                         |

|-----------------------|------------------------|--------------|-----------------------|-----------------------------|------------------------|-------------|--------------|-----------------------------------------|

|                       | 15                     | 14           | 13                    | 12                          | 11                     | 10          | 9            | 8                                       |

| PF3 (PF3H)            | 0                      | 0            | 0                     | 0                           | 0                      | 0           | PF39         | PF38                                    |

|                       | 7                      | 6            | 5                     | 4                           | 3                      | 2           | 1            | 0                                       |

| (PF3L)                | PF37                   | PF36         | PF35                  | PF34                        | PF33                   | PF32        | PF31         | PF30                                    |

|                       | PF3n                   | Specificatio | n of normal           | output (CMC                 | S output) or           | N-ch open-  | drain output | t (n = 0 to 9)                          |

|                       |                        |              |                       | • •                         | S output) or           | N-ch open-  | drain output | t (n = 0 to 9)                          |

|                       | 0                      | Normal ou    | itput (CMO            | S output)                   |                        |             |              |                                         |

|                       | 1                      | N-ch oper    | i-drain outp          | out                         |                        |             |              |                                         |

| Remarks 1. The<br>How | PF3 regis<br>ever, whe | ter can be   | read or w<br>higher 8 | ritten in 10<br>bits of the | 6-bit units<br>PF3 reg | ister as th | ne PF3H r    | F3n bit to 1.<br>register and t<br>its. |

| 0 614                 |                        |              |                       |                             |                        |             |              |                                         |

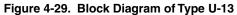

### (b) 8-bit data bus width (1/2)

32-bit data is transmitted/received via an 8-bit bus. Therefore, the data is transmitted/received in four accesses. The data is transmitted/received to/from the specified even/odd address of the external data bus.

# 7.3 Registers

The registers that control TMPn are as follows.

- TMPn control register 0 (TPnCTL0)

- TMPn control register 1 (TPnCTL1)

- TMPn I/O control register 0 (TPnIOC0)

- TMPn I/O control register 1 (TPnIOC1)

- TMPn I/O control register 2 (TPnIOC2)

- TMPn option register 0 (TPnOPT0)

- TMPn capture/compare register 0 (TPnCCR0)

- TMPn capture/compare register 1 (TPnCCR1)

- TMPn counter read buffer register (TPnCNT)

Remarks 1. When using the functions of the TIPn0, TIPn1, TOPn0, and TOPn1 pins, see Table 4-15 Settings When Pins Are Used for Alternate Functions.

**2.** n = 0 to 5

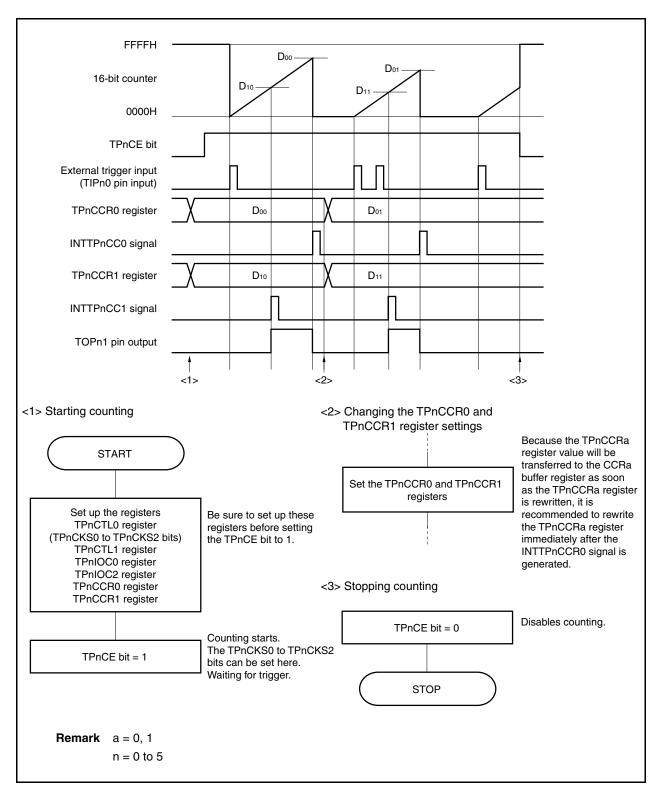

### (1) Operations in one-shot pulse output mode

# Figure 7-41. Timing and Processing of Operations in One-Shot Pulse Output Mode

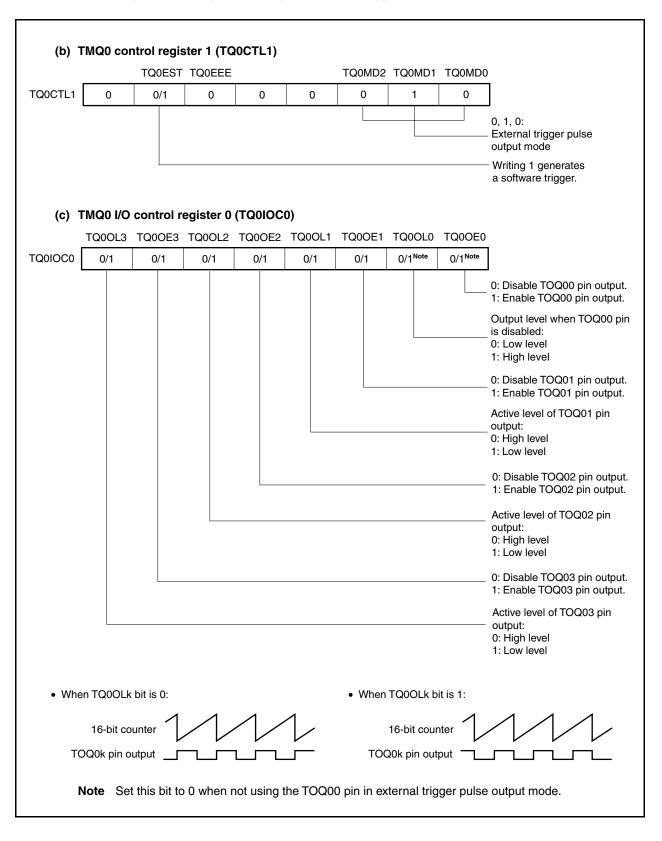

#### Figure 8-28. Register Settings in External Trigger Pulse Output Mode (2/3)

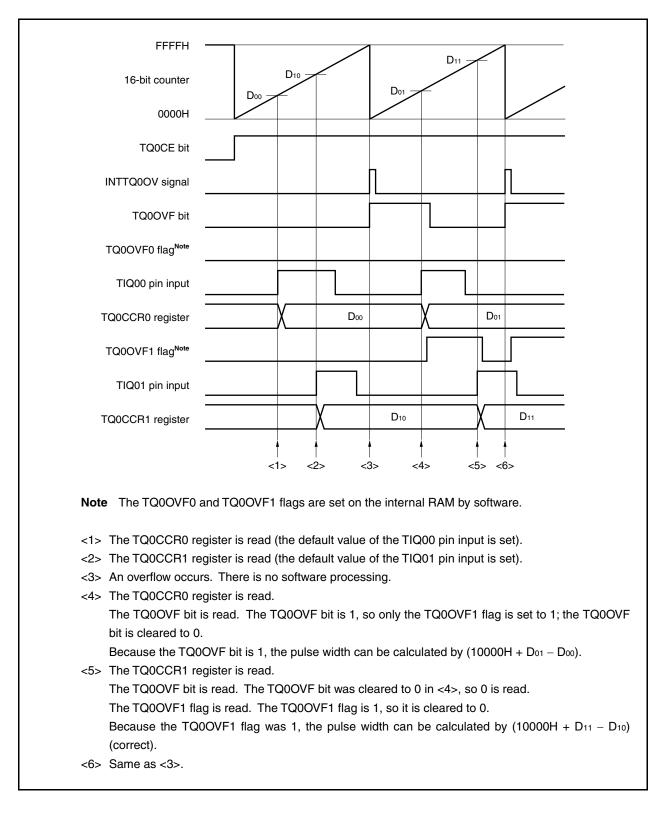

# Figure 8-62. Example of Resolving Problem When Two or More Capture Registers Are Used Without Using Overflow Interrupt

# 11.2 Configuration

The real-time counter includes the following hardware.

| Item              | Configuration                                 |

|-------------------|-----------------------------------------------|

| Control registers | Real-time counter control register 0 (RC1CC0) |

|                   | Real-time counter control register 1 (RC1CC1) |

|                   | Real-time counter control register 2 (RC1CC2) |

|                   | Real-time counter control register 3 (RC1CC3) |

|                   | Sub-count register (RC1SUBC)                  |

|                   | Second count register (RC1SEC)                |

|                   | Minute count register (RC1MIN)                |

|                   | Hour count register (RC1HOUR)                 |

|                   | Day count register (RC1DAY)                   |

|                   | Day-of-week count register (RC1WEEK)          |

|                   | Month count register (RC1MONTH)               |

|                   | Year count register (RC1YEAR)                 |

|                   | Watch error correction register (RC1SUBU)     |

|                   | Alarm minute register (RC1ALM)                |

|                   | Alarm hour register (RC1ALH)                  |

|                   | Alarm week register (RC1ALW)                  |

|                   | Prescaler mode register 0 (PRSM0)             |

|                   | Prescaler compare register 0 (PRSCM0)         |

| Table 11-1. Con | figuration of | Real-Time | Counter |

|-----------------|---------------|-----------|---------|

|-----------------|---------------|-----------|---------|

## (13) Watch error correction register (RC1SUBU)

The RC1SUBU register can be used to correct the watch with high accuracy when the watch is early or late, by changing the value (reference value: 7FFFH) overflowing from the sub-count register (RSUBC) to the second counter register.

This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

- **Remarks 1.** The RC1SUBU register can be rewritten only when the real-time counter is set to its initial values. Be sure to see **11.4.1 Initial settings**.

- 2. See 11.4.9 Watch error correction example of real-time counter for details of watch error correction.

|         | 7                     | 6                        | 5                            | 4                         | 3                                          | 2            | 1            | 0        |

|---------|-----------------------|--------------------------|------------------------------|---------------------------|--------------------------------------------|--------------|--------------|----------|

| RC1SUBU | DEV                   | F6                       | F5                           | F4                        | F3                                         | F2           | F1           | F0       |

|         |                       |                          |                              |                           |                                            |              |              |          |

|         | DEV                   |                          | Se                           | tting of wat              | ch error co                                | rrection tin | ning         |          |

|         | 0                     |                          | watch error<br>ds (every 2   |                           | ISEC (sec                                  | ond counte   | er) is at 00 | , 20, or |

|         | 1                     |                          | watch error<br>seconds).     | s when RC                 | 1SEC (sec                                  | ond counte   | er) is at 00 | seconds  |

|         |                       | 1                        |                              |                           |                                            |              |              |          |

|         | F6                    |                          | Se                           | etting of wa              | tch error co                               | prrection va | lue          |          |

|         | 0                     | F0 bits (p<br>Expression | ositive corr<br>on for calcu | ection).<br>lating incre  | nt value by<br>ment value<br>F0 bits – 1   | :            | et using th  | ne F5 to |

|         | 1                     | F0 bits (n<br>Expressio  | egative cor<br>on for calcu  | rection).<br>lating decre | int value by<br>ement value<br>ng value of | e:           | Ū            |          |

|         | If the F6<br>performe | to F0 bit val            | ues are {1/                  | 0, 0, 0, 0, 0             | ), 0, 1/0}, w                              | atch error   | correction   | is not   |

If the ADA0M0, ADA0M2, ADA0S, ADA0PFM, or ADA0PFT register is written during conversion, the conversion is aborted, and the A/D converter waits for the trigger again. However, writing to these registers is prohibited in the one-shot select mode/one-shot scan mode (n = 0 to 11).

Caution When selecting the external trigger mode, set the high-speed conversion mode. Do not input a trigger during the stabilization time that is inserted once after A/D conversion is enabled (ADA0M0.ADA0CE bit = 1).

**Remark** The trigger standby status means the status after the stabilization time has passed.

#### (3) Timer trigger mode

In this mode, converting the signal of the analog input pin (ANI0 to ANI11) specified by the ADA0S register is started by the compare match interrupt request signal (INTTP2CC0 or INTTP2CC1) of the capture/compare register connected to the timer. The INTTP2CC0 or INTTP2CC1 signal is selected by the ADA0TMD1 and ADA0TMD0 bits, and conversion is started at the rising edge of the specified compare match interrupt request signal. When the ADA0CE bit is set to 1, the A/D converter waits for a trigger, and starts conversion when the compare match interrupt request signal of the timer is input.

When conversion is completed, regardless of whether the continuous select, continuous scan, one-shot select, or one-shot scan mode is set as the operation mode by the ADA0MD1 and ADA0MD0 bits, the result of the conversion is stored in the ADA0CRn register. At the same time, the INTAD signal is generated, and the A/D converter waits for the trigger again.

When conversion is started, the ADA0EF bit is set to 1 (indicating that conversion is in progress). While the A/D converter is waiting for the trigger, however, the ADA0EF bit is cleared to 0 (indicating that conversion is stopped). If a valid trigger is input during conversion, the conversion is aborted and started again from the beginning.

If the ADA0M0, ADA0M2, ADA0S, ADA0PFM, or ADA0PFT register is written during conversion, the conversion is stopped and the A/D converter waits for the trigger again. However, writing to these registers is prohibited in the one-shot select mode/one-shot scan mode.

Caution When selecting the timer trigger mode, set the high-speed conversion mode. Do not input a trigger during the stabilization time that is inserted once after A/D conversion is enabled (ADA0M0.ADA0CE bit = 1).

**Remark** The trigger standby status means the status after the stabilization time has passed.

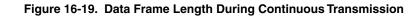

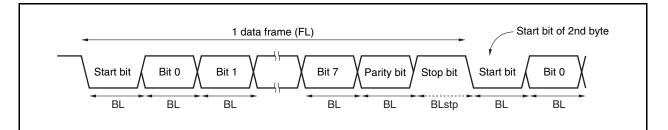

### (6) Data frame length during continuous transmission

In continuous transmission, the data frame length from the stop bit to the next start bit is 2 base clock cycles longer than usual. However, timing initialization is performed via start bit detection by the receiving side, so this has no influence on the transfer result.

Assuming a 1 bit data length of BL; a stop bit length of BLstp; and a base clock frequency of fuclk, we obtain the following equation.

BLstp = BL + 2/fuclk

Therefore, the transfer rate during continuous transmission is as follows.

Data frame length =  $11 \times BL + (2/fuclk)$

(3/3)

| 0                           | Communication start trigger invalid                                                      |

|-----------------------------|------------------------------------------------------------------------------------------|

| 1                           |                                                                                          |

|                             | Communication start trigger valid                                                        |

| This bit e                  | nables or disables the communication start trigger in reception mode.                    |

| <ul> <li>In mast</li> </ul> |                                                                                          |

| (a) In s                    | single transmission or transmission/reception mode, or continuous                        |

| . ,                         | nsmission or continuous transmission/reception mode:                                     |

|                             | e setting of the CBnSCE bit has no effect on communication.                              |

| (b) In ៖                    | single reception mode:                                                                   |

| Cle                         | ar the CBnSCE bit to 0 before reading the last receive data to disable the               |

| sta                         | rt of reception because reception is started by reading the receive data                 |

| (CE                         | BnRX register) <sup>Note 1</sup> .                                                       |

|                             | continuous reception mode                                                                |

| Cle                         | ar the CBnSCE bit to 0 one communication clock cycle before reception of                 |

| the                         | last data is completed to disable the start of reception after the last data is          |

| rec                         | eived <sup>Note 2</sup> .                                                                |

| • In slave                  | e mode                                                                                   |

| Set the                     | CBnSCE bit to 1.                                                                         |

|                             |                                                                                          |

|                             | f CBnSCE bit]                                                                            |

| -                           | e reception mode                                                                         |

|                             | en reception of the last data is completed by INTCBnR interrupt                          |

|                             | vicing, clear the CBnSCE bit to 0 before reading the CBnRX register.                     |

|                             | er confirming that the CBnSTR.CBnTSF bit is 0, clear the CBnPWR and                      |

|                             | nRXE bits to 0 to disable reception.                                                     |

|                             | receive data again, set the CBnSCE bit to 1 to start the next reception                  |

| •                           | dummy-reading the CBnRX register.                                                        |

|                             | nuous reception mode                                                                     |

|                             | ear the CBnSCE bit to 0 in the INTCBnR interrupt servicing for the receive               |

|                             | a immediately before the last one.                                                       |

|                             | ad the CBnRX register.<br>ad the last reception data by reading the CBnRX register after |

|                             | mowledging the CBnTIR interrupt.                                                         |

|                             | er confirming that the CBnSTR.CBnTSF bit is 0, clear the CBnPWR and                      |

|                             | nRXE bits to 0 to disable reception.                                                     |

|                             | receive data again, set the CBnSCE bit to 1 to wait for the next reception               |

|                             |                                                                                          |

|                             | dummy-reading the CBnRX register.                                                        |

| Notes 1.                    | If the CBnRX register is read with the CBnSCE bit set to 1, the                          |

|                             | next communication is started.                                                           |

| 2.                          | If the CBnSCE bit is not cleared to 0, one communication close                           |

|                             | cycle before reception of the last data is completed, the ne                             |

|                             | communication is automatically started.                                                  |

|                             | sommanioution to automationly started.                                                   |

| After reset: ( | )0H                                                                                                                                                                                                                                                                                                                                                             | R/W <sup>Note</sup>                   | Addres                                                         | s: IICF0 FFF                            | FFD8AH                 | , IICF1 FFFFE                                              | 09AH, IICF2 F                      | FFFDAAH                                                                                                      |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------|-----------------------------------------|------------------------|------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                | <7>                                                                                                                                                                                                                                                                                                                                                             | <6>                                   | 5                                                              | 4                                       | 3                      | 2                                                          | <1>                                | <0>                                                                                                          |  |  |  |  |

| llCFn          | STCFn                                                                                                                                                                                                                                                                                                                                                           | llCBSYn                               | 0                                                              | 0                                       | 0                      | 0                                                          | STCENn                             | IICRSVn                                                                                                      |  |  |  |  |

| = 0 to 2)      |                                                                                                                                                                                                                                                                                                                                                                 |                                       |                                                                |                                         |                        |                                                            |                                    |                                                                                                              |  |  |  |  |

|                | STCFn                                                                                                                                                                                                                                                                                                                                                           |                                       | STTn bit clear                                                 |                                         |                        |                                                            |                                    |                                                                                                              |  |  |  |  |

|                | 0                                                                                                                                                                                                                                                                                                                                                               | Start condit                          | tion issued                                                    |                                         |                        |                                                            |                                    |                                                                                                              |  |  |  |  |

|                | 1                                                                                                                                                                                                                                                                                                                                                               | Start condit                          | tion cannot                                                    | be issued, S                            | TTn bit cl             | eared                                                      |                                    |                                                                                                              |  |  |  |  |

|                | Condition                                                                                                                                                                                                                                                                                                                                                       | for clearing (S                       | clearing (STCFn bit = 0) Condition for setting (STCFn bit = 1) |                                         |                        |                                                            |                                    |                                                                                                              |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                 | by IICCn.STT<br>e IICCn.IICEr<br>et   |                                                                |                                         |                        | cleared to 0                                               |                                    | t issued and STTn flag is<br>inication reservation is                                                        |  |  |  |  |

|                | llCBSYn                                                                                                                                                                                                                                                                                                                                                         |                                       |                                                                |                                         | l <sup>2</sup> C       | COn bus status                                             |                                    |                                                                                                              |  |  |  |  |

|                | 0                                                                                                                                                                                                                                                                                                                                                               | Bus release                           | ed status (d                                                   | efault comm                             | unication              | status when S                                              | FCENn bit = 1)                     |                                                                                                              |  |  |  |  |

|                | 1                                                                                                                                                                                                                                                                                                                                                               |                                       | ,                                                              |                                         |                        | cation status w                                            | ,                                  |                                                                                                              |  |  |  |  |

|                | Condition                                                                                                                                                                                                                                                                                                                                                       | for clearing (I                       | ICBSYn bit                                                     | = 0)                                    |                        | Condition for                                              | setting (IICBS)                    | Yn bit = 1)                                                                                                  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                 | op condition i<br>e IICEn bit =<br>et |                                                                |                                         |                        |                                                            | condition is de<br>ne IICEn bit wh | tected<br>en the STCENn bit = 0                                                                              |  |  |  |  |

|                | STCENn                                                                                                                                                                                                                                                                                                                                                          |                                       |                                                                |                                         | Initial                | al start enable trigger                                    |                                    |                                                                                                              |  |  |  |  |

|                | 0                                                                                                                                                                                                                                                                                                                                                               | Start condit<br>(IICEn bit =          |                                                                | t be generate                           | ed until a             | stop condition i                                           | s detected foll                    | owing operation enable                                                                                       |  |  |  |  |

|                | 1                                                                                                                                                                                                                                                                                                                                                               | Start condit<br>(IICEn bit =          |                                                                | e generated o                           | even if a s            | en if a stop condition is not detected following operation |                                    |                                                                                                              |  |  |  |  |

|                | Condition                                                                                                                                                                                                                                                                                                                                                       | for clearing (S                       | STCENn bit                                                     | = 0)                                    |                        | Condition for setting (STCENn bit = 1)                     |                                    |                                                                                                              |  |  |  |  |

|                | <ul><li>When state</li><li>After res</li></ul>                                                                                                                                                                                                                                                                                                                  |                                       | ondition is detected     Setting by instruction                |                                         |                        |                                                            |                                    |                                                                                                              |  |  |  |  |

|                | llCRSVn                                                                                                                                                                                                                                                                                                                                                         |                                       |                                                                | Commu                                   | inication r            | eservation func                                            | tion disable bi                    | t                                                                                                            |  |  |  |  |

|                | 0                                                                                                                                                                                                                                                                                                                                                               | Communic                              | ation reserv                                                   | ation enable                            | ed                     |                                                            |                                    |                                                                                                              |  |  |  |  |

|                | 1                                                                                                                                                                                                                                                                                                                                                               | Communic                              | ation reserv                                                   | ation disable                           | əd                     |                                                            |                                    |                                                                                                              |  |  |  |  |

|                | Condition                                                                                                                                                                                                                                                                                                                                                       | for clearing (I                       | ICRSVn bit                                                     | = 0)                                    |                        | Condition for                                              | setting (IICRS                     | Vn bit = 1)                                                                                                  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                 |                                       | n                                                              |                                         |                        | <ul> <li>Setting by ir</li> </ul>                          | nstruction                         |                                                                                                              |  |  |  |  |

|                | Condition for clearing (IICRSVn bit = 0)       Condition for setting (IICRSVn bit = 1)         • Clearing by instruction       • Setting by instruction         • After reset       • Setting by instruction         Note       Bits 6 and 7 are read-only bits.         Cautions       1. Write the STCENn bit only when operation is stopped (IICEn bit = 0). |                                       |                                                                |                                         |                        |                                                            |                                    |                                                                                                              |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                 | regardl<br>enableo<br>to con          | ess of th<br>d. Theref                                         | e actual b<br>ore, to issu<br>t the bus | ous state<br>ue the fi | us immediat<br>rst start con                               | ely after the<br>dition (STTr      | 'n bit = 0) is recogni<br>e I <sup>2</sup> Cn bus operation<br>n bit = 1), it is necess<br>to not disturb of |  |  |  |  |

3. Write the IICRSVn bit only when operation is stopped (IICEn bit = 0).

| Table 19-2. | Clock Settings | \$ (2/2) |

|-------------|----------------|----------|

|-------------|----------------|----------|

| IICXm |            | IICCLm   |       | Selection Clock                                                                                                                                     | Transfer | Settable Main Clock                                      | Operating       |

|-------|------------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------|-----------------|

| Bit 0 | Bit 3      | Bit 1    | Bit 0 |                                                                                                                                                     | Clock    | Frequency (fxx) Range                                    | Mode            |

| CLXm  | SMCm       | CLm1     | CLm0  |                                                                                                                                                     |          |                                                          |                 |

| 0     | 0          | 0        | 0     | fxx (when OCKS1 = 18H set)                                                                                                                          | fxx/44   | $2.50 \text{ MHz} \leq \text{fxx} \leq 4.19 \text{ MHz}$ | Standard        |

|       |            |          |       | fxx/2 (when OCKS1 = 10H set)                                                                                                                        | fxx/88   | $4.00 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   | mode            |

|       |            |          |       | fxx/3 (when OCKS1 = 11H set)                                                                                                                        | fxx/132  | 6.00 MHz ≤ fxx ≤ 12.57 MHz                               | (SMCm bit = 0)  |

|       |            |          |       | fxx/4 (when OCKS1 = 12H set)                                                                                                                        | fxx/176  | 8.00 MHz ≤ fxx ≤ 16.76 MHz                               |                 |

|       |            |          |       | fxx/5 (when OCKS1 = 13H set)                                                                                                                        | fxx/220  | 10.00 MHz ≤ fxx ≤ 20.00 MHz                              |                 |

| 0     | 0          | 0        | 1     | fxx (when OCKS1 = 18H set)                                                                                                                          | fxx/86   | $4.19 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   |                 |

|       |            |          |       | fxx/2 (when OCKS1 = 10H set)                                                                                                                        | fxx/172  | 8.38 MHz ≤ fxx ≤ 16.76 MHz                               |                 |

|       |            |          |       | fxx/3 (when OCKS1 = 11H set)                                                                                                                        | fxx/258  | 12.57 MHz $\leq$ fxx $\leq$ 20.00 MHz                    |                 |

|       |            |          |       | fxx/4 (when OCKS1 = 12H set)                                                                                                                        | fxx/344  | 16.76 MHz ≤ fxx ≤ 20.00 MHz                              |                 |

| 0     | 0          | 1        | 0     | fxx <sup>Note</sup>                                                                                                                                 | fxx/86   | $4.19 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   |                 |

| 0     | 0          | 1        | 1     | fxx (when OCKS1 = 18H set)                                                                                                                          | fxx/66   | fxx = 6.40 MHz                                           |                 |

|       |            |          |       | fxx/2 (when OCKS1 = 10H set)         fxx/132         fxx = 12.80 MHz           fxx/3 (when OCKS1 = 11H set)         fxx/198         fxx = 19.20 MHz |          |                                                          |                 |

|       |            |          |       |                                                                                                                                                     |          | fxx = 19.20 MHz                                          |                 |

| 0     | 1          | 0        | ×     | fxx (when OCKS1 = 18H set)                                                                                                                          | fxx/24   | $4.19 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   | High-speed      |

|       |            |          |       | fxx/2 (when OCKS1 = 10H set)                                                                                                                        | fxx/48   | 8.00 MHz $\leq$ fxx $\leq$ 16.76 MHz                     | mode            |

|       |            |          |       | fxx/3 (when OCKS1 = 11H set)                                                                                                                        | fxx/72   | 12.00 MHz $\leq$ fxx $\leq$ 20.00 MHz                    | - (SMCm bit = 1 |

|       |            |          |       | fxx/4 (when OCKS1 = 12H set)                                                                                                                        | fxx/96   | 16.00 MHz $\leq$ fxx $\leq$ 20.00 MHz                    |                 |

| 0     | 1          | 1        | 0     | fxx <sup>Note</sup>                                                                                                                                 | fxx/24   | $4.00 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   |                 |

| 0     | 1          | 1        | 1     | fxx (when OCKS1 = 18H set)                                                                                                                          | fxx/18   | fxx = 6.40 MHz                                           |                 |

|       |            |          |       | fxx/2 (when OCKS1 = 10H set)                                                                                                                        | fxx/36   | fxx = 12.80 MHz                                          |                 |

|       |            |          |       | fxx/3 (when OCKS1 = 11H set)                                                                                                                        | fxx/54   | fxx = 19.20 MHz                                          |                 |

| 1     | 1          | 0        | ×     | fxx (when OCKS1 = 18H set)                                                                                                                          | fxx/12   | $4.00 \text{ MHz} \le f_{XX} \le 4.19 \text{ MHz}$       |                 |

|       |            |          |       | fxx/2 (when OCKS1 = 10H set)                                                                                                                        | fxx/24   | $8.00 \text{ MHz} \le \text{fxx} \le 8.38 \text{ MHz}$   |                 |

|       |            |          |       | fxx/3 (when OCKS1 = 11H set)                                                                                                                        | fxx/36   | 12.00 MHz $\leq$ fxx $\leq$ 12.57 MHz                    |                 |

|       |            |          |       | fxx/4 (when OCKS1 = 12H set)                                                                                                                        | fxx/48   | 16.00 MHz ≤ fxx ≤ 16.67 MHz                              | ]               |

|       |            |          |       | fxx/5 (when OCKS1 = 13H set)                                                                                                                        | fxx/60   | fxx = 20.00 MHz                                          | 1               |

| 1     | 1          | 1        | 0     | fxx <sup>Note</sup>                                                                                                                                 | fxx/12   | $4.00 \text{ MHz} \le \text{fxx} \le 4.19 \text{ MHz}$   | 1               |

|       | Other that | an above | 9     | Setting prohibited                                                                                                                                  | -        | -                                                        | -               |

**Note** Since the selection clock is fxx regardless of the value set to the OCKS1 register, clear the OCKS1 register to 00H (I<sup>2</sup>C division clock stopped status).

**Remarks 1.** m = 1, 2

**2.**  $\times$ : don't care

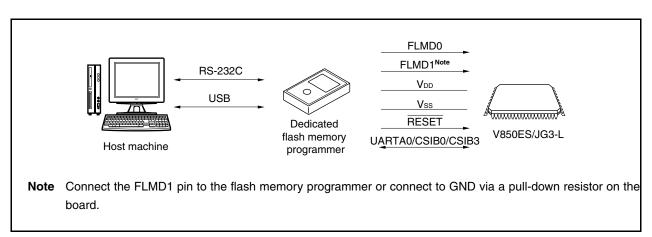

# 30.4 Rewriting by Dedicated Flash Memory Programmer

The flash memory can be rewritten by using a dedicated flash memory programmer after the V850ES/JG3-L is mounted on the target system (on-board programming). By combining the dedicated flash memory programmer with a dedicated program adapter (FA series), the flash memory can also be rewritten before the device is mounted on the target system (off-board programming).

#### 30.4.1 Programming environment

The following shows the environment required for writing programs to the flash memory of the V850ES/JG3-L.

Figure 30-2. Environment Required for Writing Programs to Flash Memory

A host machine is required for controlling the dedicated flash memory programmer. In some cases, however, it can be used stand-alone. For details, see the user's manual of the dedicated flash memory programmer.

UARTA0, CSIB0, or CSIB3 is used for the interface between the dedicated flash memory programmer and the V850ES/JG3-L to perform writing, erasing, etc. A dedicated program adapter (FA series) is required for off-board writing.

The following products are recommended:

- FA-70F3738GC-UEU-RX (GC-UEU type) (already wired)

- FA-70F3738GF-GAS-RX (GF-GAS type) (already wired)

- FA-70F3738F1-CAH-RX (F1-CAH type) (already wired)

- <R> <R>

- FA-70F3793GC-UEU-RX (GC-UEU type) (already wired) (Tentative name : Under development)

- FA-70F3793F1-CAH-RX (F1-CAH type) (already wired) (Tentative name : Under development)

- FA-100GC-UEU-B (GC-UEU type) (not wired: wiring required)

- FA-100GF-GAS-B (GF-GAS type) (not wired: wiring required)

Remark The FA series is a product of Naito Densei Machida Mfg. Co., Ltd.

# (a) Seiko Instruments Inc.: Crystal resonator ( $T_A = -40$ to +85°C) Oscillation frequency: fxt = 32.768 kHz

| Туре     | Circuit Example | Part Number | Load Capacitance<br>of Crystal |         | nmended C<br>Constant | ircuit |          | n Voltage<br>nge |

|----------|-----------------|-------------|--------------------------------|---------|-----------------------|--------|----------|------------------|

|          | Resonato        |             | Resonator (pF)                 | C1 (pF) | C2 (pF)               | Rd (Ω) | MIN. (V) | MAX. (V)         |

| Surface  | XT1 XT2         | SP-T2A      | 6                              | 5       | 5                     | 0      | 2.2      | 3.6              |

| mounting | Rd              |             | 12.5                           | 18      | 18                    | 0      | 2.2      | 3.6              |

|          |                 | SSP-T7      | 7                              | 8       | 8                     | 0      | 2.2      | 3.6              |

| Lead     |                 | VT-200      | 6                              | 6       | 6                     | 0      | 2.2      | 3.6              |

|          |                 |             | 12.5                           | 18      | 18                    | 0      | 2.2      | 3.6              |

Caution This oscillator constant is a reference value based on evaluation under a specific environment by the resonator manufacturer.

If optimization of oscillator characteristics is necessary in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit.

The oscillation voltage and oscillation frequency indicate only oscillator characteristics. Use the V850ES/JG3-L so that the internal operating conditions are within the specifications of the AC characteristics, DC characteristics, and operating conditions.

(b) Citizen Miyota Co., Ltd.: Crystal resonator ( $T_A = -40$  to +85°C)

| Туре     | Circuit Example | Part Number | Load Capacitance<br>of Crystal |         | imended C<br>Constant | ircuit |          | n Voltage<br>nge |

|----------|-----------------|-------------|--------------------------------|---------|-----------------------|--------|----------|------------------|

|          | Re              |             | Resonator (pF)                 | C1 (pF) | C2 (pF)               | Rd (Ω) | MIN. (V) | MAX. (V)         |

| Surface  | XT1 XT2         | CM200S      | 9                              | 12      | 12                    | 100    | 2.2      | 3.6              |

| mounting | ≷Rd             | CMR200T     | 9                              | 12      | 12                    | 100    | 2.2      | 3.6              |

|          |                 | CM519       | 9                              | 12      | 12                    | 100    | 2.2      | 3.6              |

| Lead     |                 | CM315       | 9                              | 12      | 12                    | 100    | 2.2      | 3.6              |

|          |                 | CFS-206     | 9                              | 12      | 12                    | 100    | 2.2      | 3.6              |

## Oscillation frequency: fxT = 32.768 kHz

Caution This oscillator constant is a reference value based on evaluation under a specific environment by the resonator manufacturer.

If optimization of oscillator characteristics is necessary in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit.

The oscillation voltage and oscillation frequency indicate only oscillator characteristics. Use the V850ES/JG3-L so that the internal operating conditions are within the specifications of the AC characteristics, DC characteristics, and operating conditions.

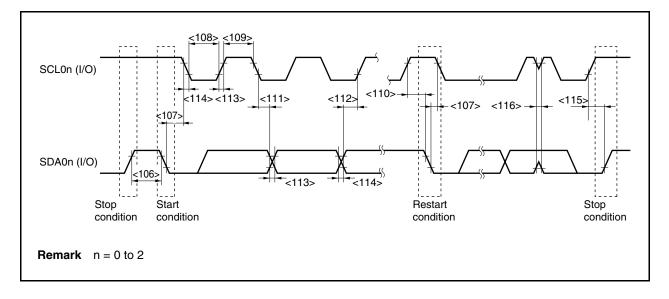

# I<sup>2</sup>C Bus Timing

# 32.8.7 A/D converter

| Parameter                     | Symbol             | Conditions                               | MIN. | TYP. | MAX.               | Unit |

|-------------------------------|--------------------|------------------------------------------|------|------|--------------------|------|

| Resolution                    |                    |                                          |      |      | 10                 | bit  |

| Overall error <sup>Note</sup> |                    | $2.7~V \leq AV_{\text{REF0}} \leq 3.6~V$ |      |      | ±0.6               | %FSR |

| A/D conversion time           | <b>t</b> CONV      | $3.0~V \leq AV_{\text{REF0}} \leq 3.6~V$ | 2.6  |      | 24                 | μs   |

|                               |                    | $2.7~V \leq AV_{\text{REF0}} \leq 3.0~V$ | 3.9  |      | 24                 | μs   |

| Zero scale error              |                    |                                          |      |      | ±0.5               | %FSR |

| Full scale error              |                    |                                          |      |      | ±0.5               | %FSR |

| Non-linearity error           |                    |                                          |      |      | ±4.0               | LSB  |

| Differential linearity error  |                    |                                          |      |      | ±4.0               | LSB  |

| Analog input voltage          | VIAN               |                                          | AVss |      | AV <sub>REF0</sub> | V    |

| Reference voltage             | AV <sub>REF0</sub> |                                          | 2.7  |      | 3.6                | V    |

| AVREF0 current                | AIREFO             | Normal conversion mode                   |      | 3    | 6.5                | mA   |

|                               |                    | High-speed conversion mode               |      | 4    | 10                 | mA   |

|                               |                    | When A/D converter unused                |      |      | 5                  | μA   |

| $(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{V}_{DD} = \text{EV}_{DD} = \text{AV}_{\text{REF0}} = \text{AV}_{\text{REF1}}, 2.7 \text{ V} \le \text{AV}_{\text{REF0}} = \text{AV}_{\text{REF1}} \le 3.6 \text{ V}, \text{V}_{\text{SS}} = \text{EV}_{\text{SS}} = \text{AV}_{\text{SS}} = 0 \text{ V}, \text{CL} = 50 \text{ V}, \text$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

**Note** Excluding quantization error (±0.05 %FSR).

Caution Do not set (read/write) alternate-function ports during A/D conversion; otherwise the conversion resolution may be degraded.

Remark LSB: Least Significant Bit FSR: Full Scale Range

#### 33.8.10 RTC back-up mode characteristics

## (1) VDD Power-down timing

(TA = -40 to +85°C, VDD = EVDD = AVREF0 = AVREF1 = 2.0 V to 3.6 V, RVDD = 1.8 V to 3.6 V, Vss = EVss = AVss = 0V,

C∟ = 50 pF)

|         | Parameter                          | Symbol  | Conditions                                                                           | MIN. | TYP. | MAX. | Unit |

|---------|------------------------------------|---------|--------------------------------------------------------------------------------------|------|------|------|------|

| <r></r> | V <sub>DD</sub> negative slew rate | VDDNSR1 | When using RTC backup mode, and setting the LVI detection level to 2.80 $\pm$ 0.10 V |      |      | 0.2  | V/ms |

| <r></r> |                                    | VDDNSR2 | When using RTC backup mode, and setting the LVI detection level to 2.30 $\pm$ 0.10 V |      |      | 0.07 | V/ms |

## (2) VDD Power-up timing

(TA = -40 to +85°C, VDD = EVDD = AVREF0 = AVREF1 = 2.0 V to 3.6 V, RVDD = 1.8 V to 3.6 V, Vss = EVss = AVss = 0V,

#### C∟ = 50 pF)

|         | Parameter              | Symbol  | Conditions | MIN. | TYP. | MAX. | Unit |

|---------|------------------------|---------|------------|------|------|------|------|

| <r></r> | VDD positive slew rate | RVDDPSR |            | 3.0  |      |      | V/s  |

# (3) Regulator output voltage for RTC backup area (VCH)

(TA = -40 to +85°C, VDD = EVDD = AVREF0 = AVREF1 = 2.0 V to 3.6 V, RVDD = 1.8 V to 3.6 V, Vss = EVss = AVss = 0V,

# C∟ = 50 pF)

| Parameter                        | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|----------------------------------|--------|------------|------|------|------|------|

| Regulator output voltage for RTC | VCH    |            | 0.8  |      | 1.8  | V    |

| backup area (VCH)                |        |            |      |      |      |      |

## (4) VCH setup time

## (TA = -40 to +85°C, VDD = EVDD = AVREF0 = AVREF1 = 2.0 V to 3.6 V, RVDD = 2.0 V to 3.6 V, VSS = EVSS = AVSS = 0V,

C∟ = 50 pF)

| Parameter      | Symbol        | Conditions                                | MIN. | TYP. | MAX. | Unit |

|----------------|---------------|-------------------------------------------|------|------|------|------|

| VCH setup time | <b>t</b> SPOR | The time from when RVDD reaches the       |      |      | 4.5  | ms   |

|                |               | maximum amplitude ( $V_{DD} = 2.0$ to 3.6 |      |      |      |      |

|                |               | V) until VCH is stable                    |      |      |      |      |

| (4/0) |

|-------|

|-------|

| Mnemonic | Operand                                   | Opcode                                                       | Operation                                                                                                                                                                                            |        | ecut         |        |    | I  | Flage | 6 |     |

|----------|-------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|--------|----|----|-------|---|-----|

|          |                                           |                                                              |                                                                                                                                                                                                      | i      | Clocl<br>r   | K<br>I | СҮ | ov | S     | Z | SAT |

| OR       | reg1,reg2                                 | rrrrr001000RRRRR                                             | GR[reg2]←GR[reg2]OR GR[reg1]                                                                                                                                                                         | 1      | 1            | 1      |    | 0  | ×     | × |     |

| ORI      | imm16,reg1,reg2                           | rrrr110100RRRRR                                              | GR[reg2]←GR[reg1]OR zero-extend(imm16)                                                                                                                                                               | 1      | 1            | 1      |    | 0  | ×     | × |     |

| PREPARE  | list12,imm5                               | 0000011110iiiiiL<br>LLLLLLLLL00001                           | Store-memory(sp–4,GR[reg in list12],Word)<br>sp←sp–4<br>repeat 1 step above until all regs in list12 is stored<br>sp←sp-zero-extend(imm5)                                                            |        | n+1<br>Note4 |        |    |    |       |   |     |

|          | list12,imm5,<br>sp/imm <sup>Note 15</sup> | 0000011110iiiiiL<br>LLLLLLLLLff011<br>imm16/imm32<br>Note 16 | Store-memory(sp-4,GR[reg in list12],Word)<br>$sp \leftarrow sp+4$<br>repeat 1 step above until all regs in list12 is stored<br>$sp \leftarrow sp$ -zero-extend (imm5)<br>$ep \leftarrow sp/imm$      | Note 4 | Note 4       | Note 4 |    |    |       |   |     |

| RETI     |                                           | 0000011111100000                                             | if PSW.EP=1<br>then PC $\leftarrow$ EIPC<br>PSW $\leftarrow$ EIPSW<br>else if PSW.NP=1<br>then PC $\leftarrow$ FEPC<br>PSW $\leftarrow$ FEPSW<br>else PC $\leftarrow$ EIPC<br>PSW $\leftarrow$ EIPSW | 3      | 3            | 3      | R  | R  | R     | R | R   |

| SAR      | reg1,reg2                                 | rrrr111111RRRRR<br>0000000010100000                          | GR[reg2]←GR[reg2]arithmetically shift right<br>by GR[reg1]                                                                                                                                           | 1      | 1            | 1      | ×  | 0  | ×     | × |     |

|          | imm5,reg2                                 | rrrr010101iiiii                                              | GR[reg2]←GR[reg2]arithmetically shift right<br>by zero-extend (imm5)                                                                                                                                 | 1      | 1            | 1      | ×  | 0  | ×     | × |     |

| SASF     | cccc,reg2                                 | rrrrr1111110cccc<br>0000001000000000                         | if conditions are satisfied<br>then GR[reg2] (GR[reg2]Logically shift left by 1)<br>OR 0000001H<br>else GR[reg2] (GR[reg2]Logically shift left by 1)<br>OR 00000000H                                 | 1      | 1            | 1      |    |    |       |   |     |

| SATADD   | reg1,reg2                                 | rrrr000110RRRRR                                              | GR[reg2]←saturated(GR[reg2]+GR[reg1])                                                                                                                                                                | 1      | 1            | 1      | ×  | ×  | ×     | × | ×   |

|          | imm5,reg2                                 | rrrrr010001iiiii                                             | GR[reg2]←saturated(GR[reg2]+sign-extend(imm5)                                                                                                                                                        | 1      | 1            | 1      | ×  | ×  | ×     | × | ×   |

| SATSUB   | reg1,reg2                                 | rrrr000101RRRRR                                              | GR[reg2]←saturated(GR[reg2]–GR[reg1])                                                                                                                                                                | 1      | 1            | 1      | ×  | ×  | ×     | × | ×   |

| SATSUBI  | imm16,reg1,reg2                           | rrrr110011RRRRR                                              | GR[reg2]←saturated(GR[reg1]–sign-extend(imm16)                                                                                                                                                       | 1      | 1            | 1      | ×  | ×  | ×     | × | ×   |

| SATSUBR  | reg1,reg2                                 | rrrr000100RRRRR                                              | GR[reg2]←saturated(GR[reg1]–GR[reg2])                                                                                                                                                                | 1      | 1            | 1      | ×  | ×  | ×     | × | ×   |

| SETF     | cccc,reg2                                 | rrrr1111110cccc<br>00000000000000000000                      | If conditions are satisfied<br>then GR[reg2]←00000001H<br>else GR[reg2]←00000000H                                                                                                                    | 1      | 1            | 1      |    |    |       |   |     |