## Intel - 10CX150YU484I6G Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 54770                                                      |

| Number of Logic Elements/Cells | 150000                                                     |

| Total RAM Bits                 | 10907648                                                   |

| Number of I/O                  | 188                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.9V                                                       |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 484-BFBGA                                                  |

| Supplier Device Package        | 484-UBGA (19x19)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/10cx150yu484i6g |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Intel<sup>®</sup> Cyclone<sup>®</sup> 10 GX Device Datasheet C10GX51002 | 2018.06.15

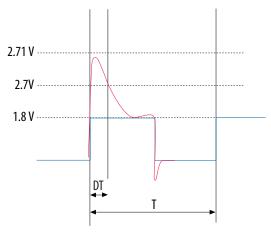

#### Figure 1. Intel Cyclone 10 GX Devices Overshoot Duration

## **Recommended Operating Conditions**

This section lists the functional operation limits for the AC and DC parameters for Intel Cyclone 10 GX devices.

#### **Recommended Operating Conditions**

#### Table 3. Recommended Operating Conditions for Intel Cyclone 10 GX Devices

This table lists the steady-state voltage values expected from Intel Cyclone 10 GX devices. Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol             | Description                                                       | Condition | Minimum <sup>(8)</sup> | Typical | Maximum <sup>(8)</sup> | Unit     |

|--------------------|-------------------------------------------------------------------|-----------|------------------------|---------|------------------------|----------|

| V <sub>CC</sub>    | Core voltage power supply                                         | —         | 0.87                   | 0.9     | 0.93                   | V        |

| V <sub>CCP</sub>   | Periphery circuitry and transceiver fabric interface power supply | _         | 0.87                   | 0.9     | 0.93                   | V        |

| V <sub>CCPGM</sub> | Configuration pins power supply                                   | 1.8 V     | 1.71                   | 1.8     | 1.89                   | V        |

|                    |                                                                   | 1.5 V     | 1.425                  | 1.5     | 1.575                  | V        |

|                    |                                                                   |           | •                      | •       | cc                     | ontinued |

<sup>(8)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

#### **Related Information**

- Early Power Estimator User Guide Provides more information about power estimation tools.

- Power Analysis and Optimization User Guide: Intel Quartus Prime Pro Edition Provides more information about power estimation tools.

#### I/O Pin Leakage Current

#### Table 5. I/O Pin Leakage Current for Intel Cyclone 10 GX Devices

If  $V_{O}$  =  $V_{CCIO}$  to  $V_{CCIOMAX},$  300  $\mu A$  of leakage current per I/O is expected.

|                  | Symbol | Description        | Condition                              | Min | Мах | Unit |

|------------------|--------|--------------------|----------------------------------------|-----|-----|------|

| $\mathbf{I}_{1}$ | I      | Input pin          | $V_{\rm I}$ = 0 V to $V_{\rm CCIOMAX}$ | -80 | 80  | μA   |

| I                | OZ     | Tri-stated I/O pin | $V_0 = 0 V$ to $V_{CCIOMAX}$           | -80 | 80  | μA   |

## **Bus Hold Specifications**

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

#### Table 6.Bus Hold Parameters for Intel Cyclone 10 GX Devices

| Parameter                                | Symbol            | Condition                                  |                                             | V <sub>CCIO</sub> (V) |                                              |     |                                              |     |     | Unit |     |     |    |

|------------------------------------------|-------------------|--------------------------------------------|---------------------------------------------|-----------------------|----------------------------------------------|-----|----------------------------------------------|-----|-----|------|-----|-----|----|

|                                          |                   |                                            | 1.                                          | 2                     | 1.                                           | 5   | 1.                                           | 8   | 2   | .5   | 3   | .0  |    |

|                                          |                   |                                            | Min                                         | Мах                   | Min                                          | Max | Min                                          | Max | Min | Max  | Min | Max |    |

| Bus-hold, low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(max) | 8 <sup>(15)</sup> ,<br>26 <sup>(16)</sup>   | _                     | 12 <sup>(15)</sup> ,<br>32 <sup>(16)</sup>   | -   | 30 <sup>(15)</sup> ,<br>55 <sup>(16)</sup>   | _   | 60  | -    | 70  | -   | μA |

| Bus-hold, high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min) | -8 <sup>(15)</sup> ,<br>-26 <sup>(16)</sup> | _                     | -12 <sup>(15)</sup> ,<br>-32 <sup>(16)</sup> | _   | -30 <sup>(15)</sup> ,<br>-55 <sup>(16)</sup> | _   | -60 | -    | -70 | -   | μA |

|                                          | continued         |                                            |                                             |                       |                                              |     |                                              |     |     |      |     |     |    |

<sup>(15)</sup> This value is only applicable for LVDS I/O bank.

$^{(16)}$  This value is only applicable for 3 V I/O bank.

| Parameter                            | Symbol            | Condition                                                           |     | V <sub>CCI0</sub> (V) |      |      |      |      |      |      | Unit |      |    |

|--------------------------------------|-------------------|---------------------------------------------------------------------|-----|-----------------------|------|------|------|------|------|------|------|------|----|

|                                      |                   |                                                                     | 1.  | 2                     | 1.   | 5    | 1.   | 8    | 2.   | 5    | 3.   | 0    |    |

|                                      |                   |                                                                     | Min | Max                   | Min  | Max  | Min  | Max  | Min  | Max  | Min  | Мах  |    |

| Bus-hold, low,<br>overdrive current  | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{\rm IN} < \\ V_{\rm CCIO} \end{array}$ | _   | 125                   | _    | 175  | _    | 200  | _    | 300  | _    | 500  | μA |

| Bus-hold, high,<br>overdrive current | I <sub>ODH</sub>  | $\begin{array}{c} 0 \ V < V_{\rm IN} < \\ V_{\rm CCIO} \end{array}$ | _   | -125                  | _    | -175 | _    | -200 | _    | -300 | _    | -500 | μA |

| Bus-hold trip<br>point               | V <sub>TRIP</sub> | _                                                                   | 0.3 | 0.9                   | 0.38 | 1.13 | 0.68 | 1.07 | 0.70 | 1.7  | 0.8  | 2    | V  |

## **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

## Table 7. OCT Calibration Accuracy Specifications for Intel Cyclone 10 GX Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                                                        | Description                                                                                                             | Condition (V)                       | Resistance | Tolerance  | Unit      |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------|------------|-----------|--|

|                                                                               |                                                                                                                         |                                     | -E5, -I5   | -E6, -I6   |           |  |

| 25-Ω and 50-Ω $R_{S}$                                                         | Internal series termination with calibration (25- $\Omega$ and 50- $\Omega$ setting)                                    | V <sub>CCIO</sub> = 1.8, 1.5, 1.2   | ± 15       | ± 15       | %         |  |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>                                  | Internal series termination with calibration (34-                                                                       | V <sub>CCIO</sub> = 1.5, 1.25, 1.2  | ± 15       | ± 15       | %         |  |

|                                                                               | $\Omega$ and 40- $\Omega$ setting)                                                                                      | V <sub>CCIO</sub> = 1.35            | ± 20       | ± 20       | %         |  |

| 48-Ω, 60-Ω, 80-Ω, and 120-Ω $R_{\rm S}$                                       | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 120- $\Omega$ setting)   | V <sub>CCIO</sub> = 1.2             | ± 15       | ± 15       | %         |  |

| 240-Ω R <sub>S</sub>                                                          | Internal series termination with calibration (240- $\Omega$ setting)                                                    | V <sub>CCI0</sub> = 1.2             | ± 20       | ± 20       | %         |  |

| 30-Ω R <sub>T</sub>                                                           | Internal parallel termination with calibration $(30-\Omega \text{ setting})$                                            | V <sub>CCIO</sub> = 1.5, 1.35, 1.25 | -10 to +40 | -10 to +40 | %         |  |

| 34- $\Omega$ , 48- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ R <sub>T</sub> | Internal parallel termination with calibration (34- $\Omega$ , 48- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2             | ± 15       | ± 15       | %         |  |

|                                                                               | •                                                                                                                       | •                                   |            |            | continued |  |

#### Table 11. Internal Weak Pull-Down Resistor Values for Intel Cyclone 10 GX Devices

| Pin Name   | Description                                                                                           | Condition (V)                 | Value <sup>(19)</sup> | Unit |

|------------|-------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|------|

| nIO_PULLUP | Dedicated input pin that determines the internal pull-ups on user I/O pins and dual-purpose I/O pins. | $V_{CC} = 0.9 \pm 3.33\%$     | 25                    | kΩ   |

| тск        | Dedicated JTAG test clock input pin.                                                                  | V <sub>CCPGM</sub> = 1.8 ±5 % | 25                    | kΩ   |

|            |                                                                                                       | V <sub>CCPGM</sub> = 1.5 ±5%  | 25                    | kΩ   |

|            |                                                                                                       | V <sub>CCPGM</sub> = 1.2 ±5%  | 25                    | kΩ   |

| MSEL[0:2]  | Configuration input pins that set the configuration scheme                                            | V <sub>CCPGM</sub> = 1.8 ±5%  | 25                    | kΩ   |

|            | for the FPGA device.                                                                                  | V <sub>CCPGM</sub> = 1.5 ±5%  | 25                    | kΩ   |

|            |                                                                                                       | V <sub>CCPGM</sub> = 1.2 ±5%  | 25                    | kΩ   |

#### **Related Information**

#### Intel Cyclone 10 GX Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

## **I/O Standard Specifications**

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Intel Cyclone 10 GX devices.

For minimum voltage values, use the minimum  $V_{CCIO}$  values. For maximum voltage values, use the maximum  $V_{CCIO}$  values.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

#### **Related Information**

Recommended Operating Conditions on page 7

| I/O Standard                       | V     | IL(DC) <b>(V)</b>       | VIH(DO                  | <sub>c)</sub> (V)        | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)                 | V <sub>он</sub> (V)                 |      | I <sub>OH</sub> <sup>(21)</sup> |

|------------------------------------|-------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|-------------------------------------|-------------------------------------|------|---------------------------------|

|                                    | Min   | Max                     | Min                     | Max                      | Max                     | Min                     | Мах                                 | Min                                 | (mA) | (mA)                            |

| SSTL-12/<br>SSTL-12<br>Class I, II | _     | V <sub>REF</sub> - 0.10 | V <sub>REF</sub> + 0.10 | _                        | V <sub>REF</sub> - 0.15 | V <sub>REF</sub> + 0.15 | 0.2 × V <sub>CCIO</sub>             | 0.8 × V <sub>CCIO</sub>             | -    | -                               |

| HSTL-18 Class I                    | -     | V <sub>REF</sub> -0.1   | $V_{REF} + 0.1$         | _                        | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 0.4                                 | V <sub>CCIO</sub> – 0.4             | 8    | -8                              |

| HSTL-18 Class<br>II                | _     | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 0.4                                 | V <sub>CCIO</sub> – 0.4             | 16   | -16                             |

| HSTL-15 Class I                    | -     | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | —                        | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 0.4                                 | V <sub>CCIO</sub> – 0.4             | 8    | -8                              |

| HSTL-15 Class<br>II                | _     | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 0.4                                 | V <sub>CCIO</sub> -0.4              | 16   | -16                             |

| HSTL-12 Class I                    | -0.15 | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$              | $0.75 \times V_{CCIO}$              | 8    | -8                              |

| HSTL-12 Class<br>II                | -0.15 | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15 | V <sub>REF</sub> + 0.15 | 0.25 × V <sub>CCIO</sub>            | 0.75 × V <sub>CCIO</sub>            | 16   | -16                             |

| HSUL-12                            | -     | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> - 0.22 | V <sub>REF</sub> + 0.22 | $0.1 \times V_{CCIO}$               | $0.9 \times V_{CCIO}$               | _    | _                               |

| POD12                              | -0.15 | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15 | V <sub>REF</sub> + 0.15 | (0.7 – 0.15) ×<br>V <sub>CCIO</sub> | (0.7 + 0.15) ×<br>V <sub>CCIO</sub> | -    | -                               |

## **Differential SSTL I/O Standards Specifications**

## Table 15. Differential SSTL I/O Standards Specifications for Intel Cyclone 10 GX Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>SWI</sub> | <sub>NG(DC)</sub> (V)   | V <sub>SWING(AC)</sub> (V)                    |                                               | V <sub>IX(AC)</sub> (V)      |     |                                 |

|------------------------|-------|-----------------------|-------|------------------|-------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------|-----|---------------------------------|

|                        | Min   | Тур                   | Мах   | Min              | Max                     | Min                                           | Мах                                           | Min                          | Тур | Max                             |

| SSTL-18 Class<br>I, II | 1.71  | 1.8                   | 1.89  | 0.25             | V <sub>CCIO</sub> + 0.6 | 0.5                                           | V <sub>CCIO</sub> + 0.6                       | V <sub>CCIO</sub> /2 - 0.175 | _   | V <sub>CCI0</sub> /2<br>+ 0.175 |

| SSTL-15 Class<br>I, II | 1.425 | 1.5                   | 1.575 | 0.2              | (22)                    | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>REF</sub> –<br>V <sub>IL(AC)</sub> ) | V <sub>CCIO</sub> /2 - 0.15  | _   | V <sub>CCIO</sub> /2 + 0.15     |

|                        |       |                       |       |                  |                         |                                               | •                                             |                              |     | continued                       |

<sup>&</sup>lt;sup>(21)</sup> To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

# **Switching Characteristics**

This section provides the performance characteristics of Intel Cyclone 10 GX core and periphery blocks for extended grade devices.

## **Transceiver Performance Specifications**

## **Transceiver Performance for Intel Cyclone 10 GX Devices**

## Table 18. Transmitter and Receiver Data Rate Performance

| Symbol/Description           | Condition                                                 | Datarate | Unit |

|------------------------------|-----------------------------------------------------------|----------|------|

|                              | Maximum data rate $V_{CCR_GXB} = V_{CCT_GXB} = 1.03 V$    | 12.5     | Gbps |

| Chip-to-Chip <sup>(29)</sup> | Maximum data rate<br>$V_{CCR_GXB} = V_{CCT_GXB} = 0.95 V$ | 11.3     | Gbps |

|                              | Minimum Data Rate                                         | 1.0 (30) | Gbps |

| Backplane                    | Maximum data rate<br>$V_{CCR_GXB} = V_{CCT_GXB} = 1.03 V$ | 6.6      | Gbps |

|                              | Minimum Data Rate                                         | 1.0 (30) | Gbps |

## Table 19. ATX PLL and Fractional PLL (fPLL) Performance

| Symbol/Description         | Condition         | Frequency | Unit |

|----------------------------|-------------------|-----------|------|

| Supported Output Executors | Maximum Frequency | 6.25      | GHz  |

| Supported Output Frequency | Minimum Frequency | 500       | MHz  |

<sup>&</sup>lt;sup>(29)</sup> Chip-to-chip links are applications with short reach channels.

<sup>&</sup>lt;sup>(30)</sup> Intel Cyclone 10 GX transceivers can support data rates down to 125 Mbps with over sampling. You must create your own over sampling logic.

#### Table 20.CMU PLL Performance

| Symbol/Description         | Condition         | Frequency | Unit |

|----------------------------|-------------------|-----------|------|

| Supported Output Executors | Maximum Frequency | 5.15625   | GHz  |

| Supported Output Frequency | Minimum Frequency | 2450      | MHz  |

#### **Related Information**

Transceiver Power Supply Operating Conditions on page 9

## **High-Speed Serial Transceiver-Fabric Interface Performance for Intel Cyclone 10 GX Devices**

## Table 21. High-Speed Serial Transceiver-Fabric Interface Performance for Intel Cyclone 10 GX Devices

The frequencies listed are the maximum frequencies.

| Symbol/Description            | Condition (V)         | Core Speed Grade |     | Unit |

|-------------------------------|-----------------------|------------------|-----|------|

|                               |                       | -5               | -6  |      |

| 20-bit interface - FIFO       | V <sub>CC</sub> = 0.9 | 400              | 400 | MHz  |

| 20-bit interface - Registered | V <sub>CC</sub> = 0.9 | 400              | 400 | MHz  |

| 32-bit interface - FIFO       | V <sub>CC</sub> = 0.9 | 404              | 335 | MHz  |

| 32-bit interface - Registered | V <sub>CC</sub> = 0.9 | 404              | 335 | MHz  |

| 64-bit interface - FIFO       | V <sub>CC</sub> = 0.9 | 234              | 222 | MHz  |

| 64-bit interface - Registered | V <sub>CC</sub> = 0.9 | 234              | 222 | MHz  |

## **Transceiver Specifications for Intel Cyclone 10 GX Devices**

## Table 22. Reference Clock Specifications

| Symbol/Description      | Condition                     | Min                                           | Тур | Max | Unit      |

|-------------------------|-------------------------------|-----------------------------------------------|-----|-----|-----------|

| Supported I/O Standards | Dedicated reference clock pin | CML, Differential LVPECL, LVDS, and HCSL (31) |     |     |           |

|                         | RX pin as a reference clock   | CML, Differential LVPECL, and LVDS            |     |     |           |

|                         | •                             | •                                             |     |     | continued |

<sup>(31)</sup> HCSL is only supported for PCIe.

### Intel<sup>®</sup> Cyclone<sup>®</sup> 10 GX Device Datasheet C10GX51002 | 2018.06.15

| Symbol/Description            | Condition                                                                 | Min | Тур       | Мах | Unit |

|-------------------------------|---------------------------------------------------------------------------|-----|-----------|-----|------|

|                               | 100-Ω setting                                                             | -   | 100 ± 20% | _   | Ω    |

| V (AC coupled)                | $V_{CCT\_GXB} = 0.95 V$                                                   | _   | 450       | _   | mV   |

| V <sub>OCM</sub> (AC coupled) | $V_{CCT\_GXB} = 1.03 V$                                                   | —   | 500       | —   | mV   |

| V <sub>OCM</sub> (DC coupled) | $V_{CCT\_GXB} = 0.95 V$                                                   | —   | 450       | —   | mV   |

|                               | $V_{CCT\_GXB} = 1.03 V$                                                   | —   | 500       | —   | mV   |

| Rise time <sup>(45)</sup>     | 20% to 80%                                                                | 20  | _         | 130 | ps   |

| Fall time <sup>(45)</sup>     | 80% to 20%                                                                | 20  | -         | 130 | ps   |

| Intra-differential pair skew  | TX V <sub>CM</sub> = 0.5 V and slew rate setting of SLEW_R5 $^{\rm (46)}$ | _   | —         | 15  | ps   |

## Table 27.Typical Transmitter Vod Settings

| Symbol                                                                          | V <sub>OD</sub> Setting | V <sub>OD</sub> -to-V <sub>CCT_GXB</sub> Ratio |  |  |  |  |  |

|---------------------------------------------------------------------------------|-------------------------|------------------------------------------------|--|--|--|--|--|

|                                                                                 | 31                      | 1.00                                           |  |  |  |  |  |

|                                                                                 | 30                      | 0.97                                           |  |  |  |  |  |

|                                                                                 | 29                      | 0.93                                           |  |  |  |  |  |

|                                                                                 | 28                      | 0.90                                           |  |  |  |  |  |

|                                                                                 | 27                      | 0.87                                           |  |  |  |  |  |

| $V_{OD}$ differential value = $V_{OD}$ -to- $V_{CCT_GXB}$ ratio x $V_{CCT_GXB}$ | 26                      | 0.83                                           |  |  |  |  |  |

|                                                                                 | 25                      | 0.80                                           |  |  |  |  |  |

|                                                                                 | 24                      | 0.77                                           |  |  |  |  |  |

|                                                                                 | 23                      | 0.73                                           |  |  |  |  |  |

|                                                                                 | 22                      | 0.70                                           |  |  |  |  |  |

| continued                                                                       |                         |                                                |  |  |  |  |  |

<sup>&</sup>lt;sup>(45)</sup> The Intel Quartus Prime software automatically selects the appropriate slew rate depending on the design configurations.

<sup>&</sup>lt;sup>(46)</sup> SLEW\_R1 is the slowest and SLEW\_R5 is the fastest. SLEW\_R6 and SLEW\_R7 are not used.

| Symbol | V <sub>OD</sub> Setting | V <sub>OD</sub> -to-V <sub>CCT_GXB</sub> Ratio |

|--------|-------------------------|------------------------------------------------|

|        | 21                      | 0.67                                           |

|        | 20                      | 0.63                                           |

|        | 19                      | 0.60                                           |

|        | 18                      | 0.57                                           |

|        | 17                      | 0.53                                           |

|        | 16                      | 0.50                                           |

|        | 15                      | 0.47                                           |

|        | 14                      | 0.43                                           |

|        | 13                      | 0.40                                           |

|        | 12                      | 0.37                                           |

## Table 28. Transmitter Channel-to-channel Skew Specifications

| Mode Channel Span                                           |                              | Maximum Skew | Unit |

|-------------------------------------------------------------|------------------------------|--------------|------|

| x6 Clock                                                    | Up to 6 channels in one bank | 61           | ps   |

| xN Clock                                                    | Within 2 banks               | 230          | ps   |

| PLL Feedback Compensation <sup>(47)</sup> , <sup>(48)</sup> | Side-wide                    | 1600         | ps   |

**Related Information**

PLLs and Clock Networks

<sup>&</sup>lt;sup>(47)</sup> refclk is set to 125 MHz during the test.

<sup>&</sup>lt;sup>(48)</sup> You can reduce the lane-to-lane skew by increasing the reference clock frequency.

| Symbol                                 | Parameter                                                                                                       | Condition                     | Min | Тур | Мах  | Unit      |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|------|-----------|

| t <sub>LOCK</sub>                      | Time required to lock from end-of-device configuration or deassertion of pll_powerdown                          | -                             | _   | _   | 1    | ms        |

| t <sub>DLOCK</sub>                     | Time required to lock dynamically (after<br>switchover or reconfiguring any non-post-<br>scale counters/delays) | _                             | _   | _   | 1    | ms        |

| f <sub>CLBW</sub>                      | PLL closed-loop bandwidth                                                                                       | —                             | 0.3 | -   | 4    | MHz       |

| t <sub>PLL_PSERR</sub>                 | Accuracy of PLL phase shift                                                                                     | _                             | _   | -   | 50   | ps        |

| t <sub>ARESET</sub>                    | Minimum pulse width on the pll_powerdown signal                                                                 | _                             | 10  | _   | _    | ns        |

| t <sub>INCCJ</sub> <sup>(50)(51)</sup> | Input clock cycle-to-cycle jitter                                                                               | $F_{REF} \ge 100 \text{ MHz}$ | _   | _   | 0.13 | UI (p-p)  |

|                                        |                                                                                                                 | F <sub>REF</sub> < 100 MHz    | _   | _   | 650  | ps (p-p)  |

| t <sub>outpj</sub> <sup>(52)</sup>     | Period jitter for clock output                                                                                  | $F_{OUT} \ge 100 \text{ MHz}$ | _   | _   | 600  | ps (p-p)  |

|                                        |                                                                                                                 | F <sub>OUT</sub> < 100 MHz    | _   | _   | 60   | mUI (p-p) |

| t <sub>outcc</sub> (52)                | Cycle-to-cycle jitter for clock output                                                                          | $F_{OUT} \ge 100 \text{ MHz}$ | _   | -   | 600  | ps (p-p)  |

|                                        |                                                                                                                 | F <sub>OUT</sub> < 100 MHz    | _   | _   | 60   | mUI (p-p) |

| dK <sub>BIT</sub>                      | Bit number of Delta Sigma Modulator (DSM)                                                                       | _                             | _   | 32  | _    | bit       |

## **Related Information**

Memory Output Clock Jitter Specifications on page 43

Provides more information about the external memory interface clock output jitter specifications.

- <sup>(51)</sup>  $F_{REF}$  is  $f_{IN}/N$ , specification applies when N = 1.

- <sup>(52)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in Memory Output Clock Jitter Specification for Intel Cyclone 10 GX Devices table.

<sup>&</sup>lt;sup>(50)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.

| Symbol                                | Parameter                                                                                                      | Condition                     | Min | Тур | Мах  | Unit      |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|------|-----------|

| t <sub>DLOCK</sub>                    | Time required to lock dynamically (after<br>switchover or reconfiguring any non-post-scale<br>counters/delays) | -                             | _   | -   | 1    | ms        |

| t <sub>PLL_PSERR</sub>                | Accuracy of PLL phase shift                                                                                    | _                             | _   | _   | ±50  | ps        |

| t <sub>ARESET</sub>                   | Minimum pulse width on the areset signal                                                                       | _                             | 10  | _   | _    | ns        |

| t <sub>INCCJ</sub> (54)(55)           | Input clock cycle-to-cycle jitter                                                                              | $F_{REF} \ge 100 \text{ MHz}$ | _   | _   | 0.15 | UI (p-p)  |

|                                       |                                                                                                                | F <sub>REF</sub> < 100 MHz    | _   | _   | 750  | ps (p-p)  |

| t <sub>outpj_dc</sub>                 | Period jitter for dedicated clock output                                                                       | $F_{OUT} \ge 100 \text{ MHz}$ | _   | _   | 175  | ps (p-p)  |

|                                       |                                                                                                                | F <sub>OUT</sub> < 100 MHz    | _   | _   | 17.5 | mUI (p-p) |

| t <sub>OUTCCJ_DC</sub>                | Cycle-to-cycle jitter for dedicated clock output                                                               | $F_{OUT} \ge 100 \text{ MHz}$ | _   | -   | 175  | ps (p-p)  |

|                                       |                                                                                                                | F <sub>OUT</sub> < 100 MHz    | _   | _   | 17.5 | mUI (p-p) |

| t <sub>outpj_io</sub> <sup>(56)</sup> | Period jitter for clock output on the regular I/O                                                              | $F_{OUT} \ge 100 \text{ MHz}$ | _   | _   | 600  | ps (p-p)  |

|                                       |                                                                                                                | $F_{OUT} < 100 \text{ MHz}$   | _   | _   | 60   | mUI (p-p) |

| t <sub>OUTCCJ_IO</sub> (56)           | Cycle-to-cycle jitter for clock output on the                                                                  | $F_{OUT} \ge 100 \text{ MHz}$ | _   | -   | 600  | ps (p-p)  |

|                                       | regular I/O                                                                                                    | F <sub>OUT</sub> < 100 MHz    | _   | -   | 60   | mUI (p-p) |

| t <sub>CASC_OUTPJ_DC</sub>            | Period jitter for dedicated clock output in                                                                    | $F_{OUT} \ge 100 \text{ MHz}$ | _   | _   | 175  | ps (p-p)  |

|                                       | cascaded PLLs                                                                                                  | F <sub>OUT</sub> < 100 MHz    | _   | _   | 17.5 | mUI (p-p) |

#### **Related Information**

Memory Output Clock Jitter Specifications on page 43 Provides more information about the external memory interface clock output jitter specifications.

- <sup>(55)</sup>  $F_{REF}$  is  $f_{IN}/N$ , specification applies when N = 1.

- <sup>(56)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in Memory Output Clock Jitter Specification for Intel Cyclone 10 GX Devices table.

<sup>&</sup>lt;sup>(54)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.

| Symbol              |                                      | Condition                                            |      | -E5, -I5 | 5                                   |      | -E6, -I6 | 5                                   | Unit  |

|---------------------|--------------------------------------|------------------------------------------------------|------|----------|-------------------------------------|------|----------|-------------------------------------|-------|

|                     |                                      |                                                      | Min  | Тур      | Max                                 | Min  | Тур      | Мах                                 |       |

|                     | TCCS (64)(59)                        | True Differential I/O<br>Standards                   | _    | -        | 150                                 | _    | -        | 150                                 | ps    |

| Receiver            | True Differential<br>I/O Standards - | SERDES factor<br>J = 4 to 10 <sup>(60)(61)(62)</sup> | 150  | -        | 1434                                | 150  | -        | 1250                                | Mbps  |

|                     | f <sub>HSDRDPA</sub> (data<br>rate)  | SERDES factor<br>J = 3 (60)(61)(62)                  | 150  | -        | 1076                                | 150  | -        | 938                                 | Mbps  |

|                     | f <sub>HSDR</sub> (data rate)        | SERDES factor J = 3 to 10                            | (62) | -        | (66)                                | (62) | _        | (66)                                | Mbps  |

|                     | (without<br>DPA) <sup>(59)</sup>     | SERDES factor J = 2, uses<br>DDR registers           | (62) | -        | (63)                                | (62) | -        | (63)                                | Mbps  |

|                     |                                      | SERDES factor J = 1, uses<br>DDR registers           | (62) | -        | (63)                                | (62) | -        | (63)                                | Mbps  |

| DPA (FIFO mode)     | DPA run length                       | _                                                    | _    | -        | 10000                               | 1    | _        | 10000                               | UI    |

| DPA (soft CDR mode) | DPA run length                       | SGMII/GbE protocol                                   | _    | -        | 5                                   | _    | _        | 5                                   | UI    |

|                     |                                      | All other protocols                                  | _    | -        | 50 data<br>transition<br>per 208 UI | _    | _        | 50 data<br>transition<br>per 208 UI | _     |

| Soft CDR mode       | Soft-CDR ppm<br>tolerance            | _                                                    | _    | -        | 300                                 | _    | -        | 300                                 | ± ppm |

| Non DPA mode        | Sampling Window                      | -                                                    | _    | -        | 300                                 | _    | -        | 300                                 | ps    |

$<sup>^{(65)}</sup>$  This applies to default pre-emphasis and V<sub>OD</sub> settings only.

<sup>&</sup>lt;sup>(66)</sup> You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

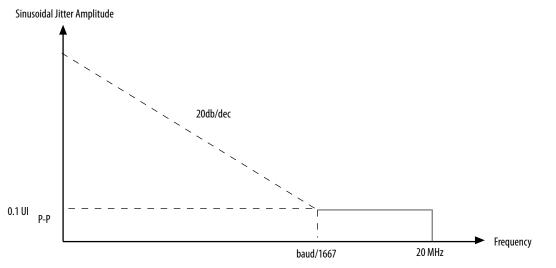

## Figure 4. LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications for a Data Rate Less than 1.4 Gbps

## Memory Standards Supported by the Hard Memory Controller

## Table 40. Memory Standards Supported by the Hard Memory Controller for Intel Cyclone 10 GX Devices

This table lists the overall capability of the hard memory controller. For specific details, refer to the External Memory Interface Spec Estimator.

| Memory Standard | Rate Support | Speed Grade | Ping Pong PHY | Maximum Fre | quency (MHz) |

|-----------------|--------------|-------------|---------------|-------------|--------------|

|                 |              |             | Support       | I/O Bank    | 3 V I/O Bank |

| DDR3 SDRAM      | Half rate    | -5          | Yes           | 533         | 225          |

|                 |              |             | -             | 533         | 225          |

|                 |              | -6          | Yes           | 466         | 166          |

|                 |              |             | -             | 466         | 166          |

|                 | Quarter rate | -5          | Yes           | 933         | 450          |

|                 |              |             | -             | 933         | 450          |

|                 |              | -6          | Yes           | 933         | 333          |

|                 |              |             |               |             | continued    |

#### Table 47. DCLK-to-DATA[] Ratio for Intel Cyclone 10 GX Devices

You cannot turn on encryption and compression at the same time for Intel Cyclone 10 GX devices.

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

| FPP (8-bit wide)     | Off        | Off         | 1                        |

|                      | On         | Off         | 1                        |

|                      | Off        | On          | 2                        |

| FPP (16-bit wide)    | Off        | Off         | 1                        |

|                      | On         | Off         | 2                        |

|                      | Off        | On          | 4                        |

| FPP (32-bit wide)    | Off        | Off         | 1                        |

|                      | On         | Off         | 4                        |

|                      | Off        | On          | 8                        |

## **FPP** Configuration Timing when DCLK-to-DATA[] = 1

*Note:* When you enable decompression or the design security feature, the DCLK-to-DATA[] ratio varies for FPP ×8, FPP ×16, and FPP ×32. For the respective DCLK-to-DATA[] ratio, refer to the DCLK-to-DATA[] Ratio for Intel Cyclone 10 GX Devices table.

## Table 48. FPP Timing Parameters When the DCLK-to-DATA[] Ratio is 1 for Intel Cyclone 10 GX Devices

Use these timing parameters when the decompression and design security features are disabled.

| Symbol              | Parameter                    | Minimum | Maximum               | Unit      |

|---------------------|------------------------------|---------|-----------------------|-----------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | 480     | 1,440                 | ns        |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low   | 320     | 960                   | ns        |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _                     | μs        |

| t <sub>STATUS</sub> | nSTATUS low pulse width      | 268     | 3,000 <sup>(70)</sup> | μs        |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high | -       | 3,000 <sup>(71)</sup> | μs        |

|                     |                              |         |                       | continued |

<sup>(70)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

# Initialization

## Table 53. Initialization Clock Source Option and the Maximum Frequency for Intel Cyclone 10 GX Devices

| Initialization Clock Source | Configuration Scheme | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, and FPP      | 12.5                    | 600                            |

| CLKUSR (82)(83)             | AS, PS, and FPP      | 100                     |                                |

## **Configuration Files**

There are two types of configuration bit stream formats for different configuration schemes:

- PS and FPP—Raw Binary File (.rbf)

- AS—Raw Programming Data File (.rpd)

The .rpd file size follows the Intel configuration devices capacity. However, the actual configuration bit stream size for .rpd file is the same as .rbf file.

<sup>(82)</sup> To enable CLKUSR as the initialization clock source, in the Intel Quartus Prime software, select Device and Pin Options > General

> Device initialization clock source > CLKUSR pin.

<sup>&</sup>lt;sup>(83)</sup> If you use the CLKUSR pin for AS and transceiver calibration simultaneously, the only allowed frequency is 100 MHz.

### Table 54. Configuration Bit Stream Sizes for Intel Cyclone 10 GX Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Intel Quartus Prime software. However, for a specific version of the Intel Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

I/O configuration shift register (IOCSR) is a long shift register that facilitates the device I/O peripheral settings. The IOCSR bit stream is part of the uncompressed configuration bit stream, and it is specifically for the Configuration via Protocol (CvP) feature.

Uncompressed configuration bit stream sizes are subject to change for improvements and optimizations in the configuration algorithm.

| Variant             | Product Line | Uncompressed Configuration Bit<br>Stream Size (bits) | IOCSR Bit Stream Size (bits) | Recommended EPCQ-L Serial Configuration<br>Device |

|---------------------|--------------|------------------------------------------------------|------------------------------|---------------------------------------------------|

| Intel Cyclone 10 GX | GX 085       | 81,923,582                                           | 2,507,264                    | EPCQ-L256 or higher density                       |

|                     | GX 105       | 81,923,582                                           | 2,507,264                    | EPCQ-L256 or higher density                       |

|                     | GX 150       | 81,923,582                                           | 2,507,264                    | EPCQ-L256 or higher density                       |

|                     | GX 220       | 81,923,582                                           | 2,507,264                    | EPCQ-L256 or higher density                       |

# **Remote System Upgrades**

## Table 56. Remote System Upgrade Circuitry Timing Specifications for Intel Cyclone 10 GX Devices

| Parameter                                | Minimum | Maximum | Unit |

|------------------------------------------|---------|---------|------|

| f <sub>MAX_RU_CLK</sub> <sup>(86)</sup>  | —       | 40      | MHz  |

| t <sub>RU_nCONFIG</sub> <sup>(87)</sup>  | 250     | -       | ns   |

| t <sub>RU_nRSTIMER</sub> <sup>(88)</sup> | 250     | —       | ns   |

#### **Related Information**

- Remote System Upgrade State Machine Provides more information about configuration reset (RU\_CONFIG) signal.

- User Watchdog Timer

Provides more information about reset\_timer (RU\_nRSTIMER) signal.

## **User Watchdog Internal Circuitry Timing Specifications**

## Table 57. User Watchdog Internal Oscillator Frequency Specifications for Intel Cyclone 10 GX Devices

| Parameter                                   | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|---------|---------|---------|------|

| User watchdog internal oscillator frequency | 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

I/O timing data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the timing analysis. You may generate the I/O timing report manually using the Timing Analyzer or using the automated script.

<sup>&</sup>lt;sup>(86)</sup> This clock is user-supplied to the remote system upgrade circuitry. If you are using the Remote Update Intel FPGA IP core, the clock user-supplied to the Remote Update Intel FPGA IP core must meet this specification.

<sup>&</sup>lt;sup>(87)</sup> This is equivalent to strobing the reconfiguration input of the Remote Update Intel FPGA IP core high for the minimum timing specification.

<sup>&</sup>lt;sup>(88)</sup> This is equivalent to strobing the reset\_timer input of the Remote Update Intel FPGA IP core high for the minimum timing specification.

The Intel Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

#### AN775: I/O Timing Information Generation Guidelines

Provides the techniques to generate I/O timing information using the Intel Quartus Prime software.

# **Programmable IOE Delay**

### Table 58. IOE Programmable Delay for Intel Cyclone 10 GX Devices

For the exact values for each setting, use the latest version of the Intel Quartus Prime software. The values in the table show the delay of programmable IOE delay chain with maximum offset settings after excluding the intrinsic delay (delay at minimum offset settings).

Programmable IOE delay settings are only applicable for I/O buffers and do not apply for any other delay elements in the PHYLite for Parallel Interfaces Intel Cyclone 10 FPGA IP core.

| Parameter <sup>(89)</sup>                      | Maximum Offset | Minimum<br>Offset <sup>(90)</sup> | Fast Model |            | Slow Model |          | Unit |

|------------------------------------------------|----------------|-----------------------------------|------------|------------|------------|----------|------|

|                                                |                | Unset (00)                        | Extended   | Industrial | -E5, -I5   | -E6, -I6 |      |

| Input Delay Chain Setting<br>(IO_IN_DLY_CHN)   | 63             | 0                                 | 2.012      | 2.003      | 5.241      | 6.035    | ns   |

| Output Delay Chain Setting<br>(IO_OUT_DLY_CHN) | 15             | 0                                 | 0.478      | 0.475      | 1.263      | 1.462    | ns   |

# Glossary

#### Table 59.Glossary

| Term                       | Definition               |

|----------------------------|--------------------------|

| Differential I/O Standards | Receiver Input Waveforms |

|                            | continued                |

<sup>(90)</sup> Minimum offset does not include the intrinsic delay.

<sup>&</sup>lt;sup>(89)</sup> You can set this value in the Intel Quartus Prime software by selecting **Input Delay Chain Setting** or **Output Delay Chain Setting** in the **Assignment Name** column.

| Term                       | Definition                                                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                            | Single-Ended Waveform     Positive Channel (p) = V <sub>IH</sub> $V_{ID}$ Negative Channel (n) = V <sub>IL</sub> Ground     Ground |

|                            | Differential Waveform<br>VID<br>Transmitter Output Waveforms<br>Single-Ended Waveform                                              |

|                            | Positive Channel (p) = V <sub>OH</sub><br>Negative Channel (n) = V <sub>OL</sub><br>Ground                                         |

|                            | $\frac{1}{\sqrt{V_{0D}}} p - n = 0 V$                                                                                              |

| f <sub>HSCLK</sub>         | I/O PLL input clock frequency.                                                                                                     |

| f <sub>HSDR</sub>          | High-speed I/O block—Maximum/minimum LVDS data transfer rate $(f_{HSDR} = 1/TUI)$ , non-DPA.                                       |

| f <sub>hsdrdpa</sub>       | High-speed I/O block—Maximum/minimum LVDS data transfer rate ( $f_{HSDRDPA} = 1/TUI$ ), DPA.                                       |

| ]                          | High-speed I/O block—Deserialization factor (width of parallel data bus).                                                          |

| JTAG Timing Specifications | JTAG Timing Specifications:                                                                                                        |

|                            | continued                                                                                                                          |

## Intel<sup>®</sup> Cyclone<sup>®</sup> 10 GX Device Datasheet C10GX51002 | 2018.06.15

| Date                     | Version    | Changes                                                                                                                                                                                                                                   |

|--------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2017 2017.11.10 |            | Changed the full symbol names for V <sub>CCR_GXB</sub> and V <sub>CCT_GXB</sub> , and changed the description for V <sub>CCH_GXB</sub> in the <i>Transceiver Power Supply Operating Conditions for Intel Cyclone 10 GX Devices</i> table. |

|                          |            | • Removed note from the Transceiver Power Supply Operating Conditions section.                                                                                                                                                            |

|                          |            | Added a footnote in the <i>Reference Clock Specifications</i> table.                                                                                                                                                                      |

|                          |            | • Removed the "Programmable AC Gain at High Gain mode and Data Rate ≤ 12.5 Gbps" parameter from the <i>Receiver Specifications</i> table.                                                                                                 |

|                          |            | • Changed the channel span descriptions for the x1 and x6 clock networks in the <i>Transceiver Clock Network Maximum Data Rate Specifications</i> table.                                                                                  |

|                          |            | • Changed the description of the VOD ratio in the Typical Transmitter V <sub>OD</sub> Settings table.                                                                                                                                     |

|                          |            | • Changed the specifications for CDR PPM deviation limit in the Receiver Specifications table.                                                                                                                                            |

|                          |            | Updated the description for V <sub>CCT_GXB</sub> , V <sub>CCR_GXB</sub> , and V <sub>CCH_GXB</sub> .                                                                                                                                      |

|                          |            | • Added note to V <sub>I</sub> in the <i>Recommended Operating Conditions for Intel Cyclone 10 GX Devices</i> table.                                                                                                                      |

|                          |            | • Updated notes to RSDS and Mini-LVDS in the Differential I/O Standards Specifications for Intel Cyclone 10 GX Devices table.                                                                                                             |

|                          |            | • Updated f <sub>VCO</sub> specifications in the <i>Fractional PLL Specifications for Intel Cyclone 10 GX Devices</i> table.                                                                                                              |

|                          |            | <ul> <li>Updated temperature range from "-40 to 125°C" to "-40 to 100°C" in the Internal Temperature Sensing Diode<br/>Specifications for Intel Cyclone 10 GX Devices table.</li> </ul>                                                   |

|                          |            | • Updated the description for the Memory Output Clock Jitter Specifications for Intel Cyclone 10 GX Devices table.                                                                                                                        |

|                          |            | Updated the following IP cores name:                                                                                                                                                                                                      |

|                          |            | <ul> <li>Remote Update Intel FPGA</li> </ul>                                                                                                                                                                                              |

|                          |            | <ul> <li>PHYLite for Parallel Interfaces Intel Cyclone 10 FPGA</li> </ul>                                                                                                                                                                 |

|                          |            | Removed automotive-grade information.                                                                                                                                                                                                     |

|                          |            | Removed Preliminary tags.                                                                                                                                                                                                                 |

| May 2017                 | 2017.05.08 | Initial release.                                                                                                                                                                                                                          |