## Intel - 10CX220YU484I6G Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                     |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 80330                                                      |

| Number of Logic Elements/Cells | 220000                                                     |

| Total RAM Bits                 | 13752320                                                   |

| Number of I/O                  | 188                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.9V                                                       |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 484-BFBGA                                                  |

| Supplier Device Package        | 484-UBGA (19x19)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/10cx220yu484i6g |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol           | Description                    | Condition | Minimum                            | Maximum | Unit |

|------------------|--------------------------------|-----------|------------------------------------|---------|------|

| I <sub>OUT</sub> | DC output current per pin      | _         | -25 <sup>(2)(3)(4)(5)</sup><br>(6) | 25      | mA   |

| Tj               | Operating junction temperature | _         | -55                                | 125     | °C   |

| T <sub>STG</sub> | Storage temperature (no bias)  | _         | -65                                | 150     | °C   |

- AN 692: Power Sequencing Considerations for Intel Cyclone 10 GX, Intel Arria 10, and Intel Stratix 10 Devices Provides the power sequencing requirements for Intel Cyclone 10 GX devices.

- Power-Up and Power-Down Sequences, Power Management in Intel Cyclone 10 GX Devices chapter Provides the power sequencing requirements for Intel Cyclone 10 GX devices.

## **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 2.70 V for LVDS I/O can only be at 2.70 V for ~4% over the lifetime of the device.

- <sup>(3)</sup> Total current per LVDS I/O bank must not exceed 100 mA.

- <sup>(4)</sup> Voltage level must not exceed 1.89 V.

- <sup>(5)</sup> Applies to all I/O standards and settings supported by LVDS I/O banks, including single-ended and differential I/Os.

- (6) Applies only to LVDS I/O banks. 3 V I/O banks are not covered under this specification and must be implemented as per the power sequencing requirement. For more details, refer to AN 692: Power Sequencing Considerations for Intel Cyclone 10 GX, Intel Arria<sup>®</sup> 10, and Intel Stratix<sup>®</sup> 10 Devices and Power Management in Intel Cyclone 10 GX Devices chapter.

<sup>&</sup>lt;sup>(2)</sup> The maximum current allowed through any LVDS I/O bank pin when the device is not turned on or during power-up/power-down conditions is 10 mA.

#### Table 2. Maximum Allowed Overshoot During Transitions for Intel Cyclone 10 GX Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime. The LVDS I/O values are applicable to the VREFP\_ADC and VREFN\_ADC I/O pins.

| Symbol              | Description      | Condition (V)           |         | Overshoot Duration as % at T <sub>1</sub> = 100°C | Unit |

|---------------------|------------------|-------------------------|---------|---------------------------------------------------|------|

|                     |                  | LVDS I/O <sup>(7)</sup> | 3 V I/O |                                                   |      |

| V <sub>i</sub> (AC) | AC input voltage | 2.50                    | 3.80    | 100                                               | %    |

|                     |                  | 2.55                    | 3.85    | 42                                                | %    |

|                     |                  | 2.60                    | 3.90    | 18                                                | %    |

|                     |                  | 2.65                    | 3.95    | 9                                                 | %    |

|                     |                  | 2.70                    | 4.00    | 4                                                 | %    |

|                     |                  | > 2.70                  | > 4.00  | No overshoot allowed                              | %    |

For an overshoot of 2.5 V, the percentage of high time for the overshoot can be as high as 100% over a 10-year period. Percentage of high time is calculated as ([delta T]/T)  $\times$  100. This 10-year period assumes that the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal.

<sup>&</sup>lt;sup>(7)</sup> The LVDS I/O values are applicable to all dedicated and dual-function configuration I/Os.

| Parameter                            | Symbol            | Condition                                                           |         | V <sub>CCIO</sub> (V) |      |      |      |      |      |      |     |      | Unit |

|--------------------------------------|-------------------|---------------------------------------------------------------------|---------|-----------------------|------|------|------|------|------|------|-----|------|------|

|                                      |                   |                                                                     | 1.2 1.5 |                       | 1.8  |      | 2.   | 2.5  |      | 3.0  |     |      |      |

|                                      |                   |                                                                     | Min     | Мах                   | Min  | Max  | Min  | Max  | Min  | Max  | Min | Мах  |      |

| Bus-hold, low,<br>overdrive current  | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{\rm IN} < \\ V_{\rm CCIO} \end{array}$ | _       | 125                   | _    | 175  | _    | 200  | _    | 300  | _   | 500  | μA   |

| Bus-hold, high,<br>overdrive current | I <sub>ODH</sub>  | $\begin{array}{c} 0 \ V < V_{\rm IN} < \\ V_{\rm CCIO} \end{array}$ | _       | -125                  | _    | -175 | _    | -200 | _    | -300 | _   | -500 | μA   |

| Bus-hold trip<br>point               | V <sub>TRIP</sub> | _                                                                   | 0.3     | 0.9                   | 0.38 | 1.13 | 0.68 | 1.07 | 0.70 | 1.7  | 0.8 | 2    | V    |

### **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

## Table 7. OCT Calibration Accuracy Specifications for Intel Cyclone 10 GX Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                                                        | Description                                                                                                             | Condition (V)                       | Resistance | Tolerance  | Unit      |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------|------------|-----------|

|                                                                               |                                                                                                                         |                                     | -E5, -I5   | -E6, -I6   |           |

| 25-Ω and 50-Ω $R_{S}$                                                         | Internal series termination with calibration (25- $\Omega$ and 50- $\Omega$ setting)                                    | V <sub>CCIO</sub> = 1.8, 1.5, 1.2   | ± 15       | ± 15       | %         |

| 34-Ω and 40-Ω $R_S$                                                           | Internal series termination with calibration (34-                                                                       | V <sub>CCIO</sub> = 1.5, 1.25, 1.2  | ± 15       | ± 15       | %         |

|                                                                               | $\Omega$ and 40- $\Omega$ setting)                                                                                      | V <sub>CCIO</sub> = 1.35            | ± 20       | ± 20       | %         |

| 48-Ω, 60-Ω, 80-Ω, and 120-Ω $R_{\rm S}$                                       | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 120- $\Omega$ setting)   | V <sub>CCIO</sub> = 1.2             | ± 15       | ± 15       | %         |

| 240-Ω R <sub>S</sub>                                                          | Internal series termination with calibration (240- $\Omega$ setting)                                                    | V <sub>CCI0</sub> = 1.2             | ± 20       | ± 20       | %         |

| 30-Ω R <sub>T</sub>                                                           | Internal parallel termination with calibration $(30-\Omega \text{ setting})$                                            | V <sub>CCIO</sub> = 1.5, 1.35, 1.25 | -10 to +40 | -10 to +40 | %         |

| 34- $\Omega$ , 48- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ R <sub>T</sub> | Internal parallel termination with calibration (34- $\Omega$ , 48- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2             | ± 15       | ± 15       | %         |

|                                                                               | •                                                                                                                       | •                                   |            |            | continued |

| Symbol                                                | Description                                                           | Condition (V)                            | Resistance | Unit       |   |

|-------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------|------------|------------|---|

|                                                       |                                                                       |                                          | -E5, -I5   | -E6, -I6   |   |

| 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ $R_T$ | Internal parallel termination with calibration                        | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2 | -10 to +40 | -10 to +40 | % |

|                                                       | (40-Ω, 60-Ω, and 120-Ω setting)                                       | $V_{\rm CCIO} = 1.2^{(17)}$              | ± 15       | ± 15       | % |

| 80-Ω R <sub>T</sub>                                   | Internal parallel termination with calibration (80- $\Omega$ setting) | V <sub>CCI0</sub> = 1.2                  | ± 15       | ± 15       | % |

I/O Standards Support in Intel Cyclone 10 GX Devices

# **OCT Without Calibration Resistance Tolerance Specifications**

## Table 8. OCT Without Calibration Resistance Tolerance Specifications for Intel Cyclone 10 GX Devices

| This table lists the Intel Cyclone 10 GX OCT without calibration resistance tolerance to PVT changes. |  |

|-------------------------------------------------------------------------------------------------------|--|

|-------------------------------------------------------------------------------------------------------|--|

| Symbol                              | Description                                                                             | Condition (V)                            | Resistance | Tolerance | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|------------|-----------|------|

|                                     |                                                                                         |                                          | -E5, -I5   | -E6, -I6  |      |

| 25-Ω and 50-Ω $R_{\rm S}$           | Internal series termination without calibration                                         | V <sub>CCIO</sub> = 3.0, 2.5             | ± 40       | ± 40      | %    |

|                                     | (25- $\Omega$ and 50- $\Omega$ setting)                                                 | V <sub>CCIO</sub> = 1.8, 1.5, 1.2        | ± 50       | ± 50      | %    |

| 34-Ω and 40-Ω $R_{S}$               | Internal series termination without calibration (34- $\Omega$ and 40- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2 | ± 50       | ± 50      | %    |

| 48- $\Omega$ and 60- $\Omega$ $R_S$ | Internal series termination without calibration (48- $\Omega$ and 60- $\Omega$ setting) | V <sub>CCI0</sub> = 1.2                  | ± 50       | ± 50      | %    |

| 120-Ω R <sub>s</sub>                | Internal series termination without calibration (120- $\Omega$ setting)                 | V <sub>CCI0</sub> = 1.2                  | ± 50       | ± 50      | %    |

| 100-Ω R <sub>D</sub>                | Internal differential termination (100- $\Omega$ setting)                               | V <sub>CCIO</sub> = 1.8                  | ± 35       | ± 40      | %    |

<sup>&</sup>lt;sup>(17)</sup> Only applicable to POD12 I/O standard.

| I/O Standard                         | ndard V <sub>CCIO</sub> (V) |      |      | V <sub>SWING(DC)</sub> (V) |      |                                               | <sub>(AC)</sub> (V)                           | V <sub>IX(AC)</sub> (V)     |                      |                             |  |

|--------------------------------------|-----------------------------|------|------|----------------------------|------|-----------------------------------------------|-----------------------------------------------|-----------------------------|----------------------|-----------------------------|--|

|                                      | Min                         | Тур  | Max  | Min                        | Max  | Min                                           | Max                                           | Min                         | Тур                  | Мах                         |  |

| SSTL-135/<br>SSTL-135<br>Class I, II | 1.283                       | 1.35 | 1.45 | 0.18                       | (22) | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> -<br>V <sub>REF</sub> ) | V <sub>CCIO</sub> /2 - 0.15 | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2 + 0.15 |  |

| SSTL-125/<br>SSTL-125<br>Class I, II | 1.19                        | 1.25 | 1.31 | 0.18                       | (22) | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> -<br>V <sub>REF</sub> ) | V <sub>CCIO</sub> /2 - 0.15 | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2 + 0.15 |  |

| SSTL-12/<br>SSTL-12<br>Class I, II   | 1.14                        | 1.2  | 1.26 | 0.16                       | (22) | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> –<br>V <sub>REF</sub> ) | V <sub>REF</sub> - 0.15     | V <sub>CCIO</sub> /2 | V <sub>REF</sub> + 0.15     |  |

| POD12                                | 1.16                        | 1.2  | 1.24 | 0.16                       | _    | 0.3                                           | -                                             | V <sub>REF</sub> - 0.08     | —                    | V <sub>REF</sub> + 0.08     |  |

### **Differential HSTL and HSUL I/O Standards Specifications**

## Table 16. Differential HSTL and HSUL I/O Standards Specifications for Intel Cyclone 10 GX Devices

| I/O Standard V <sub>CCIO</sub> (V) |       | )   | V <sub>DIF(DC)</sub> (V) |                                               | V <sub>DIF(AC)</sub> (V)                      |                                               | V <sub>IX(AC)</sub> (V)                       |                                      |                            | V <sub>CM(DC)</sub> (V)             |                            |                            |                            |

|------------------------------------|-------|-----|--------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------|----------------------------|-------------------------------------|----------------------------|----------------------------|----------------------------|

|                                    | Min   | Тур | Мах                      | Min                                           | Max                                           | Min                                           | Max                                           | Min                                  | Тур                        | Мах                                 | Min                        | Тур                        | Max                        |

| HSTL-18 Class<br>I, II             | 1.71  | 1.8 | 1.89                     | 0.2                                           | _                                             | 0.4                                           | _                                             | 0.78                                 | _                          | 1.12                                | 0.78                       | -                          | 1.12                       |

| HSTL-15 Class<br>I, II             | 1.425 | 1.5 | 1.575                    | 0.2                                           | _                                             | 0.4                                           | _                                             | 0.68                                 | _                          | 0.9                                 | 0.68                       | -                          | 0.9                        |

| HSTL-12 Class<br>I, II             | 1.14  | 1.2 | 1.26                     | 0.16                                          | V <sub>CCIO</sub><br>+ 0.3                    | 0.3                                           | V <sub>CCIO</sub><br>+ 0.48                   | _                                    | $0.5 \times V_{CCIO}$      | _                                   | 0.4 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub> | 0.6 ×<br>V <sub>CCIO</sub> |

| HSUL-12                            | 1.14  | 1.2 | 1.3                      | 2(V <sub>IH(DC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>REF</sub> –<br>V <sub>IH(DC)</sub> ) | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>REF</sub> –<br>V <sub>IH(AC)</sub> ) | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | 0.5 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub><br>+0.12 | 0.4 ×<br>V <sub>CCIO</sub> | 0.5 ×<br>V <sub>CCIO</sub> | 0.6 ×<br>V <sub>CCIO</sub> |

<sup>&</sup>lt;sup>(22)</sup> The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

#### Table 25.Receiver Specifications

| Symbol/Description                                                                                              | Condition                | Min  | Тур                           | Мах                           | Unit               |

|-----------------------------------------------------------------------------------------------------------------|--------------------------|------|-------------------------------|-------------------------------|--------------------|

| Supported I/O Standards                                                                                         | -                        | High | Speed Differential I/O, CML , | Differential LVPECL , and LVE | )S <sup>(35)</sup> |

| Absolute $V_{MAX}$ for a receiver pin <sup>(36)</sup>                                                           | _                        | _    | _                             | 1.2                           | V                  |

| Absolute $V_{MIN}$ for a receiver pin <sup>(37)</sup>                                                           | _                        | -0.4 | _                             | _                             | V                  |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) before device<br>configuration | _                        | _    | _                             | 1.6                           | v                  |

| Maximum peak-to-peak                                                                                            | $V_{CCR_{GXB}} = 0.95 V$ | _    | —                             | 2.4                           | V                  |

| differential input voltage $V_{ID}$ (diff p-p) after device configuration                                       | $V_{CCR_{GXB}} = 1.03 V$ | _    | _                             | 2.0                           | V                  |

| Minimum differential eye<br>opening at receiver serial<br>input pins <sup>(38)</sup>                            | _                        | 50   | _                             | _                             | mV                 |

| Differential on-chip                                                                                            | 85-Ω setting             | _    | 85 ± 30%                      | _                             | Ω                  |

| termination resistors                                                                                           | 100-Ω setting            | -    | 100 ± 30%                     | _                             | Ω                  |

| V <sub>ICM</sub> (AC and DC coupled)                                                                            | $V_{CCR_{GXB}} = 0.95 V$ | -    | 600                           | _                             | mV                 |

| (39)                                                                                                            | $V_{CCR_{GXB}} = 1.03 V$ | -    | 700                           | _                             | mV                 |

|                                                                                                                 |                          |      |                               |                               | continued          |

<sup>(35)</sup> CML, Differential LVPECL, and LVDS are only used on AC coupled links.

- <sup>(36)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

- <sup>(37)</sup> The device cannot tolerate prolonged operation at this absolute minimum.

- <sup>(38)</sup> The differential eye opening specification at the receiver input pins assumes that Receiver Equalization is disabled. If you enable Receiver Equalization, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

- <sup>(39)</sup> Intel Cyclone 10 GX devices support DC coupling to other Intel Cyclone 10 GX devices and other devices with a transmitter that has matching common mode voltage.

| Symbol/Description                          | Condition                                  | Min   | Тур | Мах  | Unit |

|---------------------------------------------|--------------------------------------------|-------|-----|------|------|

| t <sub>LTR</sub> <sup>(40)</sup>            | -                                          | _     | -   | 10   | μs   |

| t <sub>LTD</sub> <sup>(41)</sup>            | -                                          | 4     | —   | —    | μs   |

| t <sub>LTD_manual</sub> <sup>(42)</sup>     | -                                          | 4     | -   | -    | μs   |

| t <sub>LTR_LTD_manual</sub> <sup>(43)</sup> | -                                          | 15    | -   | -    | μs   |

| Run Length                                  | -                                          | -     | -   | 200  | UI   |

| CDR PPM tolerance                           | PCIe-only                                  | -300  | -   | 300  | PPM  |

|                                             | All other protocols                        | -1000 | -   | 1000 | PPM  |

| Programmable DC Gain                        | Setting = 0-4                              | 0     | -   | 10   | dB   |

| Programmable AC Gain at                     | Setting = 0-28<br>$V_{CCR_{GXB}} = 0.95 V$ | 0     | _   | 19   | dB   |

| High Gain mode and Data<br>Rate ≤ 6 Gbps    | Setting = 0-28<br>$V_{CCR_GXB}$ = 1.03 V   | 0     | _   | 21   | dB   |

### Table 26.Transmitter Specifications

| Symbol/Description                         | Condition    | Min | Тур      | Мах | Unit |  |  |

|--------------------------------------------|--------------|-----|----------|-----|------|--|--|

| Supported I/O Standards                    | _            | ŀ   | _        |     |      |  |  |

| Differential on-chip termination resistors | 85-Ω setting | _   | 85 ± 20% | _   | Ω    |  |  |

|                                            |              |     |          |     |      |  |  |

$^{(40)}$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$^{(41)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

$t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

- $^{(43)}$  t<sub>LTR\_LTD\_manual</sub> is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

- <sup>(44)</sup> High Speed Differential I/O is the dedicated I/O standard for the transmitter in Intel Cyclone 10 GX transceivers.

| Symbol/Description            | Condition                                                                 | Min | Тур       | Мах | Unit |

|-------------------------------|---------------------------------------------------------------------------|-----|-----------|-----|------|

|                               | 100-Ω setting                                                             | -   | 100 ± 20% | _   | Ω    |

|                               | $V_{CCT\_GXB} = 0.95 V$                                                   | _   | 450       | _   | mV   |

| V <sub>OCM</sub> (AC coupled) | $V_{CCT\_GXB} = 1.03 V$                                                   | —   | 500       | —   | mV   |

|                               | $V_{CCT\_GXB} = 0.95 V$                                                   | —   | 450       | —   | mV   |

| V <sub>OCM</sub> (DC coupled) | $V_{CCT\_GXB} = 1.03 V$                                                   | —   | 500       | —   | mV   |

| Rise time <sup>(45)</sup>     | 20% to 80%                                                                | 20  | _         | 130 | ps   |

| Fall time <sup>(45)</sup>     | 80% to 20%                                                                | 20  | -         | 130 | ps   |

| Intra-differential pair skew  | TX V <sub>CM</sub> = 0.5 V and slew rate setting of SLEW_R5 $^{\rm (46)}$ | _   | —         | 15  | ps   |

# Table 27.Typical Transmitter Vod Settings

| Symbol                                                                          | V <sub>OD</sub> Setting | V <sub>OD</sub> -to-V <sub>CCT_GXB</sub> Ratio |

|---------------------------------------------------------------------------------|-------------------------|------------------------------------------------|

|                                                                                 | 31                      | 1.00                                           |

|                                                                                 | 30                      | 0.97                                           |

|                                                                                 | 29                      | 0.93                                           |

|                                                                                 | 28                      | 0.90                                           |

|                                                                                 | 27                      | 0.87                                           |

| $V_{OD}$ differential value = $V_{OD}$ -to- $V_{CCT_GXB}$ ratio x $V_{CCT_GXB}$ | 26                      | 0.83                                           |

|                                                                                 | 25                      | 0.80                                           |

|                                                                                 | 24                      | 0.77                                           |

|                                                                                 | 23                      | 0.73                                           |

|                                                                                 | 22                      | 0.70                                           |

|                                                                                 |                         | continued                                      |

<sup>&</sup>lt;sup>(45)</sup> The Intel Quartus Prime software automatically selects the appropriate slew rate depending on the design configurations.

<sup>&</sup>lt;sup>(46)</sup> SLEW\_R1 is the slowest and SLEW\_R5 is the fastest. SLEW\_R6 and SLEW\_R7 are not used.

| Symbol                                 | Parameter                                                                                                       | Condition                     | Min | Тур | Мах  | Unit      |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|------|-----------|

| t <sub>LOCK</sub>                      | Time required to lock from end-of-device configuration or deassertion of pll_powerdown                          | -                             | _   | _   | 1    | ms        |

| t <sub>DLOCK</sub>                     | Time required to lock dynamically (after<br>switchover or reconfiguring any non-post-<br>scale counters/delays) | _                             | _   | _   | 1    | ms        |

| f <sub>CLBW</sub>                      | PLL closed-loop bandwidth                                                                                       | _                             | 0.3 | -   | 4    | MHz       |

| t <sub>PLL_PSERR</sub>                 | Accuracy of PLL phase shift                                                                                     | _                             | _   | -   | 50   | ps        |

| t <sub>ARESET</sub>                    | Minimum pulse width on the pll_powerdown signal                                                                 | _                             | 10  | _   | _    | ns        |

| t <sub>INCCJ</sub> <sup>(50)(51)</sup> | Input clock cycle-to-cycle jitter                                                                               | $F_{REF} \ge 100 \text{ MHz}$ | _   | _   | 0.13 | UI (p-p)  |

|                                        |                                                                                                                 | F <sub>REF</sub> < 100 MHz    | _   | _   | 650  | ps (p-p)  |

| t <sub>outpj</sub> <sup>(52)</sup>     | Period jitter for clock output                                                                                  | $F_{OUT} \ge 100 \text{ MHz}$ | _   | _   | 600  | ps (p-p)  |

|                                        |                                                                                                                 | F <sub>OUT</sub> < 100 MHz    | _   | _   | 60   | mUI (p-p) |

| t <sub>outcc</sub> (52)                | Cycle-to-cycle jitter for clock output                                                                          | $F_{OUT} \ge 100 \text{ MHz}$ | _   | -   | 600  | ps (p-p)  |

|                                        |                                                                                                                 | F <sub>OUT</sub> < 100 MHz    | _   | _   | 60   | mUI (p-p) |

| dK <sub>BIT</sub>                      | Bit number of Delta Sigma Modulator (DSM)                                                                       | _                             | _   | 32  | _    | bit       |

Memory Output Clock Jitter Specifications on page 43

Provides more information about the external memory interface clock output jitter specifications.

- <sup>(51)</sup>  $F_{REF}$  is  $f_{IN}/N$ , specification applies when N = 1.

- <sup>(52)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in Memory Output Clock Jitter Specification for Intel Cyclone 10 GX Devices table.

<sup>&</sup>lt;sup>(50)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.

## **I/O PLL Specifications**

## Table 31. I/O PLL Specifications for Intel Cyclone 10 GX Devices

| Symbol                   | Parameter                                                                       | Condition          | Min | Тур | Мах      | Unit       |

|--------------------------|---------------------------------------------------------------------------------|--------------------|-----|-----|----------|------------|

| f <sub>IN</sub>          | Input clock frequency                                                           | -5 speed grade     | 10  | -   | 700 (53) | MHz        |

|                          |                                                                                 | -6 speed grade     | 10  | -   | 650 (53) | MHz        |

| f <sub>INPFD</sub>       | Input clock frequency to the PFD                                                | _                  | 10  | -   | 325      | MHz        |

| f <sub>CASC_INPFD</sub>  | Input clock frequency to the PFD of destination cascade PLL                     | _                  | 10  | _   | 60       | MHz        |

| f <sub>VCO</sub>         | PLL VCO operating range                                                         | -5 speed grade     | 600 | -   | 1434     | MHz        |

|                          |                                                                                 | -6 speed grade     | 600 | -   | 1250     | MHz        |

| f <sub>CLBW</sub>        | PLL closed-loop bandwidth                                                       | _                  | 0.1 | -   | 8        | MHz        |

| t <sub>einduty</sub>     | Input clock or external feedback clock input duty cycle                         | _                  | 40  | _   | 60       | %          |

| f <sub>OUT</sub>         | Output frequency for internal global or regional clock (C counter)              | -5, -6 speed grade | _   | _   | 644      | MHz        |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock output                                      | -5 speed grade     | _   | -   | 720      | MHz        |

|                          |                                                                                 | -6 speed grade     | _   | -   | 650      | MHz        |

| toutduty                 | Duty cycle for dedicated external clock output (when set to 50%)                | _                  | 45  | 50  | 55       | %          |

| t <sub>FCOMP</sub>       | External feedback clock compensation time                                       | _                  | _   | -   | 10       | ns         |

| f <sub>DYCONFIGCLK</sub> | Dynamic configuration clock for mgmt_clk and scanclk                            | _                  | _   | -   | 100      | MHz        |

| t <sub>LOCK</sub>        | Time required to lock from end-of-device configuration or deassertion of areset | _                  | _   | _   | 1        | ms         |

|                          |                                                                                 |                    |     |     | 1        | continued. |

<sup>(53)</sup> This specification is limited by the I/O maximum frequency. The maximum achievable I/O frequency is different for each I/O standard and is depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

## **DSP Block Specifications**

## Table 32. DSP Block Performance Specifications for Intel Cyclone 10 GX Devices

| Mode                                                                      |     | Performance |     |     |     |  |

|---------------------------------------------------------------------------|-----|-------------|-----|-----|-----|--|

|                                                                           | -E5 | -15         | -E6 | -16 |     |  |

| Fixed-point 18 × 19 multiplication mode                                   | 456 | 438         | 364 | 346 | MHz |  |

| Fixed-point 27 $\times$ 27 multiplication mode                            | 450 | 434         | 358 | 344 | MHz |  |

| Fixed-point 18 $	imes$ 18 multiplier adder mode                           | 459 | 440         | 370 | 351 | MHz |  |

| Fixed-point 18 $\times$ 18 multiplier adder summed with 36-bit input mode | 444 | 422         | 349 | 326 | MHz |  |

| Fixed-point 18 $\times$ 19 systolic mode                                  | 459 | 440         | 370 | 351 | MHz |  |

| Complex 18 × 19 multiplication mode                                       | 456 | 438         | 364 | 346 | MHz |  |

| Floating point multiplication mode                                        | 447 | 427         | 347 | 326 | MHz |  |

| Floating point adder or subtract mode                                     | 388 | 369         | 288 | 266 | MHz |  |

| Floating point multiplier adder or subtract mode                          | 386 | 368         | 290 | 270 | MHz |  |

| Floating point multiplier accumulate mode                                 | 418 | 393         | 326 | 294 | MHz |  |

| Floating point vector one mode                                            | 404 | 382         | 306 | 282 | MHz |  |

| Floating point vector two mode                                            | 383 | 367         | 293 | 278 | MHz |  |

## **Memory Block Specifications**

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL and set to **50%** output duty cycle. Use the Intel Quartus Prime software to report timing for the memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in  $f_{MAX}$ .

#### **External Temperature Sensing Diode Specifications**

#### Table 35. External Temperature Sensing Diode Specifications for Intel Cyclone 10 GX Devices

- The typical value is at 25°C.

- Diode accuracy improves with lower injection current.

- Absolute accuracy is dependent on third party external diode ADC and integration specifics.

| Description                              | Min | Тур  | Мах | Unit |

|------------------------------------------|-----|------|-----|------|

| I <sub>bias</sub> , diode source current | 10  | —    | 100 | μA   |

| V <sub>bias</sub> , voltage across diode | 0.3 | —    | 0.9 | V    |

| Series resistance                        | -   | —    | < 1 | Ω    |

| Diode ideality factor                    | _   | 1.03 | _   | _    |

# Internal Voltage Sensor Specifications

### Table 36. Internal Voltage Sensor Specifications for Intel Cyclone 10 GX Devices

|                          | Parameter                            | Minimum | Typical | Maximum | Unit |

|--------------------------|--------------------------------------|---------|---------|---------|------|

| Resolution               |                                      | —       | —       | 6       | Bit  |

| Sampling rate            |                                      | —       | _       | 500     | Ksps |

| Differential non-lineari | zy (DNL)                             | —       | _       | ±1      | LSB  |

| Integral non-linearity ( | INL)                                 | —       | —       | ±1      | LSB  |

| Gain error               |                                      | —       | _       | ±1      | %    |

| Offset error             |                                      | —       | —       | ±1      | LSB  |

| Input capacitance        |                                      | —       | 20      | _       | pF   |

| Clock frequency          |                                      | 0.1     | —       | 11      | MHz  |

| Unipolar Input Mode      | Input signal range for Vsigp         | 0       | —       | 1.5     | V    |

|                          | Common mode voltage on Vsign         | 0       | _       | 0.25    | V    |

|                          | Input signal range for Vsigp – Vsign | 0       | _       | 1.25    | V    |

| Symbol              |                                      | Condition                                            |      | -E5, -I5 | 5                                   |      | -E6, -I6 | 5                                   | Unit  |

|---------------------|--------------------------------------|------------------------------------------------------|------|----------|-------------------------------------|------|----------|-------------------------------------|-------|

|                     |                                      |                                                      | Min  | Тур      | Max                                 | Min  | Тур      | Мах                                 |       |

|                     | TCCS (64)(59)                        | True Differential I/O<br>Standards                   | _    | -        | 150                                 | _    | -        | 150                                 | ps    |

| Receiver            | True Differential<br>I/O Standards - | SERDES factor<br>J = 4 to 10 <sup>(60)(61)(62)</sup> | 150  | -        | 1434                                | 150  | -        | 1250                                | Mbps  |

|                     | f <sub>HSDRDPA</sub> (data<br>rate)  | SERDES factor<br>J = 3 (60)(61)(62)                  | 150  | -        | 1076                                | 150  | -        | 938                                 | Mbps  |

|                     | f <sub>HSDR</sub> (data rate)        | SERDES factor J = 3 to 10                            | (62) | -        | (66)                                | (62) | _        | (66)                                | Mbps  |

|                     | (without<br>DPA) <sup>(59)</sup>     | SERDES factor J = 2, uses<br>DDR registers           | (62) | -        | (63)                                | (62) | -        | (63)                                | Mbps  |

|                     |                                      | SERDES factor J = 1, uses<br>DDR registers           | (62) | -        | (63)                                | (62) | -        | (63)                                | Mbps  |

| DPA (FIFO mode)     | DPA run length                       | _                                                    | _    | -        | 10000                               | 1    | _        | 10000                               | UI    |

| DPA (soft CDR mode) | DPA run length                       | SGMII/GbE protocol                                   | _    | -        | 5                                   | _    | _        | 5                                   | UI    |

|                     |                                      | All other protocols                                  | _    | -        | 50 data<br>transition<br>per 208 UI | _    | _        | 50 data<br>transition<br>per 208 UI | _     |

| Soft CDR mode       | Soft-CDR ppm<br>tolerance            | _                                                    | _    | -        | 300                                 | _    | -        | 300                                 | ± ppm |

| Non DPA mode        | Sampling Window                      | -                                                    | _    | -        | 300                                 | _    | -        | 300                                 | ps    |

$<sup>^{(65)}</sup>$  This applies to default pre-emphasis and V<sub>OD</sub> settings only.

<sup>&</sup>lt;sup>(66)</sup> You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

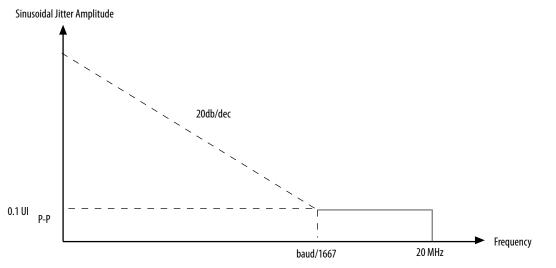

# LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications

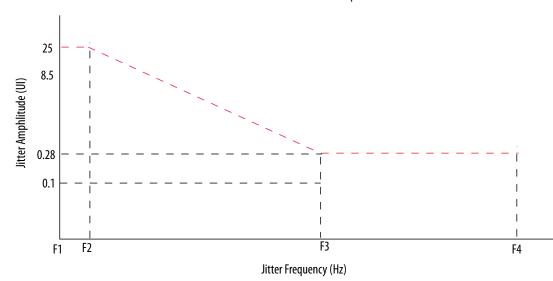

## Figure 3. LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications for a Data Rate Equal to 1.4 Gbps

LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification

Table 39.

LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate Equal to 1.4 Gbps

| Jitter Freq | Sinusoidal Jitter (UI) |       |

|-------------|------------------------|-------|

| F1          | 10,000                 | 25.00 |

| F2          | 17,565                 | 25.00 |

| F3          | 1,493,000              | 0.28  |

| F4          | 50,000,000             | 0.28  |

## Figure 4. LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications for a Data Rate Less than 1.4 Gbps

## Memory Standards Supported by the Hard Memory Controller

### Table 40. Memory Standards Supported by the Hard Memory Controller for Intel Cyclone 10 GX Devices

This table lists the overall capability of the hard memory controller. For specific details, refer to the External Memory Interface Spec Estimator.

| Memory Standard | Rate Support | Speed Grade | Ping Pong PHY | Maximum Frequency (MHz) |              |  |

|-----------------|--------------|-------------|---------------|-------------------------|--------------|--|

|                 |              |             | Support       | I/O Bank                | 3 V I/O Bank |  |

| DDR3 SDRAM      | Half rate    | -5          | Yes           | 533                     | 225          |  |

|                 |              |             | -             | 533                     | 225          |  |

|                 |              | -6          | Yes           | 466                     | 166          |  |

|                 |              |             | -             | 466                     | 166          |  |

|                 | Quarter rate | -5          | Yes           | 933                     | 450          |  |

|                 |              |             | -             | 933                     | 450          |  |

|                 |              | -6          | Yes           | 933                     | 333          |  |

|                 |              |             |               |                         | continued    |  |

| Memory Standard | Rate Support | Speed Grade | Ping Pong PHY | Maximum Fre | quency (MHz) |

|-----------------|--------------|-------------|---------------|-------------|--------------|

|                 |              |             | Support       | I/O Bank    | 3 V I/O Bank |

|                 |              |             | _             | 933         | 333          |

| DDR3L SDRAM     | Half rate    | -5          | Yes           | 533         | 225          |

|                 |              |             | _             | 533         | 225          |

|                 |              | -6          | Yes           | 466         | 166          |

|                 |              |             | _             | 466         | 166          |

|                 | Quarter rate | -5          | Yes           | 933         | 450          |

|                 |              |             | -             | 933         | 450          |

|                 |              | -6          | Yes           | 933         | 333          |

|                 |              |             | -             | 933         | 333          |

| LPDDR3 SDRAM    | Half rate    | -5          | -             | 400         | 225          |

|                 |              | -6          | _             | 333         | 166          |

|                 | Quarter rate | -5          | -             | 800         | 450          |

|                 |              | -6          | -             | 666         | 333          |

External Memory Interface Spec Estimator

Provides the specific details of the memory standards supported.

## **DLL Range Specifications**

#### Table 41. DLL Frequency Range Specifications for Intel Cyclone 10 GX Devices

Intel Cyclone 10 GX devices support memory interface frequencies lower than 600 MHz, although the reference clock that feeds the DLL must be at least 600 MHz. To support interfaces below 600 MHz, multiply the reference clock feeding the DLL to ensure the frequency is within the supported range.

| Parameter                     | Performance (for All Speed Grades) | Unit |

|-------------------------------|------------------------------------|------|

| DLL operating frequency range | 600 - 1333                         | MHz  |

| Symbol                             | Parameter                                         | Minimum                                       | Maximum | Unit |

|------------------------------------|---------------------------------------------------|-----------------------------------------------|---------|------|

| t <sub>CF2CK</sub> <sup>(72)</sup> | nCONFIG high to first rising edge on DCLK         | 3,010                                         | _       | μs   |

| t <sub>ST2CK</sub> <sup>(72)</sup> | nSTATUS high to first rising edge of DCLK         | 10                                            | _       | μs   |

| t <sub>DSU</sub>                   | DATA[] setup time before rising edge on DCLK      | 5.5                                           | _       | ns   |

| t <sub>DH</sub>                    | DATA[] hold time after rising edge on DCLK        | 0                                             | _       | ns   |

| t <sub>CH</sub>                    | DCLK high time                                    | $0.45 \times 1/f_{MAX}$                       | _       | S    |

| t <sub>CL</sub>                    | DCLK low time                                     | $0.45 \times 1/f_{MAX}$                       | _       | s    |

| t <sub>CLK</sub>                   | DCLK period                                       | 1/f <sub>MAX</sub>                            | _       | S    |

| f <sub>MAX</sub>                   | DCLK frequency (FPP ×8/×16/×32)                   | -                                             | 100     | MHz  |

| t <sub>CD2UM</sub>                 | CONF_DONE high to user mode (73)                  | 175                                           | 830     | μs   |

| t <sub>CD2CU</sub>                 | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK<br>period                    | _       | _    |

| t <sub>CD2UMC</sub>                | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> +<br>(600 × CLKUSR period) |         |      |

### **Related Information**

FPP Configuration Timing

Provides the FPP configuration timing waveforms.

<sup>&</sup>lt;sup>(71)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(72)</sup> If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

<sup>&</sup>lt;sup>(73)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

| Symbol                             | Parameter                                                          | Minimum                             | Maximum   | Unit |

|------------------------------------|--------------------------------------------------------------------|-------------------------------------|-----------|------|

| t <sub>CF2CK</sub> <sup>(80)</sup> | nCONFIG high to first rising edge on DCLK                          | 3,010                               | _         | μs   |

| t <sub>ST2CK</sub> <sup>(80)</sup> | nSTATUS high to first rising edge of DCLK                          | 10                                  | _         | μs   |

| t <sub>DSU</sub>                   | DATA[] setup time before rising edge on DCLK                       | 5.5                                 | _         | ns   |

| t <sub>DH</sub>                    | DATA[] hold time after rising edge on DCLK                         | 0                                   | _         | ns   |

| t <sub>CH</sub>                    | DCLK high time                                                     | $0.45 \times 1/f_{MAX}$             | _         | S    |

| t <sub>CL</sub>                    | DCLK low time                                                      | $0.45 \times 1/f_{MAX}$             | _         | S    |

| t <sub>CLK</sub>                   | DCLK period                                                        | 1/f <sub>MAX</sub>                  | _         | S    |

| f <sub>MAX</sub>                   | DCLK frequency                                                     | -                                   | 125       | MHz  |

| t <sub>CD2UM</sub>                 | CONF_DONE high to user mode <sup>(81)</sup>                        | 175                                 | 830       | μs   |

| t <sub>CD2CU</sub>                 | CONF_DONE high to CLKUSR enabled     4 × maximum DCLK       period |                                     | _         | -    |

| t <sub>CD2UMC</sub>                | CONF_DONE high to user mode with CLKUSR option on                  | $t_{CD2CU}$ + (600 × CLKUSR period) | JKUSR — — |      |

### **Related Information**

PS Configuration Timing

Provides the PS configuration timing waveform.

<sup>(81)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

<sup>&</sup>lt;sup>(78)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(79)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(80)</sup> If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

# **Minimum Configuration Time Estimation**

## Table 55. Minimum Configuration Time Estimation for Intel Cyclone 10 GX Devices

The estimated values are based on the uncompressed configuration bit stream sizes in the Configuration Bit Stream Sizes for Intel Cyclone 10 GX Devices table.

| Variant             | Product Line | Active Serial <sup>(84)</sup> |            |                                    | Fast Passive Parallel <sup>(85)</sup> |            |                                       |

|---------------------|--------------|-------------------------------|------------|------------------------------------|---------------------------------------|------------|---------------------------------------|

|                     |              | Width                         | DCLK (MHz) | Minimum Configuration<br>Time (ms) | Width                                 | DCLK (MHz) | Minimum<br>Configuration Time<br>(ms) |

| Intel Cyclone 10 GX | GX 085       | 4                             | 100        | 204.81                             | 32                                    | 100        | 25.60                                 |

|                     | GX 105       | 4                             | 100        | 204.81                             | 32                                    | 100        | 25.60                                 |

|                     | GX 150       | 4                             | 100        | 204.81                             | 32                                    | 100        | 25.60                                 |

|                     | GX 220       | 4                             | 100        | 204.81                             | 32                                    | 100        | 25.60                                 |

#### **Related Information**

- Configuration Files on page 52

- DCLK Frequency Specification in the AS Configuration Scheme on page 50 Provides the DCLK frequency using internal oscillator.

<sup>(84)</sup> The minimum configuration time is calculated based on DCLK frequency of 100 MHz. Only external CLKUSR may guarantee the frequency accuracy of 100 MHz. If you use internal oscillator of 100 MHz, you may not get the actual frequency of 100 MHz. For the DCLK frequency using internal oscillator, refer to the DCLK Frequency Specification in the AS Configuration Scheme table.

<sup>&</sup>lt;sup>(85)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

| Date                     | Version    | Changes                                                                                                                                                                                                                                   |

|--------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2017 2017.11.10 |            | Changed the full symbol names for V <sub>CCR_GXB</sub> and V <sub>CCT_GXB</sub> , and changed the description for V <sub>CCH_GXB</sub> in the <i>Transceiver Power Supply Operating Conditions for Intel Cyclone 10 GX Devices</i> table. |

|                          |            | • Removed note from the Transceiver Power Supply Operating Conditions section.                                                                                                                                                            |

|                          |            | Added a footnote in the <i>Reference Clock Specifications</i> table.                                                                                                                                                                      |

|                          |            | • Removed the "Programmable AC Gain at High Gain mode and Data Rate ≤ 12.5 Gbps" parameter from the <i>Receiver Specifications</i> table.                                                                                                 |

|                          |            | • Changed the channel span descriptions for the x1 and x6 clock networks in the <i>Transceiver Clock Network Maximum Data Rate Specifications</i> table.                                                                                  |

|                          |            | • Changed the description of the VOD ratio in the Typical Transmitter V <sub>OD</sub> Settings table.                                                                                                                                     |

|                          |            | • Changed the specifications for CDR PPM deviation limit in the Receiver Specifications table.                                                                                                                                            |

|                          |            | • Updated the description for V <sub>CCT_GXB</sub> , V <sub>CCR_GXB</sub> , and V <sub>CCH_GXB</sub> .                                                                                                                                    |

|                          |            | • Added note to V <sub>I</sub> in the <i>Recommended Operating Conditions for Intel Cyclone 10 GX Devices</i> table.                                                                                                                      |

|                          |            | • Updated notes to RSDS and Mini-LVDS in the Differential I/O Standards Specifications for Intel Cyclone 10 GX Devices table.                                                                                                             |

|                          |            | • Updated f <sub>VCO</sub> specifications in the <i>Fractional PLL Specifications for Intel Cyclone 10 GX Devices</i> table.                                                                                                              |

|                          |            | <ul> <li>Updated temperature range from "-40 to 125°C" to "-40 to 100°C" in the Internal Temperature Sensing Diode<br/>Specifications for Intel Cyclone 10 GX Devices table.</li> </ul>                                                   |

|                          |            | • Updated the description for the Memory Output Clock Jitter Specifications for Intel Cyclone 10 GX Devices table.                                                                                                                        |

|                          |            | Updated the following IP cores name:                                                                                                                                                                                                      |

|                          |            | - Remote Update Intel FPGA                                                                                                                                                                                                                |

|                          |            | <ul> <li>PHYLite for Parallel Interfaces Intel Cyclone 10 FPGA</li> </ul>                                                                                                                                                                 |

|                          |            | Removed automotive-grade information.                                                                                                                                                                                                     |

|                          |            | Removed Preliminary tags.                                                                                                                                                                                                                 |

| May 2017                 | 2017.05.08 | Initial release.                                                                                                                                                                                                                          |