Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | S08                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 40MHz                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                        |

| Peripherals                | LVD, POR, PWM, WDT                                        |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                      |

| Supplier Device Package    | 24-QFN-EP (4x4)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08sh4cfk |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

# **List of Chapters**

| Chapter 1  | Device Overview19                                |

|------------|--------------------------------------------------|

| Chapter 2  | Pins and Connections                             |

| Chapter 3  | Modes of Operation                               |

| Chapter 4  | Memory                                           |

| Chapter 5  | Resets, Interrupts, and General System Control59 |

| Chapter 6  | Parallel Input/Output Control75                  |

| Chapter 7  | Central Processor Unit (S08CPUV2)93              |

| Chapter 8  | Analog Comparator 5-V (S08ACMPV2)113             |

| Chapter 9  | Analog-to-Digital Converter (S08ADCV1)121        |

| Chapter 10 | Internal Clock Source (S08ICSV2)149              |

| Chapter 11 | Inter-Integrated Circuit (S08IICV2)163           |

| Chapter 12 | Modulo Timer (S08MTIMV1)183                      |

| Chapter 13 | Real-Time Counter (S08RTCV1)193                  |

| Chapter 14 | Serial Communications Interface (S08SCIV4)203    |

| Chapter 15 | Serial Peripheral Interface (S08SPIV3)223        |

| Chapter 16 | Timer Pulse-Width Modulator (S08TPMV3)239        |

| Chapter 17 | Development Support                              |

| Appendix A | Electrical Characteristics                       |

| Appendix B | Ordering Information and Mechanical Drawings     |

Chapter 4 Memory

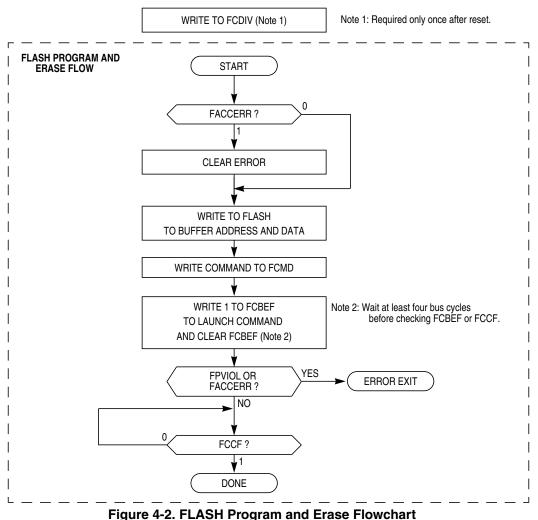

### rigure +-2. I EASIT Program and Erase Prowe

### 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

### Table 4-11. FPROT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>FPS | <b>FLASH Protect Select Bits</b> — When FPDIS = 0, this 7-bit field determines the ending address of unprotected FLASH locations at the high address end of the FLASH. Protected FLASH locations cannot be erased or programmed. |

| 0<br>FPDIS | <ul> <li>FLASH Protection Disable</li> <li>0 FLASH block specified by FPS[7:1] is block protected (program and erase not allowed).</li> <li>1 No FLASH block is protected.</li> </ul>                                            |

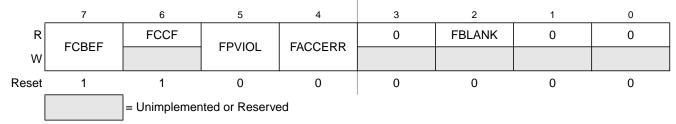

# 4.7.5 FLASH Status Register (FSTAT)

### Figure 4-9. FLASH Status Register (FSTAT)

### Table 4-12. FSTAT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FCBEF  | <ul> <li>FLASH Command Buffer Empty Flag — The FCBEF bit is used to launch commands. It also indicates that the command buffer is empty so that a new command sequence can be executed when performing burst programming. The FCBEF bit is cleared by writing a 1 to it or when a burst program command is transferred to the array for programming. Only burst program commands can be buffered.</li> <li>0 Command buffer is full (not ready for additional commands).</li> <li>1 A new burst program command can be written to the command buffer.</li> </ul> |

| 6<br>FCCF   | FLASH Command Complete Flag — FCCF is set automatically when the command buffer is empty and no command is being processed. FCCF is cleared automatically when a new command is started (by writing 1 to FCBEF to register a command). Writing to FCCF has no meaning or effect.         0       Command in progress         1       All commands complete                                                                                                                                                                                                       |

| 5<br>FPVIOL | <ul> <li>Protection Violation Flag — FPVIOL is set automatically when a command is written that attempts to erase or program a location in a protected block (the erroneous command is ignored). FPVIOL is cleared by writing a 1 to FPVIOL.</li> <li>0 No protection violation.</li> <li>1 An attempt was made to erase or program a protected location.</li> </ul>                                                                                                                                                                                             |

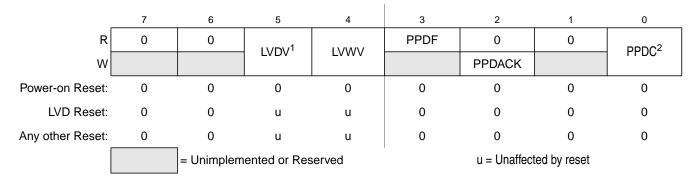

# 5.7.8 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

### Figure 5-10. System Power Management Status and Control 2 Register (SPMSC2)

### Table 5-11. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-12.                                        |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-12.                                                                                            |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |

### Table 5-12. LVD and LVW trip point typical values<sup>1</sup>

| LVDV:LVWV | LVW Trip Point             | LVD Trip Point             |

|-----------|----------------------------|----------------------------|

| 0:0       | V <sub>LVW0</sub> = 2.74 V | V <sub>LVD0</sub> = 2.56 V |

| 0:1       | V <sub>LVW1</sub> = 2.92 V |                            |

| 1:0       | V <sub>LVW2</sub> = 4.3 V  | V <sub>LVD1</sub> = 4.0 V  |

| 1:1       | V <sub>LVW3</sub> = 4.6 V  |                            |

<sup>1</sup> See Electrical Characteristics appendix for minimum and maximum values.

Chapter 5 Resets, Interrupts, and General System Control

Chapter 7 Central Processor Unit (S08CPUV2)

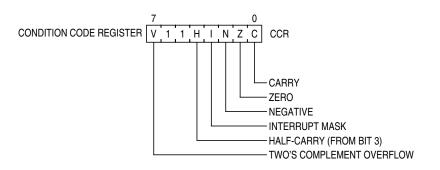

### Figure 7-2. Condition Code Register

### Table 7-1. CCR Register Field Descriptions

| Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>V | Two's Complement Overfl w Flag — The CPU sets the overflow flag when a two's complement overflow occurs.         The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.         0 No overflow         1 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>H | <ul> <li>Half-Carry Flag — The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the result to a valid BCD value.</li> <li>0 No carry between bits 3 and 4</li> <li>1 Carry between bits 3 and 4</li> </ul>                                                                            |

| 3      | Interrupt Mask Bit — When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service routine is executed.<br>Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening interrupt, provided I was set.<br>0 Interrupts disabled |

| 2<br>N | <ul> <li>Negative Flag — The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value causes N to be set if the most significant bit of the loaded or stored value was 1.</li> <li>0 Non-negative result</li> <li>1 Negative result</li> </ul>                                                                                                                                                                                                                                                                     |

| 1<br>Z | <ul> <li>Zero Flag — The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of 0x00 or 0x0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the loaded or stored value was all 0s.</li> <li>Non-zero result</li> <li>Zero result</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

| 0<br>C | <ul> <li>Carry/Borrow Flag — The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.</li> <li>0 No carry out of bit 7</li> <li>1 Carry out of bit 7</li> </ul>                                                                                                                                                                                                                                                                               |

Chapter 7 Central Processor Unit (S08CPUV2)

# 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

| Source<br>Form                                                                                                  | Operation                                                                               | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                    | Affect<br>on CCR      |            |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|-----------------------|------------|

| Form                                                                                                            |                                                                                         | Add Add                                             |                                                                                  | S                               | Details                                                  | <b>V</b> 1 1 <b>H</b> | INZC       |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry<br>A $\leftarrow$ (A) + (M) + (C)                                        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A9 ii<br>B9 dd<br>C9 hh ll<br>D9 ee ff<br>E9 ff<br>F9<br>9E D9 ee ff<br>9E E9 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | \$11\$                | - ↓ ↓ ↓    |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry<br>A $\leftarrow$ (A) + (M)                                           | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AB ii<br>BB dd<br>CB hh 11<br>DB ee ff<br>EB ff<br>FB<br>9E DB ee ff<br>9E EB ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rpp<br>rfp<br>prpp<br>prpp   | \$11\$                | - \$ \$ \$ |

| AIS #opr8i                                                                                                      | Add Immediate Value (Signed) to Stack Pointer $SP \leftarrow (SP) + (M)$                | IMM                                                 | A7 ii                                                                            | 2                               | qq                                                       | - 1 1 -               |            |

| AIX #opr8i                                                                                                      | Add Immediate Value (Signed) to<br>Index Register (H:X)<br>H:X $\leftarrow$ (H:X) + (M) | ІММ                                                 | AF ii                                                                            | 2                               | qq                                                       | - 1 1 -               |            |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP | Logical AND<br>A ← (A) & (M)                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | 011-                  | - \$ \$ -  |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL oprx8,SP                                              | Arithmetic Shift Left                                                                   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwp                     | ↓ 1 1 –               | - ↓ ↓ ↓    |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                              | Arithmetic Shift Right                                                                  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp               | ↓11-                  | - ↓ ↓ ↓    |

Table 7-2. Instruction Set Summary (Sheet 1 of 9)

Chapter 8 Analog Comparator (S08ACMPV2)

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$  and compares it to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$  the cold slope value is applied in Equation 9-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$  the hot slope value is applied in Equation 9-1.

Calibrating at 25°C will improve accuracy to  $\pm 4.5$ °C.

Calibration at three points, -40°C, 25°C, and 125°C will improve accuracy to  $\pm 2.5$ °C. Once calibration has been completed, the user will need to calculate the slope for both hot and cold. In application code, the user would then calculate the temperature using Equation 9-1 as detailed above and then determine if the temperature is above or below 25°C. Once determined if the temperature is above or below 25°C, the user can recalculate the temperature using the hot or cold slope value obtained during calibration.

Figure 9-1 shows the MC9S08SH8 with the ADC module highlighted.

| ADICLK | Selected Clock Source      |  |  |  |  |  |

|--------|----------------------------|--|--|--|--|--|

| 00     | Bus clock                  |  |  |  |  |  |

| 01     | Bus clock divided by 2     |  |  |  |  |  |

| 10     | Alternate clock (ALTCLK)   |  |  |  |  |  |

| 11     | Asynchronous clock (ADACK) |  |  |  |  |  |

#### Table 9-8. Input Clock Select

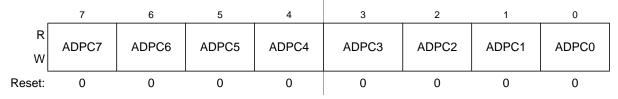

# 9.3.8 Pin Control 1 Register (APCTL1)

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

|            | Table 9-9. APCIL1 Register Field Descriptions                                                                                                                                        |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Field      | Description                                                                                                                                                                          |  |  |  |  |  |

| 7<br>ADPC7 | ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.         0 AD7 pin I/O control enabled         1 AD7 pin I/O control disabled                       |  |  |  |  |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |  |  |  |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |  |  |  |  |

### Table 9-9. APCTL1 Register Field Descriptions

## 10.1.4.4 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock. The BDC clock is not available.

# 10.1.4.5 FLL Bypassed External (FBE)

In FLL bypassed external mode, the FLL is enabled and controlled by an external reference clock, but is bypassed. The ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is supplied from the FLL.

# 10.1.4.6 FLL Bypassed External Low Power (FBELP)

In FLL bypassed external low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is not available.

## 10.1.4.7 Stop (STOP)

In stop mode the FLL is disabled and the internal or external reference clocks can be selected to be enabled or disabled. The BDC clock is not available and the ICS does not provide an MCU clock source.

# 10.2 External Signal Description

There are no ICS signals that connect off chip.

# 10.3 Register Definitio

Figure 10-1 is a summary of ICS registers.

| Table 10-1 | ICS | Register | Summary |

|------------|-----|----------|---------|

|------------|-----|----------|---------|

| Name   |   | 7  | 6    | 5         | 4      | 3    | 2       | 1       | 0        |

|--------|---|----|------|-----------|--------|------|---------|---------|----------|

| ICSC1  | R | CI | CLKS |           | RDIV   |      |         | IRCLKEN | IREFSTEN |

|        | W | 01 |      | NDIV      |        |      | IREFS   | INCEREN |          |

| ICSC2  | R | BL | DIV  | RANGE HGO | HGO    | LP   | EREFS   | ERCLKEN | EREFSTEN |

| 10002  | W |    |      |           | L!     |      | EROEREN |         |          |

| ICSTRM | R |    |      |           |        | TRIM |         |         |          |

|        | W |    |      |           |        |      |         |         |          |

| ICSSC  | R | 0  | 0    | 0         | IREFST | CL   | KST     | OSCINIT | FTRIM    |

| 10350  | W |    |      |           |        |      |         |         |          |

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

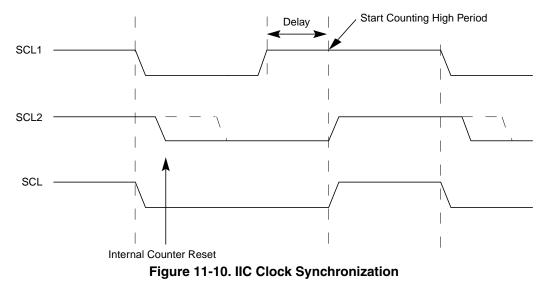

## 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

### 11.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such a case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

### 11.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

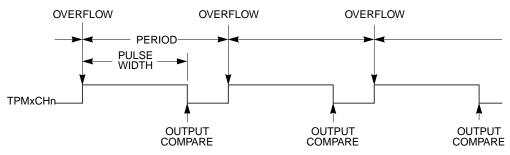

Chapter 16 Timer/PWM Module (S08TPMV3)

Figure 16-15. PWM Period and Pulse Width (ELSnA=0)

When the channel value register is set to 0x0000, the duty cycle is 0%. 100% duty cycle can be achieved by setting the timer-channel register (TPMxCnVH:TPMxCnVL) to a value greater than the modulus setting. This implies that the modulus setting must be less than 0xFFFF in order to get 100% duty cycle.

Because the TPM may be used in an 8-bit MCU, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxCnVH and TPMxCnVL, actually write to buffer registers. In edge-aligned PWM mode, values are transferred to the corresponding timer-channel registers according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

## 16.4.2.4 Center-Aligned PWM Mode

This type of PWM output uses the up/down counting mode of the timer counter (CPWMS=1). The output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM signal while the period is determined by the value in TPMxMODH:TPMxMODL. TPMxMODH:TPMxMODL should be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

```

pulse width = 2 x (TPMxCnVH:TPMxCnVL)

period = 2 x (TPMxMODH:TPMxMODL); TPMxMODH:TPMxMODL=0x0001-0x7FFF

```

If the channel-value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (non-zero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if you do not need to generate 100% duty cycle). This is not a significant limitation. The resulting period would be much longer than required for normal applications.

TPMxMODH:TPMxMODL=0x0000 is a special case that should not be used with center-aligned PWM mode. When CPWMS=0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS=1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

### **Chapter 17 Development Support**

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

# 17.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

Appendix A Electrical Characteristics

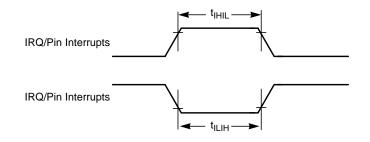

Figure A-11. IRQ/Pin Interrupt Timing

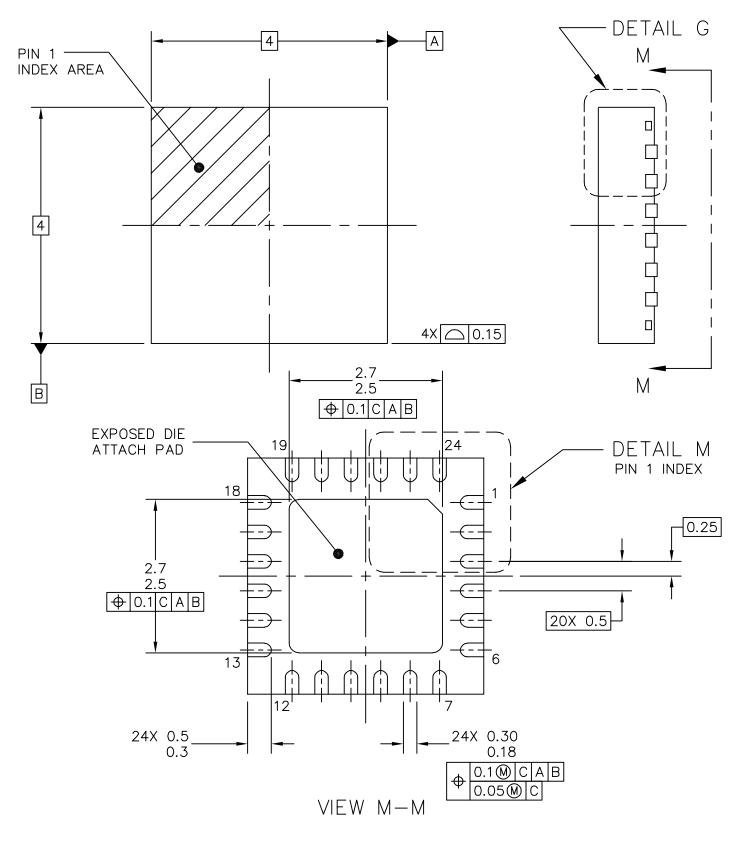

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                               | MECHANICA | LOUTLINE                      | PRINT VERSION NO | T TO SCALE  |

|-------------------------------------------------------------------------------------------------------|-----------|-------------------------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD<br>FLAT NON-LEADED PACKAGE (QFN)<br>24 TERMINAL, 0.5 PITCH (4 X 4 X 1) |           | DOCUMENT NO                   | ): 98ARE10714D   | REV: O      |

|                                                                                                       |           | CASE NUMBER                   | : 1969–01        | 23 JUL 2007 |

|                                                                                                       |           | STANDARD: JEDEC M0-220 VGGD-6 |                  |             |

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- A. THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 5. THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- 6. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA | LOUTLINE                 | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------------------|------------------|-------------|

| TITLE:<br>20LD SOIC W/B, 1.27 PITCH,<br>CASE OUTLINE    |           | DOCUMENT NO              | : 98ASB42343B    | REV: J      |

|                                                         |           | CASE NUMBER              | 2: 751D-07       | 23 MAR 2005 |

|                                                         |           | STANDARD: JEDEC MS-013AC |                  |             |

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| 16 LD TSSOP, PITCH 0.65MM                               |                    | DOCUMENT NO: 98ASH70247A |                            | RE∨: B      |

|                                                         |                    | CASE NUMBER: 948F-01     |                            | 19 MAY 2005 |

|                                                         |                    | STANDARD: JEDEC          |                            |             |

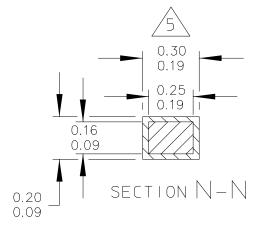

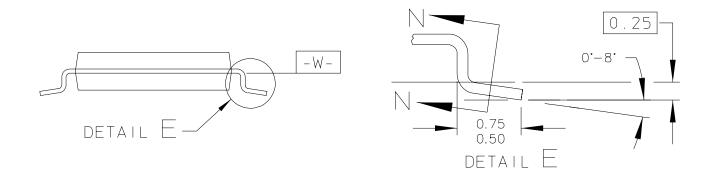

NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M-1982.

<u>A</u> DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

4 DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE

5 DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

$\overline{2}$  dimensions are to be determined at datum plane  $\overline{-W}$ -

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| 16 LD TSSOP, PITCH 0.65MM                               |                    | DOCUMENT NO: 98ASH70247A |                            | RE∨: B      |

|                                                         |                    | CASE NUMBER: 948F-01     |                            | 19 MAY 2005 |

|                                                         |                    | STANDARD: JEDEC          |                            |             |