### NXP USA Inc. - MC9S08SH4CTGR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 13                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 16-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh4ctgr |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Chapter 1 Device Overview

The MC9S08SH8 members of the low-cost, high-performance HCS08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types.

## 1.1 Devices in the MC9S08SH8 Series

Table 1-1 summarizes the feature set available in the MC9S08SH8 series of MCUs.

| Feature              | 9S08SH8 |      |     | 9S08SH4          |     |      |     |                  |  |

|----------------------|---------|------|-----|------------------|-----|------|-----|------------------|--|

| FLASH size (bytes)   |         | 8192 |     |                  |     | 4096 |     |                  |  |

| RAM size (bytes)     |         | 5    | 12  |                  | 256 |      |     |                  |  |

| Pin quantity         | 24      | 20   | 16  | 8                | 24  | 20   | 16  | 8                |  |

| ACMP                 |         |      |     | ye               | es  |      |     |                  |  |

| ADC channels         | 12      | 12   | 8   | 4                | 12  | 12   | 8   | 4                |  |

| DBG                  |         |      |     | ye               | es  |      |     |                  |  |

| ICS                  | yes     | yes  | yes | yes <sup>1</sup> | yes | yes  | yes | yes <sup>1</sup> |  |

| IIC                  |         |      |     | ye               | es  |      |     |                  |  |

| MTIM                 |         |      |     | ye               | es  |      |     |                  |  |

| Pin Interrupts       | 8       | 8    | 8   | 4                | 8   | 8    | 8   | 4                |  |

| Pin I/O <sup>2</sup> | 17      | 17   | 13  | 5                | 17  | 17   | 13  | 5                |  |

| RTC                  | yes     |      |     |                  |     |      |     |                  |  |

| SCI                  | yes     | yes  | yes | no               | yes | yes  | yes | no               |  |

| SPI                  | yes     | yes  | yes | no               | yes | yes  | yes | no               |  |

| TPM1 channels        | 2       | 2    | 2   | 1                | 2   | 2    | 2   | 1                |  |

| TPM2 channels        | 2       | 2    | 2   | 1                | 2   | 2    | 2   | 1                |  |

| XOSC                 | yes     | yes  | yes | no               | yes | yes  | yes | no               |  |

### Table 1-1. MC9S08SH8 Features by MCU and Package

<sup>1</sup> FBE and FEE modes are not available in 8-pin packages.

<sup>2</sup> Port I/O count does not include the output-only PTA4/ACMPO/BKGD/MS.

The status flag corresponding to the interrupt source must be acknowledged (cleared) before returning from the ISR. Typically, the flag is cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

## 5.5.2 External Interrupt Request Pin (IRQ)

External interrupts are managed by the IRQ status and control register, IRQSC. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

### 5.5.2.1 Pin Configuration Option

The IRQ pin enable (IRQPE) control bit in IRQSC must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

The IRQ pin, when enabled, defaults to use an internal pull device (IRQPDD = 0), the device is a pull-up or pull-down depending on the polarity chosen. If the user desires to use an external pull-up or pull-down, the IRQPDD can be written to a 1 to turn off the internal device.

BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

### NOTE

This pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ .

The voltage measured on the internally pulled up IRQ pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the IRQ pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### 5.5.2.2 Edge and Level Sensitivity

The IRQMOD control bit reconfigures the detection logic so it detects edge events and pin levels. In the edge and level detection mode, the IRQF status flag becomes set when an edge is detected (when the IRQ pin changes from the deasserted to the asserted level), but the flag is continuously set (and cannot be cleared) as long as the IRQ pin remains at the asserted level.

## 5.5.3 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

| Field     | Description                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ILAD | Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.         0       Reset not caused by an illegal address         1       Reset caused by an illegal address                              |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR.</li> <li>1 Reset caused by LVD trip or POR.</li> </ul> |

### Table 5-4. SRS Register Field Descriptions

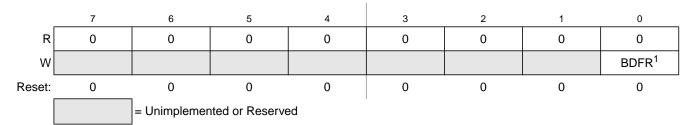

## 5.7.3 System Background Debug Force Reset Register (SBDFR)

This high page register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

### Figure 5-4. System Background Debug Force Reset Register (SBDFR)

### Table 5-5. SBDFR Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                 |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE can be used to allow an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |  |

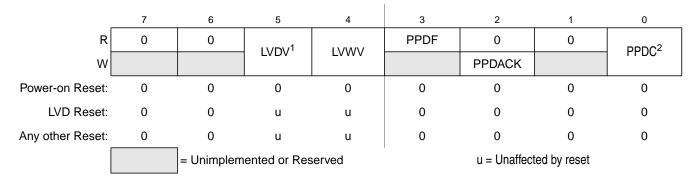

# 5.7.8 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

### Figure 5-10. System Power Management Status and Control 2 Register (SPMSC2)

### Table 5-11. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-12.                                        |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-12.                                                                                            |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |

### Table 5-12. LVD and LVW trip point typical values<sup>1</sup>

| LVDV:LVWV | LVW Trip Point             | LVD Trip Point             |

|-----------|----------------------------|----------------------------|

| 0:0       | V <sub>LVW0</sub> = 2.74 V | V <sub>LVD0</sub> = 2.56 V |

| 0:1       | V <sub>LVW1</sub> = 2.92 V |                            |

| 1:0       | V <sub>LVW2</sub> = 4.3 V  | V <sub>LVD1</sub> = 4.0 V  |

| 1:1       | V <sub>LVW3</sub> = 4.6 V  |                            |

<sup>1</sup> See Electrical Characteristics appendix for minimum and maximum values.

## 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

## 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at 0xFFFE and 0xFFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

## 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1.

### Chapter 7 Central Processor Unit (S08CPUV2)

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                               | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                            | Affect<br>on CCR      |             |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|-----------------------|-------------|

| Form                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         | Ado                                                 |                                                                                  | δ                               | Details                                          | <b>V</b> 1 1 <b>H</b> | INZC        |

| RSP                                                                                                             | Reset Stack Pointer (Low Byte)<br>SPL ← \$FF<br>(High Byte Not Affected)                                                                                                                                                                                                                                                                                                                | INH                                                 | 9C                                                                               | 1                               | р                                                | - 1 1 -               |             |

| RTI                                                                                                             | $\begin{array}{l} \mbox{Return from Interrupt} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (CCR)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (A)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (X)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (PCH)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (PCL)} \end{array}$ | INH                                                 | 80                                                                               | 9                               | uuuuufppp                                        | ↓11↓                  | \$ \$ \$ \$ |

| RTS                                                                                                             | Return from Subroutine<br>SP $\leftarrow$ SP + \$0001; Pull (PCH)<br>SP $\leftarrow$ SP + \$0001; Pull (PCL)                                                                                                                                                                                                                                                                            | INH                                                 | 81                                                                               | 5                               | ufppp                                            | - 1 1 -               |             |

| SBC #opr8i<br>SBC opr8a<br>SBC opr16a<br>SBC oprx16,X<br>SBC oprx8,X<br>SBC ,X<br>SBC oprx16,SP<br>SBC oprx8,SP | Subtract with Carry<br>A $\leftarrow$ (A) – (M) – (C)                                                                                                                                                                                                                                                                                                                                   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A2 ii<br>B2 dd<br>C2 hh 11<br>D2 ee ff<br>E2 ff<br>F2<br>9E D2 ee ff<br>9E E2 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓11-                  | - \$ \$ \$  |

| SEC                                                                                                             | Set Carry Bit $(C \leftarrow 1)$                                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 99                                                                               | 1                               | р                                                | - 1 1 -               | 1           |

| SEI                                                                                                             | Set Interrupt Mask Bit $(I \leftarrow 1)$                                                                                                                                                                                                                                                                                                                                               | INH                                                 | 9в                                                                               | 1                               | р                                                | - 1 1 -               | 1 – – –     |

| STA opr8a<br>STA opr16a<br>STA oprx16,X<br>STA oprx8,X<br>STA ,X<br>STA oprx16,SP<br>STA oprx8,SP               | Store Accumulator in Memory $M \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                          | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | B7 dd<br>C7 hh ll<br>D7 ee ff<br>E7 ff<br>F7<br>9E D7 ee ff<br>9E E7 ff          | 3<br>4<br>3<br>2<br>5<br>4      | рмбр<br>рьмбр<br>мбр<br>Бмбр<br>Бмбр<br>мбр      | 011-                  | - \$ \$ -   |

| STHX opr8a<br>STHX opr16a<br>STHX oprx8,SP                                                                      | Store H:X (Index Reg.)<br>(M:M + \$0001) ← (H:X)                                                                                                                                                                                                                                                                                                                                        | DIR<br>EXT<br>SP1                                   | 35 dd<br>96 hh 11<br>9E FF ff                                                    | 4<br>5<br>5                     | pwwpp                                            | 011-                  | - ‡ ‡ -     |

| STOP                                                                                                            | Enable Interrupts: Stop Processing<br>Refer to MCU Documentation<br>I bit $\leftarrow$ 0; Stop Processing                                                                                                                                                                                                                                                                               | INH                                                 | 8E                                                                               | 2                               | fp                                               | - 1 1 -               | 0 – – –     |

| STX opr8a<br>STX opr16a<br>STX oprx16,X<br>STX oprx8,X<br>STX ,X<br>STX oprx16,SP<br>STX oprx8,SP               | Store X (Low 8 Bits of Index Register) in Memory $M \leftarrow (X)$                                                                                                                                                                                                                                                                                                                     | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | BF dd<br>CF hh ll<br>DF ee ff<br>EF ff<br>FF<br>9E DF ee ff<br>9E EF ff          | 3<br>4<br>3<br>2<br>5<br>4      | БмББ<br>ББмББ<br>мБ<br>БмББ<br>БмББ<br>МББ       | 011-                  | - \$ \$ -   |

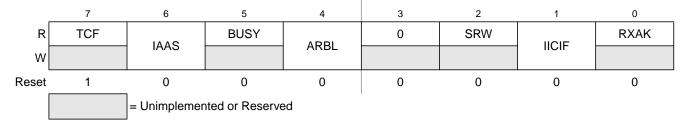

## 11.3.4 IIC Status Register (IICS)

### Figure 11-6. IIC Status Register (IICS)

### Table 11-7. IICS Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TCF   | <ul> <li>Transfer Complete Flag. This bit is set on the completion of a byte transfer. This bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                         |

| 6<br>IAAS  | <ul> <li>Addressed as a Slave. The IAAS bit is set when the calling address matches the programmed slave address or when the GCAEN bit is set and a general call is received. Writing the IICC register clears this bit.</li> <li>0 Not addressed</li> <li>1 Addressed as a slave</li> </ul>                                                                                                                    |

| 5<br>BUSY  | <ul> <li>Bus Busy. The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a start signal is detected and cleared when a stop signal is detected.</li> <li>0 Bus is idle</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                    |

| 4<br>ARBL  | <ul> <li>Arbitration Lost. This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software by writing a 1 to it.</li> <li>0 Standard bus operation</li> <li>1 Loss of arbitration</li> </ul>                                                                                                                                                                       |

| 2<br>SRW   | <ul> <li>Slave Read/Write. When addressed as a slave, the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>0 Slave receive, master writing to slave</li> <li>1 Slave transmit, master reading from slave</li> </ul>                                                                                                                                       |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag. The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a 1 to it in the interrupt routine. One of the following events can set the IICIF bit:</li> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> <li>No interrupt pending</li> <li>1 Interrupt pending</li> </ul> |

| 0<br>RXAK  | <ul> <li>Receive Acknowledge. When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received</li> <li>1 No acknowledge received</li> </ul>                                                                           |

Chapter 11 Inter-Integrated Circuit (S08IICV2)

## 11.7 Initialization/Application Information

| 1. | Module Initialization (Slave)                                                                              |                                                                                                       |  |  |  |  |

|----|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1. |                                                                                                            | nable or disable general call                                                                         |  |  |  |  |

|    |                                                                                                            | elect 10-bit or 7-bit addressing mode                                                                 |  |  |  |  |

| 2. | Write: IIC                                                                                                 | -                                                                                                     |  |  |  |  |

|    | — to se                                                                                                    | et the slave address                                                                                  |  |  |  |  |

| 3. | Write: IIC                                                                                                 | CC1                                                                                                   |  |  |  |  |

|    |                                                                                                            | nable IIC and interrupts                                                                              |  |  |  |  |

| 4. |                                                                                                            | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                             |  |  |  |  |

| 5. | Initialize                                                                                                 | RAM variables used to achieve the routine shown in Figure 11-12                                       |  |  |  |  |

|    |                                                                                                            |                                                                                                       |  |  |  |  |

|    |                                                                                                            | Module Initialization (Master)                                                                        |  |  |  |  |

| 1. | Write: IIC                                                                                                 |                                                                                                       |  |  |  |  |

|    |                                                                                                            | et the IIC baud rate (example provided in this chapter)                                               |  |  |  |  |

| 2. | Write: IIC                                                                                                 |                                                                                                       |  |  |  |  |

|    |                                                                                                            | nable IIC and interrupts                                                                              |  |  |  |  |

| 3. |                                                                                                            | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                             |  |  |  |  |

| 4. |                                                                                                            | RAM variables used to achieve the routine shown in Figure 11-12                                       |  |  |  |  |

| 5. | Write: IIC<br>— to er                                                                                      |                                                                                                       |  |  |  |  |

| 6. | Write: IIC                                                                                                 |                                                                                                       |  |  |  |  |

| 0. |                                                                                                            | nable MST (master mode)                                                                               |  |  |  |  |

| 7. | Write: IIC                                                                                                 |                                                                                                       |  |  |  |  |

|    |                                                                                                            | the address of the target slave. (The lsb of this byte determines whether the communication is        |  |  |  |  |

|    | master receive or transmit.)                                                                               |                                                                                                       |  |  |  |  |

|    | Module Use                                                                                                 |                                                                                                       |  |  |  |  |

|    | The routine shown in Figure 11-12 can handle both master and slave IIC operations. For slave operation, an |                                                                                                       |  |  |  |  |

|    |                                                                                                            | incoming IIC message that contains the proper address begins IIC communication. For master operation, |  |  |  |  |

|    | communication must be initiated by writing to the IICD register.                                           |                                                                                                       |  |  |  |  |

|    |                                                                                                            |                                                                                                       |  |  |  |  |

|    |                                                                                                            |                                                                                                       |  |  |  |  |

|    |                                                                                                            | Register Model                                                                                        |  |  |  |  |

|    | IICA                                                                                                       | AD[7:1] 0                                                                                             |  |  |  |  |

|    | non                                                                                                        |                                                                                                       |  |  |  |  |

|    |                                                                                                            | When addressed as a slave (in slave mode), the module responds to this address                        |  |  |  |  |

|    | IICF                                                                                                       | MULT ICR                                                                                              |  |  |  |  |

|    |                                                                                                            | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                                                       |  |  |  |  |

|    | IICC1                                                                                                      | IICEN IICIE MST TX TXAK RSTA 0 0                                                                      |  |  |  |  |

|    | licer                                                                                                      |                                                                                                       |  |  |  |  |

|    |                                                                                                            | Module configuration                                                                                  |  |  |  |  |

|    | IICS                                                                                                       | TCF IAAS BUSY ARBL 0 SRW IICIF RXAK                                                                   |  |  |  |  |

|    |                                                                                                            | Module status flags                                                                                   |  |  |  |  |

|    | IICD                                                                                                       | DATA                                                                                                  |  |  |  |  |

|    | Data register; Write to transmit IIC data read to read IIC data                                            |                                                                                                       |  |  |  |  |

|    |                                                                                                            |                                                                                                       |  |  |  |  |

|    | IICC2                                                                                                      |                                                                                                       |  |  |  |  |

|    |                                                                                                            | Address configuration                                                                                 |  |  |  |  |

Figure 11-11. IIC Module Quick Start

MC9S08SH8 MCU Series Data Sheet, Rev. 3

## Chapter 12 Modulo Timer (S08MTIMV1)

## 12.1 Introduction

The MTIM is a simple 8-bit timer with several software selectable clock sources and a programmable interrupt.

The central component of the MTIM is the 8-bit counter, which can operate as a free-running counter or a modulo counter. A timer overflow interrupt can be enabled to generate periodic interrupts for time-based software loops.

Figure 12-1 shows the MC9S08SH8 block diagram with the MTIM module highlighted.

## **12.1.1 MTIM Configuration In ormation**

The external clock for the MTIM module, TCLK, is selected by setting CLKS = 1:1 or 1:0 in MTIMCLK, which selects the TCLK pin input. The TCLK input on PTA0 can be enabled as external clock inputs to both MTIM and TPM modules simultaneously.

#### Chapter 13 Real-Time Counter (S08RTCV1)

```

#pragma TRAP_PROC

void RTC_ISR(void)

{

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59){

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59){

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23){

Days ++;

Hours = 0;

}

}

```

## Chapter 15 Serial Peripheral Interface (S08SPIV3)

## 15.1 Introduction

Figure 15-1 shows the MC9S08SH8 block diagram with the SPI module highlighted.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSTR  | Master/Slave Mode Select         0       SPI module configured as a slave SPI device         1       SPI module configured as a master SPI device                                                                                                                                                                                                                                                             |

| 3<br>CPOL  | <ul> <li>Clock Polarity — This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 15.5.1, "SPI Clock Formats" for more details.</li> <li>0 Active-high SPI clock (idles low)</li> <li>1 Active-low SPI clock (idles high)</li> </ul>                                                                                             |

| 2<br>CPHA  | <ul> <li>Clock Phase — This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 15.5.1, "SPI Clock Formats" for more details.</li> <li>0 First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer</li> <li>1 First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer</li> </ul> |

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — This bit is used in combination with the mode fault enable (MODFEN) bit in SPCR2 and the master/slave (MSTR) control bit to determine the function of the SS pin as shown in Table 15-2.                                                                                                                                                                                  |

| 0<br>LSBFE | <ul> <li>LSB First (Shifter Direction)</li> <li>0 SPI serial data transfers start with most significant bit</li> <li>1 SPI serial data transfers start with least significant bit</li> </ul>                                                                                                                                                                                                                  |

Table 15-2. SS Pin Function

| [ | MODFEN | SSOE | Master Mode                   | Slave Mode         |

|---|--------|------|-------------------------------|--------------------|

|   | 0      | 0    | General-purpose I/O (not SPI) | Slave select input |

| Ī | 0      | 1    | General-purpose I/O (not SPI) | Slave select input |

| Ī | 1      | 0    | SS input for mode fault       | Slave select input |

| ĺ | 1      | 1    | Automatic SS output           | Slave select input |

### NOTE

Ensure that the SPI should not be disabled (SPE=0) at the same time as a bit change to the CPHA bit. These changes should be performed as separate operations or unexpected behavior may occur.

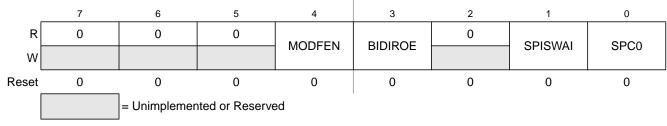

## 15.4.2 SPI Control Register 2 (SPIC2)

This read/write register is used to control optional features of the SPI system. Bits 7, 6, 5, and 2 are not implemented and always read 0.

MC9S08SH8 MCU Series Data Sheet, Rev. 3

### Table 15-3. SPIC2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MODFEN  | Master Mode-Fault Function Enable       When the SPI is configured for slave mode, this bit has no meaning or effect. (The SS pin is the slave select input.) In master mode, this bit determines how the SS pin is used (refer to Table 15-2 for more details).         0       Mode fault function disabled, master SS pin reverts to general-purpose I/O not controlled by SPI         1       Mode fault function enabled, master SS pin acts as the mode fault input or the slave select output                                                         |

| 3<br>BIDIROE | <b>Bidirectional Mode Output Enable</b> — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1,<br>BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin.<br>Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO<br>(SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect.<br>0 Output driver disabled so SPI data I/O pin acts as an input<br>1 SPI I/O pin enabled as an output |

| 1<br>SPISWAI | SPI Stop in Wait Mode         0 SPI clocks continue to operate in wait mode         1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>SPC0    | <ul> <li>SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.</li> <li>O SPI uses separate pins for data input and data output</li> <li>1 SPI configured for single-wire bidirectional operation</li> </ul>           |

## 15.4.3 SPI Baud Rate Register (SPIBR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

= Unimplemented or Reserved

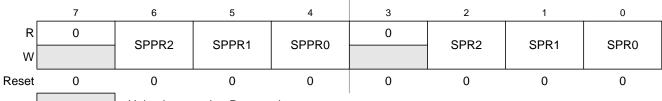

### Figure 15-7. SPI Baud Rate Register (SPIBR)

### Table 15-4. SPIBR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>SPPR[2:0] | <b>SPI Baud Rate Prescale Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 15-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 15-4). |

| 2:0<br>SPR[2:0]  | <b>SPI Baud Rate Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 15-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 15-4). The output of this divider is the SPI bit rate clock for master mode.            |

#### Chapter 16 Timer/PWM Module (S08TPMV3)

The TPM channels are programmable independently as input capture, output compare, or edge-aligned PWM channels. Alternately, the TPM can be configured to produce CPWM outputs on all channels. When the TPM is configured for CPWMs, the counter operates as an up/down counter; input capture, output compare, and EPWM functions are not practical.

If a channel is configured as input capture, an internal pullup device may be enabled for that channel. The details of how a module interacts with pin controls depends upon the chip implementation because the I/O pins and associated general purpose I/O controls are not part of the module. Refer to the discussion of the I/O port logic in a full-chip specification.

Because center-aligned PWMs are usually used to drive 3-phase AC-induction motors and brushless DC motors, they are typically used in sets of three or six channels.

## 16.2 Signal Description

Table 16-2 shows the user-accessible signals for the TPM. The number of channels may be varied from one to eight. When an external clock is included, it can be shared with the same pin as any TPM channel; however, it could be connected to a separate input pin. Refer to the I/O pin descriptions in full-chip specification for the specific chip implementation.

| Name                 | Function                                                              |

|----------------------|-----------------------------------------------------------------------|

| EXTCLK <sup>1</sup>  | External clock source which may be selected to drive the TPM counter. |

| TPMxCHn <sup>2</sup> | I/O pin associated with TPM channel n                                 |

**Table 16-2. Signal Properties**

<sup>1</sup> When preset, this signal can share any channel pin; however depending upon full-chip implementation, this signal could be connected to a separate external pin.

<sup>2</sup> n=channel number (1 to 8)

Refer to documentation for the full-chip for details about reset states, port connections, and whether there is any pullup device on these pins.

TPM channel pins can be associated with general purpose I/O pins and have passive pullup devices which can be enabled with a control bit when the TPM or general purpose I/O controls have configured the associated pin as an input. When no TPM function is enabled to use a corresponding pin, the pin reverts to being controlled by general purpose I/O controls, including the port-data and data-direction registers. Immediately after reset, no TPM functions are enabled, so all associated pins revert to general purpose I/O control.

## 16.2.1 Detailed Signal Descriptions

This section describes each user-accessible pin signal in detail. Although Table 16-2 grouped all channel pins together, any TPM pin can be shared with the external clock source signal. Since I/O pin logic is not part of the TPM, refer to full-chip documentation for a specific derivative for more details about the interaction of TPM pin functions and general purpose I/O controls including port data, data direction, and pullup controls.

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuratio                                  |

|-------|-----------|-------------|-----------------------|-----------------------------------------------|

| 0     | 00        | 01          | Input capture         | Capture on rising edge only                   |

|       |           | 10          |                       | Capture on falling edge only                  |

|       |           | 11          |                       | Capture on rising or falling edge             |

|       | 01        | 01          | Output compare        | Toggle output on compare                      |

|       |           | 10          |                       | Clear output on compare                       |

|       |           | 11          | _                     | Set output on compare                         |

|       | 1X        | 10          | Edge-aligned<br>PWM   | High-true pulses (clear output on compare)    |

|       |           | X1          |                       | Low-true pulses (set output on compare)       |

| 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses (clear output on compare-up) |

|       |           | X1          |                       | Low-true pulses (set output on compare-up)    |

Table 16-7. Mode, Edge, and Level Selection

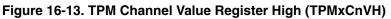

### 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel registers are cleared by reset.

| _      | 7      | 6  | 5  | 4  | 3  | 2  | 1 | 0     |

|--------|--------|----|----|----|----|----|---|-------|

| R<br>W | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| Reset  | 0      | 0  | 0  | 0  | 0  | 0  | 0 | 0     |

|        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Figure 16-14. TPM Channel Value Register Low (TPMxCnVL)

In input capture mode, reading either byte (TPMxCnVH or TPMxCnVL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This latching mechanism also resets

MC9S08SH8 MCU Series Data Sheet, Rev. 3

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

## 16.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

## 16.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 16-4. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

| CLKSB:CLKSA                                 | TPM Clock Source to Prescaler Input |  |  |

|---------------------------------------------|-------------------------------------|--|--|

| 00 No clock selected (TPM counter disabled) |                                     |  |  |

| 01                                          | Bus rate clock                      |  |  |

| 10                                          | Fixed system clock                  |  |  |

| 11                                          | External source                     |  |  |

| Table 16-8. | TPM Clock | Source | Selection |

|-------------|-----------|--------|-----------|

|             |           |        |           |

The bus rate clock is the main system bus clock for the MCU. This clock source requires no synchronization because it is the clock that is used for all internal MCU activities including operation of the CPU and buses.

In MCUs that have no PLL and FLL or the PLL and FLL are not engaged, the fixed system clock source is the same as the bus-rate-clock source, and it does not go through a synchronizer. When a PLL or FLL is present and engaged, a synchronizer is required between the crystal divided-by two clock source and the timer counter so counter transitions will be properly aligned to bus-clock transitions. A synchronizer will be used at chip level to synchronize the crystal-related source clock to the bus clock.

The external clock source may be connected to any TPM channel pin. This clock source always has to pass through a synchronizer to assure that counter transitions are properly aligned to bus clock transitions. The bus-rate clock drives the synchronizer; therefore, to meet Nyquist criteria even with jitter, the frequency of the external clock source must not be faster than the bus rate divided-by four. With ideal clocks the external clock can be as fast as bus clock divided by four.

When the external clock source shares the TPM channel pin, this pin should not be used for other channel timing functions. For example, it would be ambiguous to configure channel 0 for input capture when the TPM channel 0 pin was also being used as the timer external clock source. (It is the user's responsibility

Chapter 16 Timer/PWM Module (S08TPMV3)

In this case, the TPM v3 waits for the start of a new PWM period to begin using the new duty cycle setting. Instead, the TPM v2 changes the channel output at the middle of the current PWM period (when the count reaches 0x0000).

— TPMxCnVH:L is changed from a non-zero value to 0x0000 [SE110-TPM case 4]

In this case, the TPM v3 finishes the current PWM period using the old duty cycle setting. Instead, the TPM v2 finishes the current PWM period using the new duty cycle setting.

6. Write to TPMxMODH:L registers in BDM mode (Section 16.3.3, "TPM Counter Modulo Registers (TPMxMODH:TPMxMODL))

In the TPM v3 a write to TPMxSC register in BDM mode clears the write coherency mechanism of TPMxMODH:L registers. Instead, in the TPM v2 this coherency mechanism is not cleared when there is a write to TPMxSC register.

7. Update of EPWM signal when CLKSB:CLKSA = 00

In the TPM v3 if CLKSB:CLKSA = 00, then the EPWM signal in the channel output is not update (it is frozen while CLKSB:CLKSA = 00). Instead, in the TPM v2 the EPWM signal is updated at the next rising edge of bus clock after a write to TPMxCnSC register.

The Figure 0-1 and Figure 0-2 show when the EPWM signals generated by TPM v2 and TPM v3 after the reset (CLKSB:CLKSA = 00) and if there is a write to TPMxCnSC register.

### EPWM mode

TPMxMODH:TPMxMODL = 0x0007 TPMxCnVH:TPMxCnVL = 0x0005

| RESET (active low) |        |           |     |         |           |           |   |

|--------------------|--------|-----------|-----|---------|-----------|-----------|---|

| BUS CLOCK          |        |           |     |         | ΠΠ        | ÎΠ        | Л |

| TPMxCNTH:TPMxCNTL  | I<br>I | I<br>I 0  |     | 1 2 3 4 | 5 6 7     | 0 1       | 2 |

| CLKSB:CLKSA BITS   | <br>   | 1<br>1 00 |     |         | 1<br>1 01 | <br>      |   |

| MSnB:MSnA BITS     | 00     | <br> <br> | 10  |         | <br> <br> | <br> <br> |   |

| ELSnB:ELSnA BITS   | 00     | <br>      | 10  |         | <br>      | <br> <br> |   |

| TPMv2 TPMxCHn      |        |           |     |         |           |           |   |

| TPMv3 TPMxCHn      |        | -         | _(( |         | <br> <br> |           |   |

| CHnF BIT           |        |           | "   |         | ]         |           |   |

Figure 0-1. Generation of high-true EPWM signal by TPM v2 and v3 after the reset

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>WS  | <ul> <li>Wait or Stop Status — When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ_STATUS command to check that BDMACT = 1 before attempting other BDC commands.</li> <li>0 Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active)</li> <li>1 Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode</li> </ul> |

| 1<br>WSF | <ul> <li>Wait or Stop Failure Status — This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)</li> <li>Memory access did not conflict with a wait or stop instruction</li> <li>Memory access command failed because the CPU entered wait or stop mode</li> </ul>                                                                                   |

| 0<br>DVF | <ul> <li>Data Valid Failure Status — This status bit is not used in the MC9S08SH8 because it does not have any slow access memory.</li> <li>0 Memory access did not conflict with a slow memory access</li> <li>1 Memory access command failed because CPU was not finished with a slow memory access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### Table 17-2. BDCSCR Register Field Descriptions (continued)

### 17.4.1.2 BDC Breakpoint Match Register (BDCBKPT)

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ\_BKPT and WRITE\_BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 17.2.4, "BDC Hardware Breakpoint."

## 17.4.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

## A.8 External Oscillator (XOSC) Characteristics

| Nu<br>m | С | Rating                                                     | Symbol                         | Min     | Typ <sup>1</sup> | Max        | Unit |

|---------|---|------------------------------------------------------------|--------------------------------|---------|------------------|------------|------|

|         |   | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)   |                                |         |                  |            |      |

|         |   | Low range (RANGE = 0)                                      | f <sub>lo</sub>                | 32      | —                | 38.4       | kHz  |

| 1       | С | High range (RANGE = 1) FEE or FBE mode $^2$                | f <sub>hi</sub>                | 1       | —                | 5          | MHz  |

|         |   | High range (RANGE = 1, HGO = 1) FBELP mode                 | f <sub>hi-hgo</sub>            | 1       | —                | 16         | MHz  |

|         |   | High range (RANGE = 1, HGO = 0) FBELP mode                 | f <sub>hi-lp</sub>             | 1       | —                | 8          | MHz  |

| 2       | _ | Load capacitors                                            | C <sub>1,</sub> C <sub>2</sub> |         |                  | r resonato |      |

|         |   | Feedback resistor                                          |                                |         |                  |            |      |

| 3       | — | Low range (32 kHz to 100 kHz)                              | R <sub>F</sub>                 | —       | 10               | —          | MΩ   |

|         |   | High range (1 MHz to 16 MHz)                               |                                | —       | 1                | —          |      |

|         |   | Series resistor                                            |                                |         |                  |            |      |

|         |   | Low range, low gain (RANGE = 0, HGO = 0)                   |                                | —       | 0                | —          |      |

|         |   | Low range, high gain (RANGE = 0, HGO = 1)                  |                                | —       | 100              | —          |      |

| 4       | _ | High range, low gain (RANGE = 1, HGO = 0)                  | R <sub>S</sub>                 | —       | 0                | _          | kΩ   |

|         |   | High range, high gain (RANGE = 1, HGO = 1)                 |                                |         |                  |            |      |

|         |   | ≥ 8 MHz                                                    |                                | —       | 0                | 0          |      |

|         |   | 4 MHz                                                      |                                | —       | 0                | 10         |      |

|         |   | 1 MHz                                                      |                                | —       | 0                | 20         |      |

|         |   | Crystal start-up time <sup>3</sup>                         |                                |         |                  |            |      |

|         |   | Low range, low gain (RANGE = 0, HGO = 0)                   | CSTL-LP                        | —       | 200              | —          |      |

| 5       | т | Low range, high gain (RANGE = 0, HGO = 1)                  | t<br>CSTL-HGO                  | —       | 400              | —          | ms   |

|         |   | High range, low gain (RANGE = 1, HGO = $0$ ) <sup>4</sup>  | t<br>CSTH-LP                   | _       | 5                | _          |      |

|         |   | High range, high gain (RANGE = 1, HGO = 1) <sup>4</sup>    | <sup>t</sup> CSTH-HGO          | _       | 20               | —          |      |

|         |   | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1) |                                |         |                  |            |      |

| 6       | Т | FEE or FBE mode <sup>2</sup>                               | f <sub>extal</sub>             | 0.03125 | —                | 5          | MHz  |

|         |   | FBELP mode                                                 |                                | 0       | —                | 40         | MHz  |

### Table A-8. Oscillator Electrical Specifications (emperature Range = -40 to 125°C Ambient)

$^1\,$  Typical data was characterized at 5.0 V, 25°C or is recommended value.

$^2$  The input clock source must be divided using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> This parameter is characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications.

<sup>4</sup> 4 MHz crystal

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

- 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

| DIM                                                     | MILLIMETERS<br>MIN MAX |             | DIM | INCHES<br>MIN MAX |             | DIM | MILLIMI<br>MIN           | ILLIMETERS<br>N MAX |  | MI | INCHES<br>MIN MAX |    |

|---------------------------------------------------------|------------------------|-------------|-----|-------------------|-------------|-----|--------------------------|---------------------|--|----|-------------------|----|

| А                                                       | 24.39                  | 24.99       |     | 0.960             | 0.984       |     |                          |                     |  |    |                   |    |

| В                                                       | 6.96                   | 7.49        |     | 0.274             | 0.295       |     |                          |                     |  |    |                   |    |

| С                                                       | 3.56                   | 5.08        |     | 0.140             | 0.200       |     |                          |                     |  |    |                   |    |

| D                                                       | 0.38                   | 0.56        |     | 0.015             | 0.022       |     |                          |                     |  |    |                   |    |

| E                                                       | 1.27 BSC               |             |     | 0.050 BSC         |             |     |                          |                     |  |    |                   |    |

| F                                                       | 1.14                   | 1.52        |     | 0.045             | 0.060       |     |                          |                     |  |    |                   |    |

| G                                                       | 2.54 BSC               |             |     | 0.100 BSC         |             |     |                          |                     |  |    |                   |    |

| J                                                       | 0.20                   | 0.38        |     | 0.008             | 0.015       |     |                          |                     |  |    |                   |    |

| К                                                       | 2.79                   | 3.76        |     | 0.110             | 0.148       |     |                          |                     |  |    |                   |    |

| L                                                       | 7.62 BSC               |             |     | 0.300 BSC         |             |     |                          |                     |  |    |                   |    |

| М                                                       | 0.                     | 15 <b>.</b> |     | 0.                | 15 <b>·</b> |     |                          |                     |  |    |                   |    |

| N                                                       | 0.50                   | 1.01        |     | 0.020             | 0.040       |     |                          |                     |  |    |                   |    |

| R                                                       | •••••                  | 1.29        |     |                   | 0.051       |     |                          |                     |  |    |                   |    |

|                                                         |                        |             |     |                   |             |     |                          | l                   |  |    |                   |    |

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. |                        |             |     |                   | MECHANICAL  |     | OUTLINE                  | PRINT VERSION NO    |  |    | T TO SCALE        |    |

| TITLE:                                                  |                        |             |     |                   |             | I   | DOCUMENT NO: 98ASB42899B |                     |  |    | REV: B            |    |

| 20LD .300 PDIP                                          |                        |             |     |                   |             | C   | CASE NUMBER: 738C-01     |                     |  |    | 24 MAY 200        | 15 |

|                                                         |                        |             |     |                   |             |     | STANDARD: NON-JEDEC      |                     |  |    |                   |    |