Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | S08                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 40MHz                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                        |

| Peripherals                | LVD, POR, PWM, WDT                                        |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | 20-DIP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08sh4mpj |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

### Title

### Page

|      | 13.3.3 RTC Modulo Register (RTCMOD)    |  |

|------|----------------------------------------|--|

| 13.4 | Functional Description                 |  |

|      | 13.4.1 RTC Operation Example           |  |

| 13.5 | Initialization/Application Information |  |

## Chapter 14 Serial Communications Interface (S08SCIV4)

| 14.1 | Introduc | tion                                       |  |

|------|----------|--------------------------------------------|--|

|      | 14.1.1   | Features                                   |  |

|      | 14.1.2   | Modes of Operation                         |  |

|      | 14.1.3   | Block Diagram                              |  |

| 14.2 | Register | Definition                                 |  |

|      |          | SCI Baud Rate Registers (SCIxBDH, SCIxBDL) |  |

|      | 14.2.2   | SCI Control Register 1 (SCIxC1)            |  |

|      | 14.2.3   | SCI Control Register 2 (SCIxC2)            |  |

|      | 14.2.4   | SCI Status Register 1 (SCIxS1)             |  |

|      | 14.2.5   | SCI Status Register 2 (SCIxS2)             |  |

|      | 14.2.6   | SCI Control Register 3 (SCIxC3)            |  |

|      | 14.2.7   | SCI Data Register (SCIxD)                  |  |

| 14.3 | Function | nal Description                            |  |

|      | 14.3.1   | Baud Rate Generation                       |  |

|      | 14.3.2   | Transmitter Functional Description         |  |

|      | 14.3.3   | Receiver Functional Description            |  |

|      |          | Interrupts and Status Flags                |  |

|      | 14.3.5   | Additional SCI Functions                   |  |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

| 15.1 | Introduction                                 |  |

|------|----------------------------------------------|--|

|      | 15.1.1 Features                              |  |

|      | 15.1.2 Block Diagrams                        |  |

|      | 15.1.3 SPI Baud Rate Generation              |  |

| 15.2 | External Signal Description                  |  |

|      | 15.2.1 SPSCK — SPI Serial Clock              |  |

|      | 15.2.2 MOSI — Master Data Out, Slave Data In |  |

|      | 15.2.3 MISO — Master Data In, Slave Data Out |  |

|      | 15.2.4 $\overline{SS}$ — Slave Select        |  |

| 15.3 | Modes of Operation                           |  |

|      | 15.3.1 SPI in Stop Modes                     |  |

| 15.4 | Register Definition                          |  |

|      | 15.4.1 SPI Control Register 1 (SPIC1)        |  |

|      | 15.4.2 SPI Control Register 2 (SPIC2)        |  |

|      |                                              |  |

# Chapter 1 Device Overview

The MC9S08SH8 members of the low-cost, high-performance HCS08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types.

# 1.1 Devices in the MC9S08SH8 Series

Table 1-1 summarizes the feature set available in the MC9S08SH8 series of MCUs.

| Feature              | 9S08SH8 |     |     | 9S08SH4          |      |     |     |                  |

|----------------------|---------|-----|-----|------------------|------|-----|-----|------------------|

| FLASH size (bytes)   |         | 81  | 92  |                  | 4096 |     |     |                  |

| RAM size (bytes)     |         | 5   | 12  |                  | 256  |     |     |                  |

| Pin quantity         | 24      | 20  | 16  | 8                | 24   | 20  | 16  | 8                |

| ACMP                 |         |     |     | ye               | es   |     |     |                  |

| ADC channels         | 12      | 12  | 8   | 4                | 12   | 12  | 8   | 4                |

| DBG                  |         |     |     | ye               | es   |     |     |                  |

| ICS                  | yes     | yes | yes | yes <sup>1</sup> | yes  | yes | yes | yes <sup>1</sup> |

| IIC                  | yes     |     |     |                  |      |     |     |                  |

| MTIM                 |         |     |     | ye               | es   |     |     |                  |

| Pin Interrupts       | 8       | 8   | 8   | 4                | 8    | 8   | 8   | 4                |

| Pin I/O <sup>2</sup> | 17      | 17  | 13  | 5                | 17   | 17  | 13  | 5                |

| RTC                  |         |     |     | ye               | es   |     |     |                  |

| SCI                  | yes     | yes | yes | no               | yes  | yes | yes | no               |

| SPI                  | yes     | yes | yes | no               | yes  | yes | yes | no               |

| TPM1 channels        | 2       | 2   | 2   | 1                | 2    | 2   | 2   | 1                |

| TPM2 channels        | 2       | 2   | 2   | 1                | 2    | 2   | 2   | 1                |

| XOSC                 | yes     | yes | yes | no               | yes  | yes | yes | no               |

#### Table 1-1. MC9S08SH8 Features by MCU and Package

<sup>1</sup> FBE and FEE modes are not available in 8-pin packages.

<sup>2</sup> Port I/O count does not include the output-only PTA4/ACMPO/BKGD/MS.

The voltage measured on the internally pulled up  $\overline{\text{RESET}}$  pin will not be pulled to  $V_{\text{DD}}$ . The internal gates connected to this pin are pulled to  $V_{\text{DD}}$ . If the  $\overline{\text{RESET}}$  pin is required to drive to a  $V_{\text{DD}}$  level an external pullup should be used.

#### NOTE

In EMC-sensitive applications, an external RC filter is recommended on the RESET. See Figure 2-5 for an example.

## 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.7.3, "System Background Debug Force Reset Register (SBDFR)," for more information), the PTA4/ACMPO/BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. When enabled as the BKGD/MS pin (BKGDPE = 1), an internal pullup device is automatically enabled.

The background debug communication function is enabled when BKGDPE in SOPT1 is set. BKGDPE is set following any reset of the MCU and must be cleared to use the PTA4/ACMPO/BKGD/MS pin's alternative pin function.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the maximum bus clock rate, so there must never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

## 2.2.5 General-Purpose I/O and Peripheral Ports

The MC9S08SH8 series of MCUs support up to 17 general-purpose I/O pins and 1 output-only pin, which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

Table 4-9. Security States<sup>1</sup>

SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.

## 4.7.3 FLASH Configuration Register (FCNFG

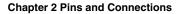

#### Figure 4-7. FLASH Configuration Register (FCNFG

#### Table 4-10. FCNFG Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.6, "Security."</li> <li>0 Writes to 0xFFB0–0xFFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>1 Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

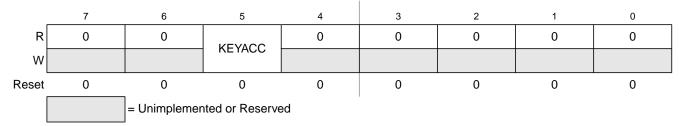

# 4.7.4 FLASH Protection Register (FPROT and NVPROT)

During reset, the contents of the nonvolatile location NVPROT are copied from FLASH into FPROT. This register can be read at any time. If FPDIS = 0, protection can be increased (that is, a smaller value of FPS can be written). If FPDIS = 1, writes do not change protection.

Background commands can be used to change the contents of these bits in FPROT.

Figure 4-8. FLASH Protection Register (FPROT)

MC9S08SH8 MCU Series Data Sheet, Rev. 3

1

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COP watchdog is enabled (see Section 5.7.4, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPT bits in SOPT1.

The COP counter is reset by writing 0x0055 and 0x00AA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x0055 or 0x00AA is written to SRS, the MCU is immediately reset.

The COPCLKS bit in SOPT2 (see Section 5.7.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there are three associated time-outs controlled by the COPT bits in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the longest time-out  $(2^{10} \text{ cycles})$ .

| Contr   | ol Bits   |       | Clock Source COP Window <sup>1</sup> Opens COP Overfl |                                                |

|---------|-----------|-------|-------------------------------------------------------|------------------------------------------------|

| COPCLKS | COPT[1:0] |       | (COPW = 1)                                            |                                                |

| N/A     | 0:0       | N/A   | N/A                                                   | COP is disabled                                |

| 0       | 0:1       | 1 kHz | N/A                                                   | 2 <sup>5</sup> cycles (32 ms <sup>2</sup> )    |

| 0       | 1:0       | 1 kHz | N/A                                                   | 2 <sup>8</sup> cycles (256 ms <sup>1</sup> )   |

| 0       | 1:1       | 1 kHz | N/A                                                   | 2 <sup>10</sup> cycles (1.024 s <sup>1</sup> ) |

| 1       | 0:1       | Bus   | 6144 cycles                                           | 2 <sup>13</sup> cycles                         |

| 1       | 1:0       | Bus   | 49,152 cycles                                         | 2 <sup>16</sup> cycles                         |

| 1       | 1:1       | Bus   | 196,608 cycles                                        | 2 <sup>18</sup> cycles                         |

#### Table 5-1. COP Configuration Option

<sup>1</sup> Windowed COP operation requires the user to clear the COP timer in the last 25% of the selected timeout period. This column displays the minimun number of clock counts required before the COP timer can be reset hen in windowed COP mode (COPW = 1).

<sup>2</sup> Values shown in in miliseconds based on  $t_{LPO} = 1$  ms. See  $t_{LPO}$  in the appendix Section A.12.1, "Control Timing" for the tolerance of this value.

When the bus clock source is selected, windowed COP operation is available by setting COPW in the SOPT2 register. In this mode, writes to the SRS register to clear the COP timer must occur in the last 25% of the selected timeout period. A premature write immediately resets the MCU. When the 1-kHz clock source is selected, windowed COP operation is not available.

**Chapter 6 Parallel Input/Output Control**

# 6.4 Pin Interrupts

Port A[3:0] and port B[3:0] pins can be configured as external interrupt inputs and as an external means of waking the MCU from stop3 or wait low-power modes.

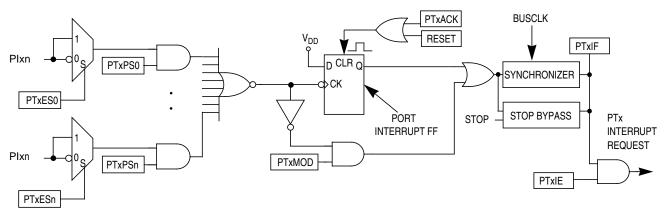

The block diagram for the pin interrupts is shown Figure 6-2.

Figure 6-2. Pin Interrupt Block Diagram

Writing to the PTxPSn bits in the port interrupt pin enable register (PTxPS) independently enables or disables each port pin interrupt. Each port can be configured as edge sensitive or edge and level sensitive based on the PTxMOD bit in the port interrupt status and control register (PTxSC). Edge sensitivity can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the PTxESn bits in the port interrupt edge select register (PTxES).

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled pin interrupt inputs must be at the deasserted logic level. A falling edge is detected when an enabled port input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

# 6.4.1 Edge Only Sensitivity

A valid edge on an enabled pin interrupt will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC.

# 6.4.2 Edge and Level Sensitivity

A valid edge or level on an enabled pin interrupt will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC provided all enabled pin interrupt inputs are at their deasserted levels. PTxIF will remain set if any enabled pin interrupt is asserted while attempting to clear by writing a 1 to PTxACK.

#### Chapter 7 Central Processor Unit (S08CPUV2)

#### Table 7-2. Instruction Set Summary (Sheet 9 of 9)

| Source<br>Form | Operation                                                            | Address<br>Mode | Object Code | /cles  | ≌ Cyc-by-Cyc<br>> Details | Affect<br>on CCR      |      |

|----------------|----------------------------------------------------------------------|-----------------|-------------|--------|---------------------------|-----------------------|------|

|                |                                                                      | PA<br>■         |             | ۍ<br>ر |                           | <b>V</b> 1 1 <b>H</b> | INZC |

| тхѕ            | Transfer Index Reg. to SP SP $\leftarrow$ (H:X) – \$0001             | INH             | 94          | 2      | fp                        | - 1 1 -               |      |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit $\leftarrow$ 0; Halt CPU | INH             | 8F          | 2+     | fp                        | - 1 1 -               | 0    |

Source Form: Everything in the source forms columns, except expressions in italic characters, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (#, () and +) are always a literal characters.

- Any label or expression that evaluates to a single integer in the range 0-7. n

- opr8i Any label or expression that evaluates to an 8-bit immediate value.

- opr16i Any label or expression that evaluates to a 16-bit immediate value.

- opr8a Any label or expression that evaluates to an 8-bit direct-page address (\$00xx).

- Any label or expression that evaluates to a 16-bit address. opr16a

- Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing. oprx8

- Any label or expression that evaluates to a 16-bit value, used for indexed addressing. oprx16

- rel Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction.

#### **Operation Symbols:**

- Accumulator А

- CCR Condition code register

- Index register high byte н

- Μ Memory location

- Any bit n

- Operand (one or two bytes) opr

- PC Program counter

- PCH Program counter high byte

- Program counter low byte PCL

- Relative program counter offset byte rel

- SP Stack pointer

- SPL

- Stack pointer low byte Х Index register low byte

- Logical AND &

- Logical OR . ⊕

- Logical EXCLUSIVE OR Contents of

- ()

- Add +

- Subtract, Negation (two's complement)

- × Multiply

- Divide ÷

- # Immediate value

- I oaded with  $\leftarrow$

- Concatenated with

#### CCR Bits:

- Overflow bit V

- Half-carry bit н

- Interrupt mask Т

- Ν Negative bit

- Ζ Zero bit

- С Carry/borrow bit

- Addressing Modes: DIR

- Direct addressing mode FXT

- Extended addressing mode Immediate addressing mode IMM

- INH Inherent addressing mode

- IX Indexed, no offset addressing mode

- IX1 Indexed, 8-bit offset addressing mode

- IX2 Indexed, 16-bit offset addressing mode

- IX+ Indexed, no offset, post increment addressing mode

- Indexed, 8-bit offset, post increment addressing mode IX1+

- REL Relative addressing mode

- Stack pointer, 8-bit offset addressing mode SP1

- SP2 Stack pointer 16-bit offset addressing mode

#### Cycle-by-Cycle Codes:

- Free cycle. This indicates a cycle where the CPU f does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

- Program fetch; read from next consecutive р location in program memory

- Read 8-bit operand r

- s

- Push (write) one byte onto stack Pop (read) one byte from stack

- u

- Read vector from \$FFxx (high byte first) v

- Write 8-bit operand w

#### CCR Effects:

- Set or cleared \$

- Not affected

- U Undefined

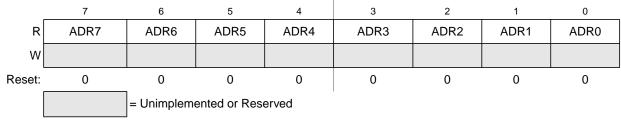

Figure 9-7. Data Result Low Register (ADCRL)

# 9.3.5 Compare Value High Register (ADCCVH)

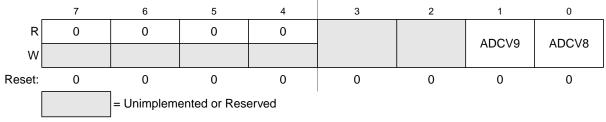

This register holds the upper two bits of the 10-bit compare value. These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled. In 8-bit operation, ADCCVH is not used during compare.

Figure 9-8. Compare Value High Register (ADCCVH)

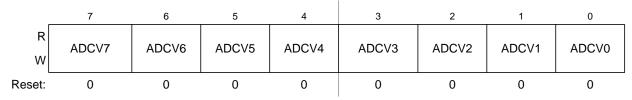

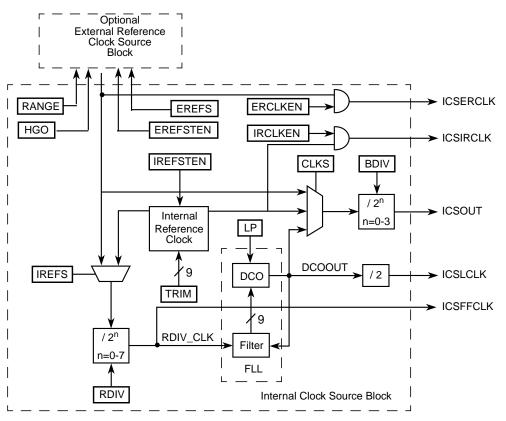

## 9.3.6 Compare Value Low Register (ADCCVL)

This register holds the lower 8 bits of the 10-bit compare value, or all 8 bits of the 8-bit compare value. Bits ADCV7:ADCV0 are compared to the lower 8 bits of the result following a conversion in either 10-bit or 8-bit mode.

# 9.3.7 Configuration Register (ADCCFG

ADCCFG is used to select the mode of operation, clock source, clock divide, and configure for low power or long sample time.

## 9.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

### 9.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 10-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source ( $R_{AS}$ ) is kept below 5 k $\Omega$ .

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

#### 9.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit mode or 10 in 10-bit mode).

#### 9.6.2.3 Noise-Induced Errors

System noise which occurs during the sample or conversion process can affect the accuracy of the conversion. The ADC accuracy numbers are guaranteed as specified only if the following conditions are met:

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>REFH</sub> to V<sub>REFL</sub>.

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- If inductive isolation is used from the primary supply, an additional 1  $\mu$ F capacitor is placed from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- $V_{SSAD}$  (and  $V_{REFL}$ , if connected) is connected to  $V_{SS}$  at a quiet point in the ground plane.

- Operate the MCU in wait or stop3 mode before initiating (hardware triggered conversions) or immediately after initiating (hardware or software triggered conversions) the ADC conversion.

- For software triggered conversions, immediately follow the write to the ADCSC1 with a WAIT instruction or STOP instruction.

- For stop3 mode operation, select ADACK as the clock source. Operation in stop3 reduces V<sub>DD</sub> noise but increases effective conversion time due to stop recovery.

- There is no I/O switching, input or output, on the MCU during the conversion.

There are some situations where external system activity causes radiated or conducted noise emissions or excessive  $V_{DD}$  noise is coupled into the ADC. In these situations, or when the MCU cannot be placed in wait or stop3 or I/O activity cannot be halted, these recommended actions may reduce the effect of noise on the accuracy:

• Place a 0.01  $\mu$ F capacitor (C<sub>AS</sub>) on the selected input channel to V<sub>REFL</sub> or V<sub>SSAD</sub> (this will improve noise issues but will affect sample rate based on the external analog source resistance).

Chapter 10 Internal Clock Source (S08ICSV2)

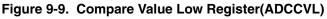

Figure 10-2. Internal Clock Source (ICS) Block Diagram

## 10.1.4 Modes of Operation

There are seven modes of operation for the ICS: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

## 10.1.4.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

## 10.1.4.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

## 10.1.4.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

#### Chapter 10 Internal Clock Source (S08ICSV2)

The CLKS bits can also be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. The actual switch to the newly selected clock will not occur until after a few full cycles of the new clock. If the newly selected clock is not available, the previous clock will remain selected.

### 10.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

### 10.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL to be disabled and thus conserve power when it is not being used. However, in some applications it may be desirable to enable the FLL and allow it to lock for maximum accuracy before switching to an FLL engaged mode. Do this by writing the LP bit to 0.

#### 10.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as ICSIRCLK, which can be used as an additional clock source. The ICSIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the ICSTRM register. Writing a larger value will slow down the ICSIRCLK frequency, and writing a smaller value to the ICSTRM register will speed up the ICSIRCLK frequency. The TRIM bits will effect the ICSOUT frequency if the ICS is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or FLL bypassed internal low power (FBILP) mode. The TRIM and FTRIM value will not be affected by a reset.

Until ICSIRCLK is trimmed, programming low reference divider (RDIV) factors may result in ICSOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN is set and the IRCLKEN bit is written to 1, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

All MCU devices are factory programmed with a trim value in a reserved memory location. This value can be copied to the ICSTRM register during reset initialization. The factory trim value does not include the FTRIM bit. For finer precision, the user can trim the internal oscillator in the application and set the FTRIM bit accordingly.

## 10.4.6 Optional External Reference Clock

The ICS module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in all modes. When the ERCLKEN is set, the external reference clock signal will be presented as ICSERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL and will only be used as ICSERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

# 11.3.3 IIC Control Register (IICC1)

Figure 11-5. IIC Control Register (IICC1)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.         0 IIC is not enabled         1 IIC is enabled                                                                                                                                                                                                                                               |

| 6<br>IICIE | <ul> <li>IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.</li> <li>0 IIC interrupt request not enabled</li> <li>1 IIC interrupt request enabled</li> </ul>                                                                                                                                                                             |

| 5<br>MST   | <ul> <li>Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave mode</li> <li>1 Master mode</li> </ul>                                                  |

| 4<br>TX    | <b>Transmit Mode Select.</b> The TX bit selects the direction of master and slave transfers. In master mode, this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high. When addressed as a slave, this bit should be set by software according to the SRW bit in the status register. 0 Receive 1 Transmit |

| 3<br>TXAK  | <ul> <li>Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge cycles for master and slave receivers.</li> <li>0 An acknowledge signal is sent out to the bus after receiving one data byte</li> <li>1 No acknowledge signal response is sent</li> </ul>                                                                    |

| 2<br>RSTA  | <b>Repeat start.</b> Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                              |

Chapter 11 Inter-Integrated Circuit (S08IICV2)

## 11.4.3 General Call Address

General calls can be requested in 7-bit address or 10-bit address. If the GCAEN bit is set, the IIC matches the general call address as well as its own slave address. When the IIC responds to a general call, it acts as a slave-receiver and the IAAS bit is set after the address cycle. Software must read the IICD register after the first byte transfer to determine whether the address matches is its own slave address or a general call. If the value is 00, the match is a general call. If the GCAEN bit is clear, the IIC ignores any data supplied from a general call address by not issuing an acknowledgement.

# 11.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

# 11.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 11-12 occur, provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a 1 to it in the interrupt routine. You can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | licif | IICIE        |

| Match of received calling address | IAAS   | licif | IICIE        |

| Arbitration Lost                  | ARBL   | licif | IICIE        |

Table 11-12. Interrupt Summary

## 11.6.1 Byte Transfer Interrupt

The TCF (transfer complete flag) bit is set at the falling edge of the ninth clock to indicate the completion of byte transfer.

## 11.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

## 11.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

#### Table 14-5. SCIxS1 Field Descriptions (continued)

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIxS1 with FE = 1 and then read the SCI data register (SCIxD).</li> <li>0 No framing error detected. This does not guarantee the framing is correct.</li> <li>1 Framing error.</li> </ul> |  |  |  |  |  |  |  |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                            |  |  |  |  |  |  |  |

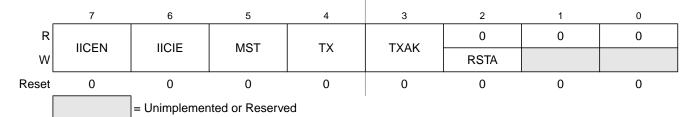

# 14.2.5 SCI Status Register 2 (SCIxS2)

This register has one read-only status flag.

#### Figure 14-9. SCI Status Register 2 (SCIxS2)

#### Table 14-6. SCIxS2 Field Descriptions

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>LBKDIF             | LIN Break Detect Interrupt Flag — LBKDIF is set when the LIN break detect circuitry is enabled and a LIN break character is detected. LBKDIF is cleared by writing a "1" to it.<br>0 No LIN break character has been detected.<br>1 LIN break character has been detected.                                                                                                           |  |  |  |  |  |  |

| 6<br>RXEDGIF            | <b>RxD Pin Active Edge Interrupt Flag</b> — RXEDGIF is set when an active edge (falling if RXINV = 0, rising if RXINV=1) on the RxD pin occurs. RXEDGIF is cleared by writing a "1" to it.         0 No active edge on the receive pin has occurred.         1 An active edge on the receive pin has occurred.                                                                       |  |  |  |  |  |  |

| 4<br>RXINV <sup>1</sup> | <ul> <li>Receive Data Inversion — Setting this bit reverses the polarity of the received data input.</li> <li>0 Receive data not inverted</li> <li>1 Receive data inverted</li> </ul>                                                                                                                                                                                                |  |  |  |  |  |  |

| 3<br>RWUID              | <ul> <li>Receive Wake Up Idle Detect— RWUID controls whether the idle character that wakes up the receiver sets the IDLE bit.</li> <li>0 During receive standby state (RWU = 1), the IDLE bit does not get set upon detection of an idle character.</li> <li>1 During receive standby state (RWU = 1), the IDLE bit gets set upon detection of an idle character.</li> </ul>         |  |  |  |  |  |  |

| 2<br>BRK13              | <ul> <li>Break Character Generation Length — BRK13 is used to select a longer transmitted break character length.</li> <li>Detection of a framing error is not affected by the state of this bit.</li> <li>0 Break character is transmitted with length of 10 bit times (11 if M = 1)</li> <li>1 Break character is transmitted with length of 13 bit times (14 if M = 1)</li> </ul> |  |  |  |  |  |  |

MC9S08SH8 MCU Series Data Sheet, Rev. 3

#### Table 15-3. SPIC2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4<br>MODFEN  | Master Mode-Fault Function Enable       When the SPI is configured for slave mode, this bit has no meaning or effect. (The SS pin is the slave select input.) In master mode, this bit determines how the SS pin is used (refer to Table 15-2 for more details).         0       Mode fault function disabled, master SS pin reverts to general-purpose I/O not controlled by SPI         1       Mode fault function enabled, master SS pin acts as the mode fault input or the slave select output                                                         |  |  |  |  |  |

| 3<br>BIDIROE | <b>Bidirectional Mode Output Enable</b> — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1,<br>BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin.<br>Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO<br>(SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect.<br>0 Output driver disabled so SPI data I/O pin acts as an input<br>1 SPI I/O pin enabled as an output |  |  |  |  |  |

| 1<br>SPISWAI | SPI Stop in Wait Mode         0 SPI clocks continue to operate in wait mode         1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 0<br>SPC0    | <ul> <li>SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.</li> <li>O SPI uses separate pins for data input and data output</li> <li>1 SPI configured for single-wire bidirectional operation</li> </ul>           |  |  |  |  |  |

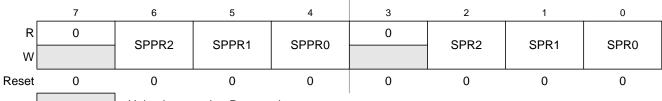

## 15.4.3 SPI Baud Rate Register (SPIBR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

= Unimplemented or Reserved

#### Figure 15-7. SPI Baud Rate Register (SPIBR)

#### Table 15-4. SPIBR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 6:4<br>SPPR[2:0] | <b>SPI Baud Rate Prescale Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 15-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 15-4). |  |  |  |  |  |  |

| 2:0<br>SPR[2:0]  | <b>SPI Baud Rate Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 15-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 15-4). The output of this divider is the SPI bit rate clock for master mode.            |  |  |  |  |  |  |

#### Table 15-7. SPIS Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPRF  | <ul> <li>SPI Read Buffer Full Flag — SPRF is set at the completion of an SPI transfer to indicate that received data may be read from the SPI data register (SPID). SPRF is cleared by reading SPRF while it is set, then reading the SPI data register.</li> <li>0 No data available in the receive data buffer</li> <li>1 Data available in the receive data buffer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>SPTEF | SPI Transmit Buffer Empty Flag — This bit is set when there is room in the transmit data buffer. It is cleared by reading SPIS with SPTEF set, followed by writing a data value to the transmit buffer at SPID. SPIS must be read with SPTEF = 1 before writing data to SPID or the SPID write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPIC1 is also set. SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register. For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPID is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer. After completion of the transfer of the value in the shift register, the queued value from the transmit buffer will automatically move to the shifter and SPTEF will be set to indicate there is room for new data in the transmit buffer. If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter. 0 SPI transmit buffer not empty 1 SPI transmit buffer empty |

| 4<br>MODF  | Master Mode Fault Flag — MODF is set if the SPI is configured as a master and the slave select input goes<br>low, indicating some other SPI device is also configured as a master. The SS pin acts as a mode fault error input<br>only when MSTR = 1, MODFEN = 1, and SSOE = 0; otherwise, MODF will never be set. MODF is cleared by<br>reading MODF while it is 1, then writing to SPI control register 1 (SPIC1).<br>0 No mode fault error<br>1 Mode fault error detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## 15.4.5 SPI Data Register (SPID)

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Figure 15-9. SPI Data Register (SPID)

Reads of this register return the data read from the receive data buffer. Writes to this register write data to the transmit data buffer. When the SPI is configured as a master, writing data to the transmit data buffer initiates an SPI transfer.

Data should not be written to the transmit data buffer unless the SPI transmit buffer empty flag (SPTEF) is set, indicating there is room in the transmit buffer to queue a new transmit byte.

Data may be read from SPID any time after SPRF is set and before another transfer is finished. Failure to read the data out of the receive data buffer before a new transfer ends causes a receive overrun condition and the data from the new transfer is lost.

MC9S08SH8 MCU Series Data Sheet, Rev. 3

Chapter 15 Serial Peripheral Interface (S08SPIV3)

# 15.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 15.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

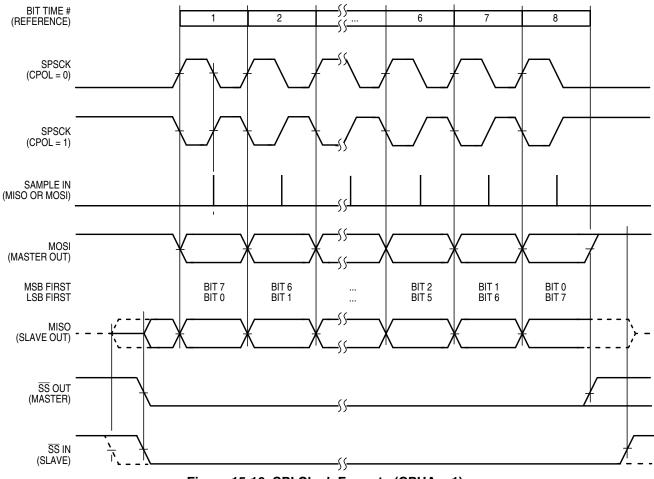

# 15.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 15-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output

pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low one-half SPSCK cycle before the start of the transfer and goes back high at the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 15-10. SPI Clock Formats (CPHA = 1)

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 15-11 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting

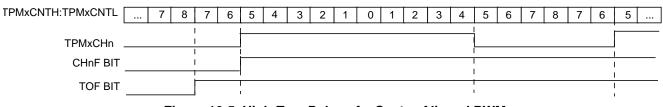

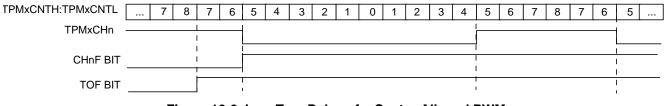

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter; the timer counter is counting up and the channel value register matches the timer counter; the timer counter is counter is counter; the timer counter is counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Figure 16-6. Low-True Pulse of a Center-Aligned PWM

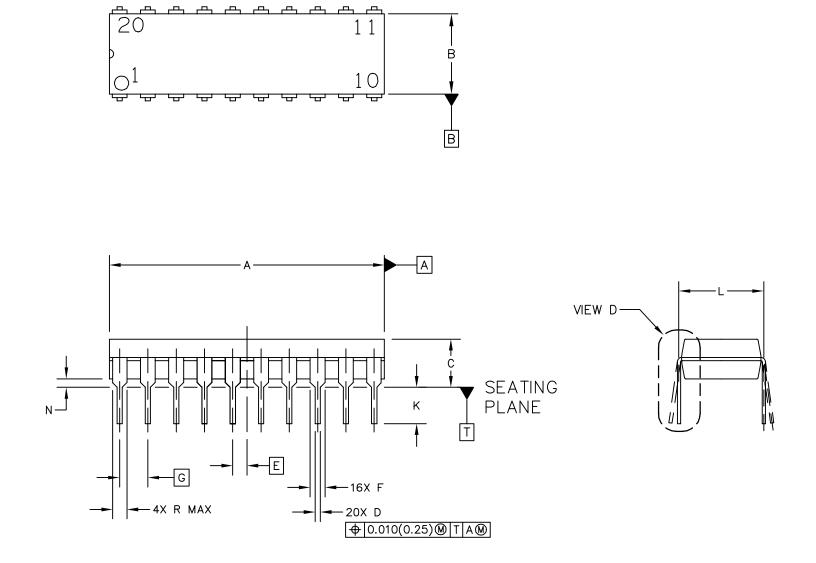

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA | CAL OUTLINE PRINT VERSION NOT TO SCA |                |             |

|---------------------------------------------------------|-----------|--------------------------------------|----------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO                          | ]: 98ASB42899B | RE∨: B      |

| 20LD .300 PDI                                           | D         | CASE NUMBER                          | R: 738C-01     | 24 MAY 2005 |

|                                                         |           | STANDARD: NO                         | IN-JEDEC       |             |