Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 40MHz                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 17                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 512 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                              |

| Supplier Device Package    | 20-DIP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08sh8cpj |

| Sec | ction N  | lumber Title                                     | Page |

|-----|----------|--------------------------------------------------|------|

|     | 8.1.3    | ACMP/TPM Configuration Information               |      |

|     | 8.1.4    | Features                                         |      |

|     | 8.1.5    | Modes of Operation                               |      |

|     | 8.1.6    | Block Diagram                                    |      |

| 8.2 |          | al Signal Description                            |      |

| 8.3 |          | ry Map                                           |      |

| 0.4 | 8.3.1    |                                                  |      |

| 8.4 | Function | onal Description                                 | 119  |

|     |          | Chapter 9 Analog-to-Digital Converter (S08ADCV1) |      |

| 9.1 | Introdu  | iction                                           | 121  |

|     | 9.1.1    | Channel Assignments                              |      |

|     | 9.1.2    | Alternate Clock                                  |      |

|     | 9.1.3    | Hardware Trigger                                 |      |

|     | 9.1.4    | Temperature Sensor                               |      |

|     | 9.1.5    | Features                                         |      |

|     | 9.1.6    | Block Diagram                                    |      |

| 9.2 | Externa  | al Signal Description                            |      |

|     | 9.2.1    | Analog Power (V <sub>DDAD</sub> )                | 127  |

|     | 9.2.2    | Analog Ground (V <sub>SSAD</sub> )               |      |

|     | 9.2.3    | Voltage Reference High (V <sub>REFH</sub> )      | 127  |

|     | 9.2.4    | Voltage Reference Low (V <sub>REFL</sub> )       |      |

|     | 9.2.5    | Analog Channel Inputs (ADx)                      |      |

| 9.3 | Registe  | er Definition                                    | 127  |

|     | 9.3.1    | Status and Control Register 1 (ADCSC1)           | 127  |

|     | 9.3.2    | Status and Control Register 2 (ADCSC2)           | 129  |

|     | 9.3.3    | Data Result High Register (ADCRH)                | 130  |

|     | 9.3.4    | Data Result Low Register (ADCRL)                 | 130  |

|     | 9.3.5    | Compare Value High Register (ADCCVH)             | 131  |

|     | 9.3.6    | Compare Value Low Register (ADCCVL)              | 131  |

|     | 9.3.7    | Configuration Register (ADCCFG)                  | 131  |

|     | 9.3.8    | Pin Control 1 Register (APCTL1)                  | 133  |

|     | 9.3.9    | Pin Control 2 Register (APCTL2)                  | 134  |

|     | 9.3.10   | Pin Control 3 Register (APCTL3)                  |      |

| 9.4 |          | onal Description                                 |      |

|     | 9.4.1    | Clock Select and Divide Control                  | 136  |

|     | 9.4.2    | Input Select and Pin Control                     | 137  |

|     | 9.4.3    | Hardware Trigger                                 | 137  |

|     | 9.4.4    | Conversion Control                               | 137  |

|     | 9.4.5    | Automatic Compare Function                       | 140  |

|     | 9.4.6    | MCU Wait Mode Operation                          | 140  |

|     |          |                                                  |      |

| Sec  | tion Number                                 | Title                     | Page |

|------|---------------------------------------------|---------------------------|------|

|      | 17.2.2 Communication Details                |                           | 270  |

|      | 17.2.3 BDC Commands                         |                           | 274  |

|      | 17.2.4 BDC Hardware Breakpoint              |                           | 276  |

| 17.3 | On-Chip Debug System (DBG)                  |                           | 277  |

|      | 17.3.1 Comparators A and B                  |                           | 277  |

|      | 17.3.2 Bus Capture Information and FIFO     | Operation                 | 277  |

|      | 17.3.3 Change-of-Flow Information           |                           | 278  |

|      | 17.3.4 Tag vs. Force Breakpoints and Tri    | ggers                     | 278  |

|      | 17.3.5 Trigger Modes                        |                           |      |

|      | 17.3.6 Hardware Breakpoints                 |                           | 281  |

| 17.4 | Register Definition                         |                           |      |

|      | 17.4.1 BDC Registers and Control Bits       |                           |      |

|      | 17.4.2 System Background Debug Force        |                           |      |

|      | 17.4.3 DBG Registers and Control Bits       |                           | 284  |

|      |                                             | pendix A                  |      |

|      |                                             | Characteristics           |      |

| A.1  | Introduction                                |                           |      |

| A.2  | Parameter Classification                    |                           |      |

| A.3  | Absolute Maximum Ratings                    |                           |      |

| A.4  | Thermal Characteristics                     |                           |      |

| A.5  | ESD Protection and Latch-Up Immunity        |                           |      |

| A.6  | DC Characteristics                          |                           |      |

| A.7  | Supply Current Characteristics              |                           |      |

| A.8  | External Oscillator (XOSC) Characteristics  |                           |      |

| A.9  | Internal Clock Source (ICS) Characteristics |                           |      |

|      | Analog Comparator (ACMP) Electricals        |                           |      |

|      | ADC Characteristics                         |                           |      |

| A.12 | AC Characteristics                          |                           |      |

|      | A.12.1 Control Timing                       |                           |      |

|      | A.12.2 TPM/MTIM Module Timing               |                           |      |

| . 10 | A.12.3 SPI                                  |                           |      |

|      | FLASH Specifications                        |                           |      |

| A.14 | EMC Performance                             |                           |      |

|      | A.14.1 Radiated Emissions                   |                           |      |

|      | A.14.2 Conducted Transient Susceptibility   | y                         | 316  |

|      | • •                                         | pendix B                  |      |

| D 1  |                                             | and Mechanical Drawings   | 210  |

| B.1  | Ordering Information                        |                           |      |

| D 2  | B.1.1 Device Numbering Scheme               |                           |      |

| B.2  | Mechanical Drawings                         |                           | 320  |

|      | MC9S08SH8 MCU                               | Series Data Sheet, Rev. 3 |      |

The voltage measured on the internally pulled up  $\overline{RESET}$  pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the  $\overline{RESET}$  pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### NOTE

In EMC-sensitive applications, an external RC filter is recommended on the  $\overline{\text{RESET}}$ . See Figure 2-5 for an example.

## 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.7.3, "System Background Debug Force Reset Register (SBDFR)," for more information), the PTA4/ACMPO/BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. When enabled as the BKGD/MS pin (BKGDPE = 1), an internal pullup device is automatically enabled.

The background debug communication function is enabled when BKGDPE in SOPT1 is set. BKGDPE is set following any reset of the MCU and must be cleared to use the PTA4/ACMPO/BKGD/MS pin's alternative pin function.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the maximum bus clock rate, so there must never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

# 2.2.5 General-Purpose I/O and Peripheral Ports

The MC9S08SH8 series of MCUs support up to 17 general-purpose I/O pins and 1 output-only pin, which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

### **Table 4-11. FPROT Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                                      |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:1<br>FPS | <b>FLASH Protect Select Bits</b> — When FPDIS = 0, this 7-bit field determines the ending address of unprotected FLASH locations at the high address end of the FLASH. Protected FLASH locations cannot be erased or programmed. |  |  |  |  |  |

| 0<br>FPDIS | FLASH Protection Disable 0 FLASH block specified by FPS[7:1] is block protected (program and erase not allowed). 1 No FLASH block is protected.                                                                                  |  |  |  |  |  |

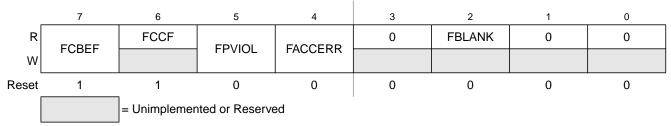

# 4.7.5 FLASH Status Register (FSTAT)

Figure 4-9. FLASH Status Register (FSTAT)

**Table 4-12. FSTAT Register Field Descriptions**

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FCBEF  | FLASH Command Buffer Empty Flag — The FCBEF bit is used to launch commands. It also indicates that the command buffer is empty so that a new command sequence can be executed when performing burst programming. The FCBEF bit is cleared by writing a 1 to it or when a burst program command is transferred to the array for programming. Only burst program commands can be buffered.  O Command buffer is full (not ready for additional commands).  A new burst program command can be written to the command buffer. |

| 6<br>FCCF   | FLASH Command Complete Flag — FCCF is set automatically when the command buffer is empty and no command is being processed. FCCF is cleared automatically when a new command is started (by writing 1 to FCBEF to register a command). Writing to FCCF has no meaning or effect.  O Command in progress  All commands complete                                                                                                                                                                                             |

| 5<br>FPVIOL | Protection Violation Flag — FPVIOL is set automatically when a command is written that attempts to erase or program a location in a protected block (the erroneous command is ignored). FPVIOL is cleared by writing a 1 to FPVIOL.  O No protection violation.  An attempt was made to erase or program a protected location.                                                                                                                                                                                             |

## 5.7.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                | 7                | 6                   | 5                   | 4                   | 3                   | 2              | 1    | 0 |

|------------------|------------------|---------------------|---------------------|---------------------|---------------------|----------------|------|---|

| R                | POR              | PIN                 | COP                 | ILOP                | ILAD                | 0              | LVD  | 0 |

| w                |                  | Wı                  | riting 0x55, 0xA    | A to SRS addr       | ess clears CO       | P watchdog tim | ner. |   |

| POR:             | 1                | 0                   | 0                   | 0                   | 0                   | 0              | 1    | 0 |

| LVR:             | u <sup>(1)</sup> | 0                   | 0                   | 0                   | 0                   | 0              | 1    | 0 |

| Any other reset: | 0                | Note <sup>(2)</sup> | Note <sup>(2)</sup> | Note <sup>(2)</sup> | Note <sup>(2)</sup> | 0              | 0    | 0 |

<sup>1</sup> u = unaffected

Figure 5-3. System Reset Status (SRS)

**Table 5-4. SRS Register Field Descriptions**

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.  O Reset not caused by POR.  1 POR caused reset.                                                                     |

| 6<br>PIN  | External Reset Pin — Reset was caused by an active-low level on the external reset pin.  O Reset not caused by external reset pin.  Reset came from external reset pin.                                                                                                                                                                                                                               |

| 5<br>COP  | Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPT bits = 0:0  Reset not caused by COP timeout. Reset caused by COP timeout.                                                                                                                                                                                |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.  O Reset not caused by an illegal opcode.  1 Reset caused by an illegal opcode. |

<sup>&</sup>lt;sup>2</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

## 6.4.3 Pull-up/Pull-down Resistors

The pin interrupts can be configured to use an internal pull-up/pull-down resistor using the associated I/O port pull-up enable register. If an internal resistor is enabled, the PTxES register is used to select whether the resistor is a pull-up (PTxESn = 0) or a pull-down (PTxESn = 1).

## 6.4.4 Pin Interrupt Initialization

When a pin interrupt is first enabled, it is possible to get a false interrupt flag. To prevent a false interrupt request during pin interrupt initialization, the user should do the following:

- 1. Mask interrupts by clearing PTxIE in PTxSC.

- 2. Select the pin polarity by setting the appropriate PTxESn bits in PTxES.

- 3. If using internal pull-up/pull-down device, configure the associated pull enable bits in PTxPE.

- 4. Enable the interrupt pins by setting the appropriate PTxPSn bits in PTxPS.

- 5. Write to PTxACK in PTxSC to clear any false interrupts.

- 6. Set PTxIE in PTxSC to enable interrupts.

## 6.5 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, I/O data previously stored in RAM, before the STOP instruction was executed, peripherals may require being initialized and restored to their pre-stop condition. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

## 6.6 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

Chapter 7 Central Processor Unit (S08CPUV2)

## 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

## 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

# 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

94 Freescale Semiconductor

### MC9S08SH8 MCU Series Data Sheet, Rev. 3

## 7.4.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

**Chapter 7 Central Processor Unit (S08CPUV2)**

# 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

Table 7-2. Instruction Set Summary (Sheet 1 of 9)

| Source<br>Form                                                                                                  | Operation                                                                | Address<br>Mode<br>Obje               | Object Code                                                                      | Cycles                               | Cyc-by-Cyc<br>Details           | Affect on CCR         |         |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|---------------------------------|-----------------------|---------|

| 1 01111                                                                                                         |                                                                          |                                       |                                                                                  |                                      |                                 | <b>V</b> 1 1 <b>H</b> | INZC    |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry $A \leftarrow (A) + (M) + (C)$                            | IMM DIR EXT IX2 IX1 IX SP2 SP1        | A9 ii B9 dd C9 hh ll D9 ee ff E9 ff F9 9E D9 ee ff 9E E9 ff                      | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp prpp rfp pprpp prpp | <b>↓11</b> ↑          | - 🗘 🗘   |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry $A \leftarrow (A) + (M)$                               | IMM DIR EXT IX2 IX1 IX SP2 SP1        | AB ii BB dd CB hh ll DB ee ff EB ff FB 9E DB ee ff 9E EB ff                      | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp prpp rfp pprpp prpp | <b>↓11</b>            | - 1 1   |

| AIS #opr8i                                                                                                      | Add Immediate Value (Signed) to Stack Pointer $SP \leftarrow (SP) + (M)$ | IMM                                   | A7 ii                                                                            | 2                                    | pp                              | - 1 1 -               |         |

| AIX #opr8i                                                                                                      | Add Immediate Value (Signed) to Index Register (H:X) H:X ← (H:X) + (M)   | IMM                                   | AF ii                                                                            | 2                                    | pp                              | - 1 1 -               |         |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP | Logical AND<br>A ← (A) & (M)                                             | IMM DIR EXT IX2 IX1 IX SP2 SP1        | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp rpp prpp rpp rfp pprpp prpp  | 011-                  | - ↑ ↑ - |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL oprx8,SP                                              | Arithmetic Shift Left  C 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0             | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp p p rfwpp rfwp prfwpp     | ↑ 1 1 -               | - 1 1 1 |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                              | Arithmetic Shift Right  b7 b0                                            | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp p p rfwpp rfwp prfwpp     | <b>↑11</b> —          | - 1 1 1 |

### Chapter 7 Central Processor Unit (S08CPUV2)

Table 7-2. Instruction Set Summary (Sheet 3 of 9)

| Source<br>Form                                                                                    | Operation                                                                                                                                                              | Address<br>Mode<br>Opject Co                                            | Object Code                                                                                  | de Cycles                            | Cyc-by-Cyc<br>Details                                                                  | Affect on CCR         |         |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|-----------------------|---------|

| 1 01111                                                                                           |                                                                                                                                                                        |                                                                         | ,                                                                                            |                                      |                                                                                        | <b>V</b> 1 1 <b>H</b> | INZC    |

| BPL rel                                                                                           | Branch if Plus (if N = 0)                                                                                                                                              | REL                                                                     | 2A rr                                                                                        | 3                                    | ppp                                                                                    | - 1 1 -               |         |

| BRA rel                                                                                           | Branch Always (if I = 1)                                                                                                                                               | REL                                                                     | 20 rr                                                                                        | 3                                    | ppp                                                                                    | - 1 1 -               |         |

| BRCLR n,opr8a,rel                                                                                 | Branch if Bit $n$ in Memory Clear (if (Mn) = 0)                                                                                                                        | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 01 dd rr<br>03 dd rr<br>05 dd rr<br>07 dd rr<br>09 dd rr<br>0B dd rr<br>0D dd rr<br>0F dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5      | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp                            | - 1 1 -               | \$      |

| BRN rel                                                                                           | Branch Never (if I = 0)                                                                                                                                                | REL                                                                     | 21 rr                                                                                        | 3                                    | ppp                                                                                    | - 1 1 -               |         |

| BRSET n,opr8a,rel                                                                                 | Branch if Bit <i>n</i> in Memory Set (if (Mn) = 1)                                                                                                                     | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 00 dd rr<br>02 dd rr<br>04 dd rr<br>06 dd rr<br>08 dd rr<br>0A dd rr<br>0C dd rr<br>0E dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5      | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp | - 1 1 -               | \$      |

| BSET n,opr8a                                                                                      | Set Bit $n$ in Memory (Mn $\leftarrow$ 1)                                                                                                                              | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 10 dd<br>12 dd<br>14 dd<br>16 dd<br>18 dd<br>1A dd<br>1C dd<br>1E dd                         | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp rfwpp rfwpp rfwpp rfwpp rfwpp rfwpp rfwpp rfwpp                                  | - 1 1 -               |         |

| BSR rel                                                                                           | Branch to Subroutine $ PC \leftarrow (PC) + \$0002 $ push (PCL); $SP \leftarrow (SP) - \$0001 $ push (PCH); $SP \leftarrow (SP) - \$0001 $ $PC \leftarrow (PC) + rel $ | REL                                                                     | AD rr                                                                                        | 5                                    | sappp                                                                                  | - 1 1 -               |         |

| CBEQ opr8a,rel CBEQA #opr8i,rel CBEQX #opr8i,rel CBEQ oprx8,X+,rel CBEQ ,X+,rel CBEQ oprx8,SP,rel | Compare and Branch if (A) = (M) Branch if (A) = (M) Branch if (X) = (M) Branch if (A) = (M) Branch if (A) = (M) Branch if (A) = (M)                                    | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                 | 31 dd rr<br>41 ii rr<br>51 ii rr<br>61 ff rr<br>71 rr<br>9E 61 ff rr                         | 5<br>4<br>4<br>5<br>5                | rpppp<br>pppp<br>rpppp<br>rfppp<br>rfppp                                               | - 1 1 -               |         |

| CLC                                                                                               | Clear Carry Bit (C ← 0)                                                                                                                                                | INH                                                                     | 98                                                                                           | 1                                    | р                                                                                      | - 1 1 -               | 0       |

| CLI                                                                                               | Clear Interrupt Mask Bit (I ← 0)                                                                                                                                       | INH                                                                     | 9A                                                                                           | 1                                    | р                                                                                      | - 1 1 -               | 0       |

| CLR opr8a CLRA CLRX CLRH CLR oprx8,X CLR ,X CLR oprx8,SP                                          | Clear M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00<br>M ← \$00                                                                                 | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1                            | 3F dd<br>4F<br>5F<br>8C<br>6F ff<br>7F<br>9E 6F ff                                           | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp p p rfwpp rfwpp prfwpp                                                           | 0 1 1 -               | - 0 1 - |

#### Chapter 8 Analog Comparator 5-V (S08ACMPV2)

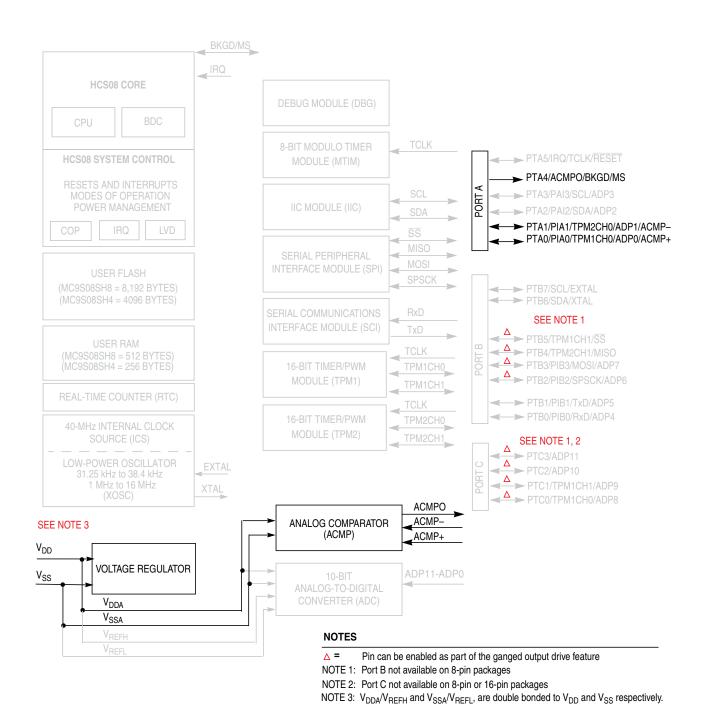

Figure 8-1. MC9S08SH8 Block Diagram Highlighting the ACMP Module

are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

# 9.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) are used to disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

## 9.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

### 9.4.4 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC module can be configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

## 9.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

#### Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

- Average the result by converting the analog input many times in succession and dividing the sum of the results. Four samples are required to eliminate the effect of a 1LSB, one-time error.

- Reduce the effect of synchronous noise by operating off the asynchronous clock (ADACK) and averaging. Noise that is synchronous to ADCK cannot be averaged out.

### 9.6.2.4 Code Width and Quantization Error

The ADC quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points to one code and the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

$$1LSB = (V_{REFH} - V_{REFL}) / 2^{N}$$

Eqn. 9-2

There is an inherent quantization error due to the digitization of the result. For 8-bit or 10-bit conversions the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm$  1/2LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

## 9.6.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error (E<sub>ZS</sub>) (sometimes called offset) This error is defined as the difference between

the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first

conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is

used.

- Full-scale error (E<sub>FS</sub>) This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

# 9.6.2.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the

MC9S08SH8 MCU Series Data Sheet, Rev. 3

#### Chapter 10 Internal Clock Source (S08ICSV2)

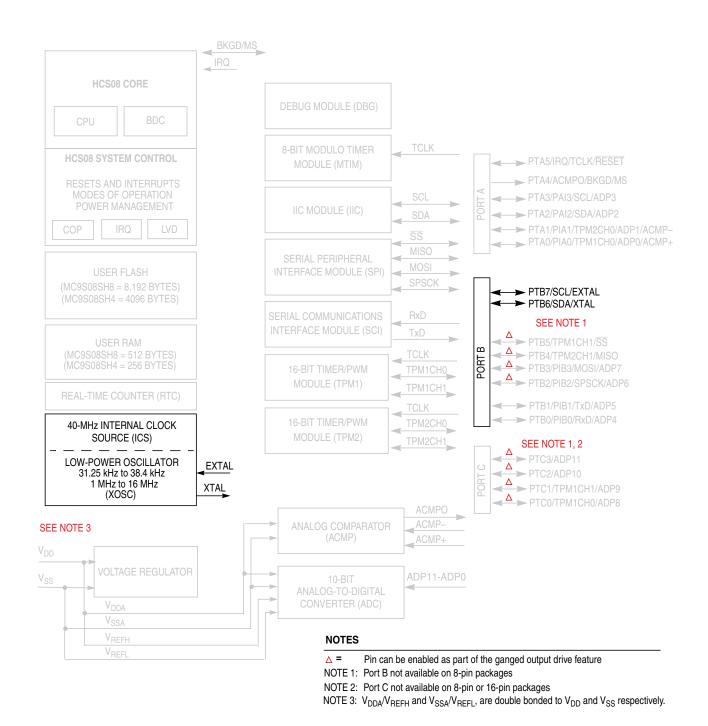

Figure 10-1. MC9S08SH8 Block Diagram Highlighting the ICS Module

| <b>Table 15-3. SP</b> | IC2 Register | Field Descr | iptions |

|-----------------------|--------------|-------------|---------|

|-----------------------|--------------|-------------|---------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MODFEN  | Master Mode-Fault Function Enable — When the SPI is configured for slave mode, this bit has no meaning or effect. (The $\overline{SS}$ pin is the slave select input.) In master mode, this bit determines how the $\overline{SS}$ pin is used (refer to Table 15-2 for more details).  0 Mode fault function disabled, master $\overline{SS}$ pin reverts to general-purpose I/O not controlled by SPI 1 Mode fault function enabled, master $\overline{SS}$ pin acts as the mode fault input or the slave select output              |

| 3<br>BIDIROE | Bidirectional Mode Output Enable — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1, BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin. Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO (SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect. 0 Output driver disabled so SPI data I/O pin acts as an input 1 SPI I/O pin enabled as an output |

| 1<br>SPISWAI | SPI Stop in Wait Mode 0 SPI clocks continue to operate in wait mode 1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0<br>SPC0    | SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.  0 SPI uses separate pins for data input and data output 1 SPI configured for single-wire bidirectional operation                          |

# 15.4.3 SPI Baud Rate Register (SPIBR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

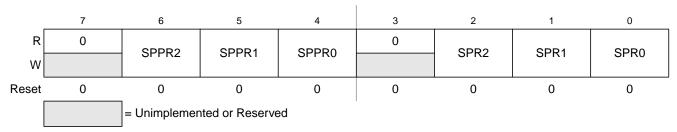

Figure 15-7. SPI Baud Rate Register (SPIBR)

Table 15-4. SPIBR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>SPPR[2:0] | SPI Baud Rate Prescale Divisor — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 15-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 15-4). |

| 2:0<br>SPR[2:0]  | SPI Baud Rate Divisor — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 15-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 15-4). The output of this divider is the SPI bit rate clock for master mode.            |

MC9S08SH8 MCU Series Data Sheet, Rev. 3

#### Chapter 15 Serial Peripheral Interface (S08SPIV3)

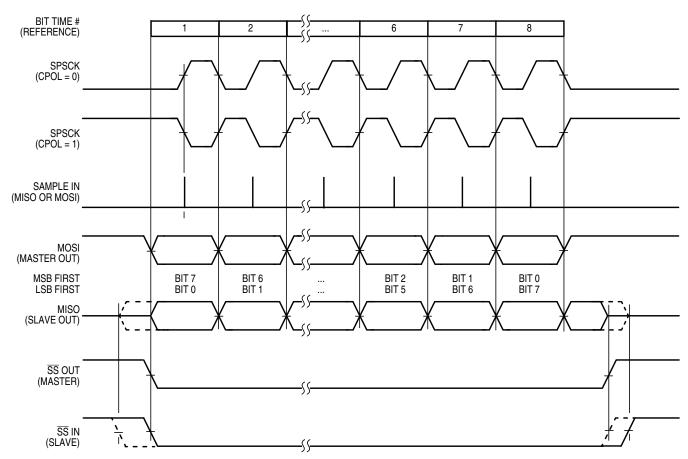

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 15-11. SPI Clock Formats (CPHA = 0)

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

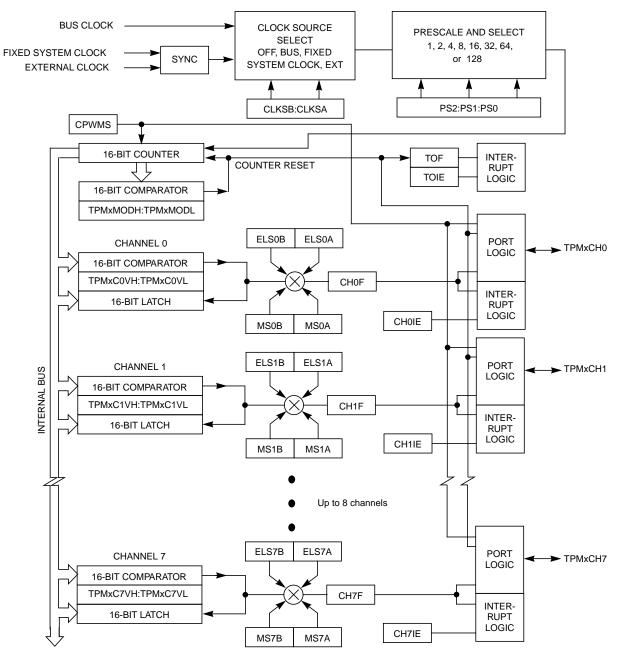

Figure 16-2. TPM Block Diagram

#### Chapter 16 Timer/PWM Module (S08TPMV3)

to avoid such settings.) The TPM channel could still be used in output compare mode for software timing functions (pin controls set not to affect the TPM channel pin).

### 16.4.1.2 Counter Overfl w and Modulo Reset

An interrupt flag and enable are associated with the 16-bit main counter. The flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE=0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE=1) where a static hardware interrupt is generated whenever the TOF flag is equal to one.

The conditions causing TOF to become set depend on whether the TPM is configured for center-aligned PWM (CPWMS=1). In the simplest mode, there is no modulus limit and the TPM is not in CPWMS=1 mode. In this case, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the TPM is in center-aligned PWM mode (CPWMS=1), the TOF flag gets set as the counter changes direction at the end of the count value set in the modulus register (that is, at the transition from the value set in the modulus register to the next lower count value). This corresponds to the end of a PWM period (the 0x0000 count value corresponds to the center of a period).

## 16.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

### 16.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

### 16.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

**Table 17-1. BDC Command Summary**

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |

|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to Freescale document order no. HCS08RMv1/D           |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to Freescale document order no. HCS08RMv1/D          |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging (HCS08 devices have no external tagging pin)      |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                                |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte located at H:X                              |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |

$<sup>^{\</sup>mbox{\scriptsize 1}}$  The SYNC command is a special operation that does not have a command code.

### MC9S08SH8 MCU Series Data Sheet, Rev. 3

**Chapter 17 Development Support**

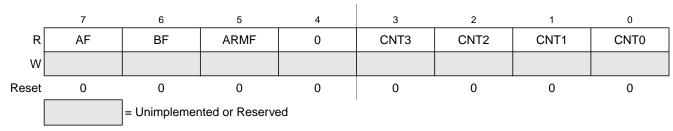

# 17.4.3.9 Debug Status Register (DBGS)

This is a read-only status register.

Figure 17-9. Debug Status Register (DBGS)

**Table 17-6. DBGS Register Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>AF         | Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.  O Comparator A has not matched  Comparator A match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6<br>BF         | Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.  O Comparator B has not matched  Comparator B match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 5<br>ARMF       | Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writing 1 to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. A debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). A debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.  0 Debugger not armed 1 Debugger armed                                                                                                                                                                                                                                                                  |  |  |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO. 0000 Number of valid words in FIFO = No valid data 0001 Number of valid words in FIFO = 1 0010 Number of valid words in FIFO = 2 0011 Number of valid words in FIFO = 3 0100 Number of valid words in FIFO = 4 0101 Number of valid words in FIFO = 5 0110 Number of valid words in FIFO = 6 0111 Number of valid words in FIFO = 7 1000 Number of valid words in FIFO = 8 |  |  |