Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | 508                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 40MHz                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                        |

| Peripherals                | LVD, POR, PWM, WDT                                        |

| Number of I/O              | 5                                                         |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | 8-SOIC                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08sh8csc |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Addendum for Revision 3.0

# 1 Addendum for Revision 3.0

#### Table 1. MC9S08SH8 Rev 3.0 Addendum

| Location               | Description                                                                                                                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix A "Electrical | In "Control Timing" table, changed minimum value of "Internal low power oscillator period" parameter from 800 $\mu$ s to 700 $\mu$ s. This value is under 5V VDD, -40 °C to 125 °C temperature range condition. |

# 2 Revision History

Table 2 provides a revision history for this document.

#### Table 2. Revision History Table

| Rev. Number | Substantive Changes                                                                                                                                    | Date of Release |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|             | Initial release. Changed minimum value of "Internal low power oscillator period" parameter from 800 $\mu$ s to 700 $\mu$ s, in "Control Timing" table. | 05/2012         |

# MC9S08SH8 MC9S08SH4

Data Sheet

HCS08 Microcontrollers

MC9S08SH8 Rev. 3 6/2008

freescale.com

# Contents

**Section Number**

Page

### Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08SH8 Series | 19 |

|-----|---------------------------------|----|

| 1.2 | MCU Block Diagram               | 20 |

| 1.3 | System Clock Distribution       | 22 |

# Chapter 2 Pins and Connections

| Device | Pin Assignment                             | 23                                                                                                                                                                                                                                           |

|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                            |                                                                                                                                                                                                                                              |

|        |                                            |                                                                                                                                                                                                                                              |

| 2.2.2  | Oscillator (XOSC)                          | 26                                                                                                                                                                                                                                           |

| 2.2.3  | RESET                                      | 26                                                                                                                                                                                                                                           |

| 2.2.4  | Background / Mode Select (BKGD/MS)         | 27                                                                                                                                                                                                                                           |

| 2.2.5  | General-Purpose I/O and Peripheral Ports   | 27                                                                                                                                                                                                                                           |

|        | Recomm<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | Device Pin Assignment         Recommended System Connections         2.2.1 Power         2.2.2 Oscillator (XOSC)         2.2.3 RESET         2.2.4 Background / Mode Select (BKGD/MS)         2.2.5 General-Purpose I/O and Peripheral Ports |

# Chapter 3 Modes of Operation

| 3.1 | Introduc | ction                                    | 31 |

|-----|----------|------------------------------------------|----|

| 3.2 | Features | 5                                        | 31 |

| 3.3 | Run Mo   | ode                                      | 31 |

| 3.4 | Active I | Background Mode                          | 31 |

|     |          | ode                                      |    |

| 3.6 | Stop Mo  | odes                                     | 32 |

|     | 1        | Stop3 Mode                               |    |

|     | 3.6.2    | Stop2 Mode                               | 34 |

|     | 3.6.3    | On-Chip Peripheral Modules in Stop Modes | 34 |

# Chapter 4 Memory

| 4.1 | MC9S0 | 8SH8 Memory Map                 | 37 |

|-----|-------|---------------------------------|----|

|     |       | nd Interrupt Vector Assignments |    |

|     |       | Addresses and Bit Assignments   |    |

|     | -     |                                 |    |

| 4.5 | FLASH |                                 | 46 |

|     | 4.5.1 | Features                        | 47 |

|     | 4.5.2 | Program and Erase Times         | 47 |

|     |       |                                 |    |

# **Section Number**

# Title

### Page

|      | 11.3.2     | IIC Frequency Divider Register (IICF) | 167 |

|------|------------|---------------------------------------|-----|

|      | 11.3.3     | IIC Control Register (IICC1)          | 170 |

|      |            | IIC Status Register (IICS)            |     |

|      | 11.3.5     | IIC Data I/O Register (IICD)          | 172 |

|      | 11.3.6     | IIC Control Register 2 (IICC2)        | 172 |

| 11.4 | Function   | nal Description                       | 173 |

|      | 11.4.1     | IIC Protocol                          | 173 |

|      | 11.4.2     | 10-bit Address                        | 177 |

|      | 11.4.3     | General Call Address                  | 178 |

| 11.5 | Resets .   |                                       | 178 |

| 11.6 | Interrup   | ts                                    | 178 |

|      | 11.6.1     | Byte Transfer Interrupt               | 178 |

|      |            | Address Detect Interrupt              |     |

|      | 11.6.3     | Arbitration Lost Interrupt            | 178 |

| 11.7 | Initializa | ation/Application Information         |     |

# Chapter 12 Modulo Timer (S08MTIMV1)

| 12.1 | Introduction                       |                   |

|------|------------------------------------|-------------------|

|      | 12.1.1 MTIM Configuration Informa  | tion              |

|      | 12.1.2 Features                    |                   |

|      | 12.1.3 Modes of Operation          |                   |

|      | 12.1.4 Block Diagram               |                   |

| 12.2 | 2 External Signal Description      |                   |

| 12.3 | B Register Definition              |                   |

|      | 12.3.1 MTIM Status and Control Reg | tister (MTIMSC)   |

|      | 12.3.2 MTIM Clock Configuration R  | egister (MTIMCLK) |

|      | 12.3.3 MTIM Counter Register (MT)  | MCNT)             |

|      | 12.3.4 MTIM Modulo Register (MTI   | MMOD)             |

| 12.4 | Functional Description             |                   |

|      | 12.4.1 MTIM Operation Example      |                   |

|      | ÷ *                                |                   |

# Chapter 13 Real-Time Counter (S08RTCV1)

| 13.1 | Introduction                                   | 193 |

|------|------------------------------------------------|-----|

|      | 13.1.1 Features                                |     |

|      | 13.1.2 Modes of Operation                      | 195 |

|      | 13.1.3 Block Diagram                           | 196 |

| 13.2 | External Signal Description                    |     |

|      | Register Definition                            |     |

|      | 13.3.1 RTC Status and Control Register (RTCSC) |     |

|      | 13.3.2 RTC Counter Register (RTCCNT)           |     |

|      |                                                |     |

MC9S08SH8 MCU Series Data Sheet, Rev. 3

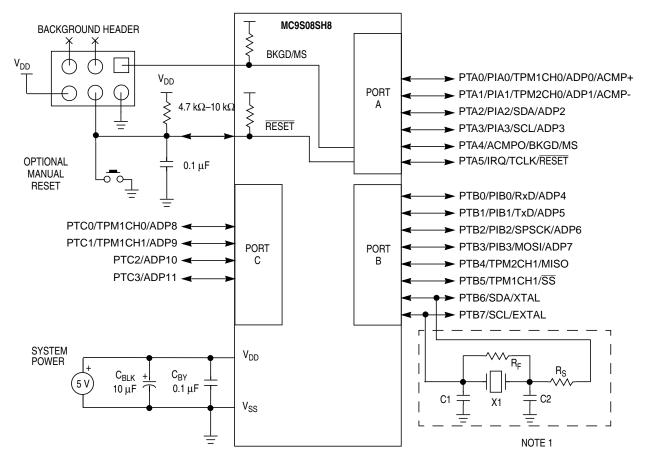

NOTES:

- 1. External crystal circuit not required if using the internal clock option.

- RESET pin can only be used to reset into user mode, you can not enter BDM using RESET pin. BDM can be entered by holding MS low during POR or writing a 1 to BDFR in SBDFR with MS low after issuing BDM command.

- 3. RC filter on RESET pin recommended for noisy environments.

#### Figure 2-5. Basic System Connections

#### 2.2.1 **Power**

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry, ACMP and ADC modules, and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise. Each pin must have a bypass capacitor for best noise suppression.

# 5.7.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

|                     | 7                | 6                   | 5                   | 4                   | 3                   | 2              | 1    | 0 |

|---------------------|------------------|---------------------|---------------------|---------------------|---------------------|----------------|------|---|

| R                   | POR              | PIN                 | COP                 | ILOP                | ILAD                | 0              | LVD  | 0 |

| W                   |                  | Wi                  | riting 0x55, 0xA    | A to SRS addr       | ess clears CO       | P watchdog tim | ier. |   |

| POR:                | 1                | 0                   | 0                   | 0                   | 0                   | 0              | 1    | 0 |

| LVR:                | u <sup>(1)</sup> | 0                   | 0                   | 0                   | 0                   | 0              | 1    | 0 |

| Any other<br>reset: | 0                | Note <sup>(2)</sup> | Note <sup>(2)</sup> | Note <sup>(2)</sup> | Note <sup>(2)</sup> | 0              | 0    | 0 |

<sup>1</sup> u = unaffected

<sup>2</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-4. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                                     |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                             |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPT bits = 0:0</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                           |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul> |

### 8.1.4 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPO.

- Can operate in stop3 mode

### 8.1.5 Modes of Operation

This section defines the ACMP operation in wait, stop and background debug modes.

### 8.1.5.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt, ACIE is enabled. For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 8.1.5.2 ACMP in Stop Modes

### 8.1.5.2.1 Stop3 Mode Operation

The ACMP continues to operate in Stop3 mode if enabled and compare operation remains active. If ACOPE is enabled, comparator output operates as in the normal operating mode and comparator output is placed onto the external pin. The MCU is brought out of stop when a compare event occurs and ACIE is enabled; ACF flag sets accordingly.

If stop is exited with a reset, the ACMP will be put into its reset state.

### 8.1.5.2.2 Stop2 and Stop1 Mode Operation

During either Stop2 and Stop1 mode, the ACMP module will be fully powered down. Upon wake-up from Stop2 or Stop1 mode, the ACMP module will be in the reset state.

### 8.1.5.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP will continue to operate normally.

### 8.1.6 Block Diagram

The block diagram for the Analog Comparator module is shown Figure 8-2.

MC9S08SH8 MCU Series Data Sheet, Rev. 3

Chapter 8 Analog Comparator (S08ACMPV2)

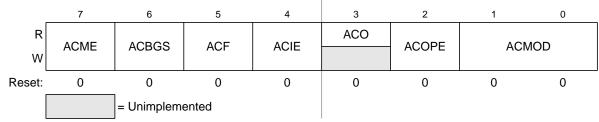

# 8.3.1.1 ACMP Status and Control Register (ACMPSC)

ACMPSC contains the status flag and control bits which are used to enable and configure the ACMP.

#### Figure 8-3. ACMP Status and Control Register

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACME    | <ul> <li>Analog Comparator Module Enable — ACME enables the ACMP module.</li> <li>0 ACMP not enabled</li> <li>1 ACMP is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

| 6<br>ACBGS   | <ul> <li>Analog Comparator Bandgap Select — ACBGS is used to select between the bandgap reference voltage or the ACMP+ pin as the input to the non-inverting input of the analog comparatorr.</li> <li>0 External pin ACMP+ selected as non-inverting input to comparator</li> <li>1 Internal reference select as non-inverting input to comparator</li> <li>Note: refer to this chapter introduction to verify if any other config bits are necessary to enable the bandgap reference in the chip level.</li> </ul> |

| 5<br>ACF     | <ul> <li>Analog Comparator Flag — ACF is set when a compare event occurs. Compare events are defined by ACMOD.</li> <li>ACF is cleared by writing a one to ACF.</li> <li>0 Compare event has not occured</li> <li>1 Compare event has occured</li> </ul>                                                                                                                                                                                                                                                             |

| 4<br>ACIE    | <ul> <li>Analog Comparator Interrupt Enable — ACIE enables the interrupt from the ACMP. When ACIE is set, an interrupt will be asserted when ACF is set.</li> <li>0 Interrupt disabled</li> <li>1 Interrupt enabled</li> </ul>                                                                                                                                                                                                                                                                                       |

| 3<br>ACO     | Analog Comparator Output — Reading ACO will return the current value of the analog comparator output. ACO is reset to a 0 and will read as a 0 when the ACMP is disabled (ACME = 0).                                                                                                                                                                                                                                                                                                                                 |

| 2<br>ACOPE   | <ul> <li>Analog Comparator Output Pin Enable — ACOPE is used to enable the comparator output to be placed onto the external pin, ACMPO.</li> <li>0 Analog comparator output not available on ACMPO</li> <li>1 Analog comparator output is driven out on ACMPO</li> </ul>                                                                                                                                                                                                                                             |

| 1:0<br>ACMOD | Analog Comparator Mode — ACMOD selects the type of compare event which sets ACF.         00 Encoding 0 — Comparator output falling edge         01 Encoding 1 — Comparator output rising edge         10 Encoding 2 — Comparator output falling edge         11 Encoding 3 — Comparator output rising or falling edge                                                                                                                                                                                                |

#### Table 8-2. ACMP Status and Control Register Field Descriptions

MC9S08SH8 MCU Series Data Sheet, Rev. 3

Chapter 12 Modulo Timer (S08MTIMV1)

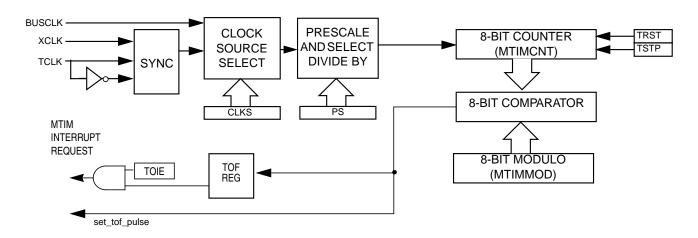

# 12.1.4 Block Diagram

The block diagram for the modulo timer module is shown Figure 12-2.

# 12.2 External Signal Description

The MTIM includes one external signal, TCLK, used to input an external clock when selected as the MTIM clock source. The signal properties of TCLK are shown in Table 12-1.

| Table 12-1. | Signal | Properties |

|-------------|--------|------------|

|-------------|--------|------------|

| Signal | Function                              |   |

|--------|---------------------------------------|---|

| TCLK   | External clock source input into MTIM | Ι |

The TCLK input must be synchronized by the bus clock. Also, variations in duty cycle and clock jitter must be accommodated. Therefore, the TCLK signal must be limited to one-fourth of the bus frequency.

The TCLK pin can be muxed with a general-purpose port pin. See the Pins and Connections chapter for the pin location and priority of this function.

Chapter 12 Modulo Timer (S08MTIMV1)

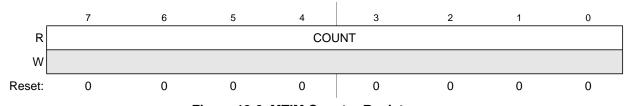

# 12.3.3 MTIM Counter Register (MTIMCNT)

MTIMCNT is the read-only value of the current MTIM count of the 8-bit counter.

Figure 12-6. MTIM Counter Register

| Field | Description                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>MTIM Count</b> — These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset clears the count to \$00. |

# 12.3.4 MTIM Modulo Register (MTIMMOD)

Figure 12-7. MTIM Modulo Register

#### Table 12-5. MTIM Modulo Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>MOD | <b>MTIM Modulo</b> — These eight read/write bits contain the modulo value used to reset the count and set TOF. A value of \$00 puts the MTIM in free-running mode. Writing to MTIMMOD resets the COUNT to \$00 and clears TOF. Reset sets the modulo to \$00. |

#### Chapter 13 Real-Time Counter (S08RTCV1)

```

#pragma TRAP_PROC

void RTC_ISR(void)

{

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59){

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59){

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23){

Days ++;

Hours = 0;

}

}

```

Writing 0 to TE does not immediately release the pin to be a general-purpose I/O pin. Any transmit activity that is in progress must first be completed. This includes data characters in progress, queued idle characters, and queued break characters.

### 14.3.2.1 Send Break and Queued Idle

The SBK control bit in SCIxC2 is used to send break characters which were originally used to gain the attention of old teletype receivers. Break characters are a full character time of logic 0 (10 bit times including the start and stop bits). A longer break of 13 bit times can be enabled by setting BRK13 = 1. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 1 and then write 0 to the SBK bit. This action queues a break character to be sent as soon as the shifter is available. If SBK is still 1 when the queued break moves into the shifter (synchronized to the baud rate clock), an additional break character is queued. If the receiving device is another Freescale Semiconductor SCI, the break characters will be received as 0s in all eight data bits and a framing error (FE = 1) occurs.

When idle-line wakeup is used, a full character time of idle (logic 1) is needed between messages to wake up any sleeping receivers. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 0 and then write 1 to the TE bit. This action queues an idle character to be sent as soon as the shifter is available. As long as the character in the shifter does not finish while TE = 0, the SCI transmitter never actually releases control of the TxD pin. If there is a possibility of the shifter finishing while TE = 0, set the general-purpose I/O controls so the pin that is shared with TxD is an output driving a logic 1. This ensures that the TxD line will look like a normal idle line even if the SCI loses control of the port pin between writing 0 and then 1 to TE.

The length of the break character is affected by the BRK13 and M bits as shown below.

| BRK13 | М | Break Character Length |

|-------|---|------------------------|

| 0     | 0 | 10 bit times           |

| 0     | 1 | 11 bit times           |

| 1     | 0 | 13 bit times           |

| 1     | 1 | 14 bit times           |

Table 14-8. Break Character Length

### 14.3.3 Receiver Functional Description

In this section, the receiver block diagram (Figure 14-3) is used as a guide for the overall receiver functional description. Next, the data sampling technique used to reconstruct receiver data is described in more detail. Finally, two variations of the receiver wakeup function are explained.

The receiver input is inverted by setting RXINV = 1. The receiver is enabled by setting the RE bit in SCIxC2. Character frames consist of a start bit of logic 0, eight (or nine) data bits (LSB first), and a stop bit of logic 1. For information about 9-bit data mode, refer to Section 14.3.5.1, "8- and 9-Bit Data Modes." For the remainder of this discussion, we assume the SCI is configured for normal 8-bit data mode.

After receiving the stop bit into the receive shifter, and provided the receive data register is not already full, the data character is transferred to the receive data register and the receive data register full (RDRF) status

#### Table 15-3. SPIC2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MODFEN  | Master Mode-Fault Function Enable       When the SPI is configured for slave mode, this bit has no meaning or effect. (The SS pin is the slave select input.) In master mode, this bit determines how the SS pin is used (refer to Table 15-2 for more details).         0       Mode fault function disabled, master SS pin reverts to general-purpose I/O not controlled by SPI         1       Mode fault function enabled, master SS pin acts as the mode fault input or the slave select output                                                         |

| 3<br>BIDIROE | <b>Bidirectional Mode Output Enable</b> — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1,<br>BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin.<br>Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO<br>(SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect.<br>0 Output driver disabled so SPI data I/O pin acts as an input<br>1 SPI I/O pin enabled as an output |

| 1<br>SPISWAI | SPI Stop in Wait Mode         0 SPI clocks continue to operate in wait mode         1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>SPC0    | <ul> <li>SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.</li> <li>O SPI uses separate pins for data input and data output</li> <li>1 SPI configured for single-wire bidirectional operation</li> </ul>           |

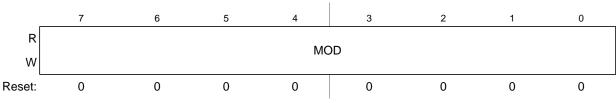

# 15.4.3 SPI Baud Rate Register (SPIBR)

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

= Unimplemented or Reserved

#### Figure 15-7. SPI Baud Rate Register (SPIBR)

#### Table 15-4. SPIBR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>SPPR[2:0] | <b>SPI Baud Rate Prescale Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 15-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 15-4). |

| 2:0<br>SPR[2:0]  | <b>SPI Baud Rate Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 15-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 15-4). The output of this divider is the SPI bit rate clock for master mode.            |

Chapter 15 Serial Peripheral Interface (S08SPIV3)

# 15.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 15.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

# 15.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 15-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output

### 16.2.1.1 EXTCLK — External Clock Source

Control bits in the timer status and control register allow the user to select nothing (timer disable), the bus-rate clock (the normal default source), a crystal-related clock, or an external clock as the clock which drives the TPM prescaler and subsequently the 16-bit TPM counter. The external clock source is synchronized in the TPM. The bus clock clocks the synchronizer; the frequency of the external source must be no more than one-fourth the frequency of the bus-rate clock, to meet Nyquist criteria and allowing for jitter.

The external clock signal shares the same pin as a channel I/O pin, so the channel pin will not be usable for channel I/O function when selected as the external clock source. It is the user's responsibility to avoid such settings. If this pin is used as an external clock source (CLKSB:CLKSA = 1:1), the channel can still be used in output compare mode as a software timer (ELSnB:ELSnA = 0:0).

### 16.2.1.2 TPMxCHn — TPM Channel n I/O Pin(s)

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the channel configuration. The TPM pins share with general purpose I/O pins, where each pin has a port data register bit, and a data direction control bit, and the port has optional passive pullups which may be enabled whenever a port pin is acting as an input.

The TPM channel does not control the I/O pin when (ELSnB:ELSnA = 0:0) or when (CLKSB:CLKSA = 0:0) so it normally reverts to general purpose I/O control. When CPWMS = 1 (and ELSnB:ELSnA not = 0:0), all channels within the TPM are configured for center-aligned PWM and the TPMxCHn pins are all controlled by the TPM system. When CPWMS=0, the MSnB:MSnA control bits determine whether the channel is configured for input capture, output compare, or edge-aligned PWM.

When a channel is configured for input capture (CPWMS=0, MSnB:MSnA = 0:0 and ELSnB:ELSnA not = 0:0), the TPMxCHn pin is forced to act as an edge-sensitive input to the TPM. ELSnB:ELSnA control bits determine what polarity edge or edges will trigger input-capture events. A synchronizer based on the bus clock is used to synchronize input edges to the bus clock. This implies the minimum pulse width—that can be reliably detected—on an input capture pin is four bus clock periods (with ideal clock pulses as near as two bus clocks can be detected). TPM uses this pin as an input capture input to override the port data and data direction controls for the same pin.

When a channel is configured for output compare (CPWMS=0, MSnB:MSnA = 0:1 and ELSnB:ELSnA not = 0:0), the associated data direction control is overridden, the TPMxCHn pin is considered an output controlled by the TPM, and the ELSnB:ELSnA control bits determine how the pin is controlled. The remaining three combinations of ELSnB:ELSnA determine whether the TPMxCHn pin is toggled, cleared, or set each time the 16-bit channel value register matches the timer counter.

When the output compare toggle mode is initially selected, the previous value on the pin is driven out until the next output compare event—then the pin is toggled.

#### Chapter 16 Timer/PWM Module (S08TPMV3)

to avoid such settings.) The TPM channel could still be used in output compare mode for software timing functions (pin controls set not to affect the TPM channel pin).

### 16.4.1.2 Counter Overfl w and Modulo Reset

An interrupt flag and enable are associated with the 16-bit main counter. The flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE=0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE=1) where a static hardware interrupt is generated whenever the TOF flag is equal to one.

The conditions causing TOF to become set depend on whether the TPM is configured for center-aligned PWM (CPWMS=1). In the simplest mode, there is no modulus limit and the TPM is not in CPWMS=1 mode. In this case, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the TPM is in center-aligned PWM mode (CPWMS=1), the TOF flag gets set as the counter changes direction at the end of the count value set in the modulus register (that is, at the transition from the value set in the modulus register to the next lower count value). This corresponds to the end of a PWM period (the 0x0000 count value corresponds to the center of a period).

### 16.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

### 16.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

# 16.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

A force-type breakpoint waits for the current instruction to finish and then acts upon the breakpoint request. The usual action in response to a breakpoint is to go to active background mode rather than continuing to the next instruction in the user application program.

The tag vs. force terminology is used in two contexts within the debug module. The first context refers to breakpoint requests from the debug module to the CPU. The second refers to match signals from the comparators to the debugger control logic. When a tag-type break request is sent to the CPU, a signal is entered into the instruction queue along with the opcode so that if/when this opcode ever executes, the CPU will effectively replace the tagged opcode with a BGND opcode so the CPU goes to active background mode rather than executing the tagged instruction. When the TRGSEL control bit in the DBGT register is set to select tag-type operation, the output from comparator A or B is qualified by a block of logic in the debug module that tracks opcodes and only produces a trigger to the debugger if the opcode at the compare address is actually executed. There is separate opcode tracking logic for each comparator so more than one compare event can be tracked through the instruction queue at a time.

# 17.3.5 Trigger Modes

The trigger mode controls the overall behavior of a debug run. The 4-bit TRG field in the DBGT register selects one of nine trigger modes. When TRGSEL = 1 in the DBGT register, the output of the comparator must propagate through an opcode tracking circuit before triggering FIFO actions. The BEGIN bit in DBGT chooses whether the FIFO begins storing data when the qualified trigger is detected (begin trace), or the FIFO stores data in a circular fashion from the time it is armed until the qualified trigger is detected (end trigger).

A debug run is started by writing a 1 to the ARM bit in the DBGC register, which sets the ARMF flag and clears the AF and BF flags and the CNT bits in DBGS. A begin-trace debug run ends when the FIFO gets full. An end-trace run ends when the selected trigger event occurs. Any debug run can be stopped manually by writing a 0 to ARM or DBGEN in DBGC.

In all trigger modes except event-only modes, the FIFO stores change-of-flow addresses. In event-only trigger modes, the FIFO stores data in the low-order eight bits of the FIFO.

The BEGIN control bit is ignored in event-only trigger modes and all such debug runs are begin type traces. When TRGSEL = 1 to select opcode fetch triggers, it is not necessary to use R/W in comparisons because opcode tags would only apply to opcode fetches that are always read cycles. It would also be unusual to specify TRGSEL = 1 while using a full mode trigger because the opcode value is normally known at a particular address.

The following trigger mode descriptions only state the primary comparator conditions that lead to a trigger. Either comparator can usually be further qualified with R/W by setting RWAEN (RWBEN) and the corresponding RWA (RWB) value to be matched against R/W. The signal from the comparator with optional R/W qualification is used to request a CPU breakpoint if BRKEN = 1 and TAG determines whether the CPU request will be a tag request or a force request.

| Num | С | Characteristic                                                                                       | Symbol            | Condition | Min          | Typ <sup>1</sup> | Max          | Unit |

|-----|---|------------------------------------------------------------------------------------------------------|-------------------|-----------|--------------|------------------|--------------|------|

| 15  | D | POR re-arm voltage <sup>8</sup>                                                                      | V <sub>POR</sub>  |           | 0.9          | 1.4              | 2.0          | V    |

| 16  | D | POR re-arm time <sup>9</sup>                                                                         | t <sub>POR</sub>  |           | 10           | —                |              | μs   |

| 17  | Ρ | Low-voltage detection threshold —<br>high range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVD1</sub> |           | 3.9<br>4.0   | 4.0<br>4.1       | 4.1<br>4.2   | V    |

| 18  | Ρ | Low-voltage detection threshold —<br>low range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising  | V <sub>LVD0</sub> |           | 2.48<br>2.54 | 2.56<br>2.62     | 2.64<br>2.70 | V    |

| 19  | Ρ | Low-voltage warning threshold —<br>high range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVW3</sub> |           | 4.5<br>4.6   | 4.6<br>4.7       | 4.7<br>4.8   | v    |

| 20  | Ρ | Low-voltage warning threshold —<br>high range 0<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVW2</sub> |           | 4.2<br>4.3   | 4.3<br>4.4       | 4.4<br>4.5   | v    |

| 21  | Ρ | Low-voltage warning threshold<br>low range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising    | V <sub>LVW1</sub> |           | 2.84<br>2.90 | 2.92<br>2.98     | 3.00<br>3.06 | V    |

| 22  | Ρ | Low-voltage warning threshold —<br>low range 0<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising  | V <sub>LVW0</sub> |           | 2.66<br>2.72 | 2.74<br>2.80     | 2.82<br>2.88 | V    |

| 23  | Т | Low-voltage inhibit reset/recover hysteresis                                                         | V <sub>hys</sub>  | 5 V       | _            | 100              | —            | mV   |

|     |   | -                                                                                                    |                   | 3 V       |              | 60               |              |      |

| 24  | Ρ | Bandgap Voltage Reference <sup>10</sup>                                                              | V <sub>BG</sub>   |           | 1.18         | 1.20             | 1.21         | V    |

#### Table A-6. DC Characteristics (continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested.

<sup>2</sup> When IRQ or a pin interrupt is configured to detect rising edges, pulldown resistors are used in place of pullup resistors.

<sup>3</sup> The specified resistor value is the actual value internal to the device. The pullup value may measure higher when measured externally on the pin.

- <sup>4</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- $^{5}$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub>.

- <sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>7</sup> The  $\overline{\text{RESET}}$  pin does not have a clamp diode to V<sub>DD</sub>. Do not drive this pin above V<sub>DD</sub>.

- <sup>8</sup> Maximum is highest voltage that POR will occur.

- <sup>9</sup> Simulated, not tested

- <sup>10</sup> Factory trimmed at  $V_{DD} = 5.0$  V, Temp = 25°C

#### **Appendix A Electrical Characteristics**

| Characteristic         | Conditions    | С | Symb                | Min | Typ <sup>1</sup> | Max | Unit  | Comment |

|------------------------|---------------|---|---------------------|-----|------------------|-----|-------|---------|

| Temp sensor            | –40°C to 25°C |   | D m                 | —   | 3.266            |     | mV/°C |         |

| slope                  | 25°C to 125°C |   |                     |     | 3.638            | _   |       |         |

| Temp sensor<br>voltage | 25°C          | D | V <sub>TEMP25</sub> | _   | 1.396            | _   | mV    |         |

Table A-12. ADC Characteristics (continued)

<sup>1</sup> Typical values assume V<sub>DD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> Based on input pad leakage current. Refer to pad electricals.

Appendix A Electrical Characteristics

# A.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

# A.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East).

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter           | Symbol              | Conditions                                         | Frequency     | f <sub>osc</sub> /f <sub>вus</sub> | Level <sup>1</sup><br>(Max) | Unit           |  |    |  |  |  |  |  |

|---------------------|---------------------|----------------------------------------------------|---------------|------------------------------------|-----------------------------|----------------|--|----|--|--|--|--|--|

|                     | V <sub>RE_TEM</sub> | $V_{DD} = 5 V$                                     | 0.15 – 50 MHz | 4 MHz crystal                      | 0                           | dBμV           |  |    |  |  |  |  |  |

|                     |                     | T <sub>A</sub> = +25°C<br>package type<br>16-TSSOP | 50 – 150 MHz  | 16 MHzbus                          | 0                           |                |  |    |  |  |  |  |  |

| Radiated emissions, |                     |                                                    | 150 – 500 MHz |                                    | -6                          |                |  |    |  |  |  |  |  |

| electric field      |                     |                                                    |               |                                    |                             | 500 – 1000 MHz |  | -9 |  |  |  |  |  |

|                     |                     |                                                    |               |                                    |                             |                |  |    |  |  |  |  |  |

|                     |                     |                                                    | SAE Level     |                                    | 1                           | —              |  |    |  |  |  |  |  |

Table A-17. Radiated Emissions, Electric Field

<sup>1</sup> Data based on qualification test results.

# A.14.2 Conducted Transient Susceptibility

Microcontroller transient conducted susceptibility is measured in accordance with an internal Freescale test method. The measurement is performed with the microcontroller installed on a custom EMC evaluation board and running specialized EMC test software designed in compliance with the test method. The conducted susceptibility is determined by injecting the transient susceptibility signal on each pin of the microcontroller. The transient waveform and injection methodology is based on IEC 61000-4-4 (EFT/B). The transient voltage required to cause performance degradation on any pin in the tested configuration is greater than or equal to the reported levels unless otherwise indicated by footnotes below Table A-18.